Symbol LMS algorithm and system for assembly line ADC calibration

An LMS algorithm and pipeline technology, applied in the direction of analog/digital conversion calibration/test, electrical components, code conversion, etc., can solve the problem of failing to reach convergence speed and misalignment accuracy, increasing misalignment accuracy, and unable to reduce convergence speed and misalignment accuracy And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The technical solutions in the embodiments of the present invention will be described clearly and in detail below with reference to the drawings in the embodiments of the present invention. The described embodiments are only some of the embodiments of the invention.

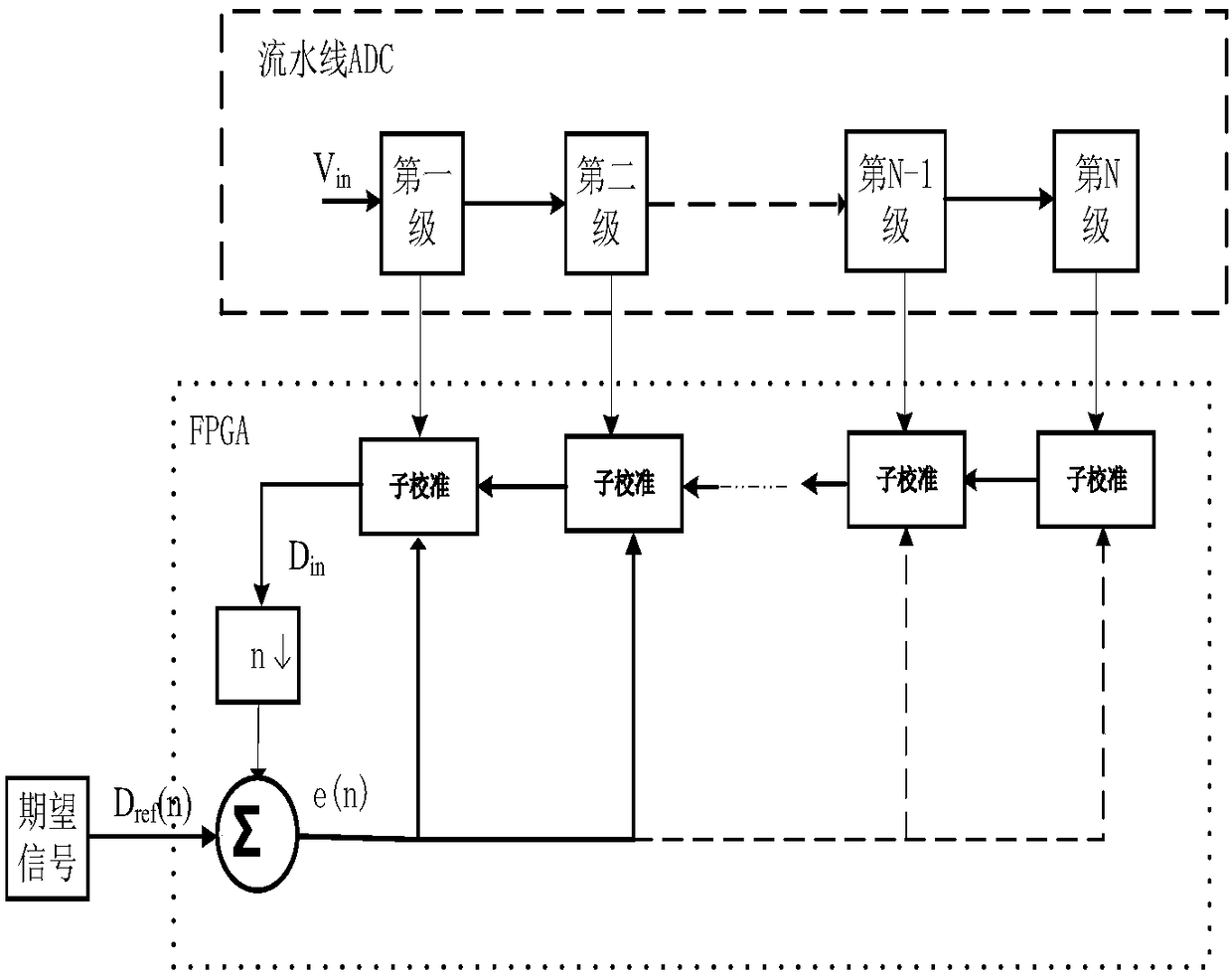

[0034] The technical scheme that the present invention solves the problems of the technologies described above is:

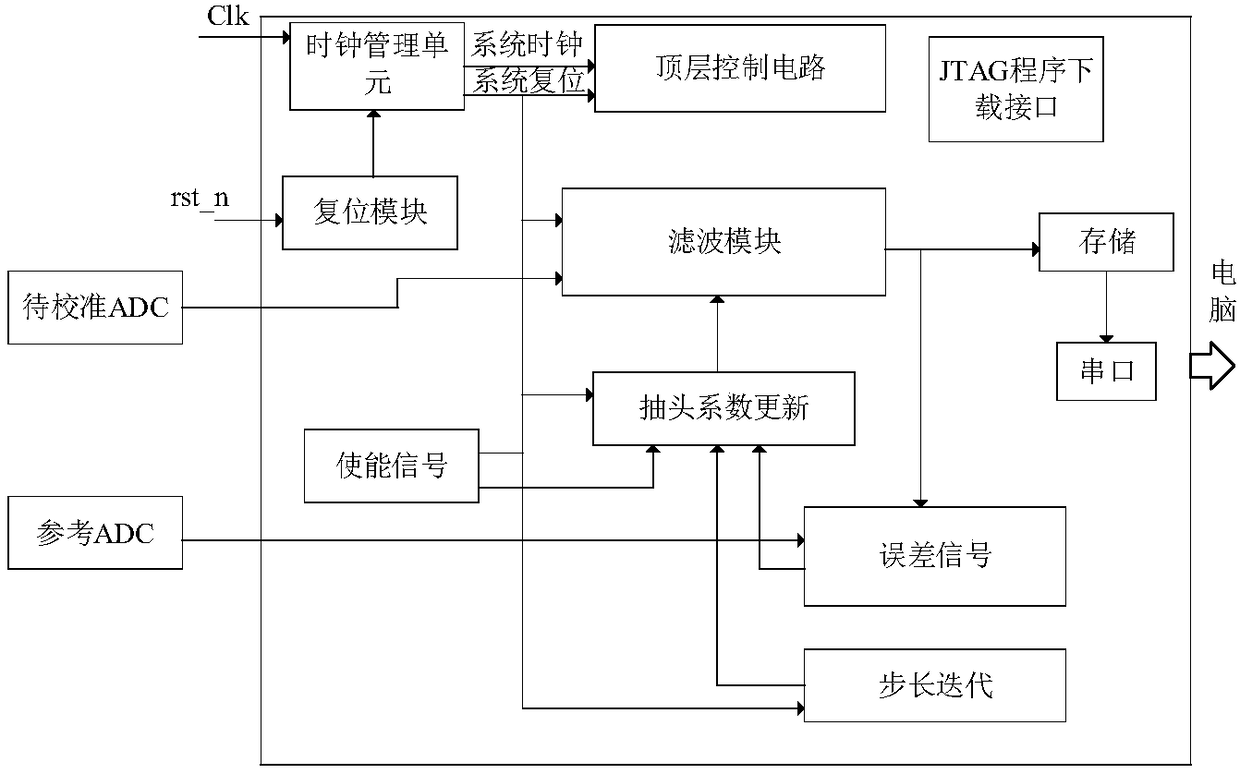

[0035] The application example of the present invention adopts a 12bit 100MS / s pipeline ADC. The calibration work platform adopts Virtex-5ML507 (XC5VFX70T), which is a high-performance FPGA based on 65nm process.

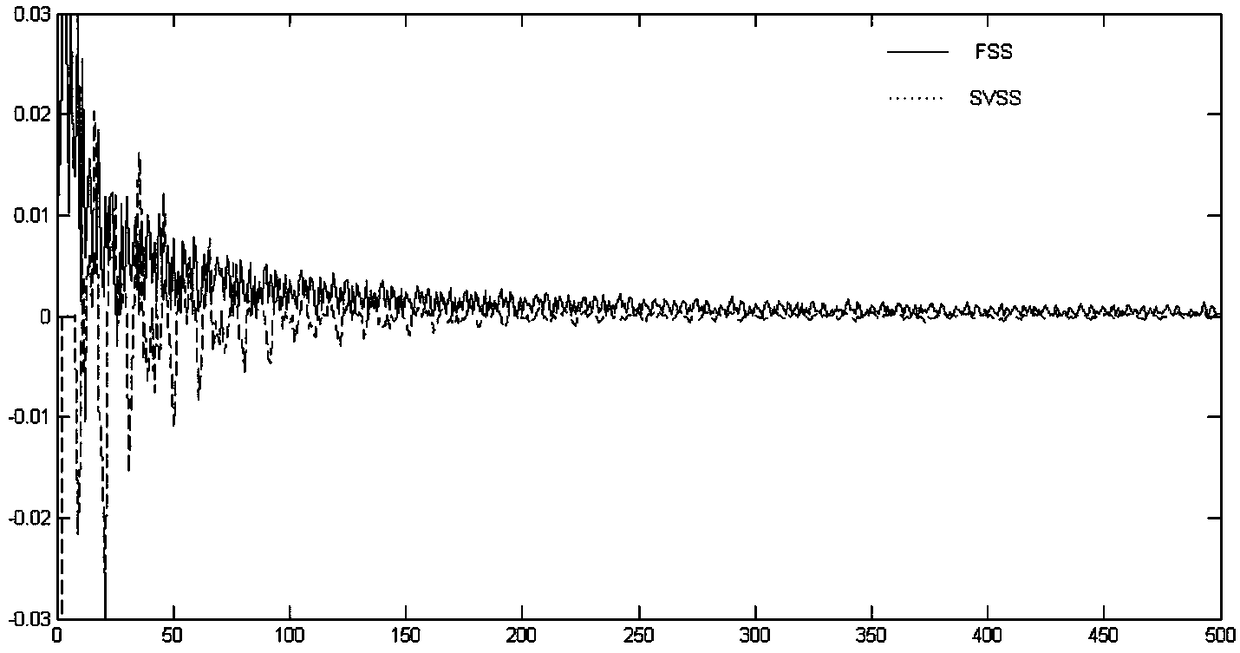

[0036] figure 1Shown is the comparison diagram of the error convergence curve of the present invention, and the FSS in the figure is the output curve diagram of the traditional LMS. Here it refers to the analysis of the output error after calibration using the progressive mode and the oscillation mode respectively. The FSS algorithm adopts a gradual mode during calibration, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More