Semiconductor structure and formation method thereof

A technology of semiconductor and pore structure, which is applied in the field of semiconductor structure and its formation, can solve the problems of product reliability decline, influence of current transmission effect on the surface of semiconductor layer, and influence of product yield, so as to improve quality, improve current transmission performance, eliminate The effect of defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] Specific implementations of the semiconductor structure and its forming method provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

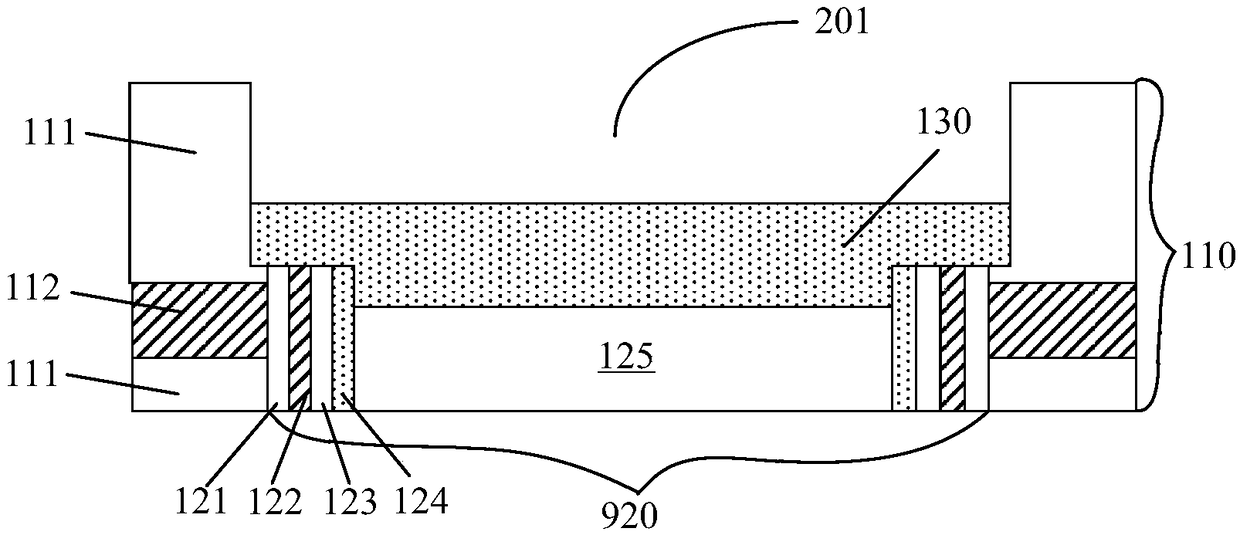

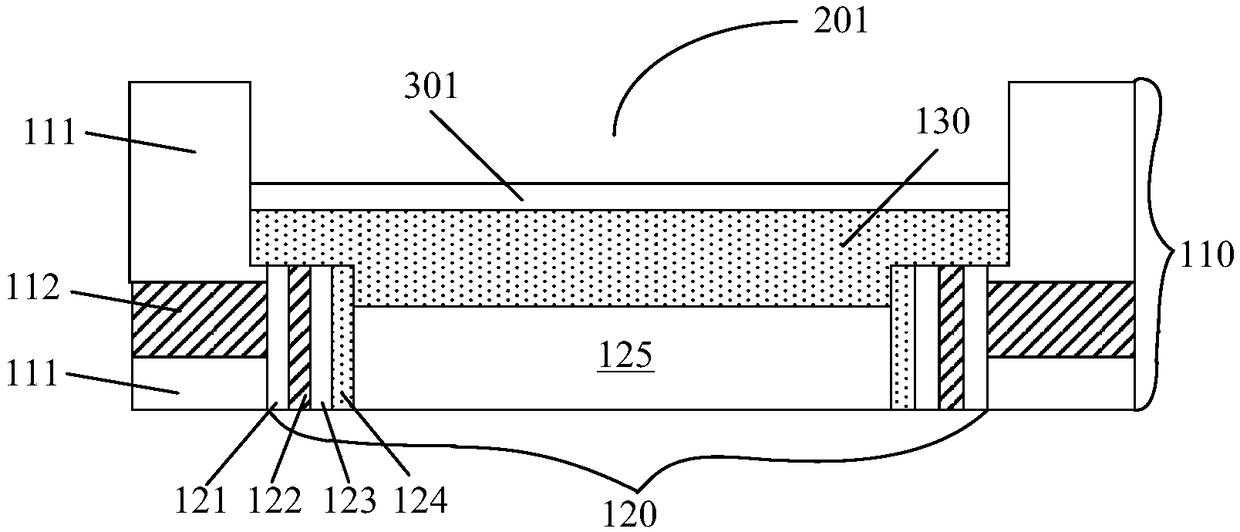

[0025] Please refer to Figure 1 to Figure 8 The specific embodiment of the present invention also provides a method for forming a semiconductor structure.

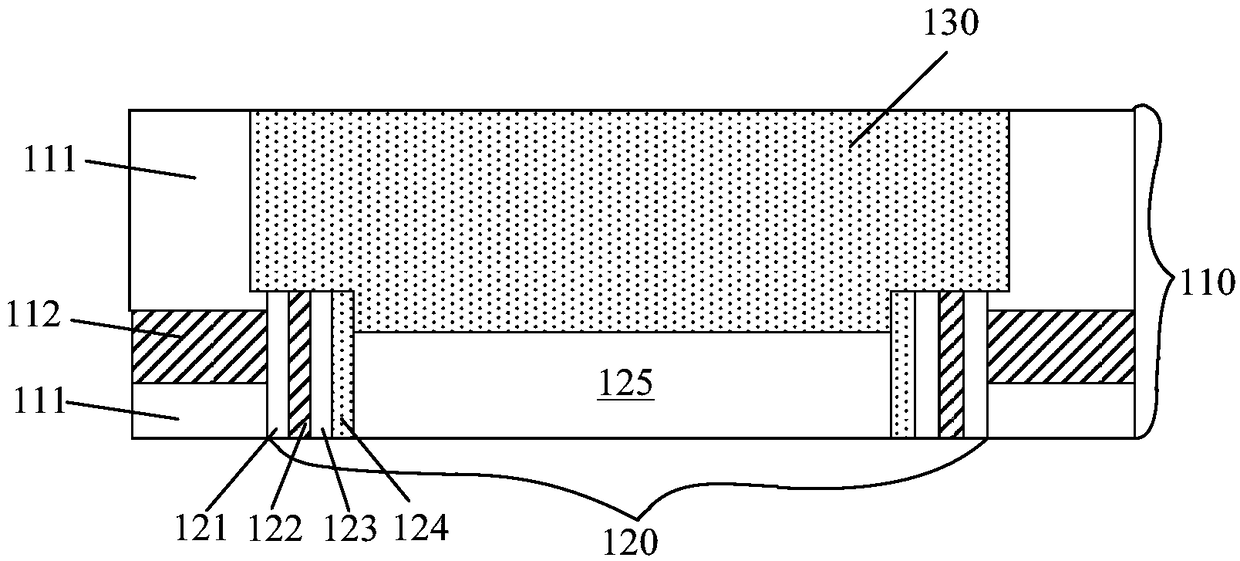

[0026] Please refer to figure 1 , providing a base, the base includes a first stack structure 110 , a first channel hole structure 120 penetrating through the first stack structure 110 , and a semiconductor layer 130 is formed on the top of the first channel hole structure 120 .

[0027] The base includes a substrate (not shown in the figure), forming a first stacked structure 110 stacked with the surface of the substrate along a direction perpendicular to the surface of the substrate, and the first stacked structure 110 includes first insulating layers stacked on each other. layer 111 and the first sacrificial layer 112...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More