Patents

Literature

137results about How to "Improve yield and reliability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

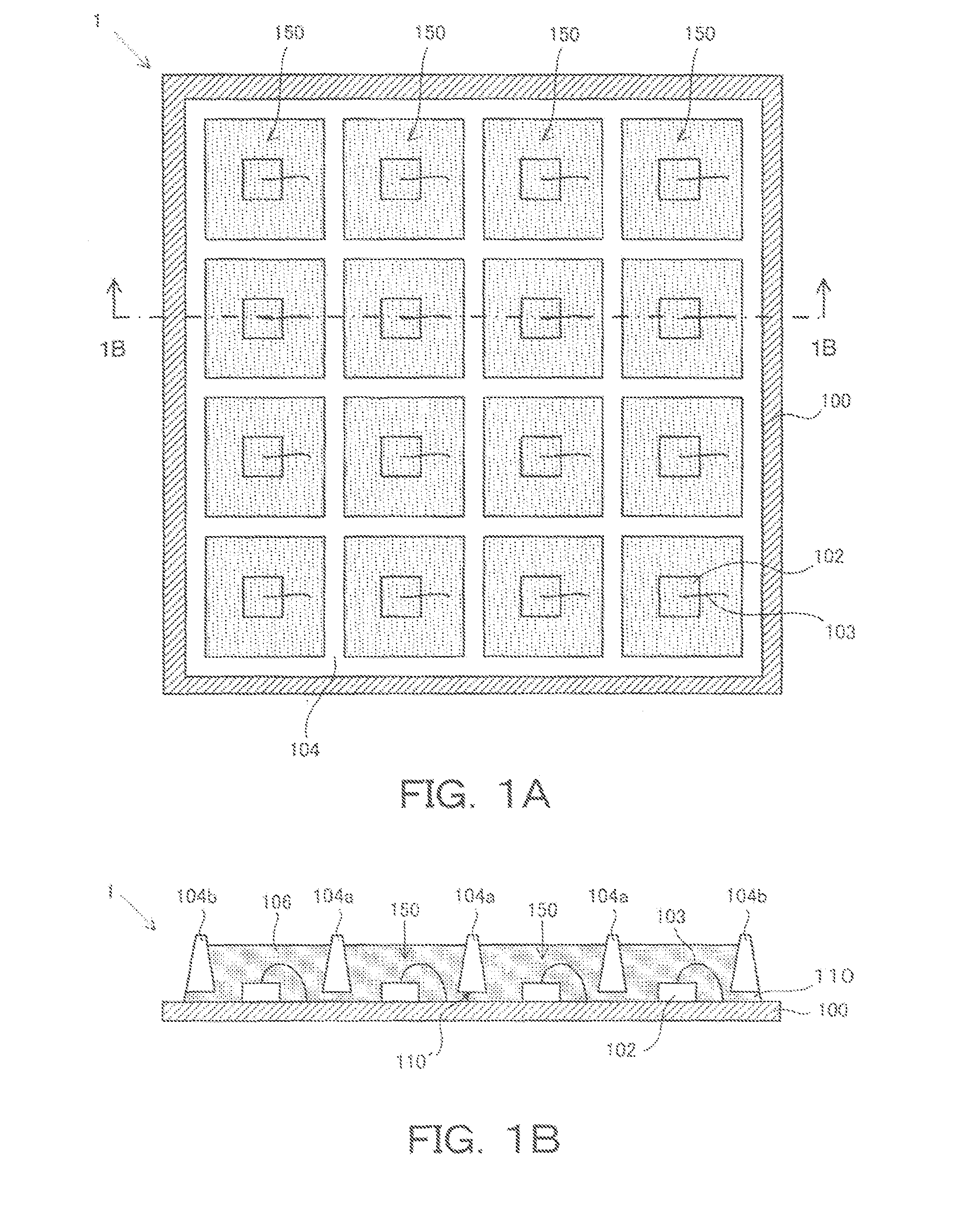

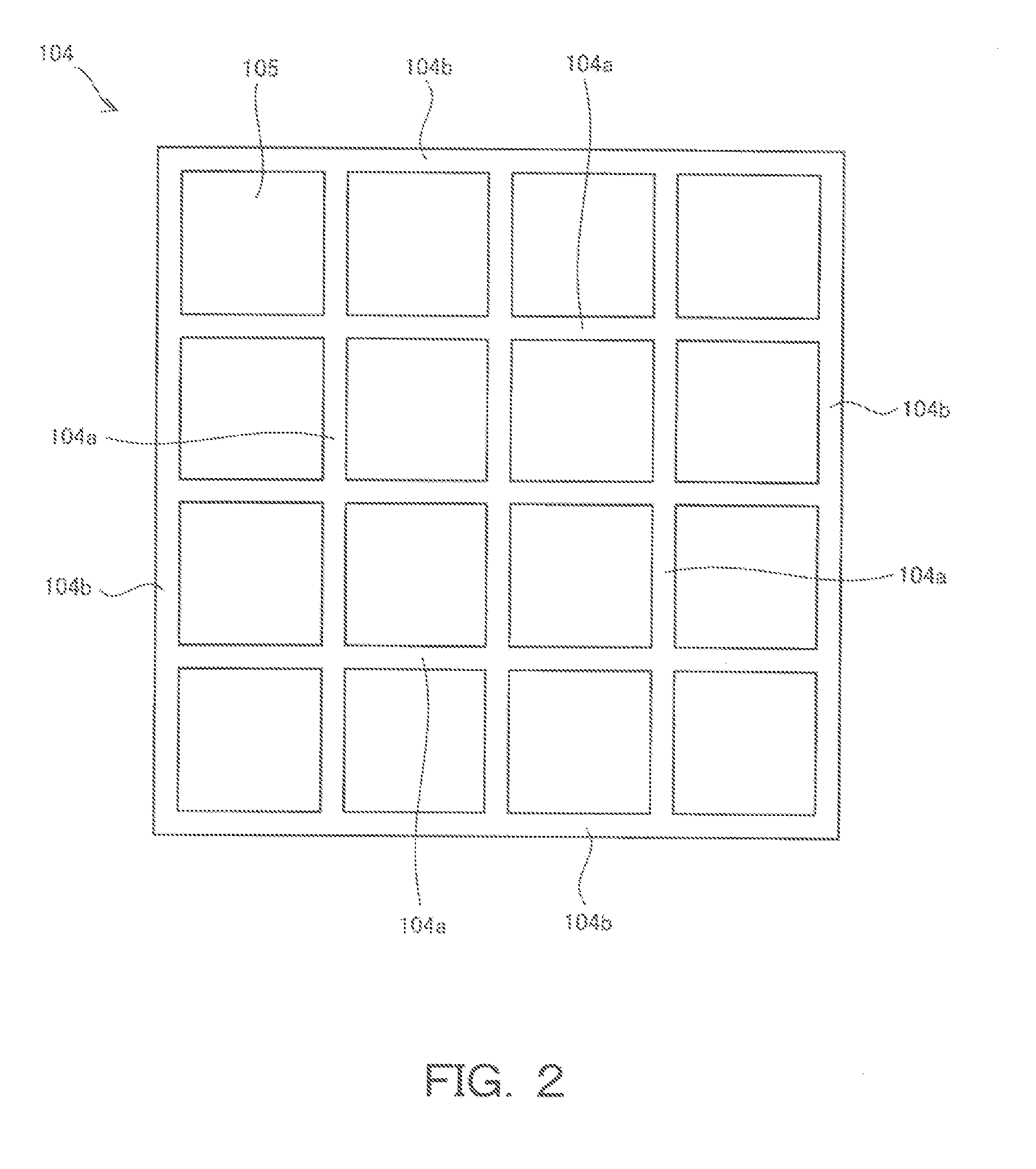

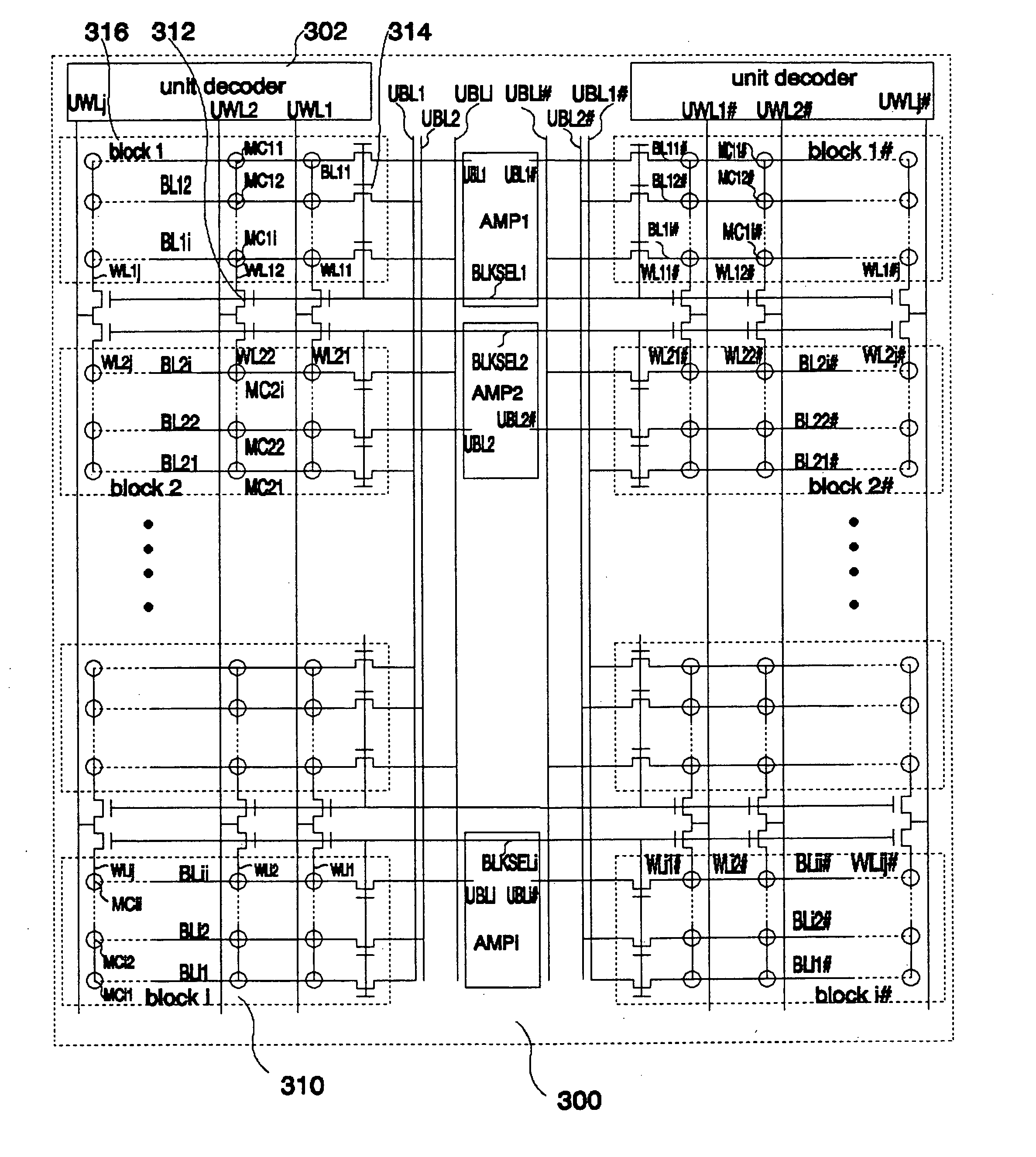

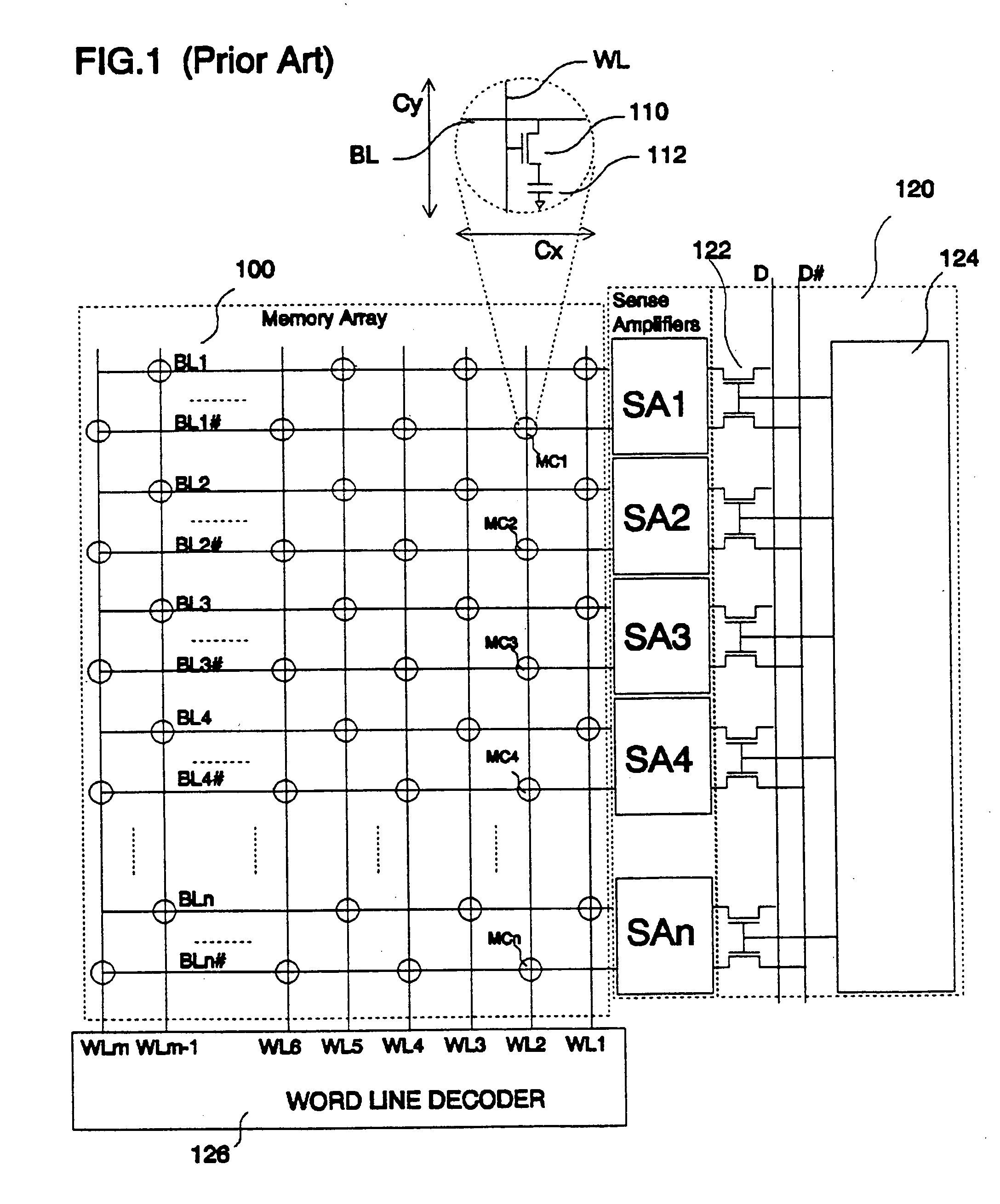

High performance embedded semiconductor memory devices with multiple dimension first-level bit-lines

InactiveUS7064376B2Improve performanceReduce power consumptionTransistorSolid-state devicesBit lineInternal memory

Owner:UNIRAM TECH

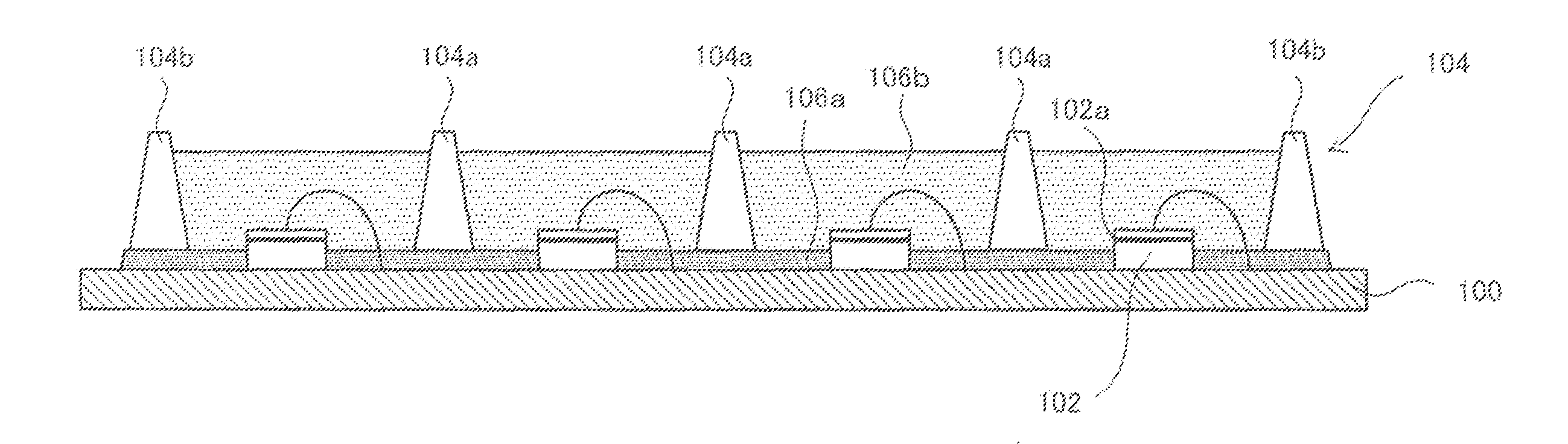

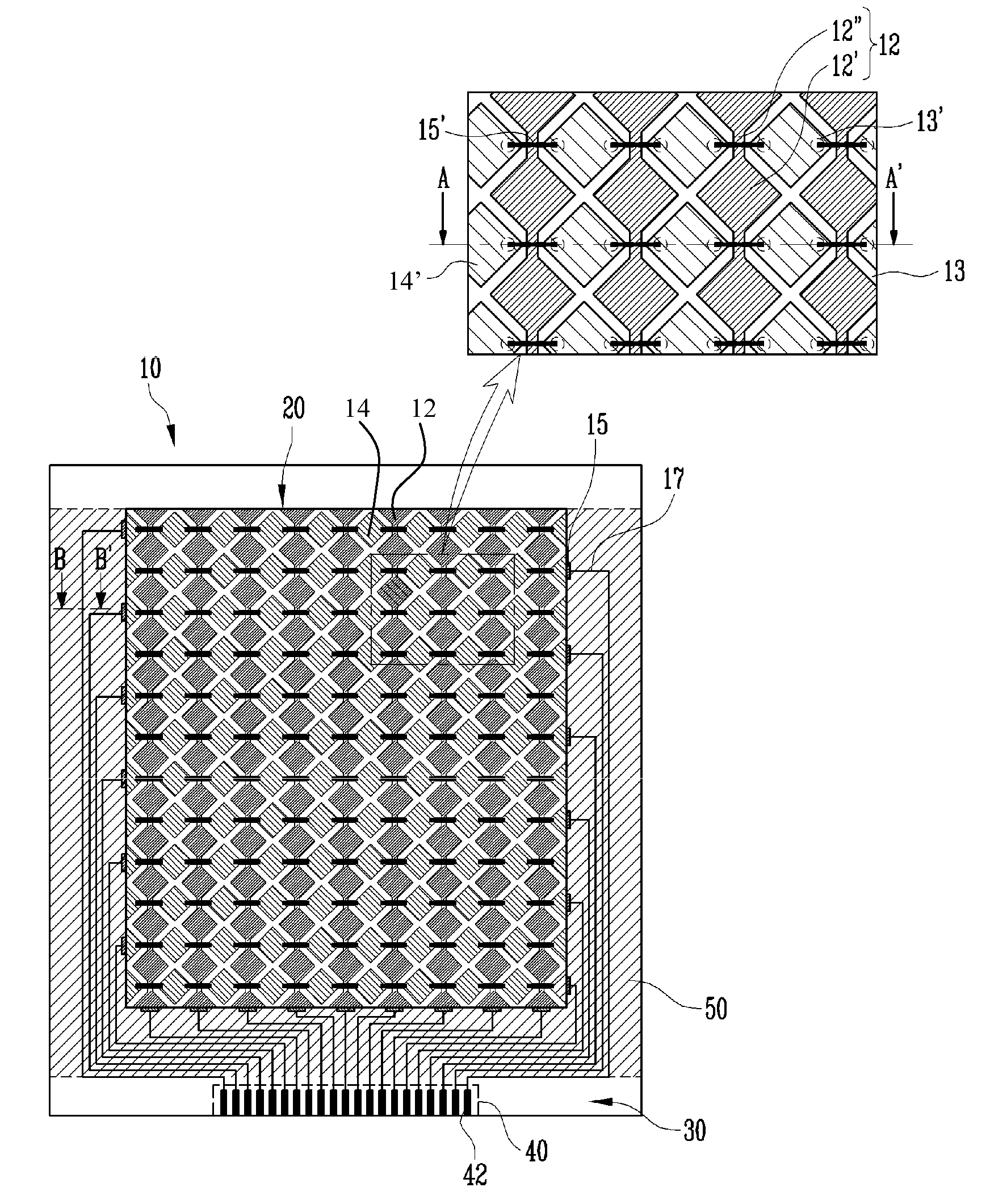

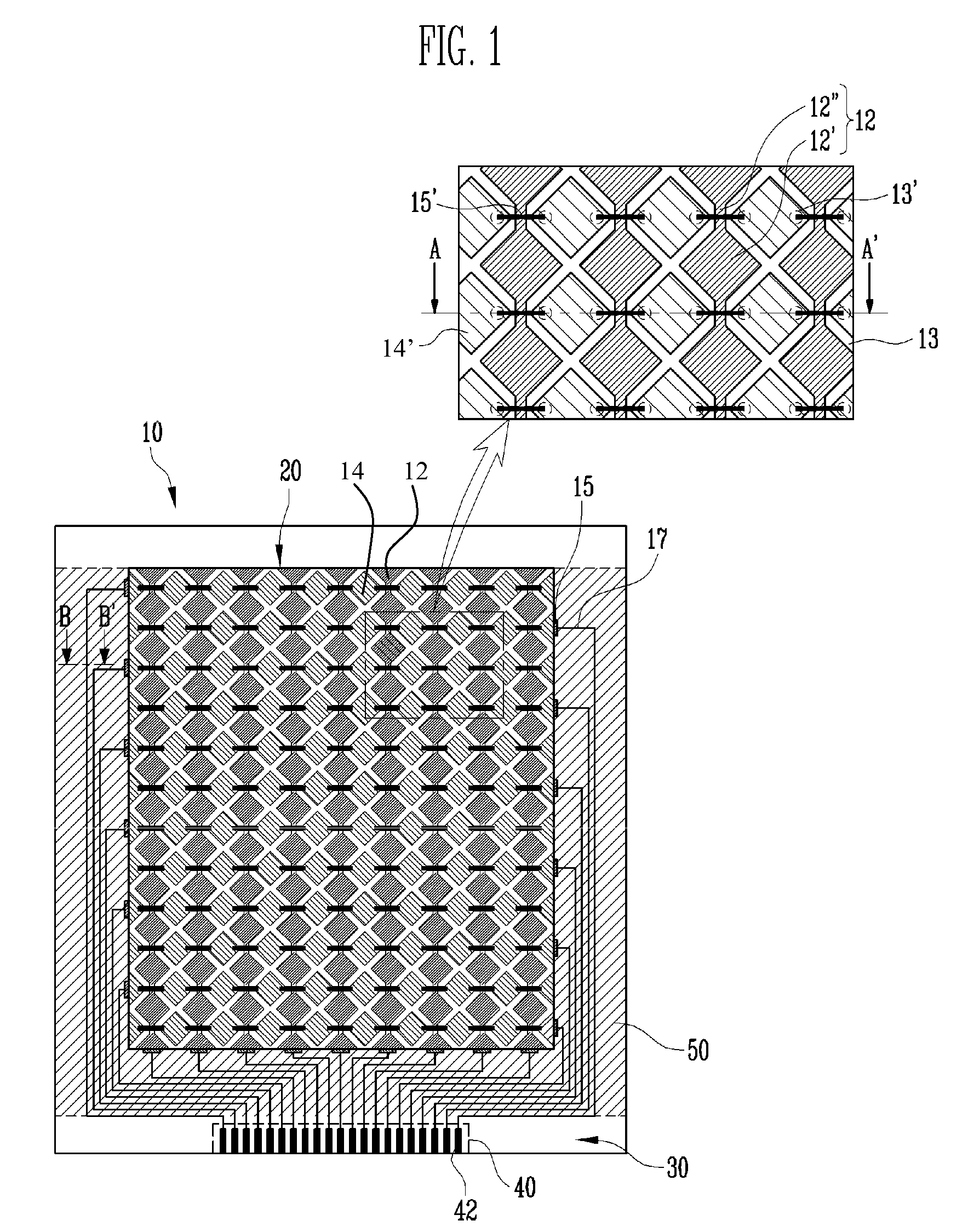

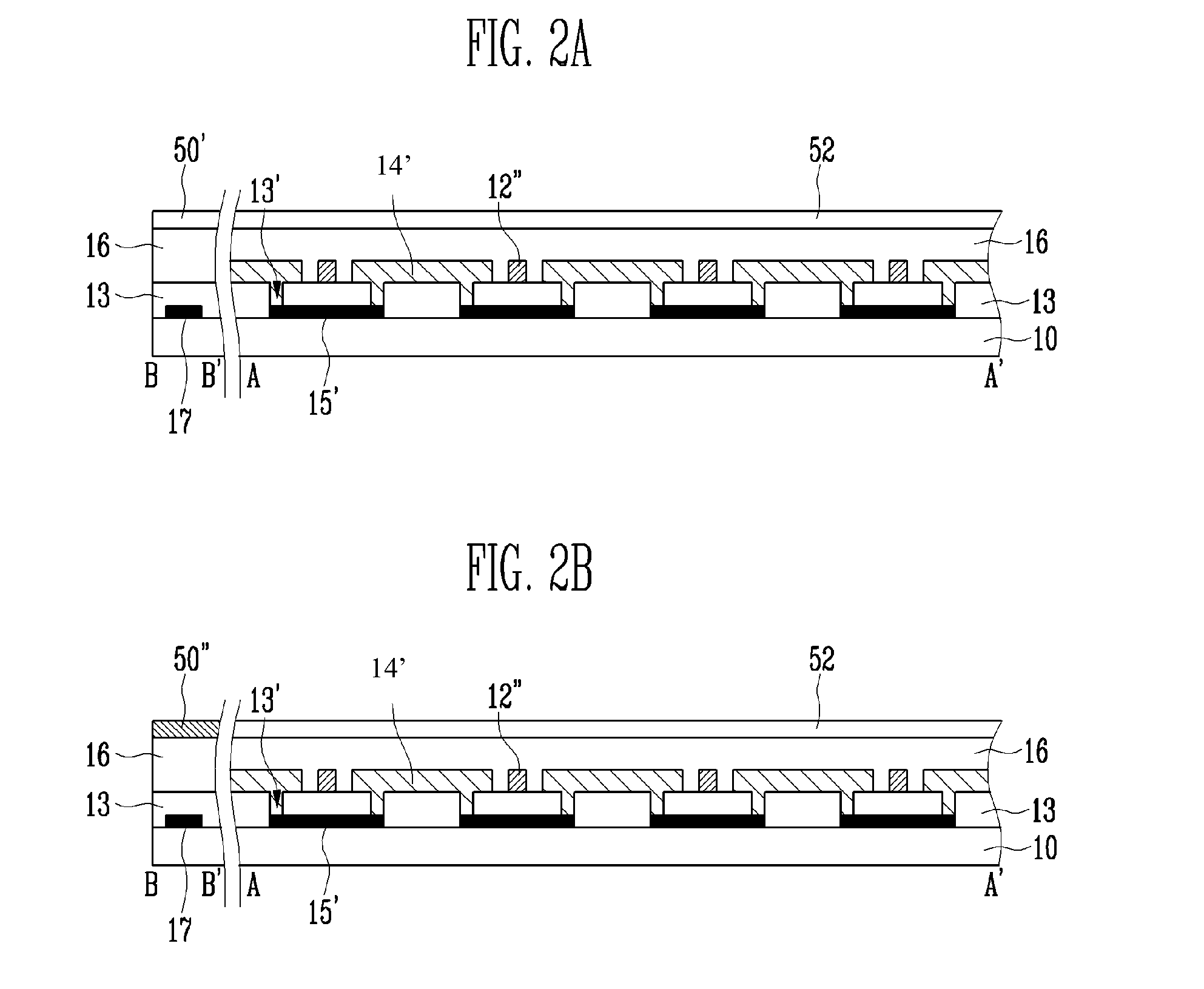

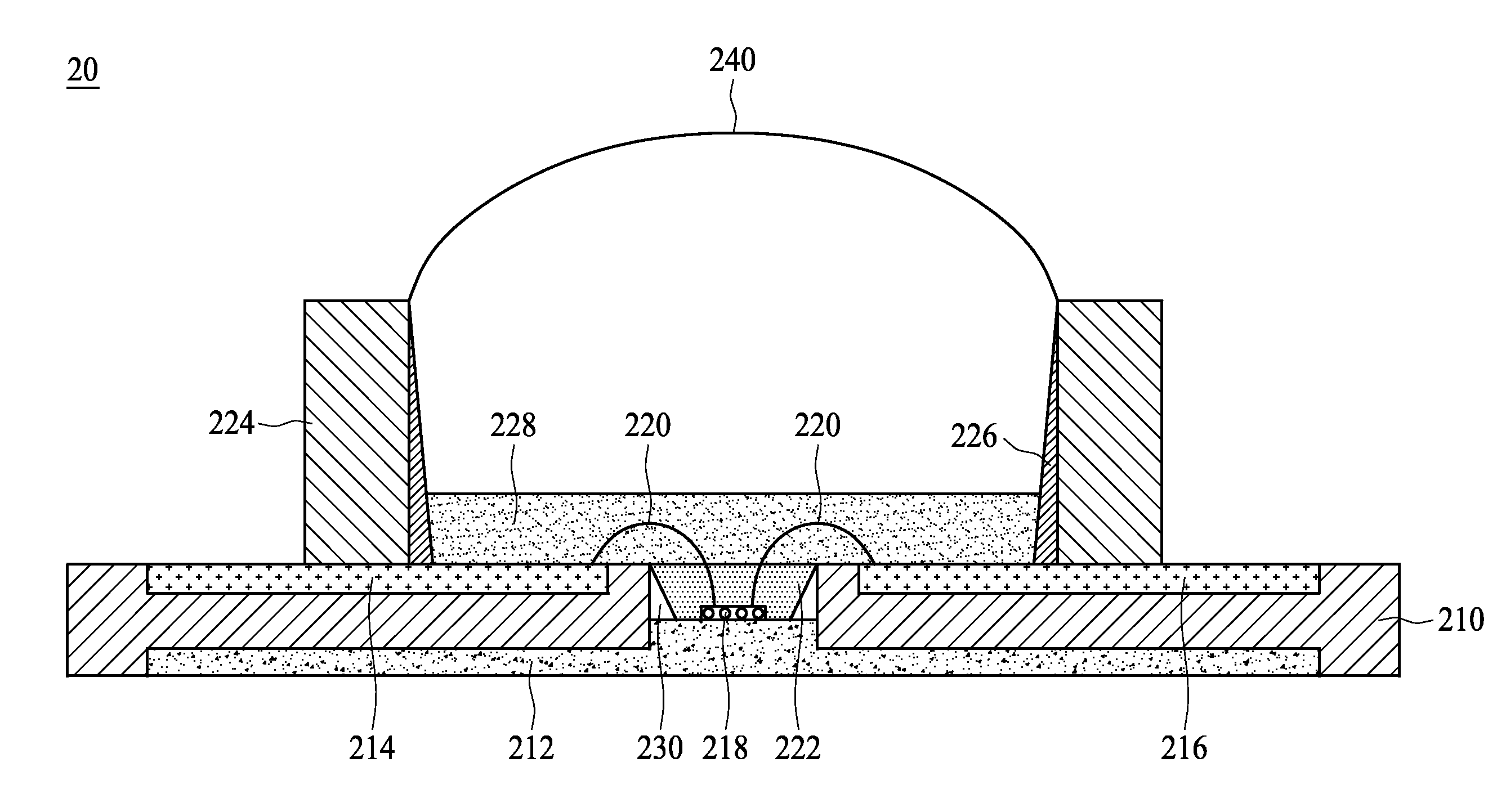

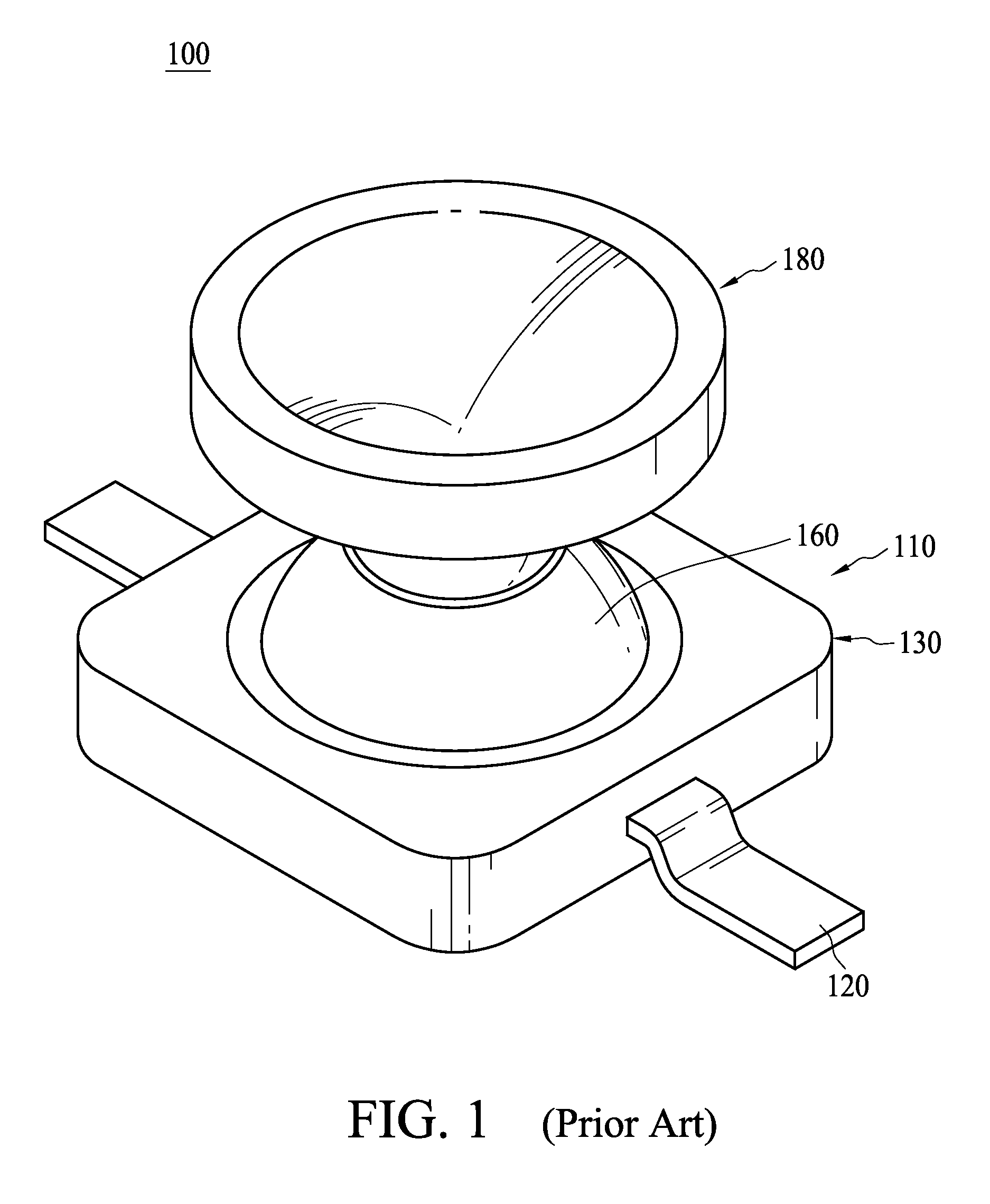

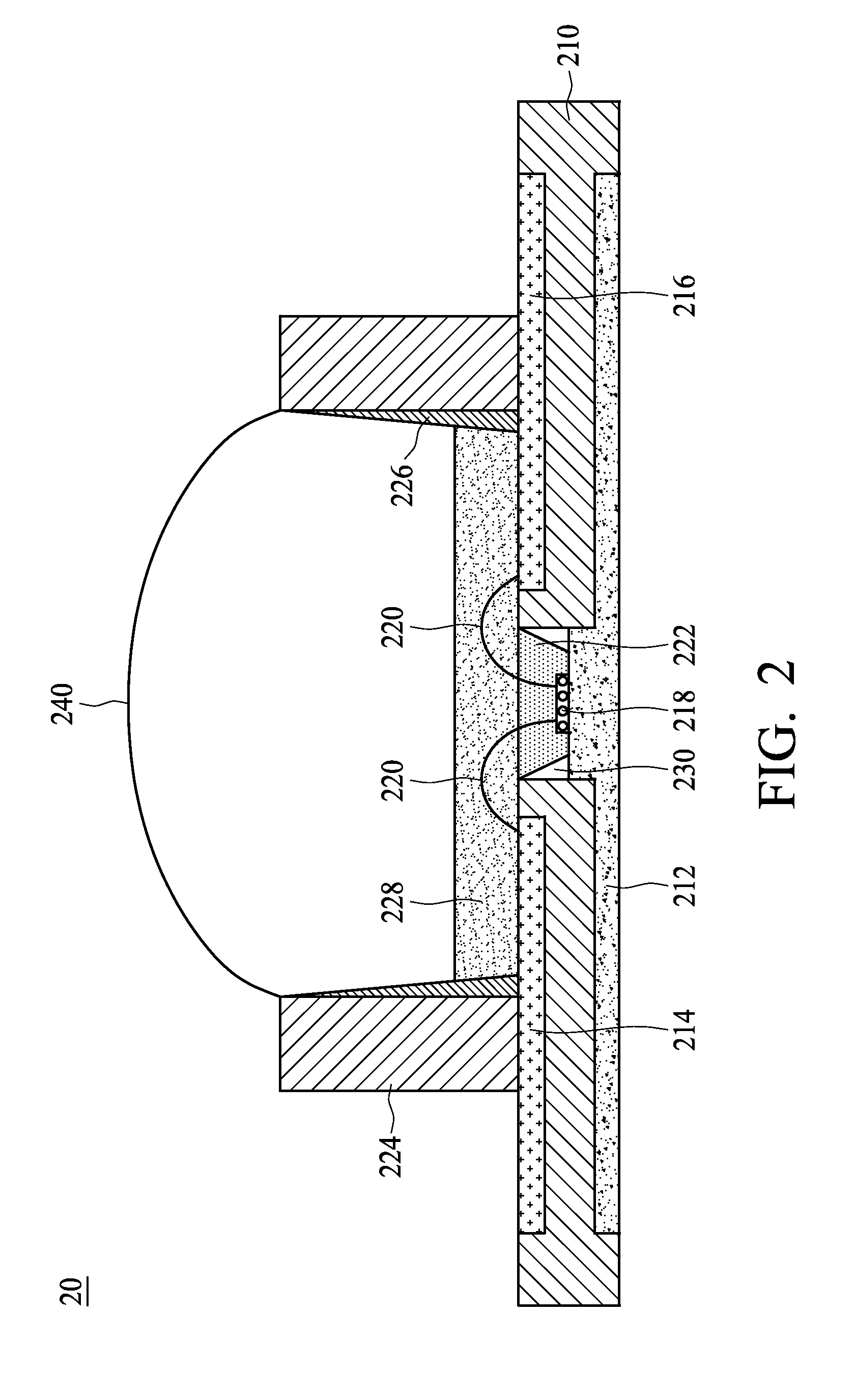

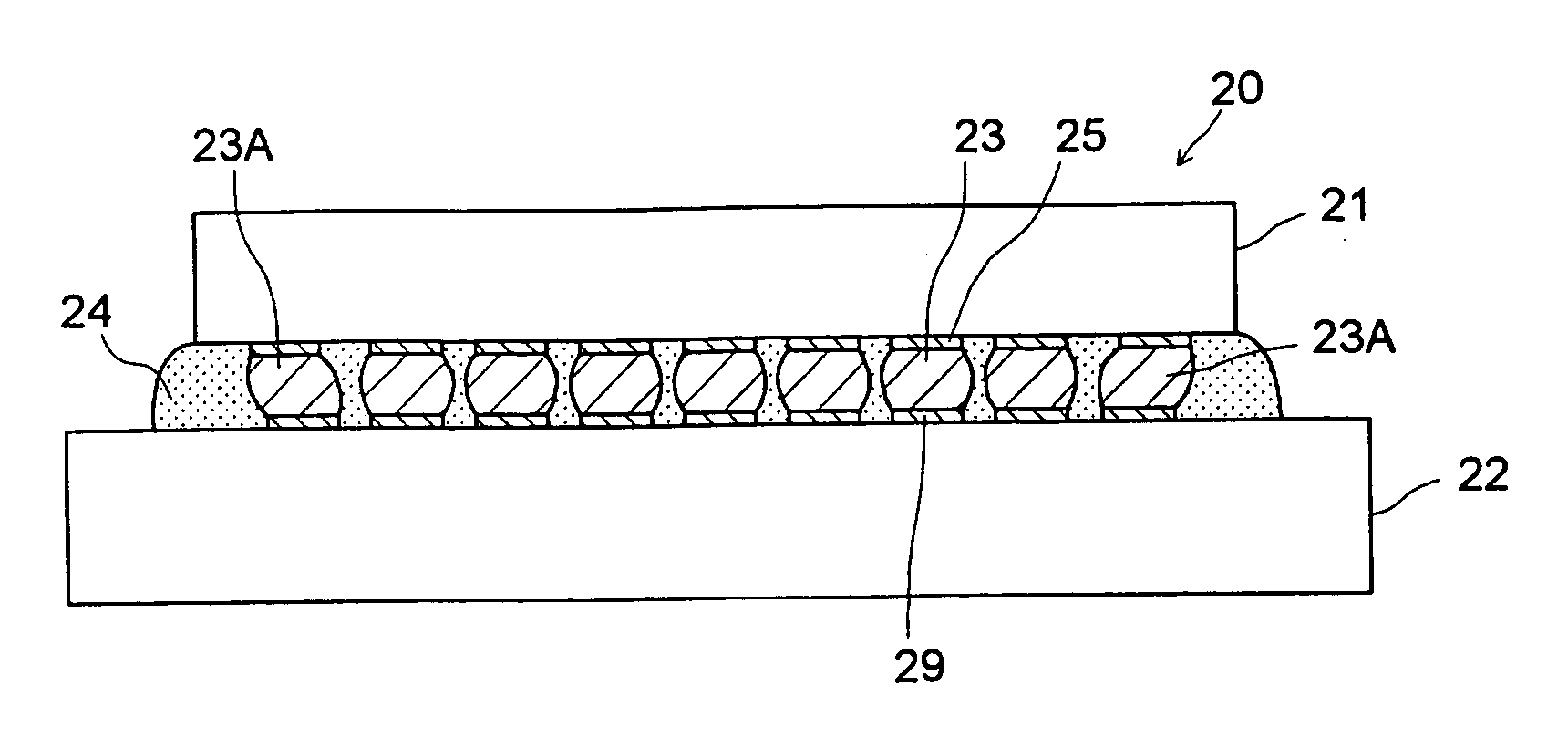

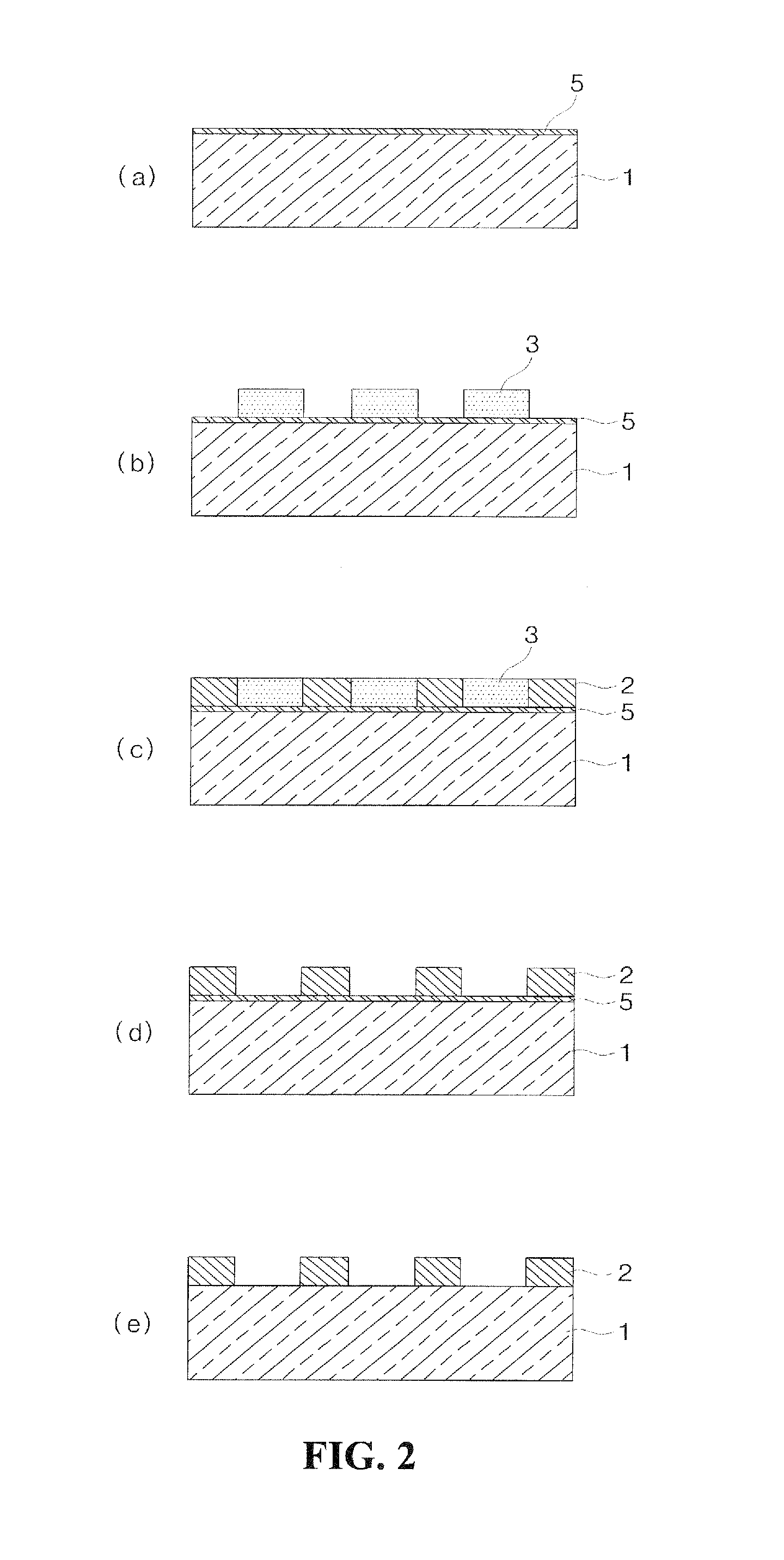

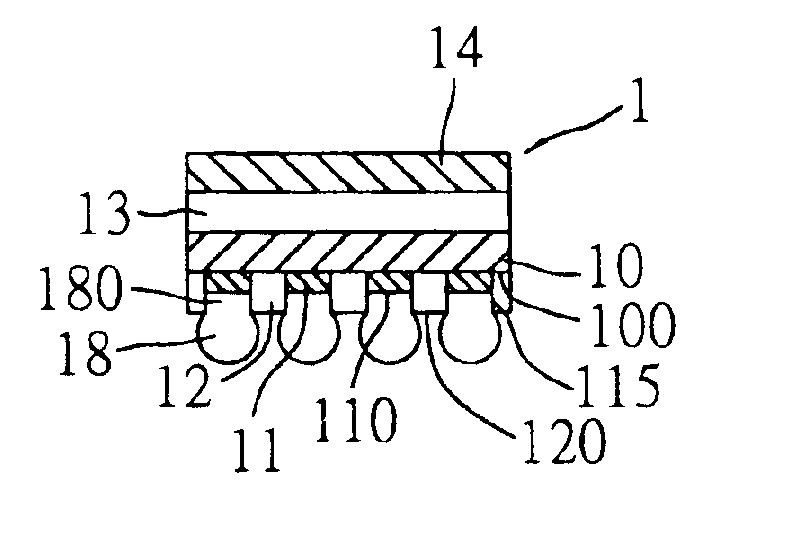

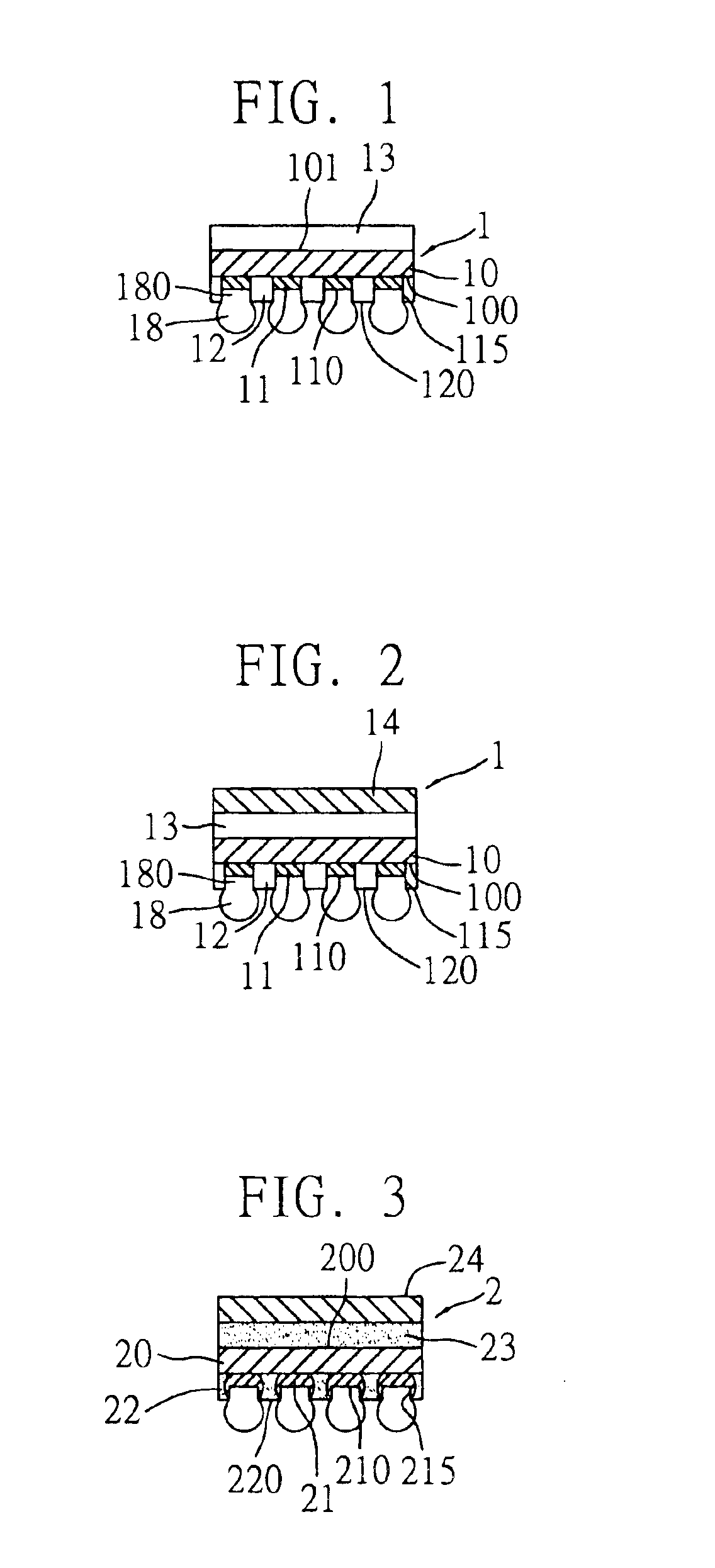

Light emitting device and manufacturing method thereof

ActiveUS20100320482A1Reduce product costImprove yield and reliabilityPlanar light sourcesPoint-like light sourceLight emitting device

A light emitting device comprises a substrate having a plurality of light emitting elements mounted thereon; a side wall structure having a partition wall portion separating a plurality of light emitting areas that each include at least one of the light emitting elements; and encapsulating resin filled in the light emitting areas to bury the light emitting elements therein. The side wall structure is separated by a space from the substrate at, at least, the partition wall portion so as to be in noncontact with the substrate, and the encapsulating resin is formed so as to integrally, continuously fill the light emitting areas and the space without producing any interface therein.

Owner:STANLEY ELECTRIC CO LTD

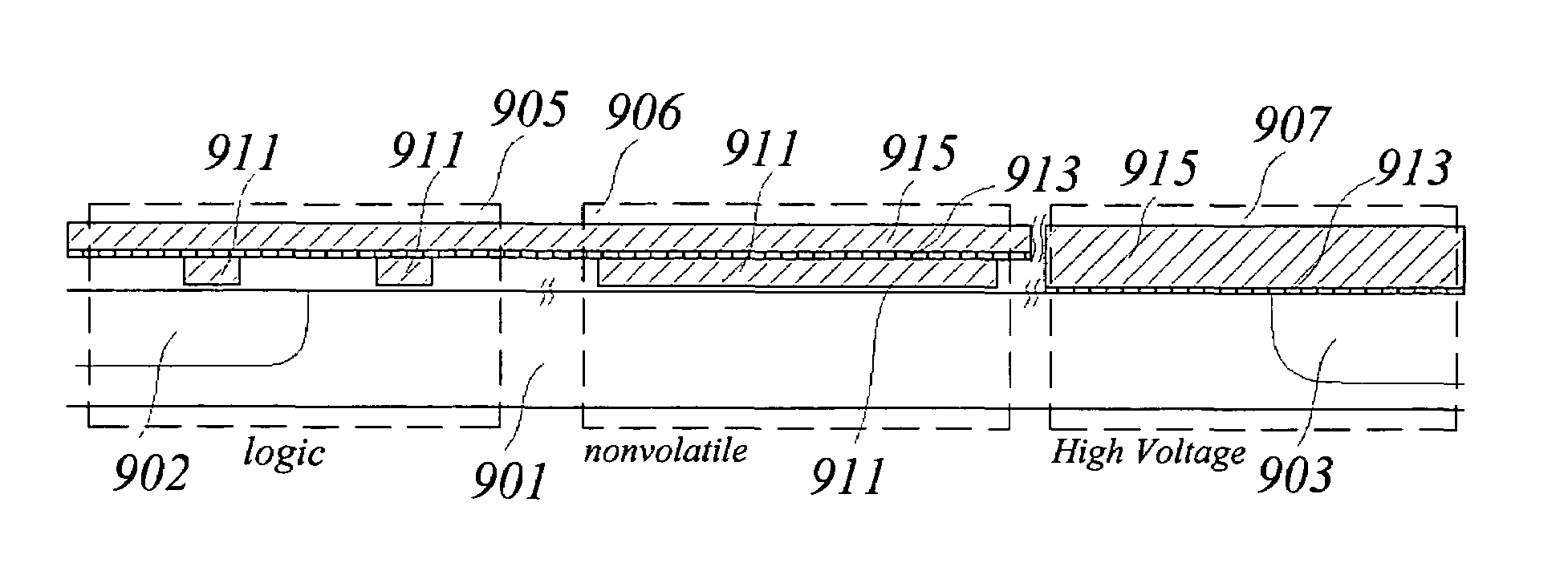

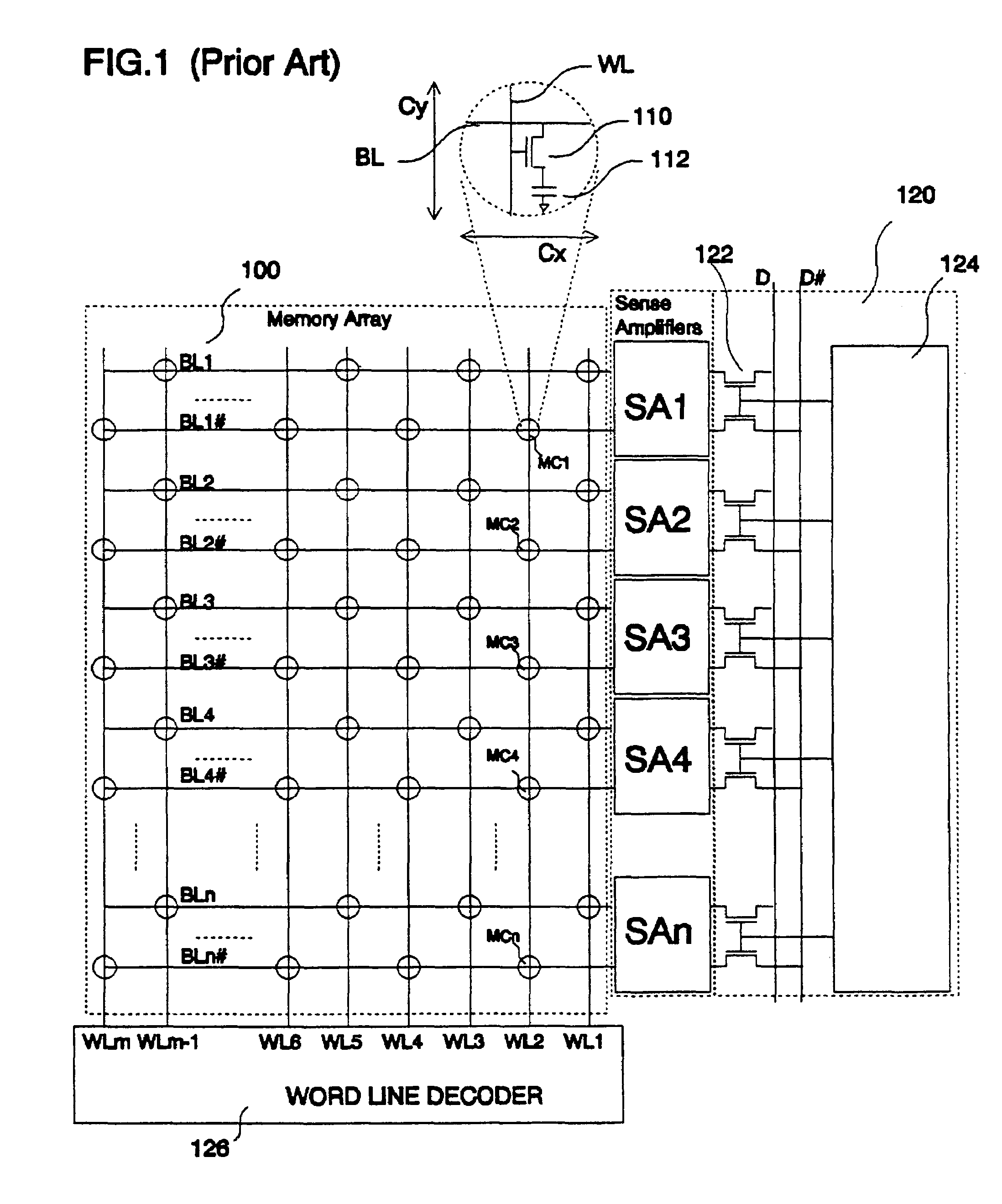

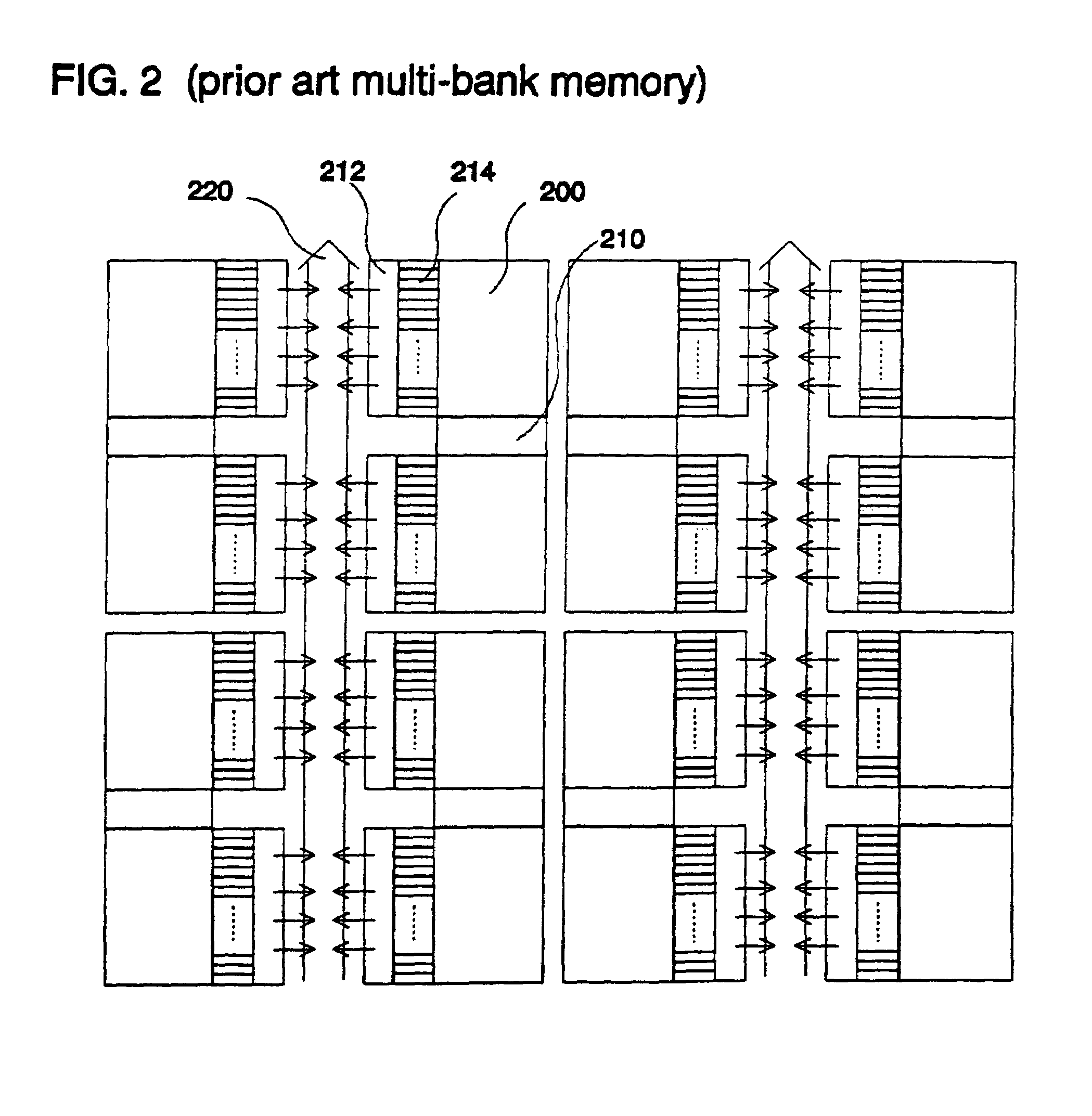

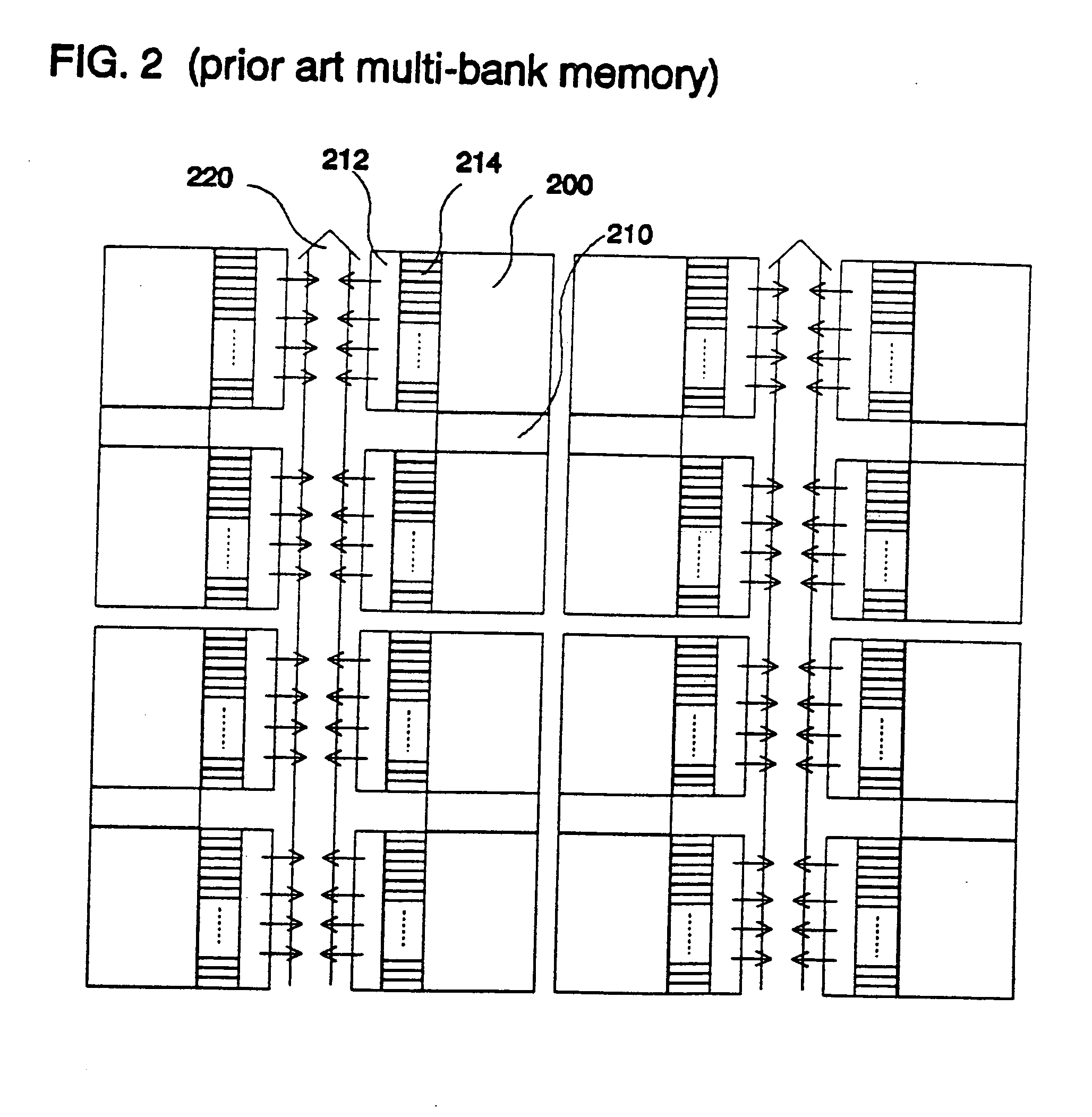

High performance embedded semiconductor memory devices with multiple dimension first-level bit-lines

InactiveUS20050133852A1Improve performanceReduce power consumptionTransistorSolid-state devicesBit lineInternal memory

A dynamic random access memory solves long-existing tight pitch layout problems using a multiple-dimensional bit line structure. Improvement in decoder design further reduces total area of this memory. A novel memory access procedure provides the capability to make internal memory refresh completely invisible to external users. By use of such memory architecture, higher performance DRAM can be realized without degrading memory density. The requirements for system support are also simplified significantly.

Owner:UNIRAM TECH

Flat panel display integrated with touch screen panel

InactiveUS20110216018A1Improve esd defectImprove yield and reliabilityNon-linear opticsInput/output processes for data processingDefect preventionFlat panel display

A touch screen panel is directly formed on an upper substrate of a flat panel display which provides a flat panel display integrated with the touch screen panel with an improved yield and reliability by improving ESD defect prevention due to the introduction of electrostatic by using a shield member covering sensing lines so that the sensing lines formed in a non-display region of the touch screen panel are not exposed to the outside.

Owner:SAMSUNG DISPLAY CO LTD

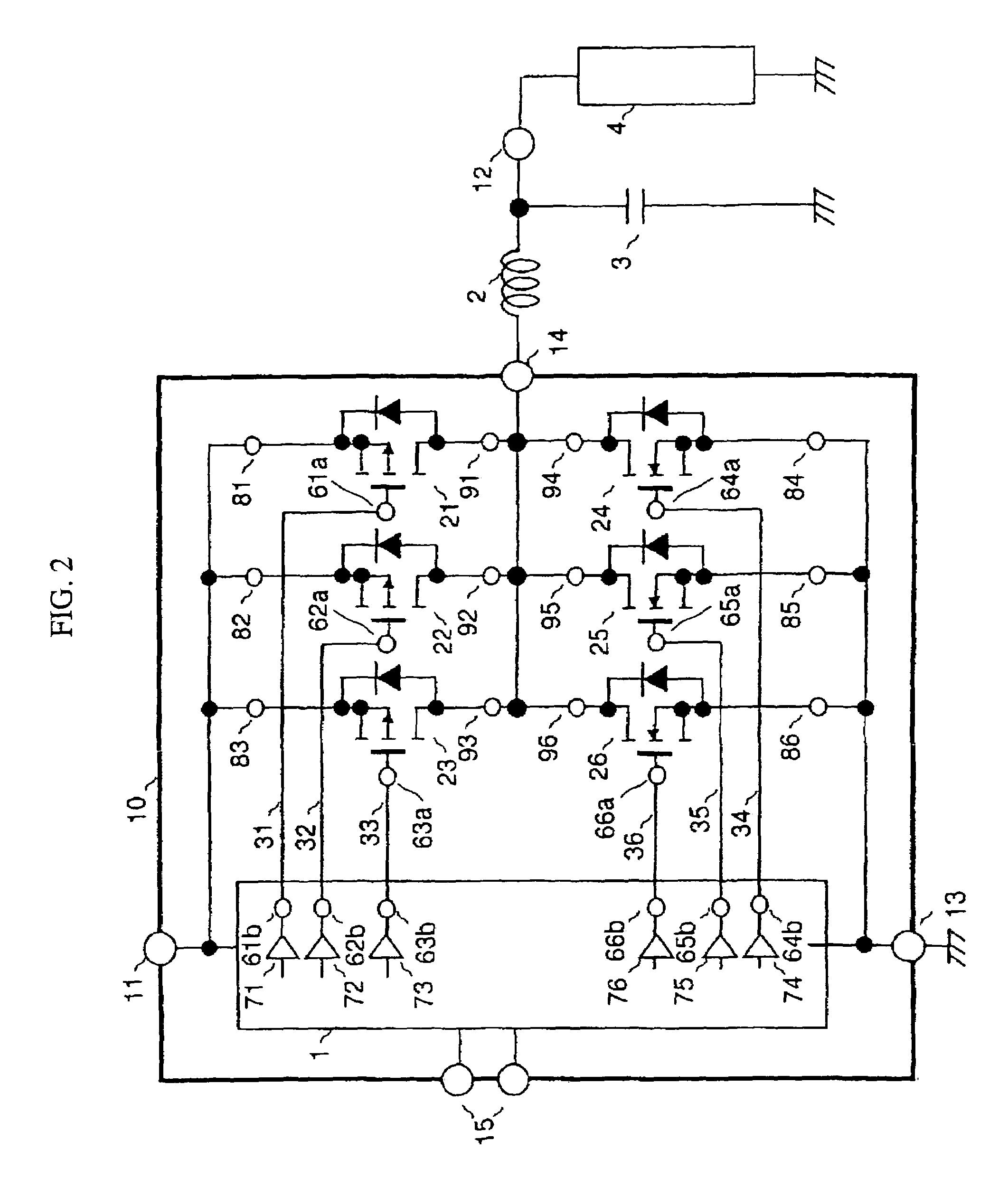

Display device

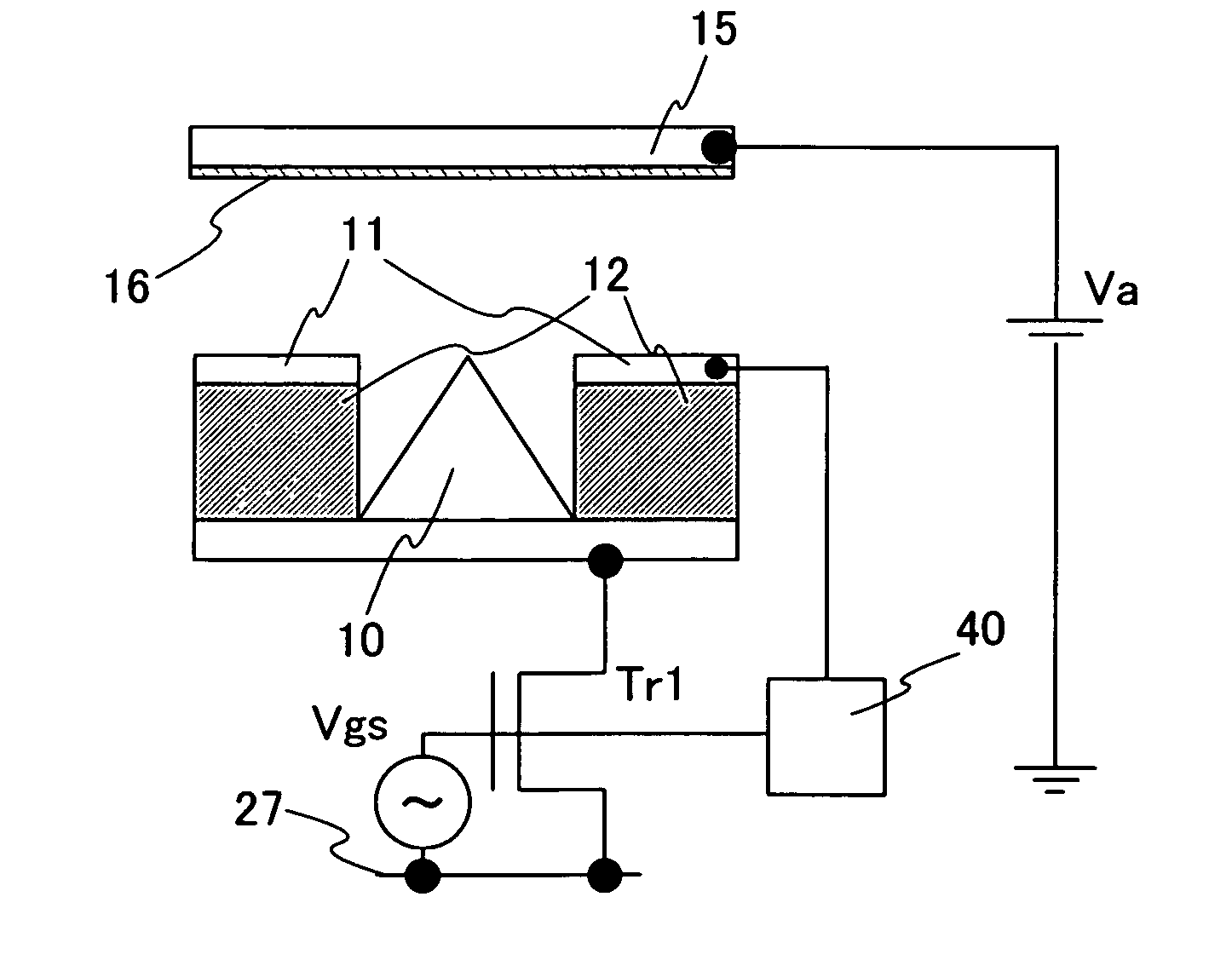

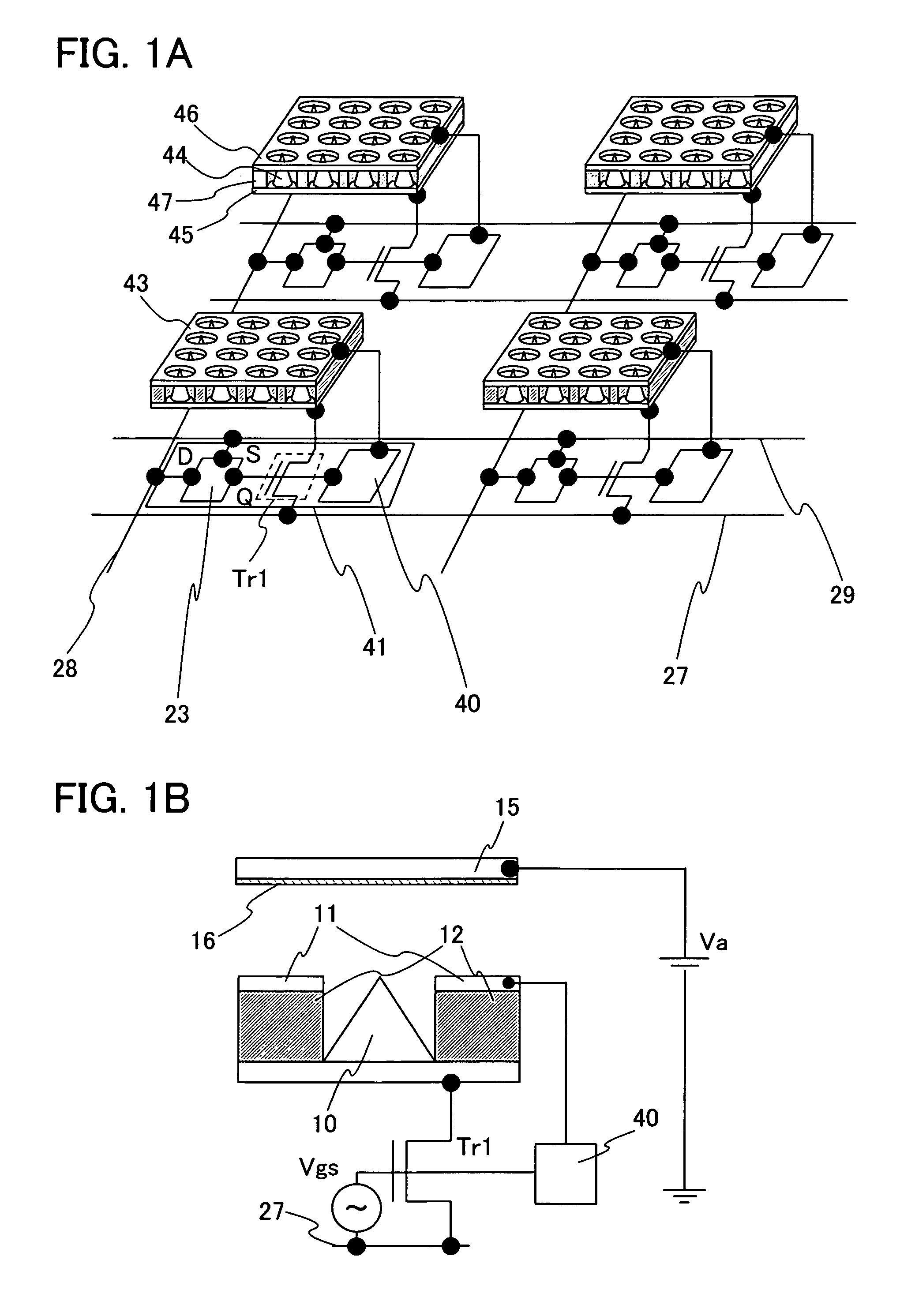

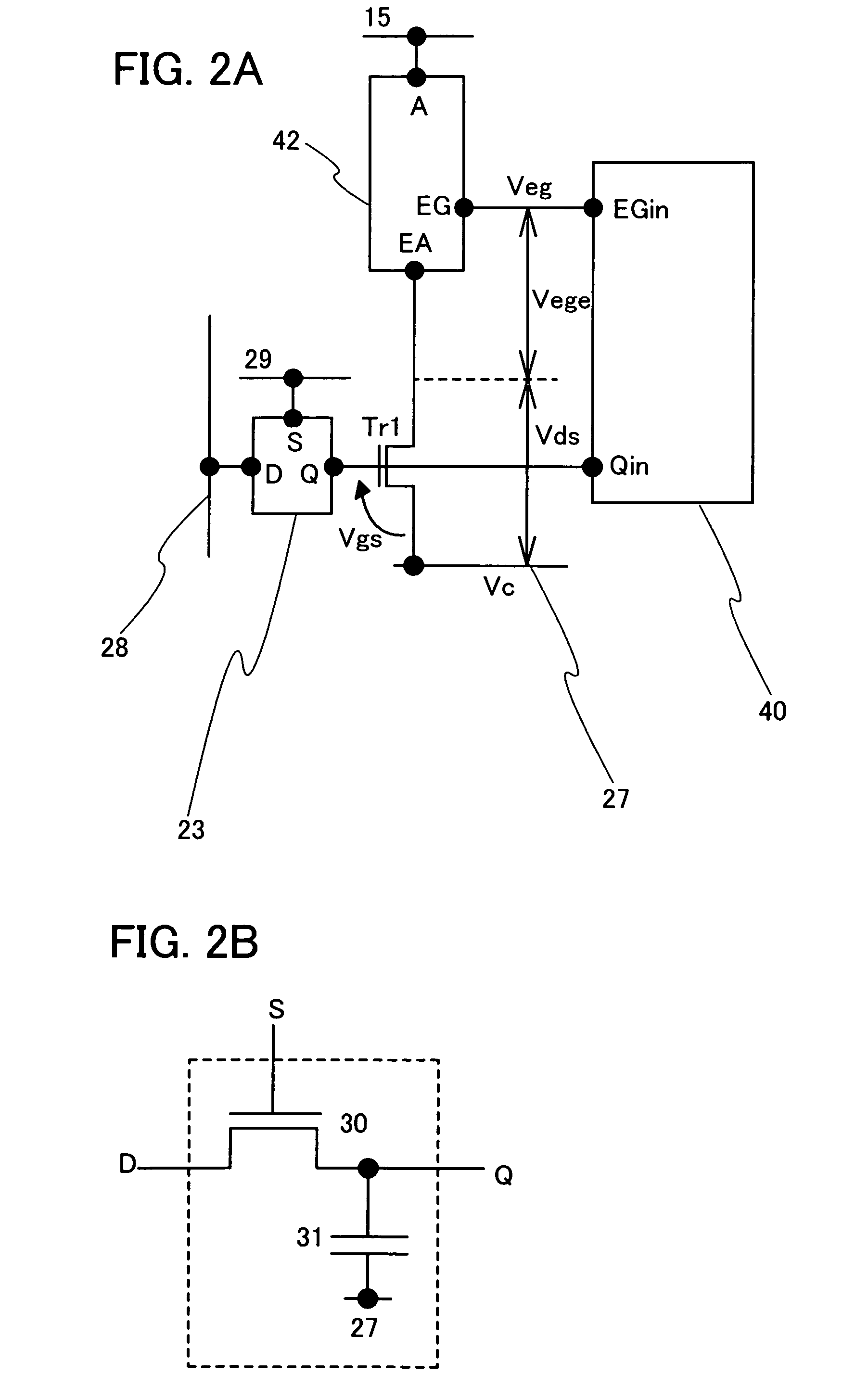

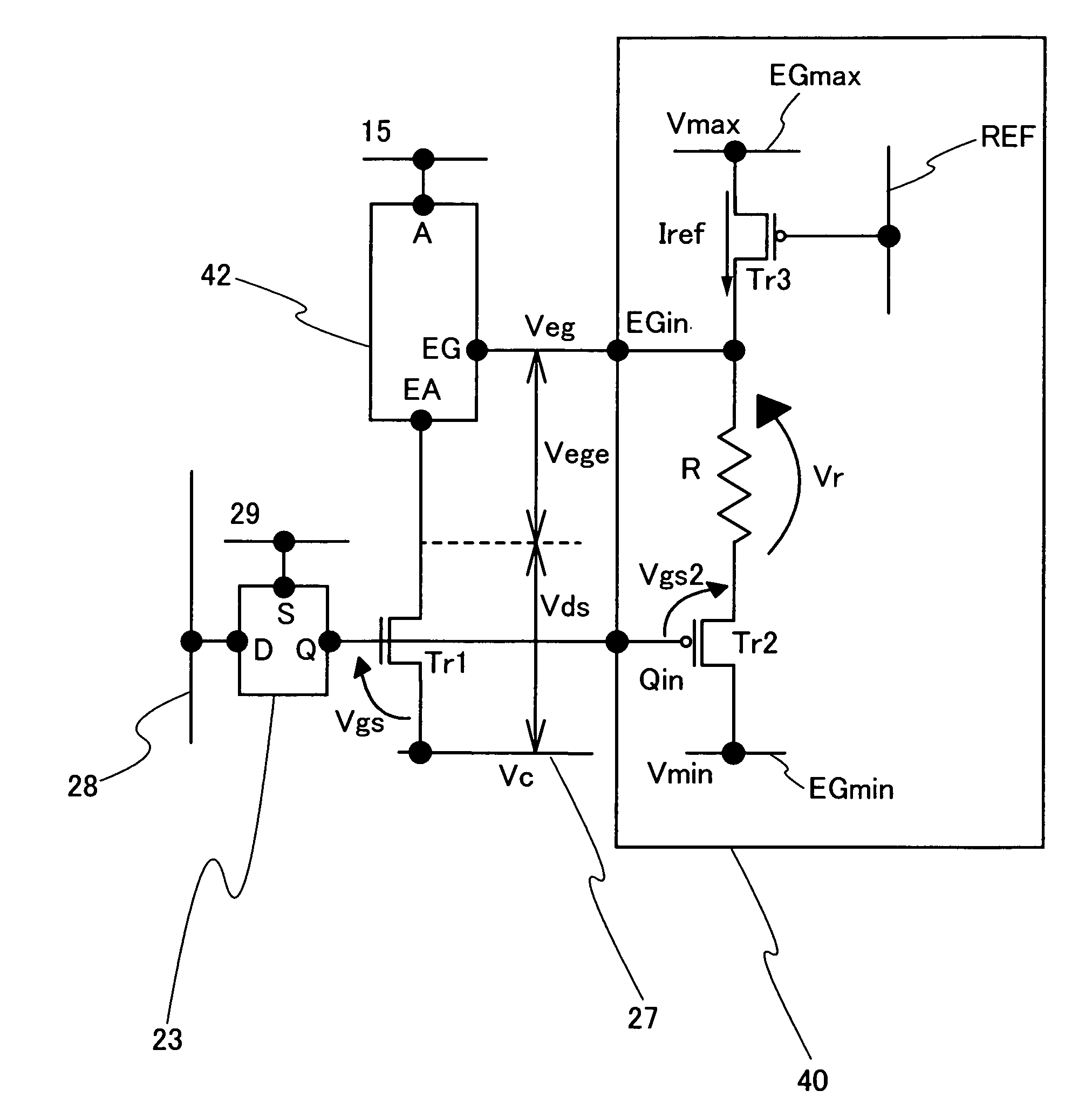

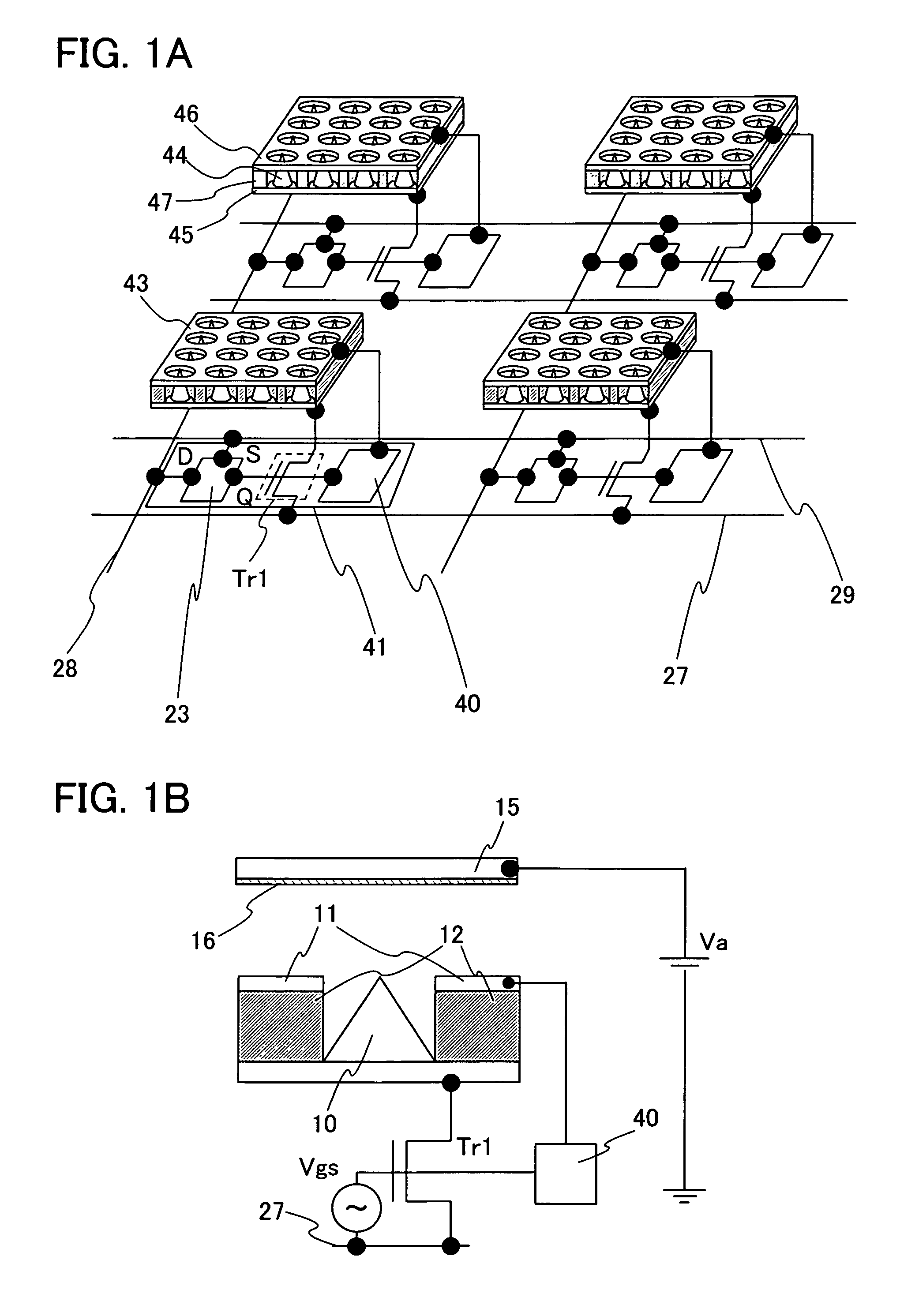

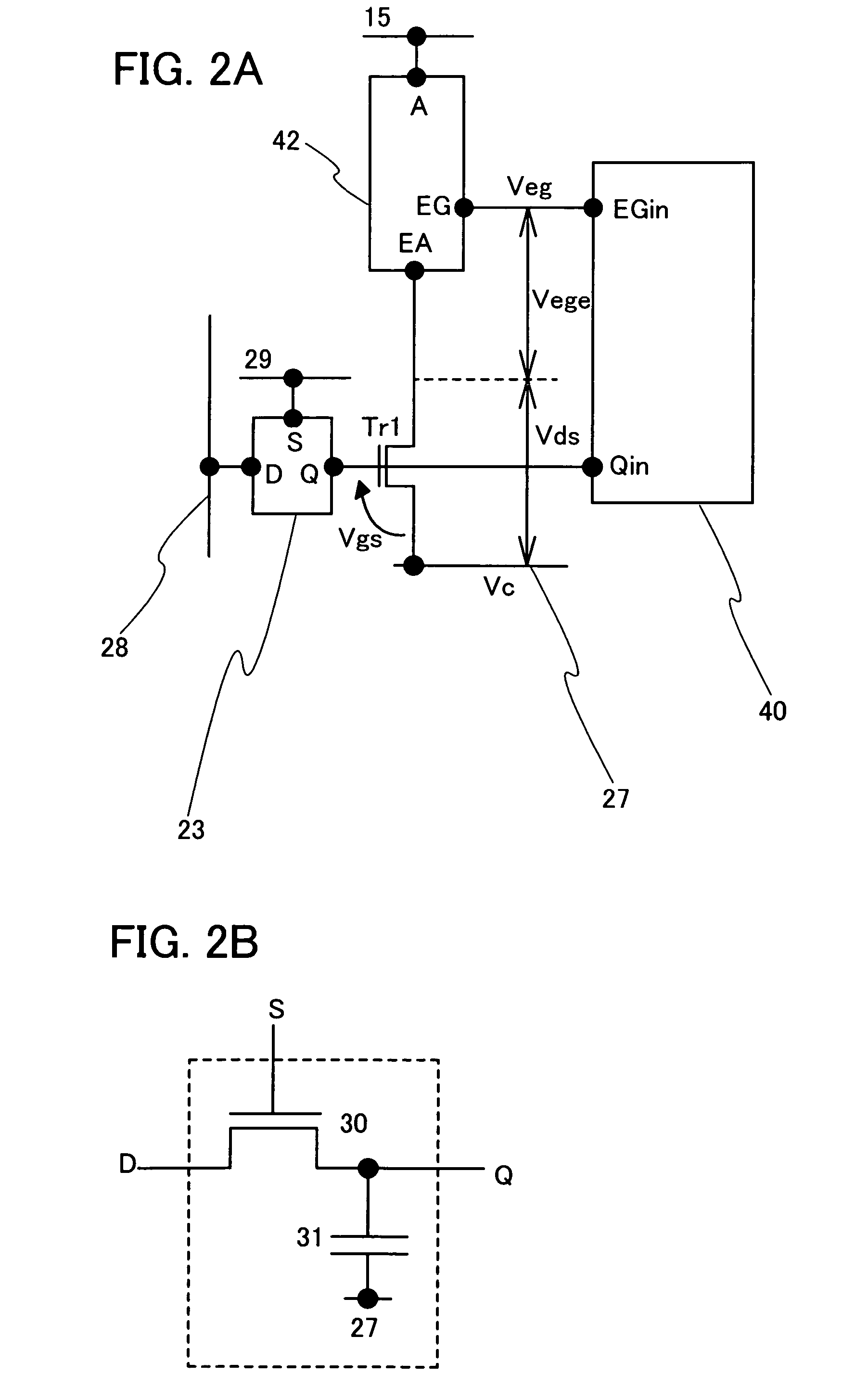

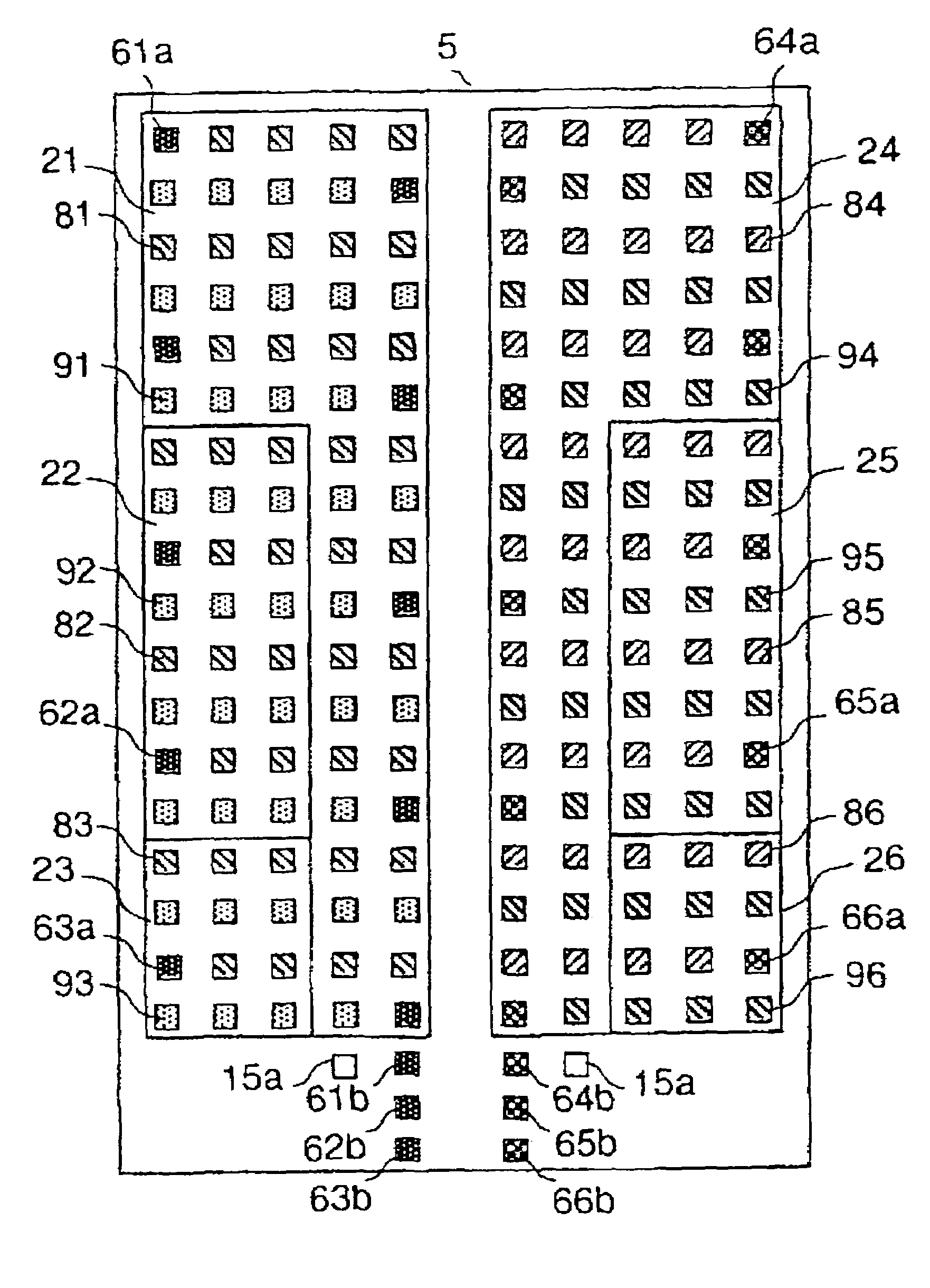

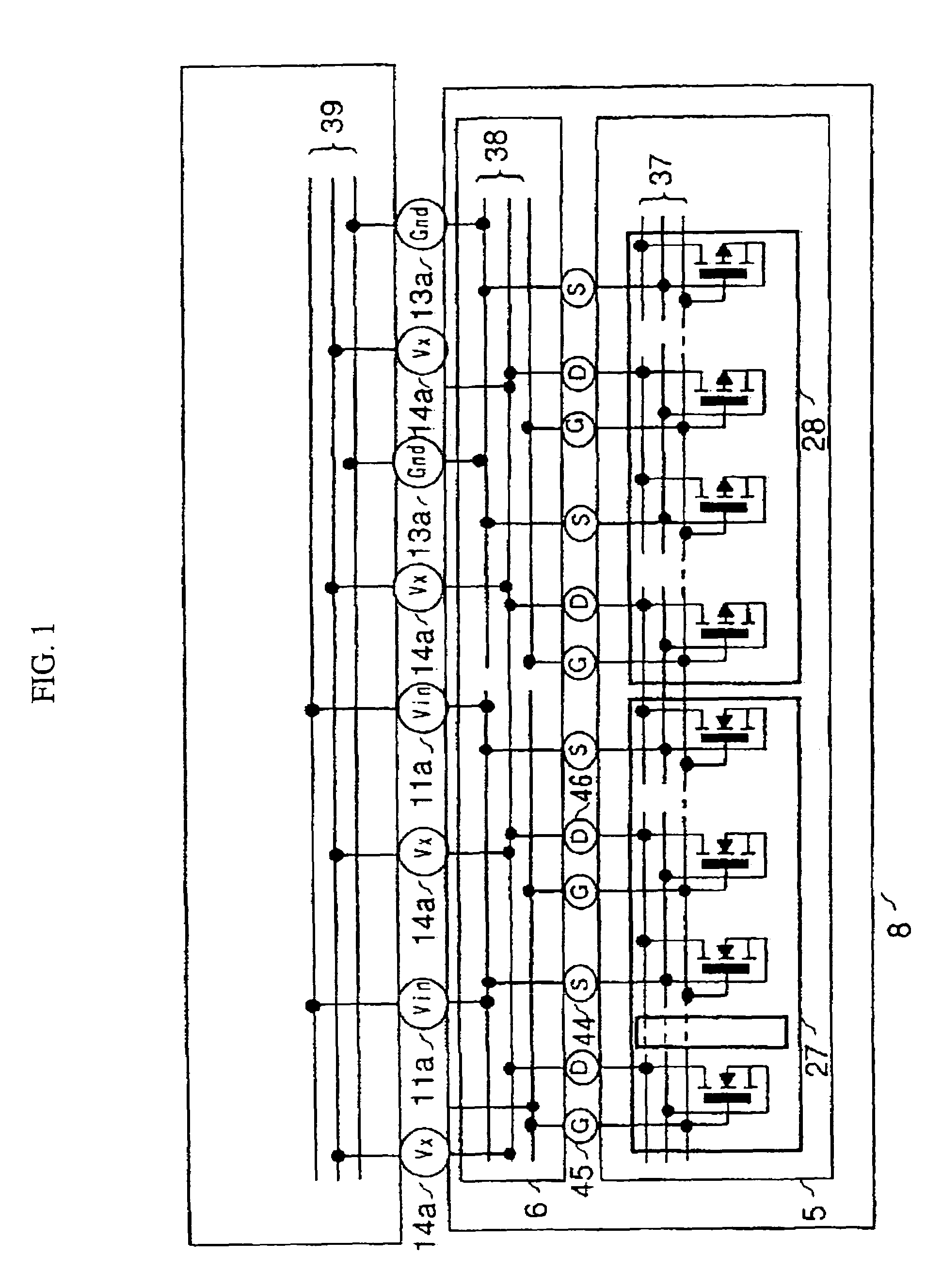

InactiveUS20070085778A1Reduce voltageSmall in luminance variationCathode ray tubes/electron beam tubesStatic indicating devicesActive matrixLow voltage

To provide a highly reliable display device whose electrical element is applied with a low voltage. The display device is an active matrix FED display device whose pixel has an individual extraction gate electrode, an emitter array, a driving transistor which is connected to the emitter array in series, a potential control circuit which controls the potential of the extraction gate electrode, and a circuit which includes a switching element and a voltage holding element. By varying the potential of the extraction gate electrode in accordance with Vgs of the driving transistor, the active matrix driving method is performed by connecting a driving transistor to the emitter array in series and voltage which is applied to the driving transistor can be reduced.

Owner:SEMICON ENERGY LAB CO LTD

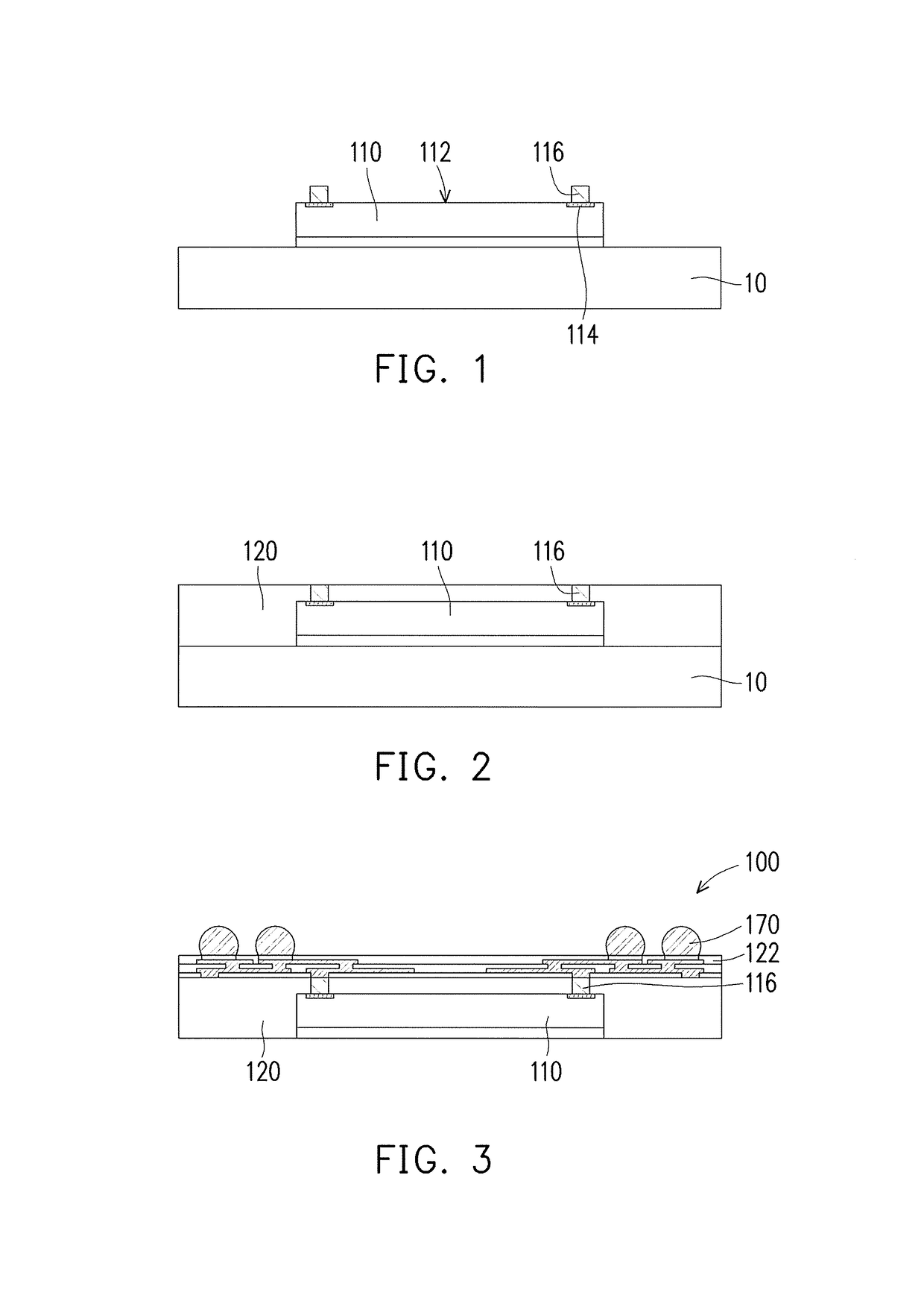

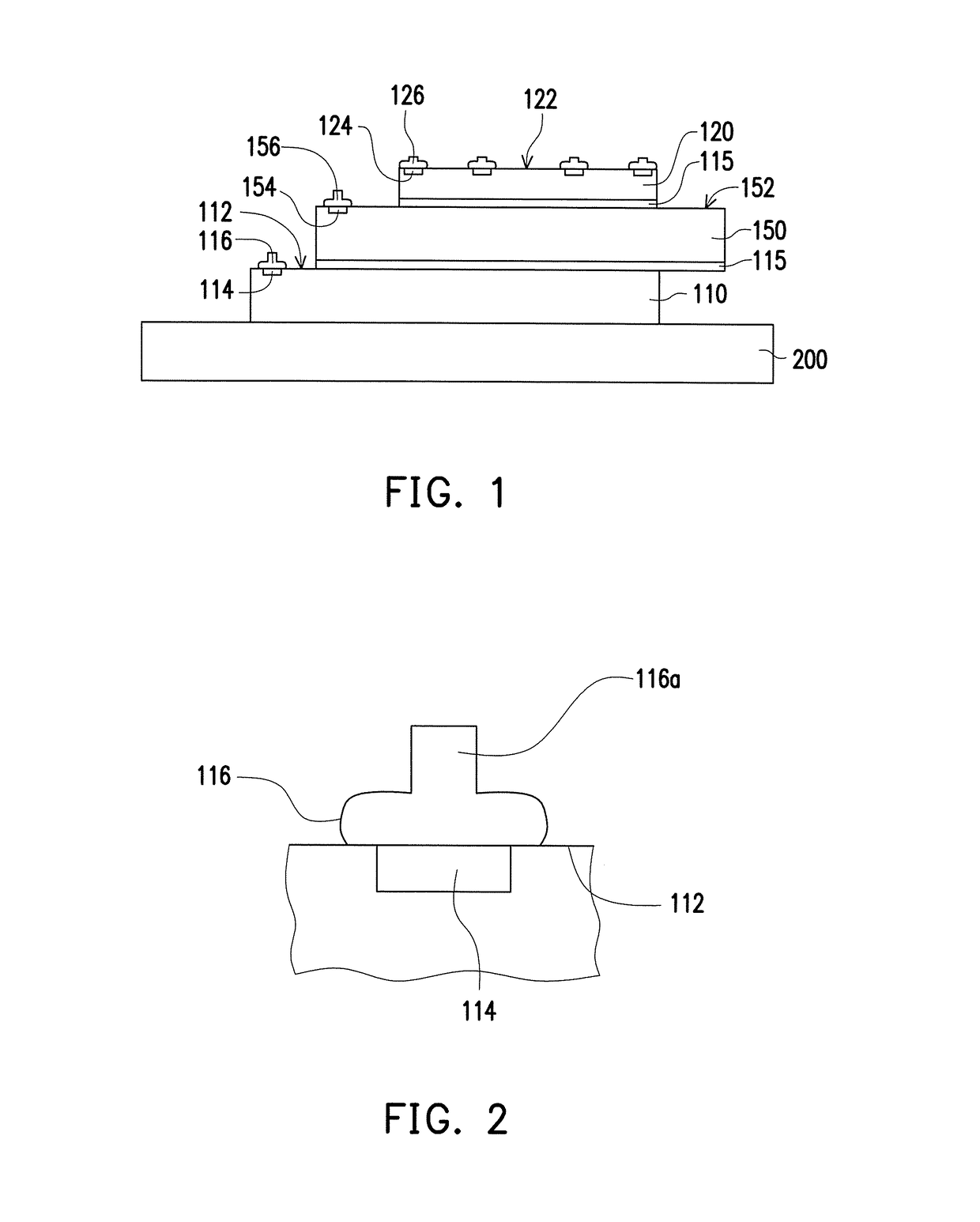

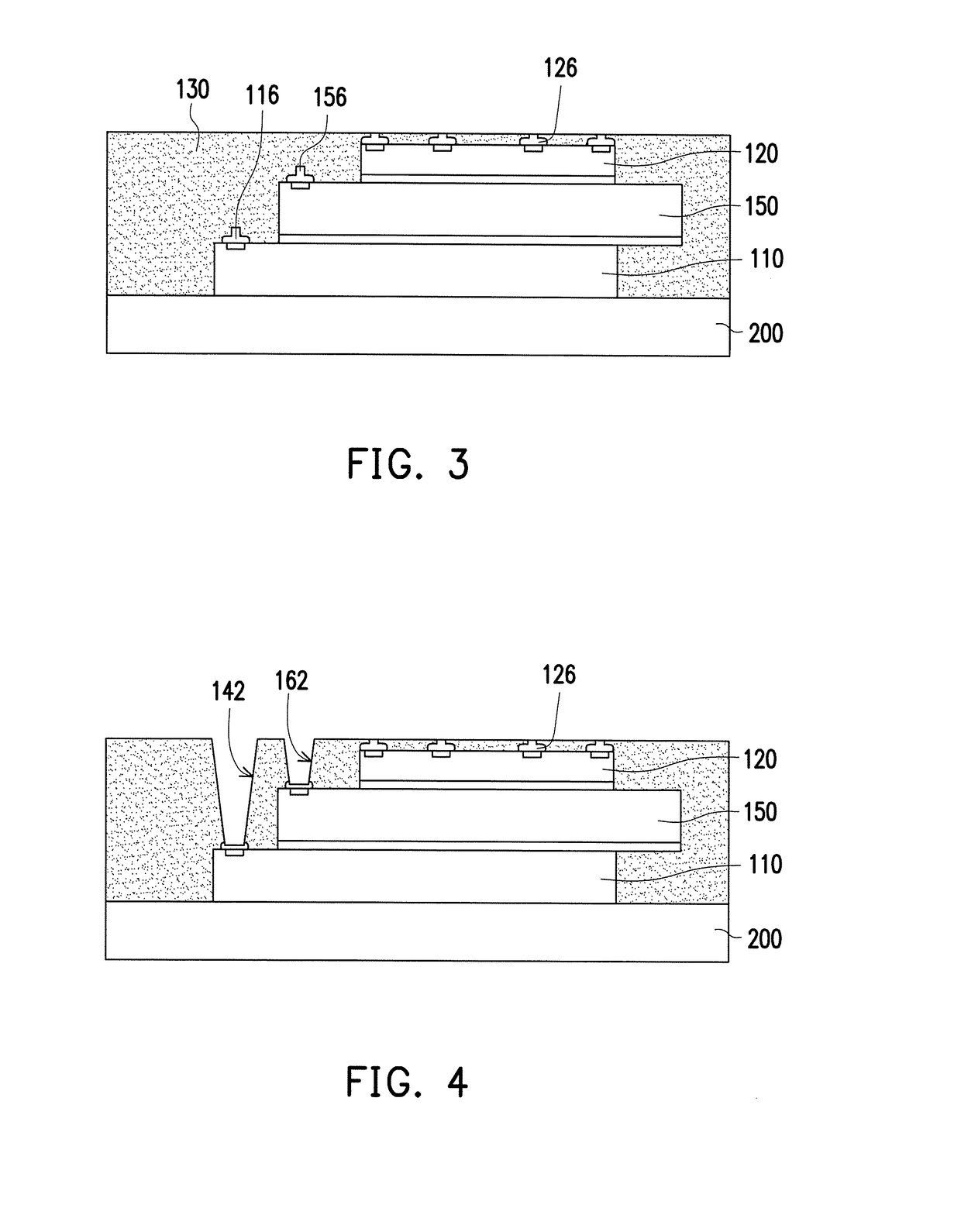

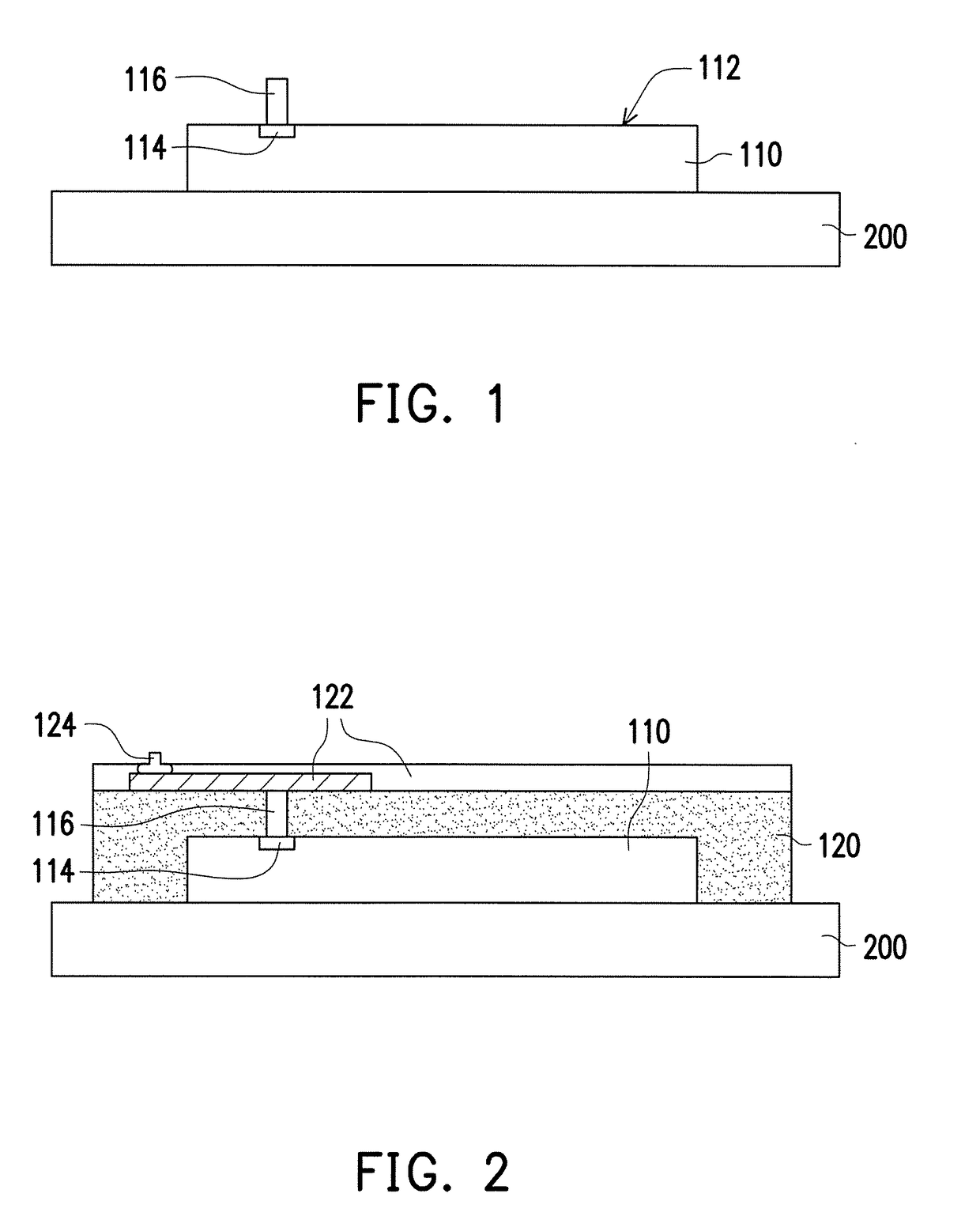

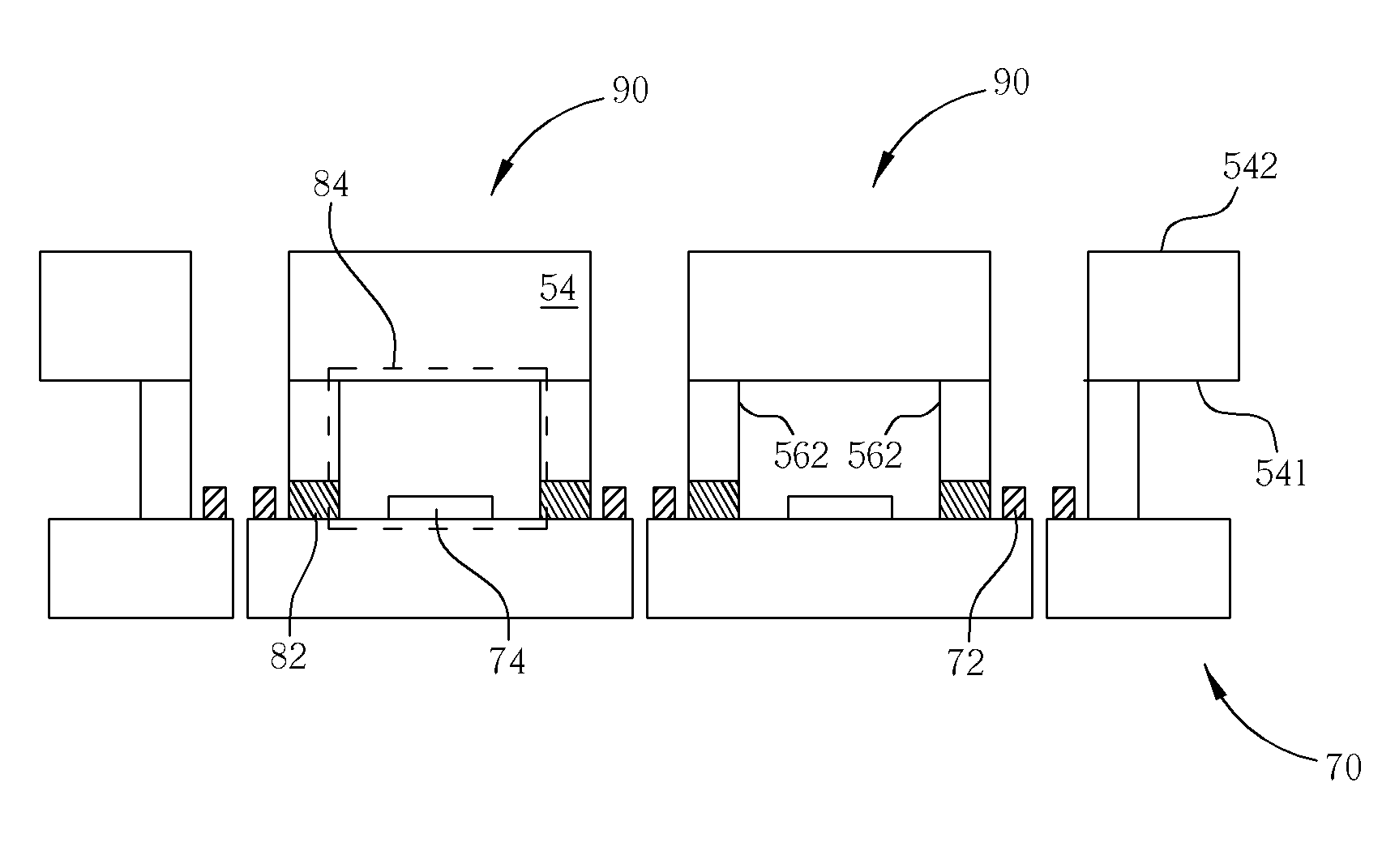

Chip package structure with conductive pillar and a manufacturing method thereof

ActiveUS10157828B2Reduce thicknessProduction cost be reduceSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerSemiconductor components

A chip package structure includes a semiconductor component, a plurality of conductive pillars, an encapsulant and a redistribution layer. The semiconductor component includes a plurality of pads. The conductive pillars are disposed on the pads, wherein each of the conductive pillars is a solid cylinder including a top surface and a bottom surface, and a diameter of the top surface is substantially the same as a diameter of the bottom surface. The encapsulant encapsulates the semiconductor component and the conductive pillars, wherein the encapsulant exposes the top surface of each of the conductive pillars. The redistribution layer is disposed on the encapsulant and electrically connected to the conductive pillars.

Owner:POWERTECH TECHNOLOGY

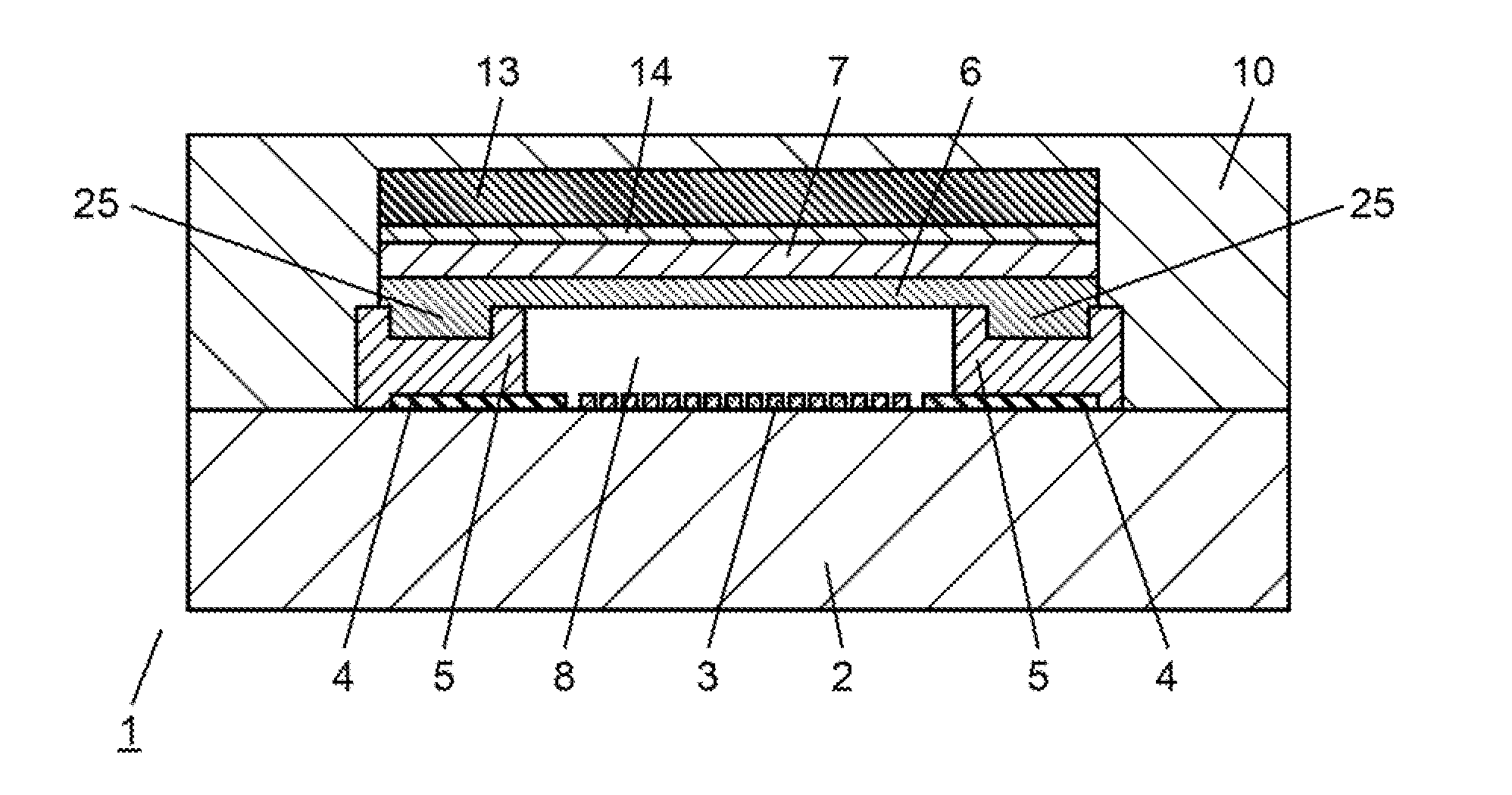

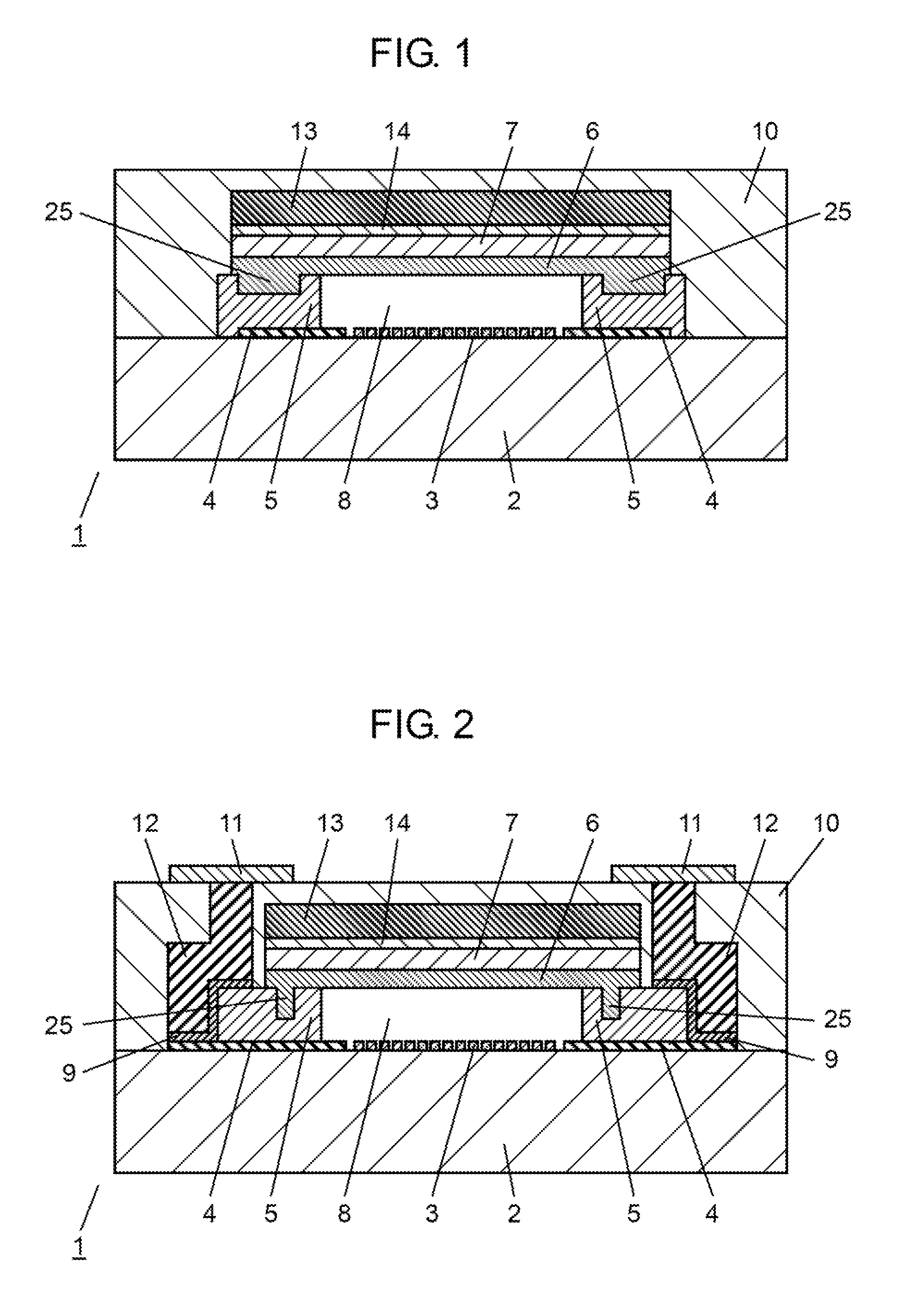

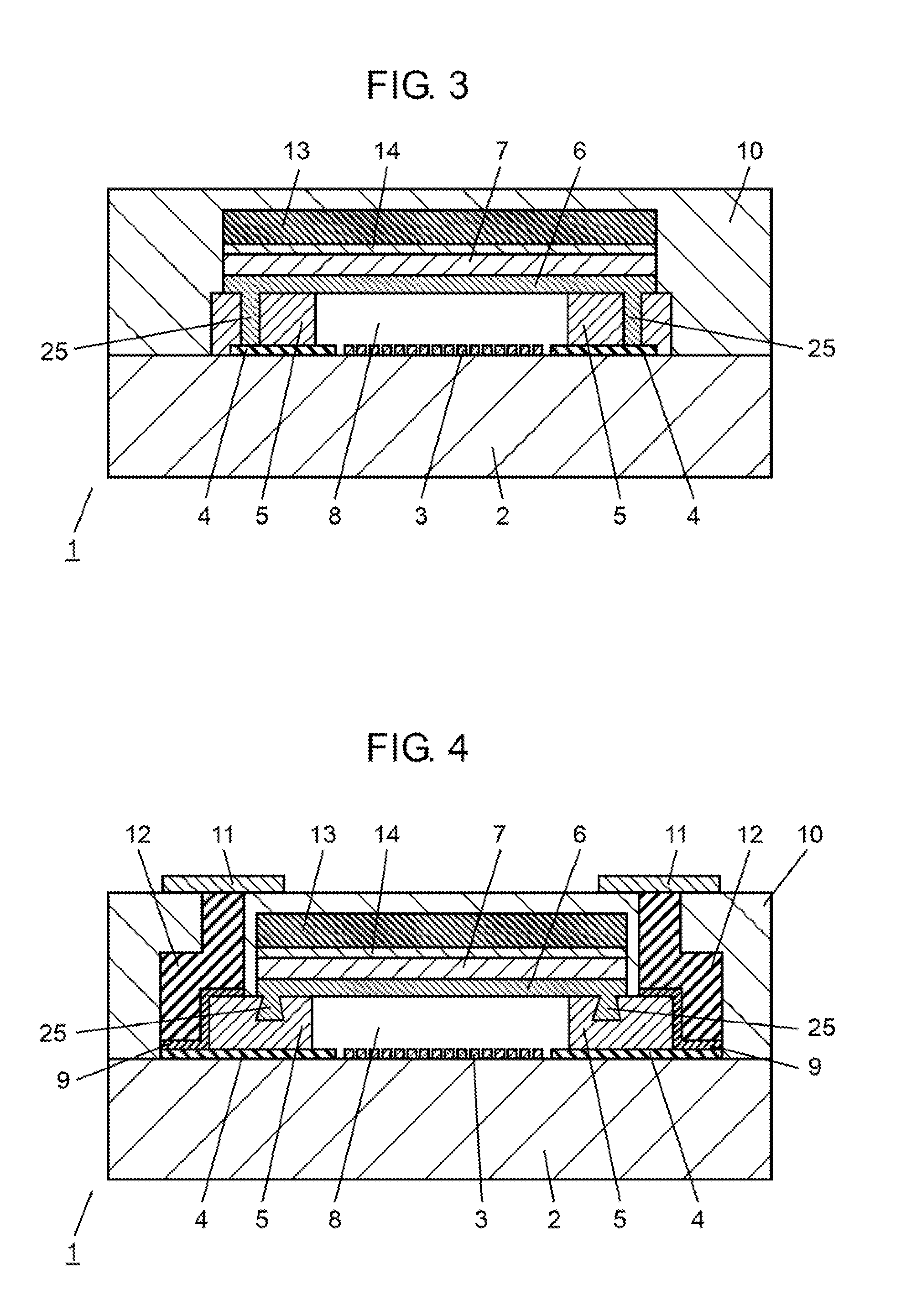

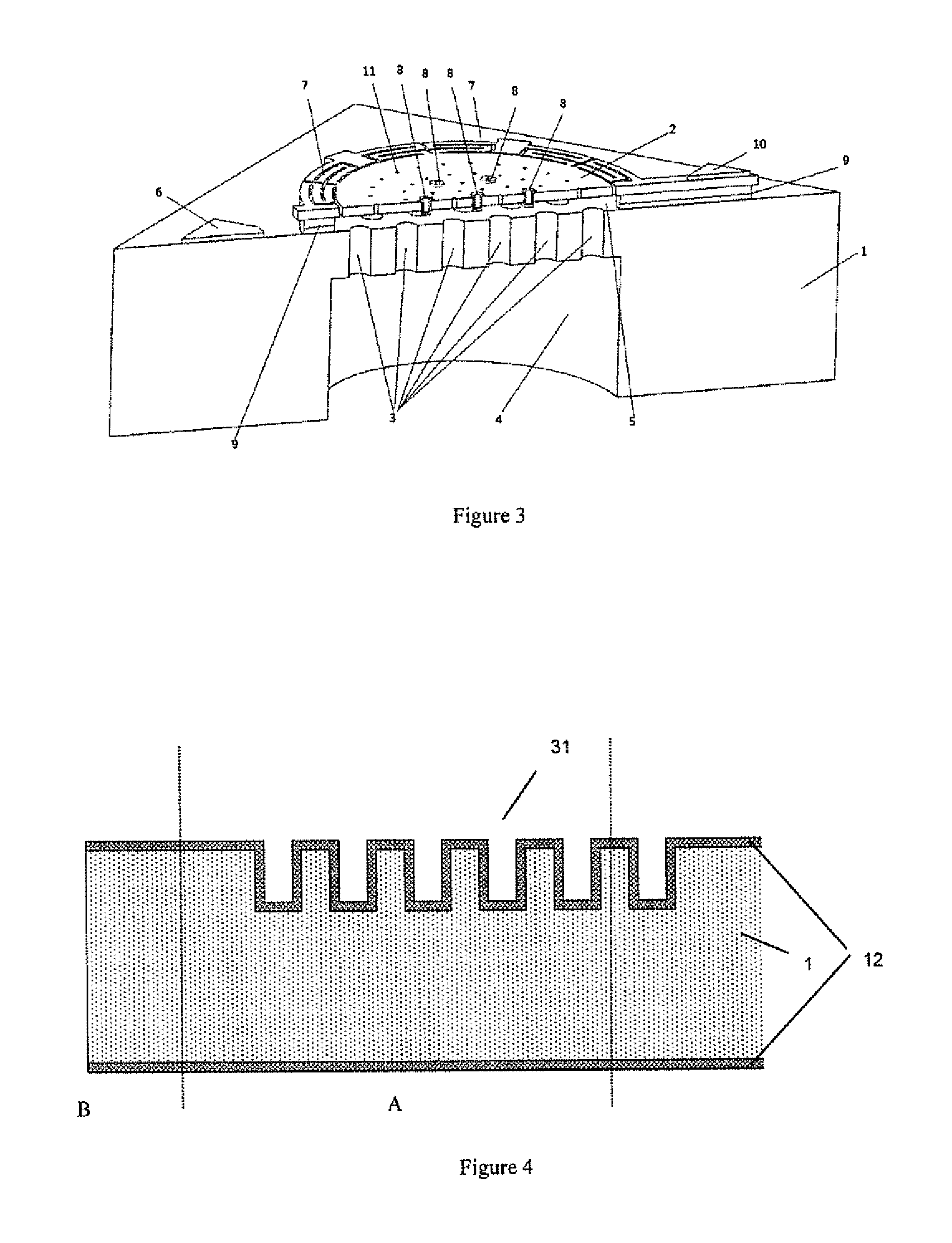

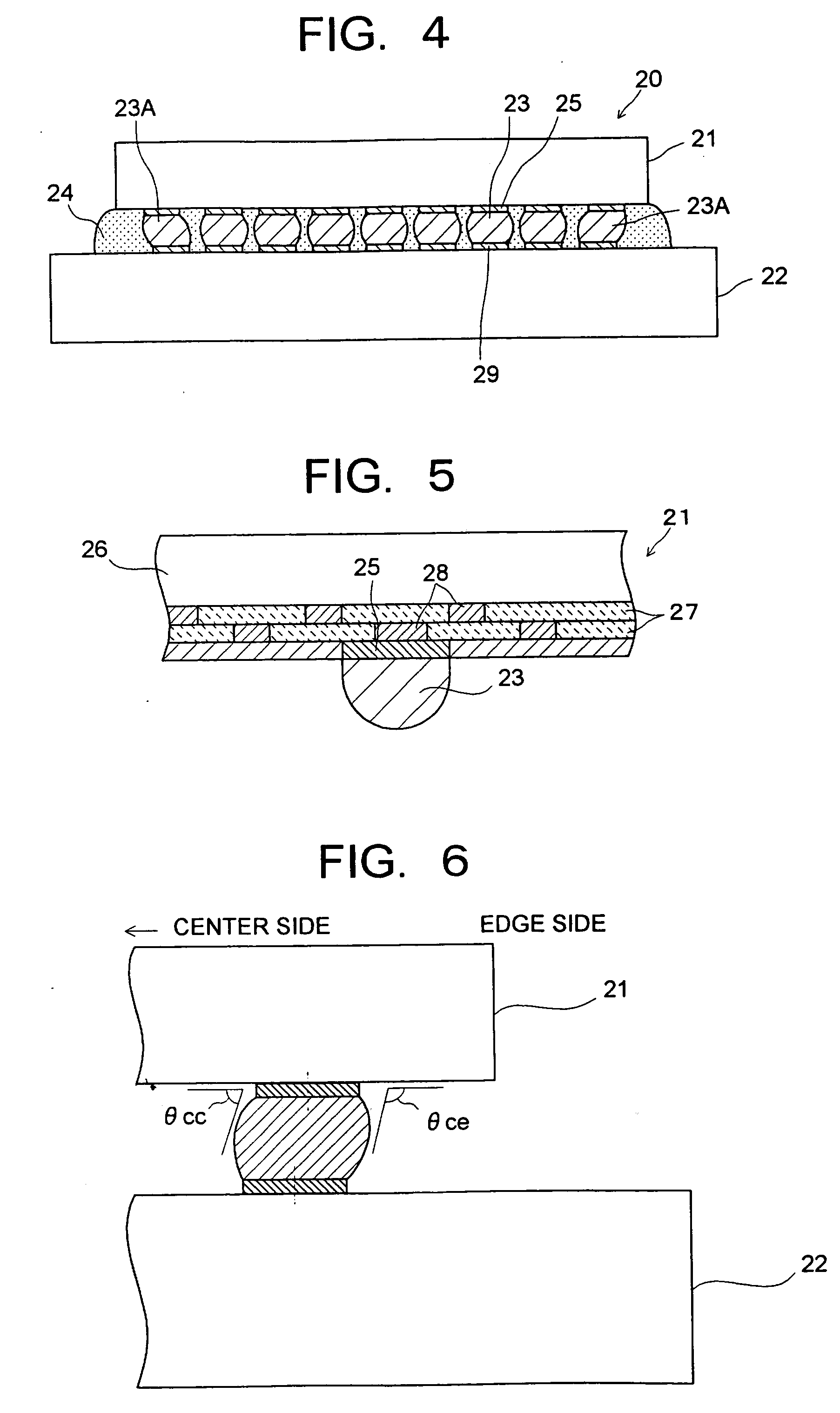

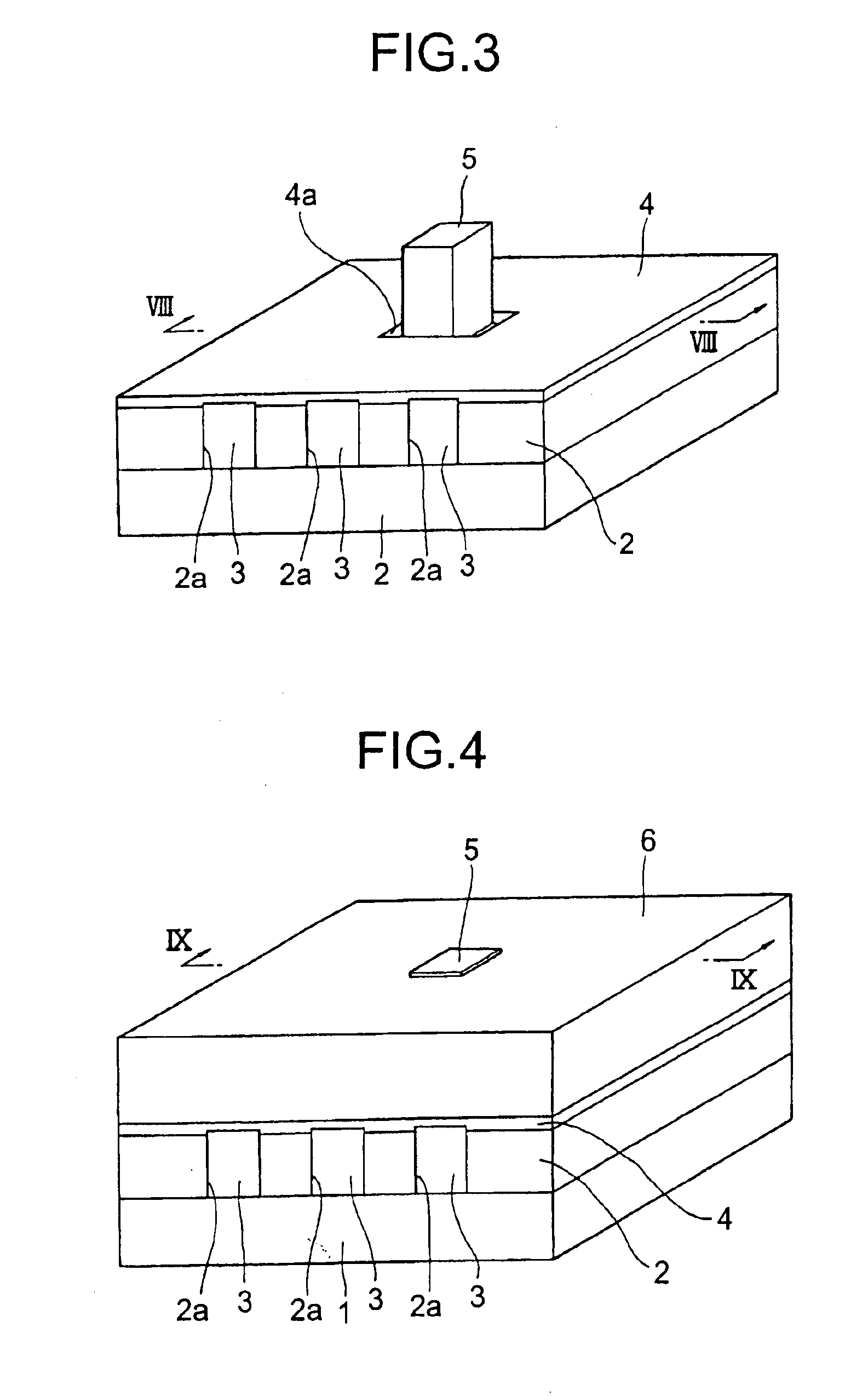

Acoustic wave element and electronic device including the same

ActiveUS20120086309A1Reduce protrusionHigh strengthImpedence networksPiezoelectric/electrostriction/magnetostriction machinesElectricityAdhesive

An acoustic wave element of the present invention includes a piezoelectric substrate, an IDT electrode, a sidewall, a lid, and an adhesive layer. The IDT electrode is provided on the piezoelectric substrate. The sidewall is provided around the IDT electrode above the piezoelectric substrate. The lid is provided above the sidewall so as to cover a space above the IDT electrode. The adhesive layer is made of an adhesive provided between the lid and the sidewall. The top surface of the sidewall has a groove. The groove is filled with an adhesive, which reduces the protrusion amount of the adhesive.

Owner:SKYWORKS PANASONIC FILTER SOLUTIONS JAPAN

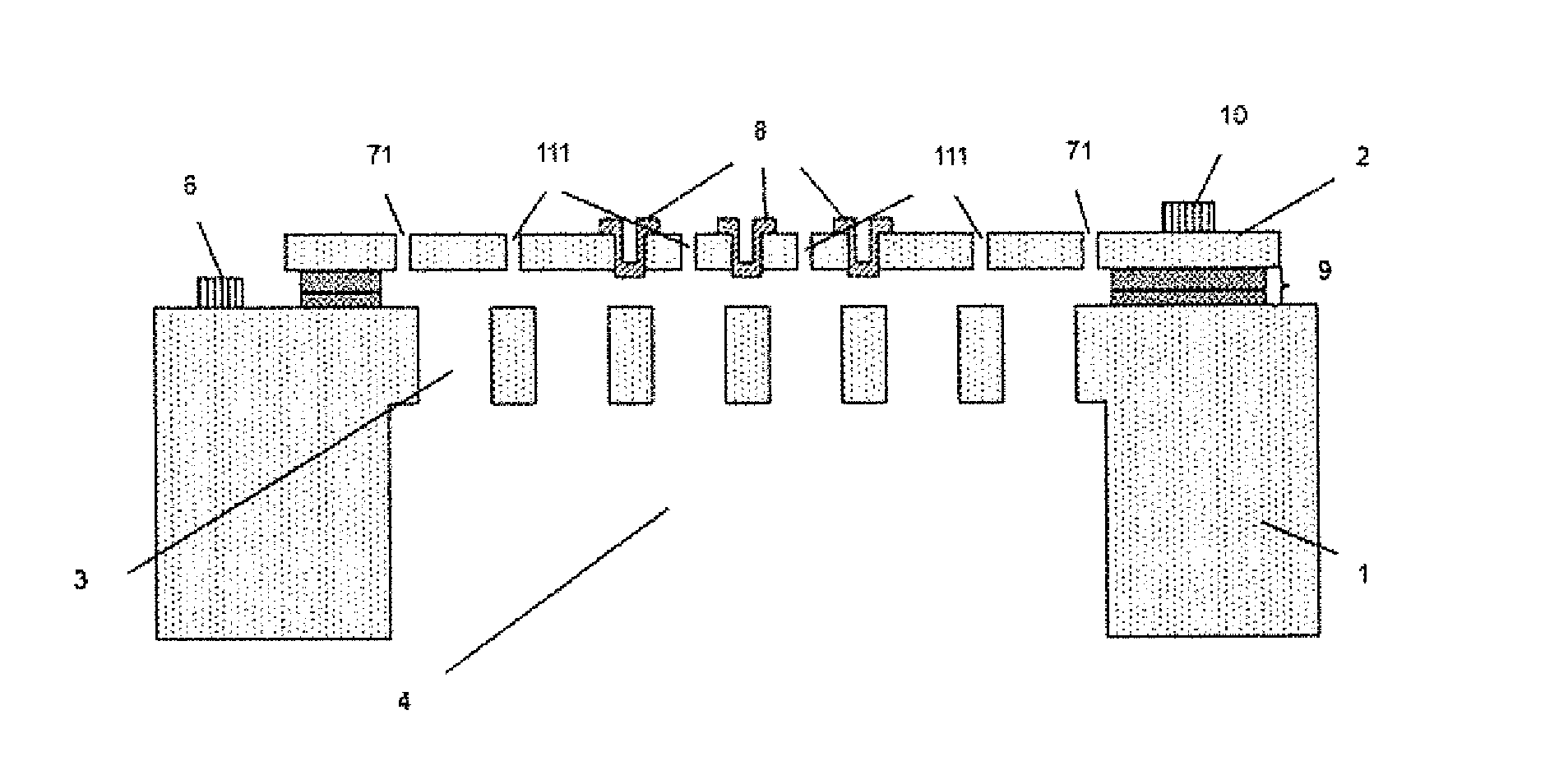

MEMS silicone microphone and manufacturing method thereof

ActiveUS20160304337A1Simple manufacturing processHigh sensitivityMicrophonesDecorative surface effectsMems microphoneOptoelectronics

This invention relates to the field of silicon microphone technology, more specifically, to a method for fabricating a MEMS microphone using multi-cavity SOT wafer by Si-Si fusion bonding technology, which comprises a multi-cavity silicon backplate and a monocrystalline silicon diaphragm, both are separated with a layer of silicon dioxide to form the capacitor of the MEMS microphone. The monocrystalline silicon diaphragm has advantages such as low residual stress and good uniformity, which increase the yield and sensitivity of MEMS silicon microphone; the diaphragm comprises tiny release-assistant holes, spring structures with anchors and bumps which can quickly release the residual stress and reduce the probability of stiction between the backplate and the silicon diaphragm. This structure will further improve yield and reliability of MEMS microphone. Therefore, this invention provides simple and reliable process for fabricating MEMS microphones with high sensitivity, good uniformity, excellent reliability and high yield.

Owner:MICROLINK SENSTECH SHANGHAI LTD

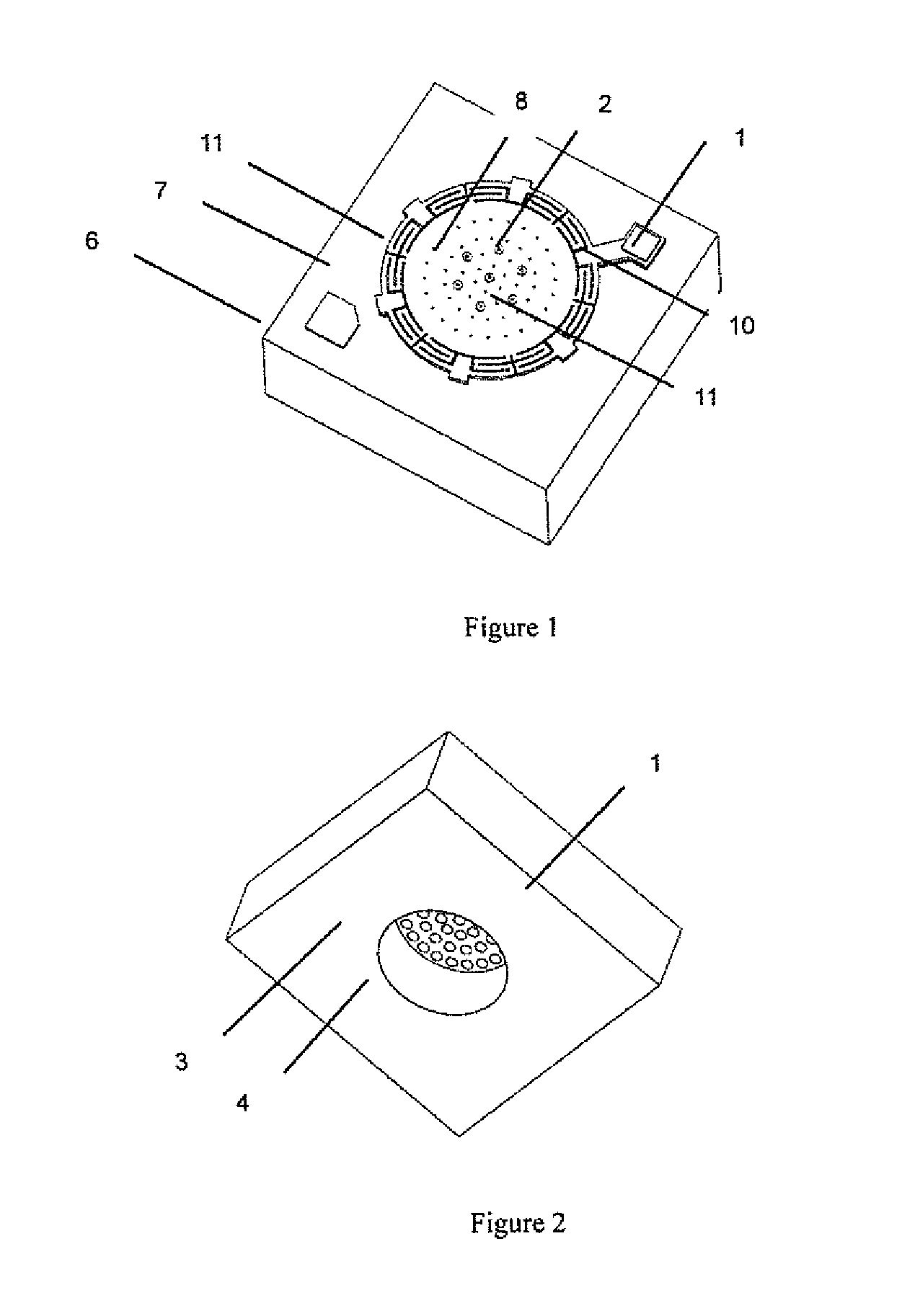

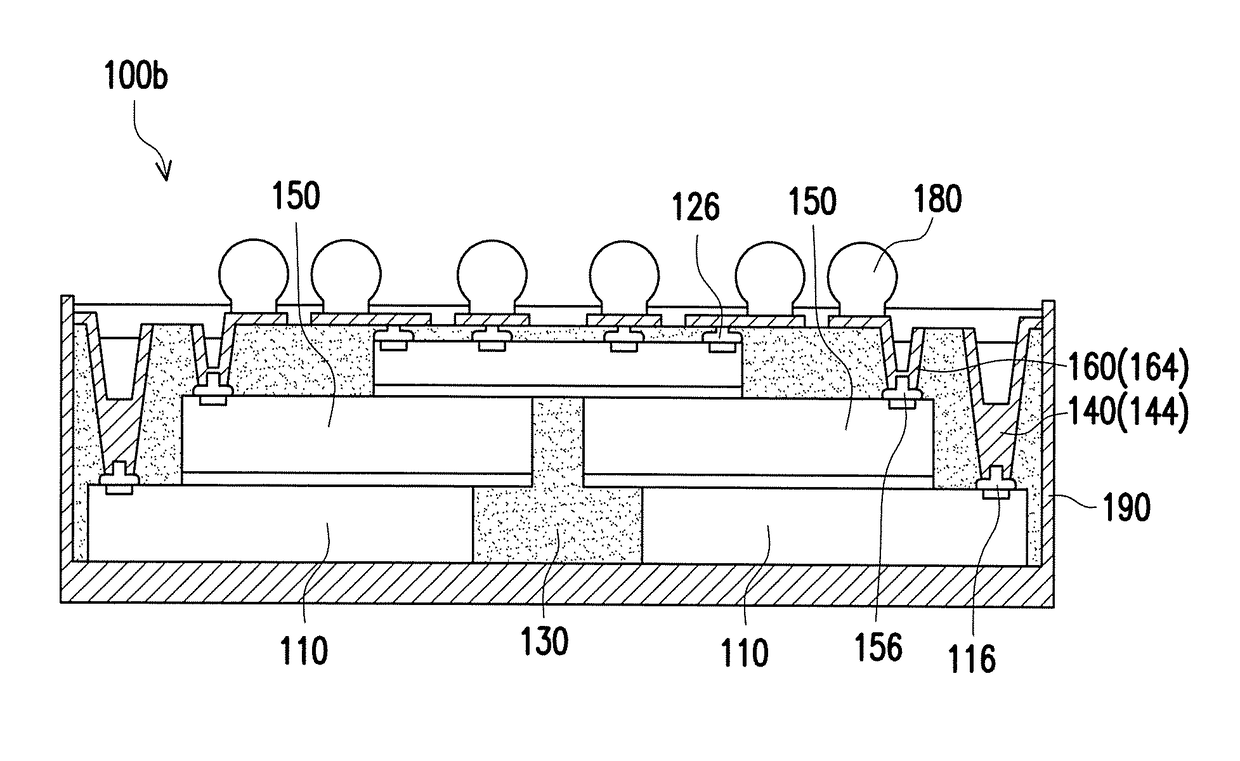

Photoelectric device, method of fabricating the same and packaging apparatus for the same

InactiveUS20110068358A1Improve reliabilityHigh yieldSolid-state devicesSemiconductor/solid-state device manufacturingMetallurgyTransfer molding

A method for fabricating a photoelectric device initially provides a ceramic substrate comprising a thermal dissipation layer on a bottom layer of the ceramic substrate, an electrode layer on the top surface of the ceramic substrate, and a reflective structure in cavities of the ceramic substrate. Next, a plurality of photoelectric dies is disposed on the top surface of the ceramic substrate. Then, a first packaging layer is formed on the top surfaces of the photoelectric dies. Next, the ceramic substrate is placed between an upper mold and a lower mold. Finally, a plurality of lenses is formed on the top surface of the first packaging layer by using an injection molding technique or a transfer molding technique.

Owner:ADVANCED OPTOELECTRONICS TECH

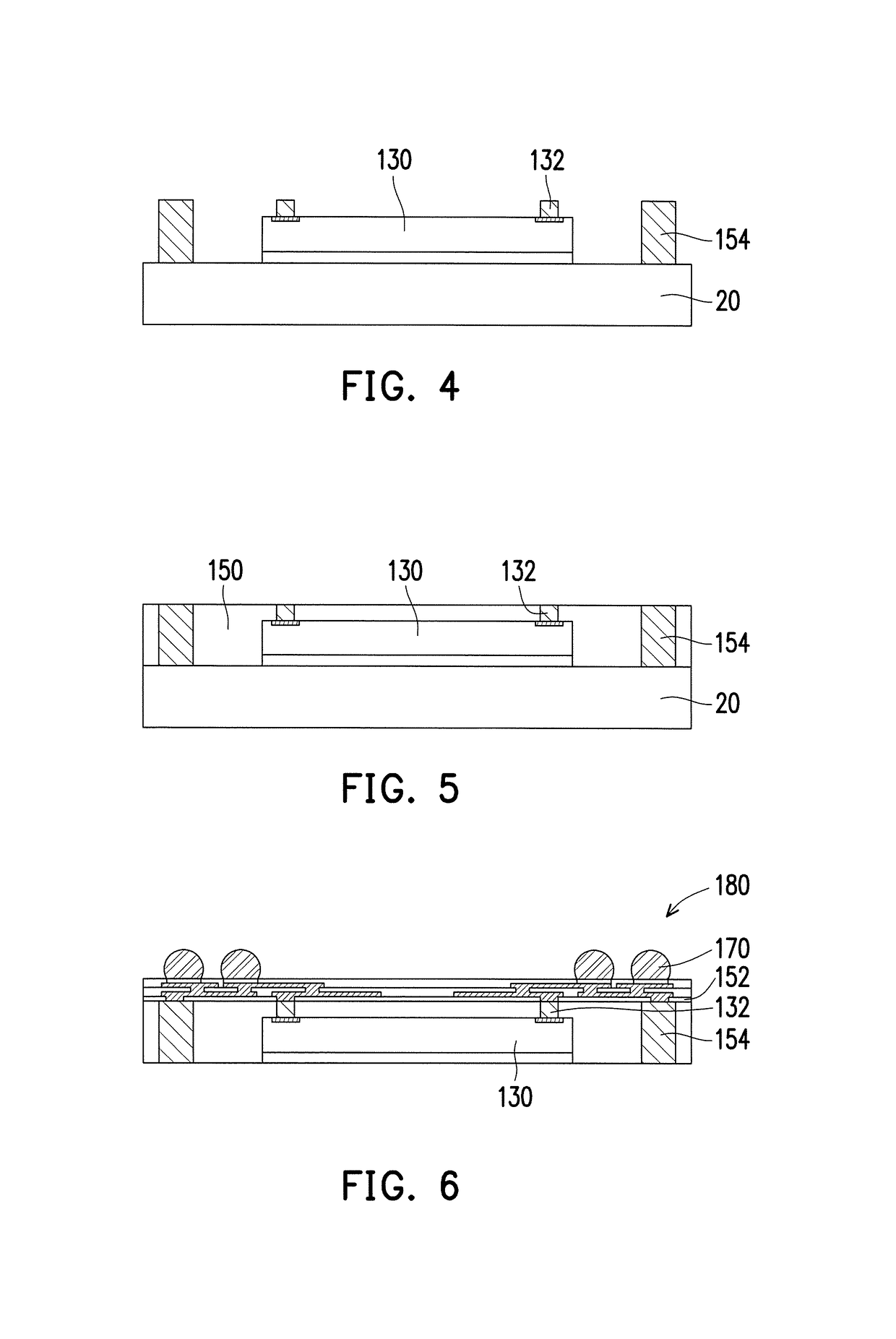

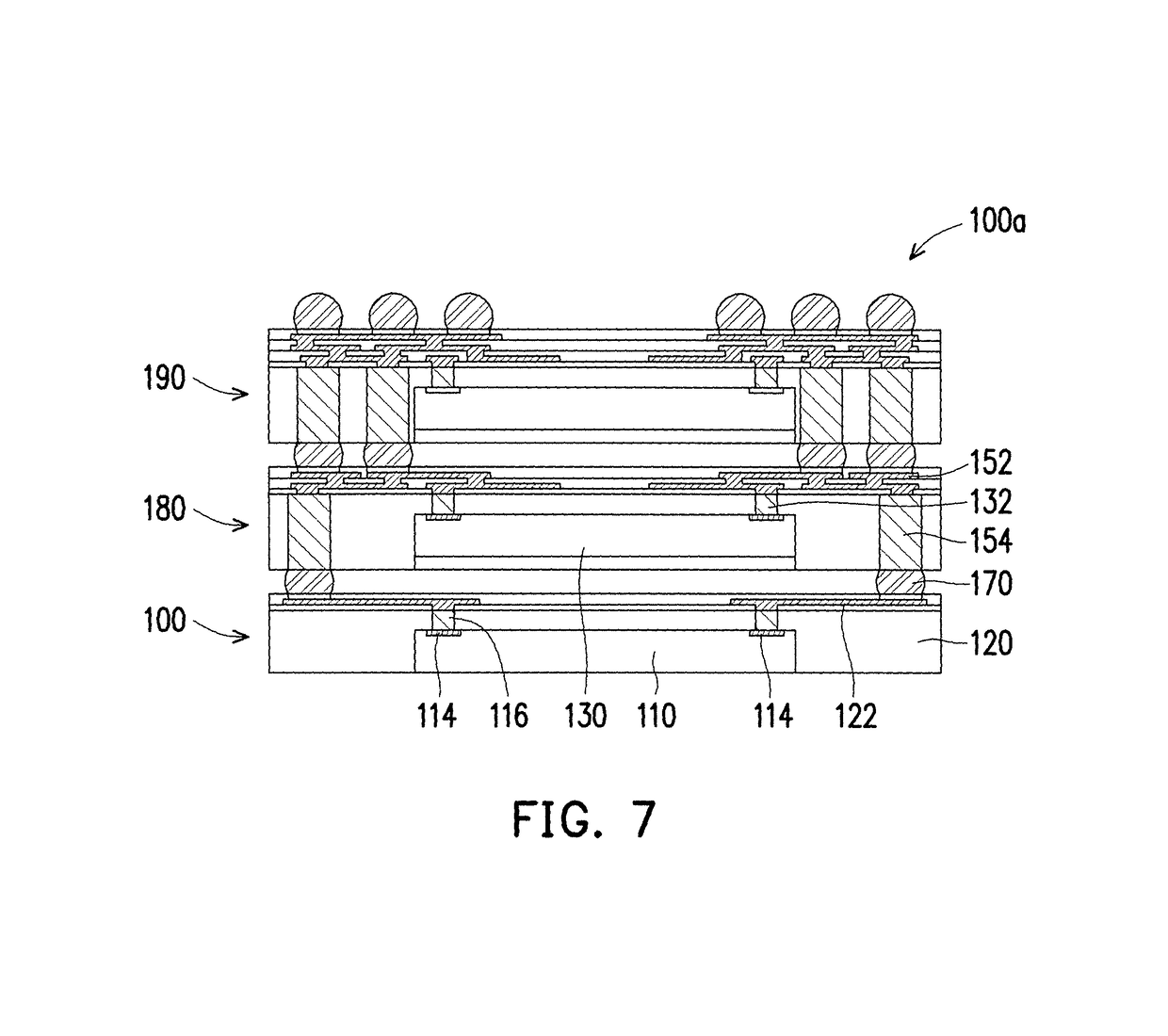

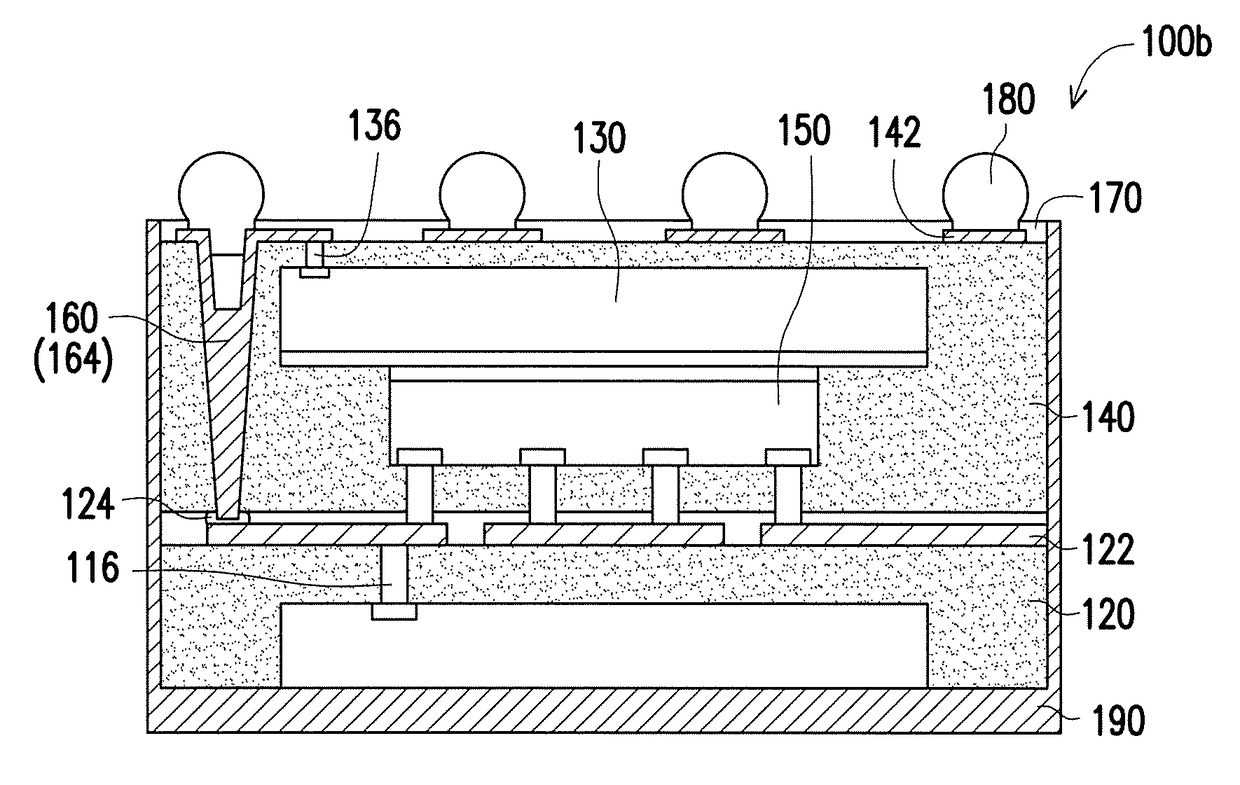

Stacked chip package structure and manufacturing method thereof

InactiveUS20170287870A1Low production costThin thicknessSemiconductor/solid-state device detailsSolid-state devicesRough surfaceElectrical and Electronics engineering

A stacked chip package structure includes a first chip, stud bumps, a second chip, pillar bumps, an encapsulant and conductive vias. The first stud bumps are respectively disposed on a plurality of first pads of the first chip, wherein each first stud bump includes a rough surface, and the rough surface of each first stud bump is rougher than a top surface of each first pad. The second chip is disposed on the first chip and exposes the first pads. The pillar bumps are respectively disposed on a plurality of second pads of the second chips. The encapsulant encapsulates the first chip and the second chip and exposes a top surface of each second stud bump. The first conductive vias penetrate the encapsulant and connect the first stud bumps. Each first conductive via covers the rough surface of each first stud bump.

Owner:POWERTECH TECHNOLOGY

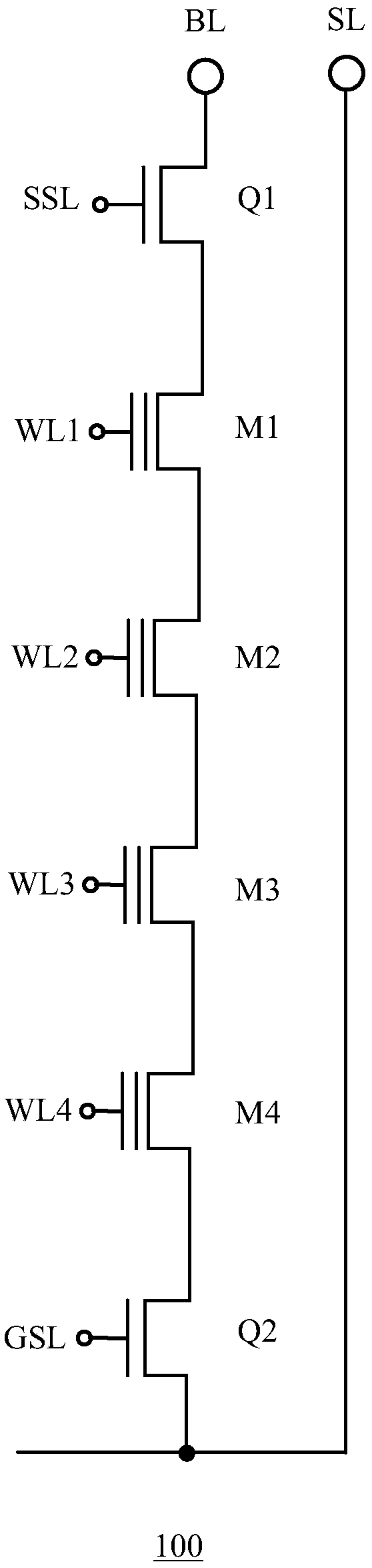

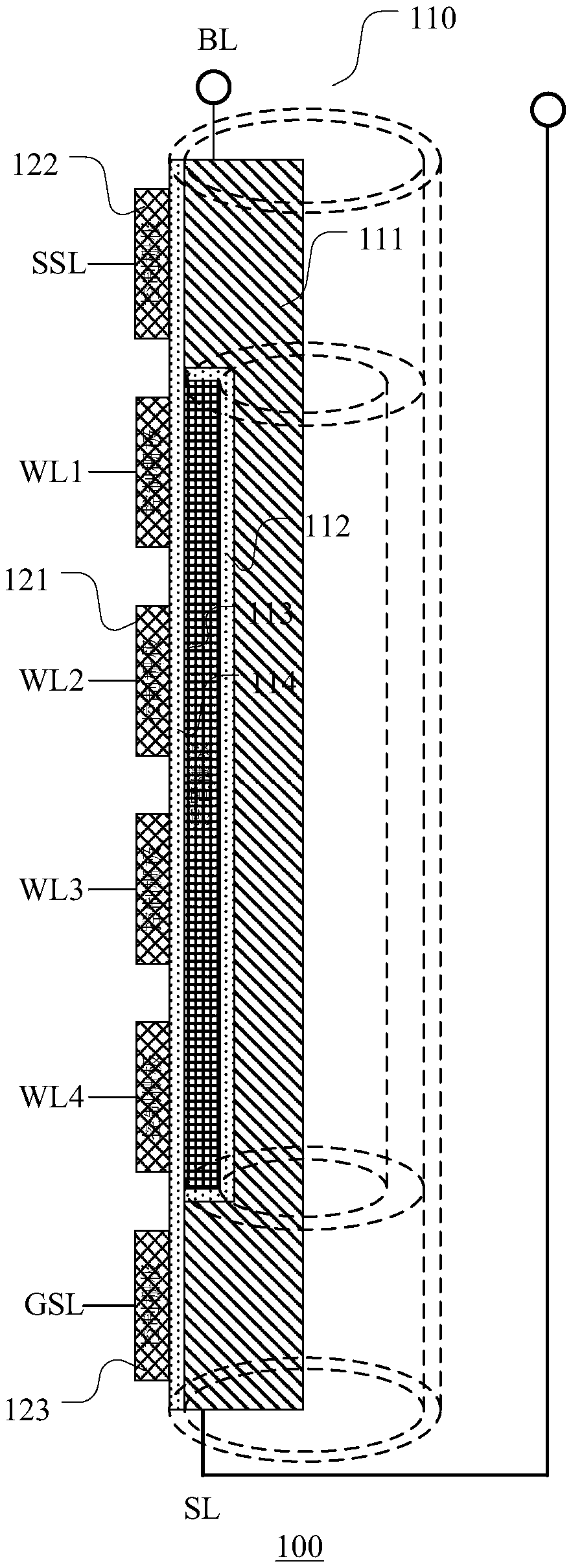

3D storage device

PendingCN109300902AAvoid device damageImprove yield and reliabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringGate stack

The present invention discloses a 3D memory device. The 3D memory device includes a gate stack structure, a plurality of channel pillars, and a plurality of dummy channel pillars; the gate stack structure includes a plurality of gate conductors and a plurality of interlayer insulating layers which are alternately stacked; the plurality of channel pillars penetrate the gate stack structure so as toform a transistor; and the plurality of dummy channel pillars pass through at least some of the gate conductors in the gate stack structure so as to provide support, wherein at least one of the dummychannel pillars is connected with a heat dissipation structure. According to the 3D memory device of the invention, the dummy channel pillars are connected to the heat dissipation structure, so thata heat dissipation path can be provided, and therefore, the yield and reliability of the 3D memory device can be improved.

Owner:YANGTZE MEMORY TECH CO LTD

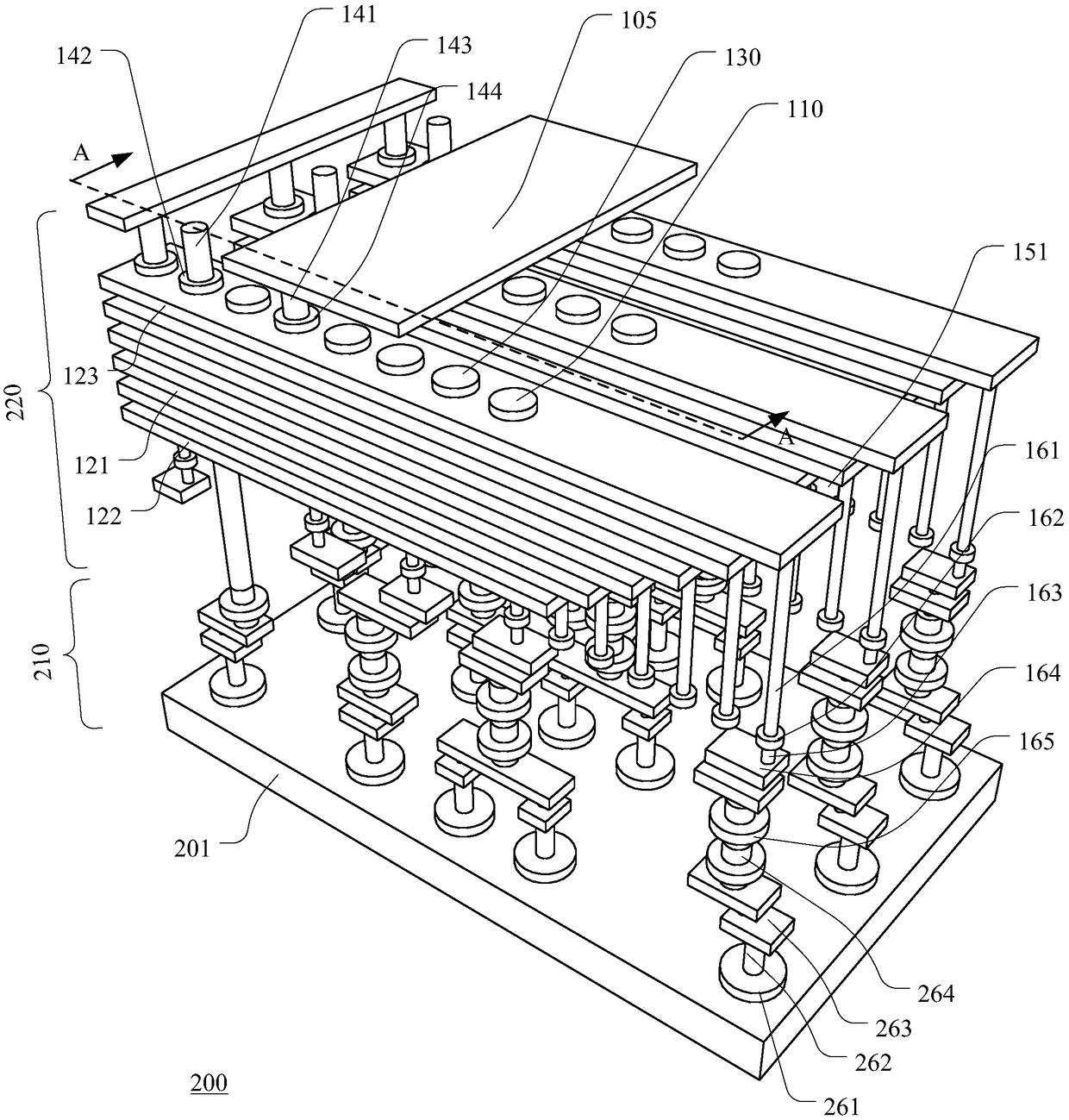

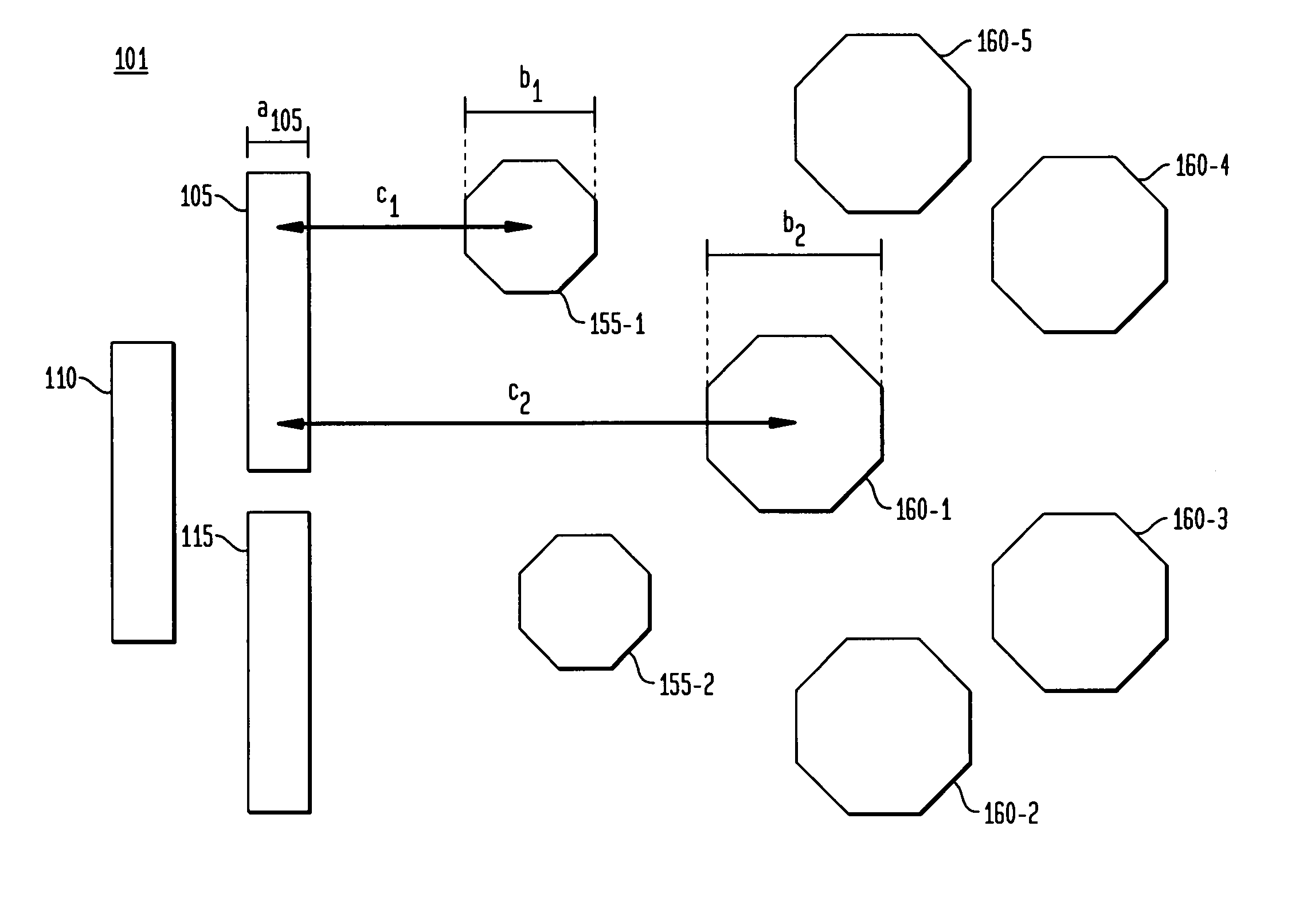

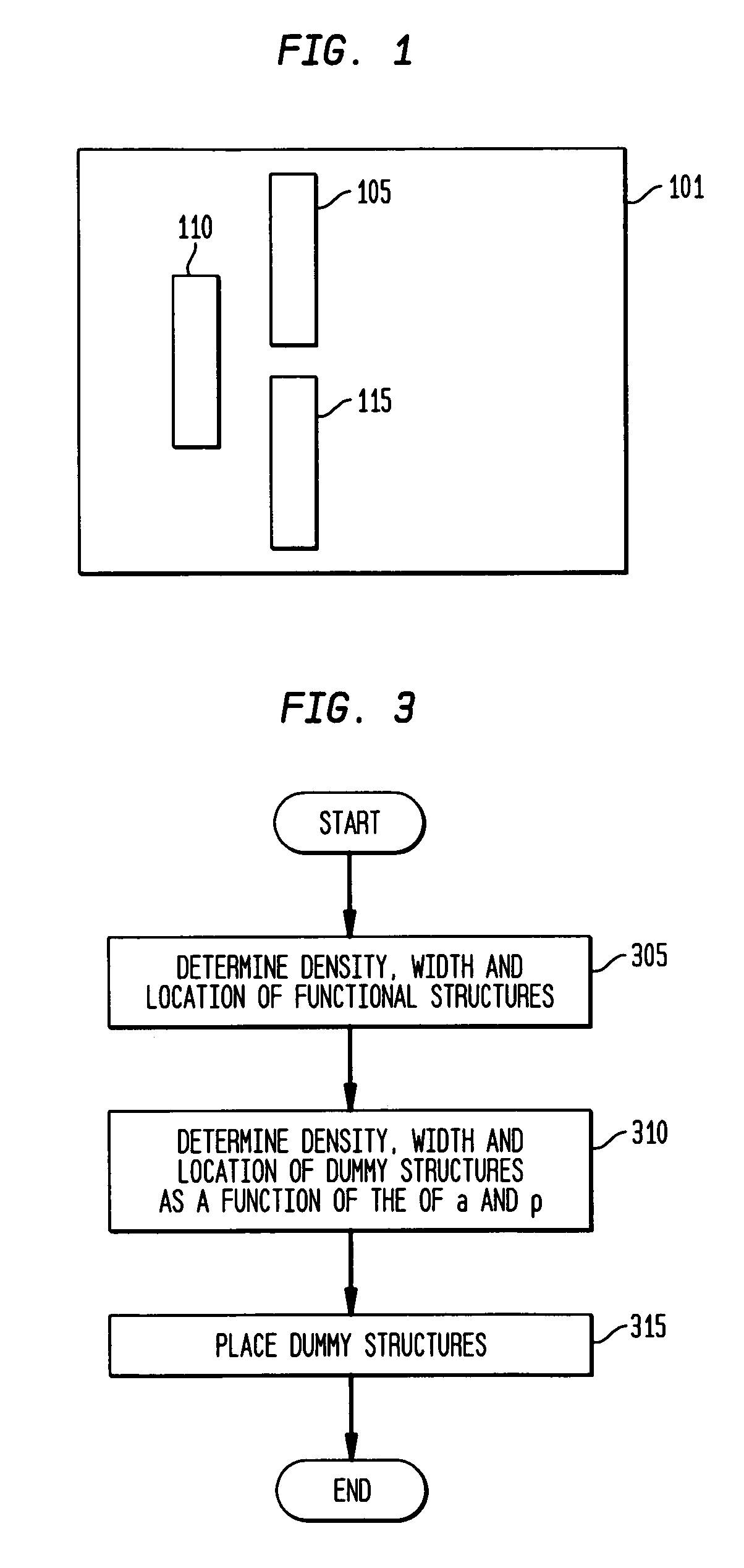

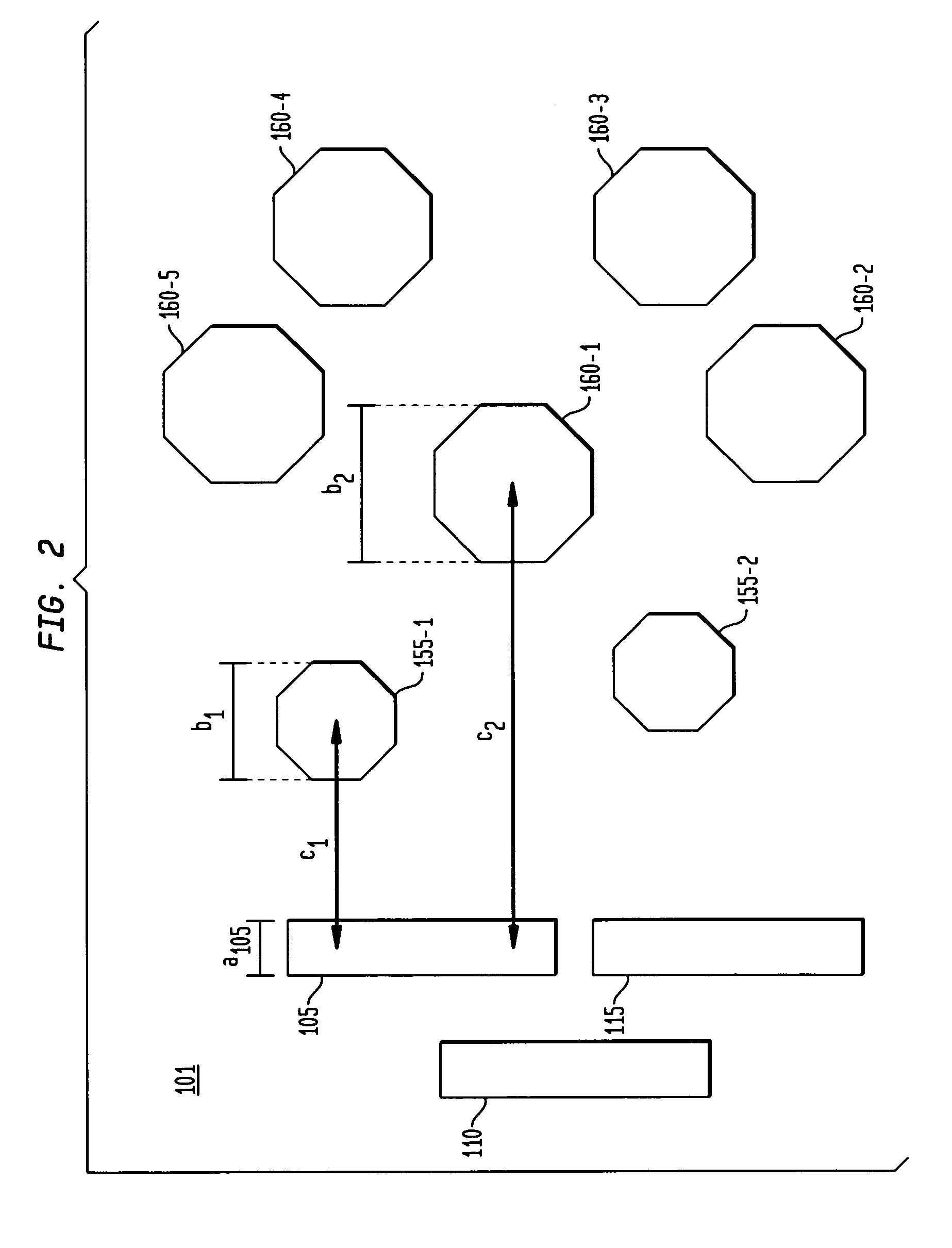

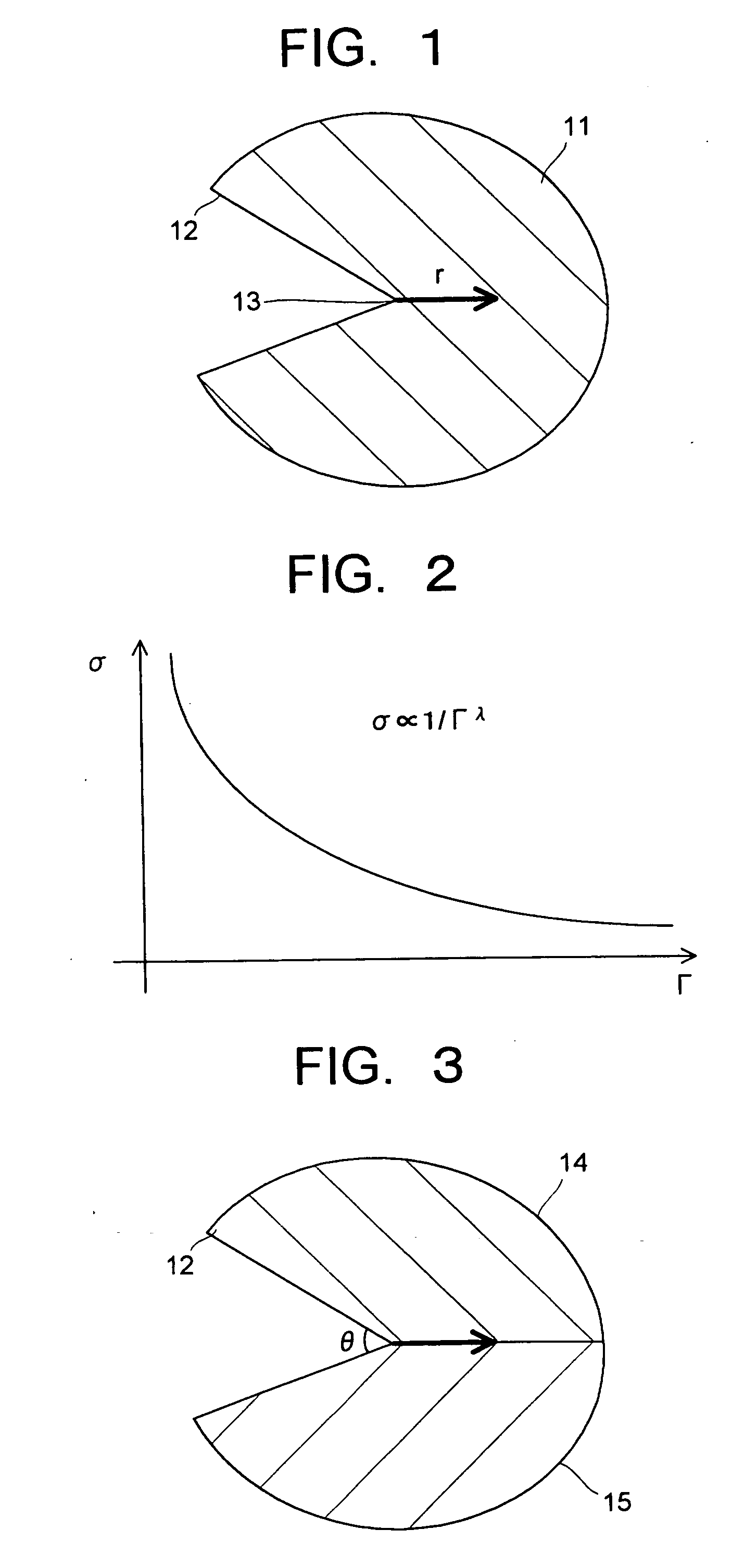

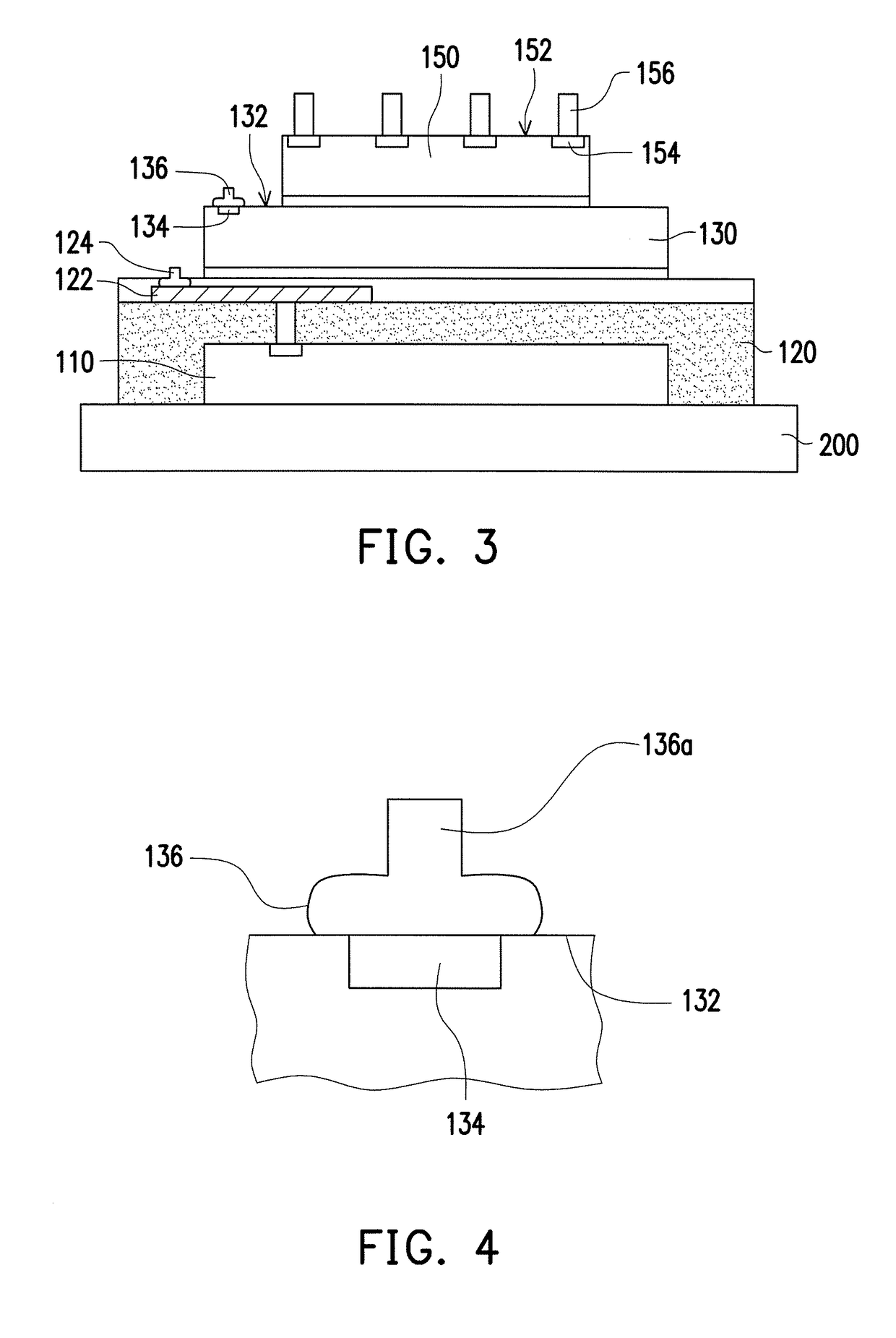

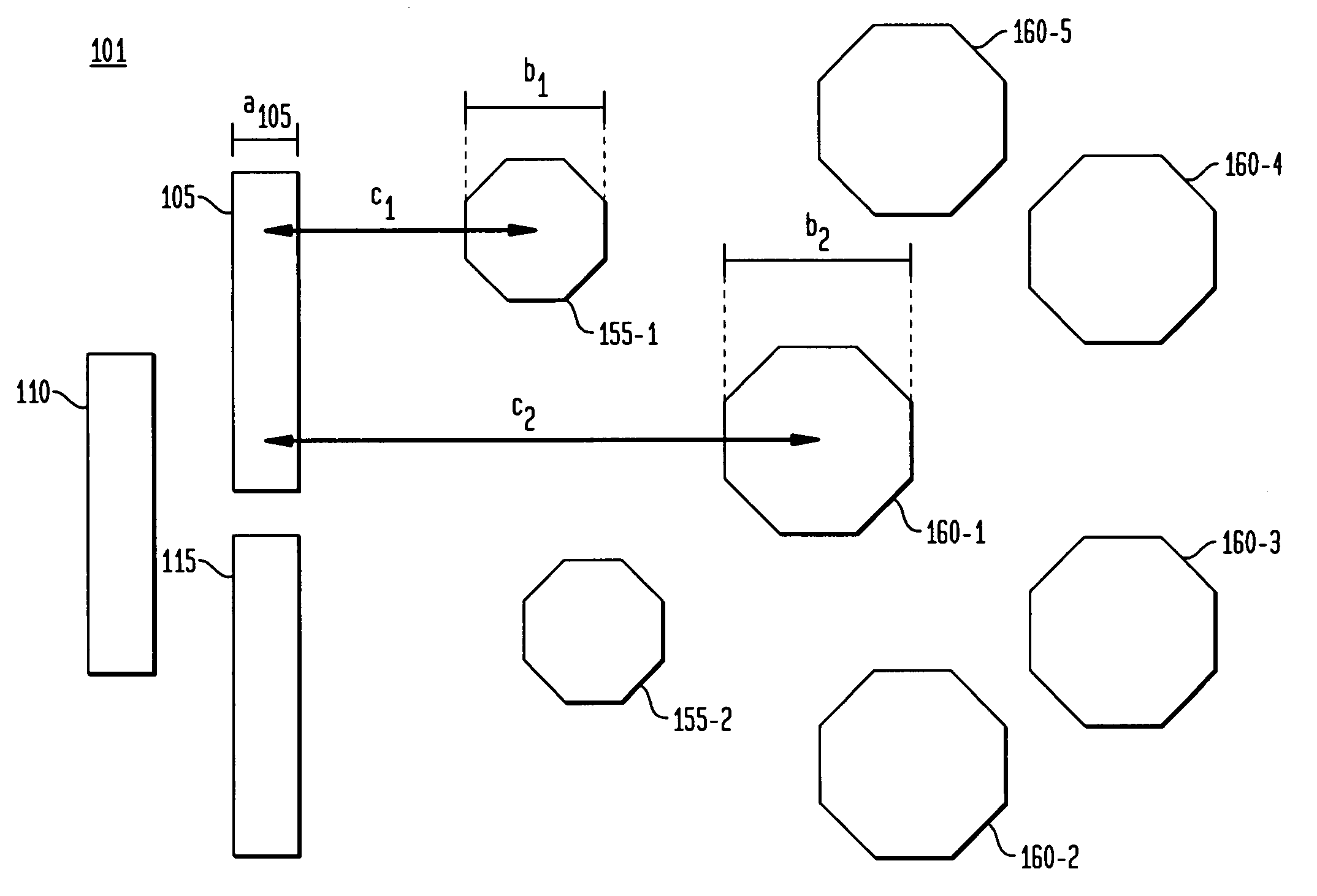

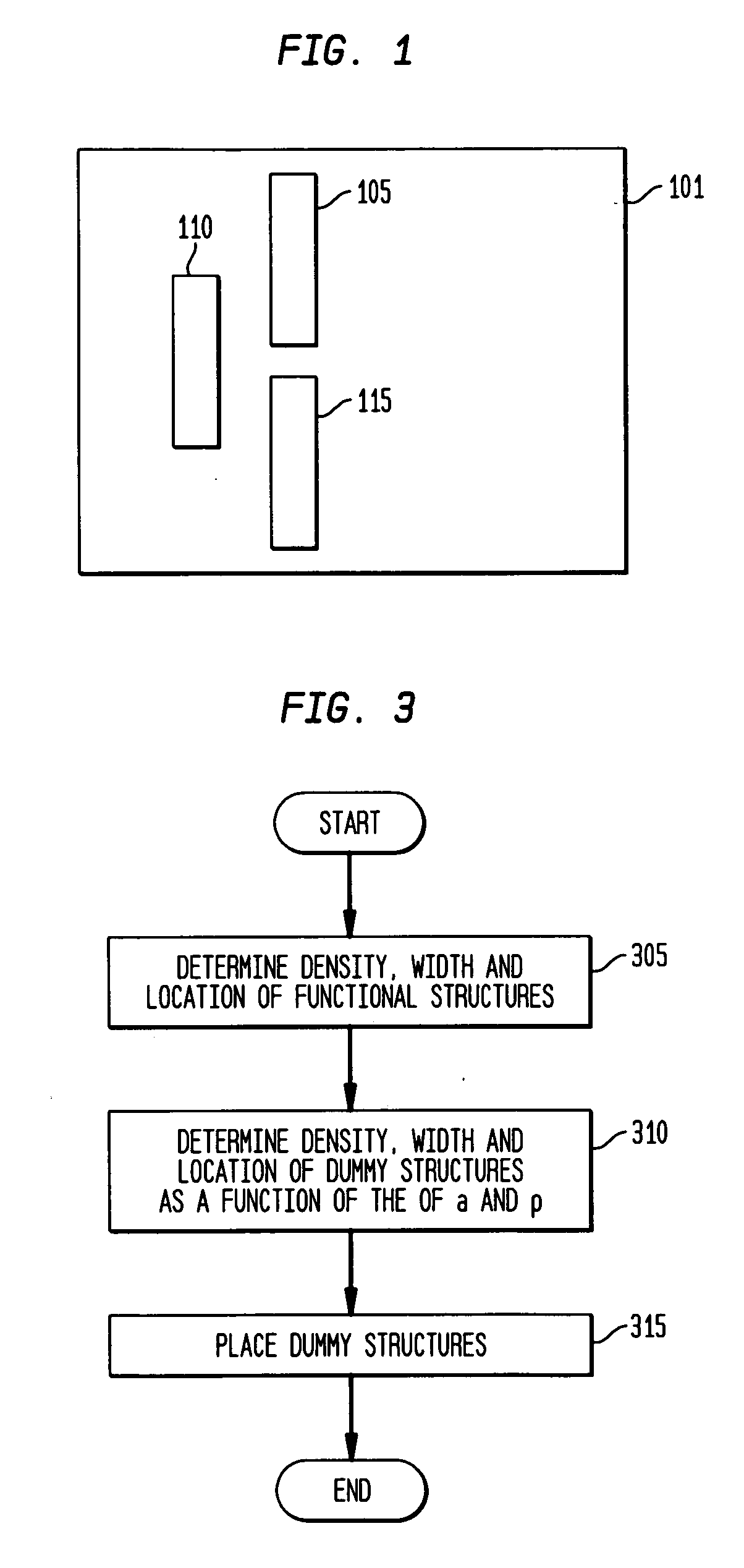

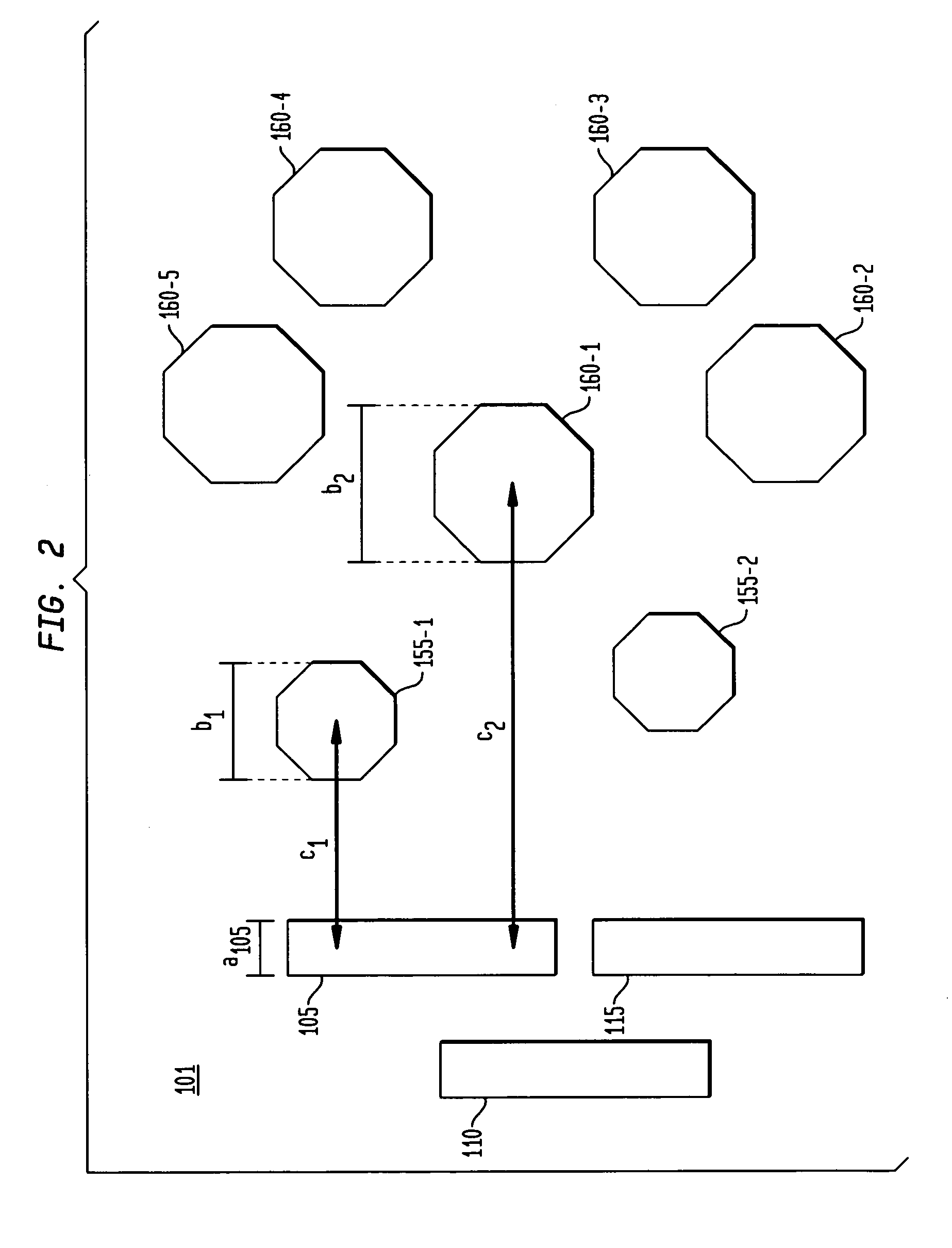

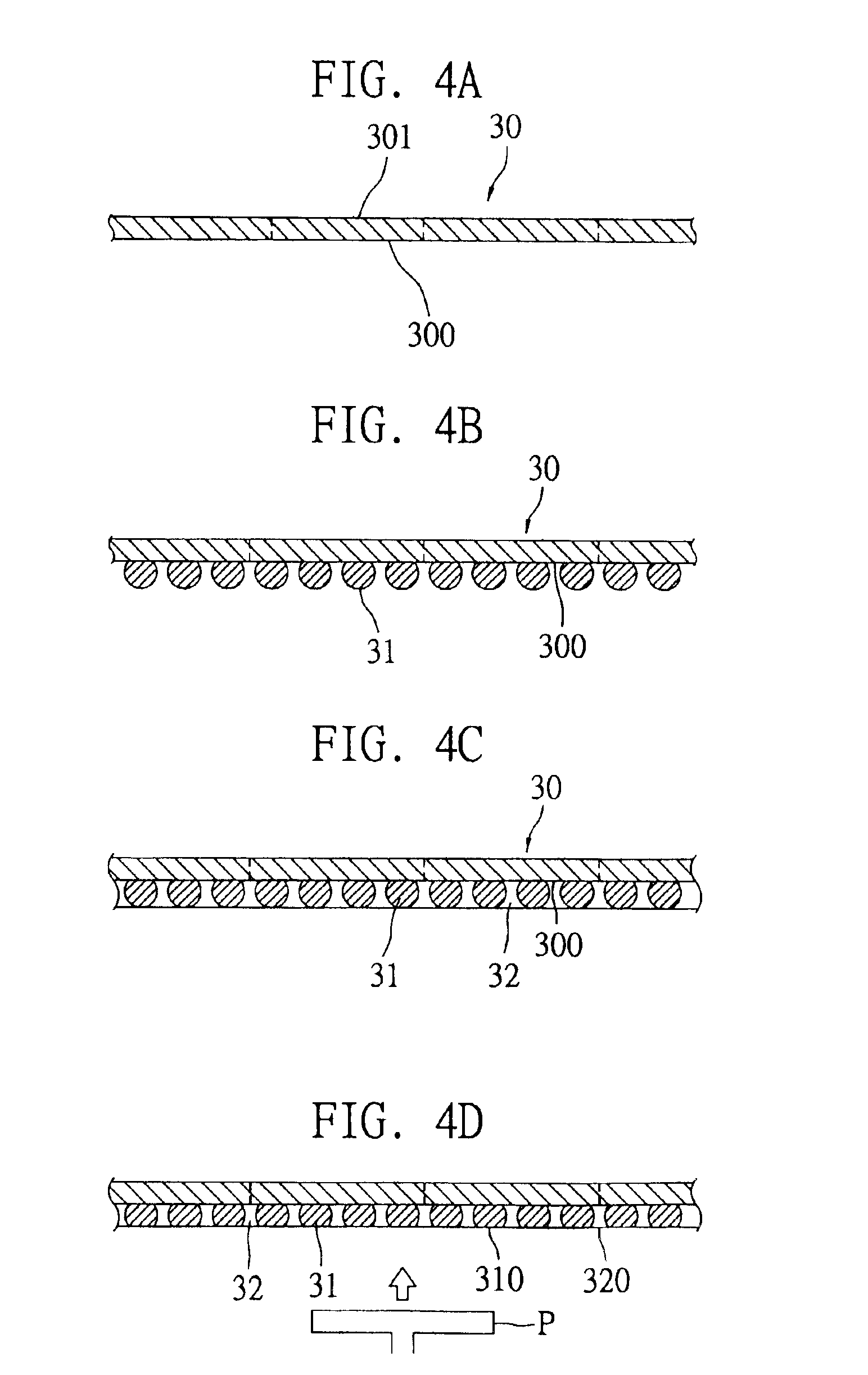

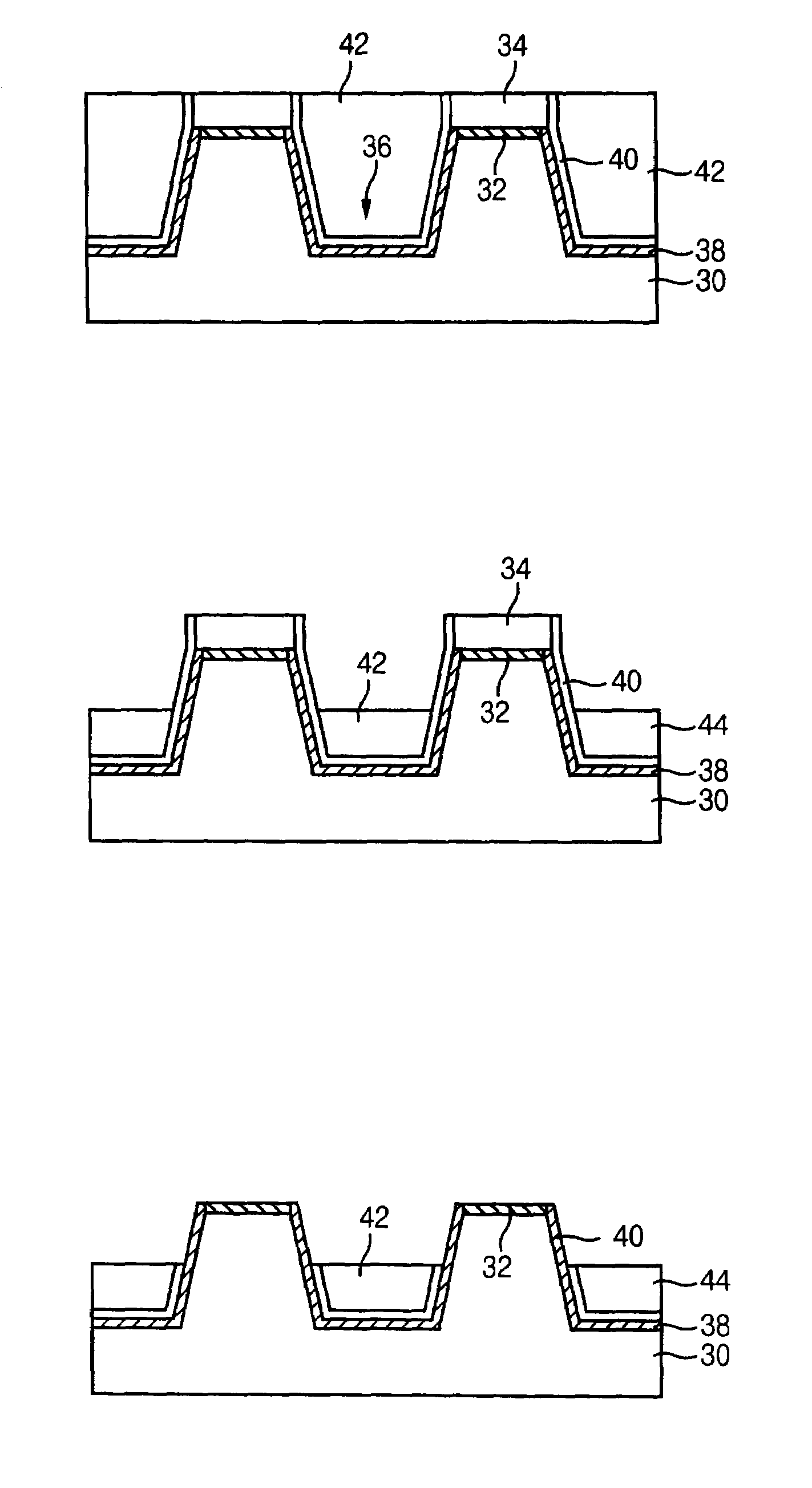

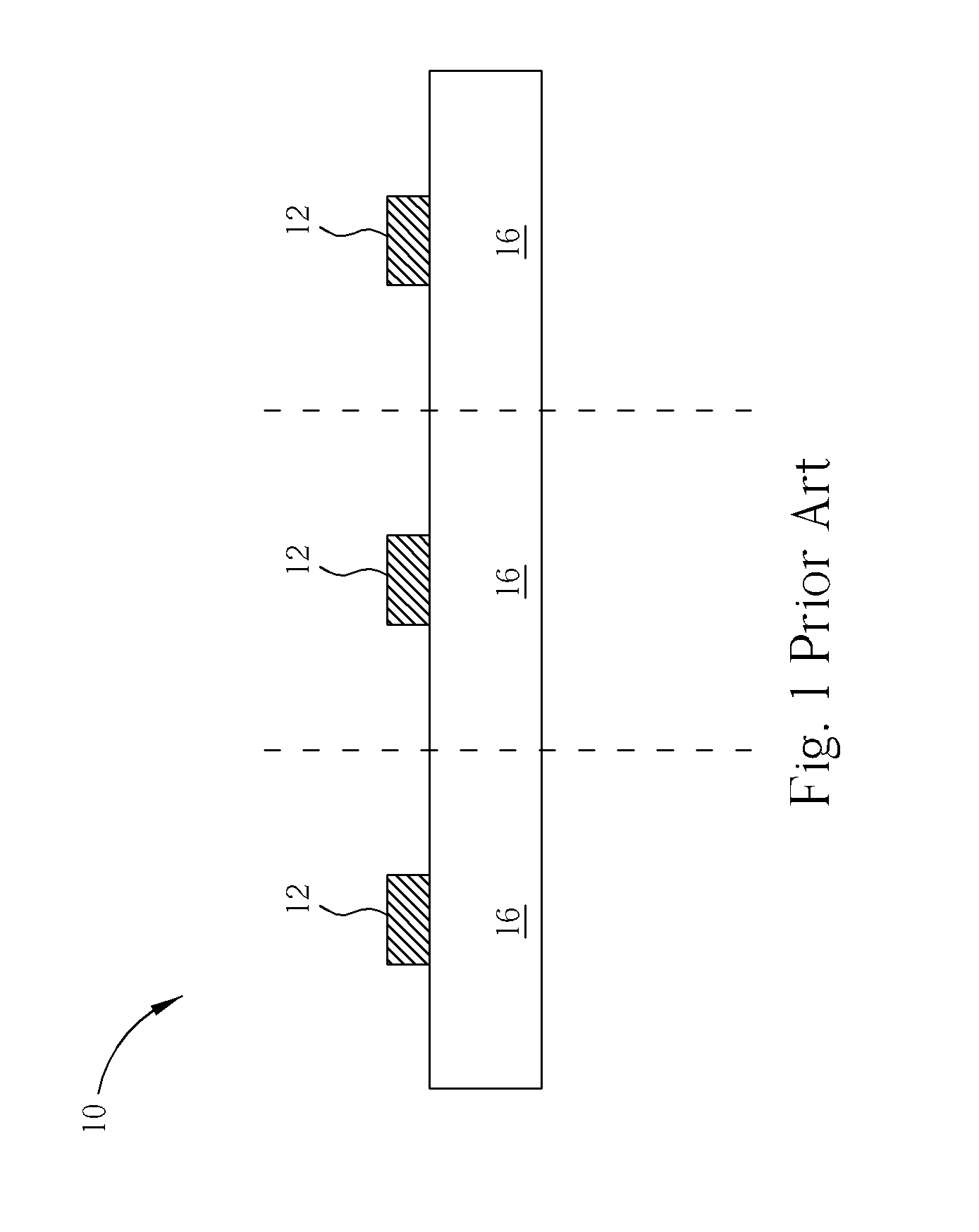

Structure and method for placement, sizing and shaping of dummy structures

InactiveUS7071074B2Improve yield and reliabilitySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingEngineeringSizing

A material layer on a substrate being processed, e.g. to form chips, includes one or more functional structures. In order to control pattern density during fabrication of the chip, dummy fill structures of different sizes and shapes are added to the chip at different distances from the functional structures of the material layer. In particular, the placement, size and shape of the dummy structures are determined as a function of a distance to, and density of, the functional structures of the material layer.

Owner:INFINEON TECH AG

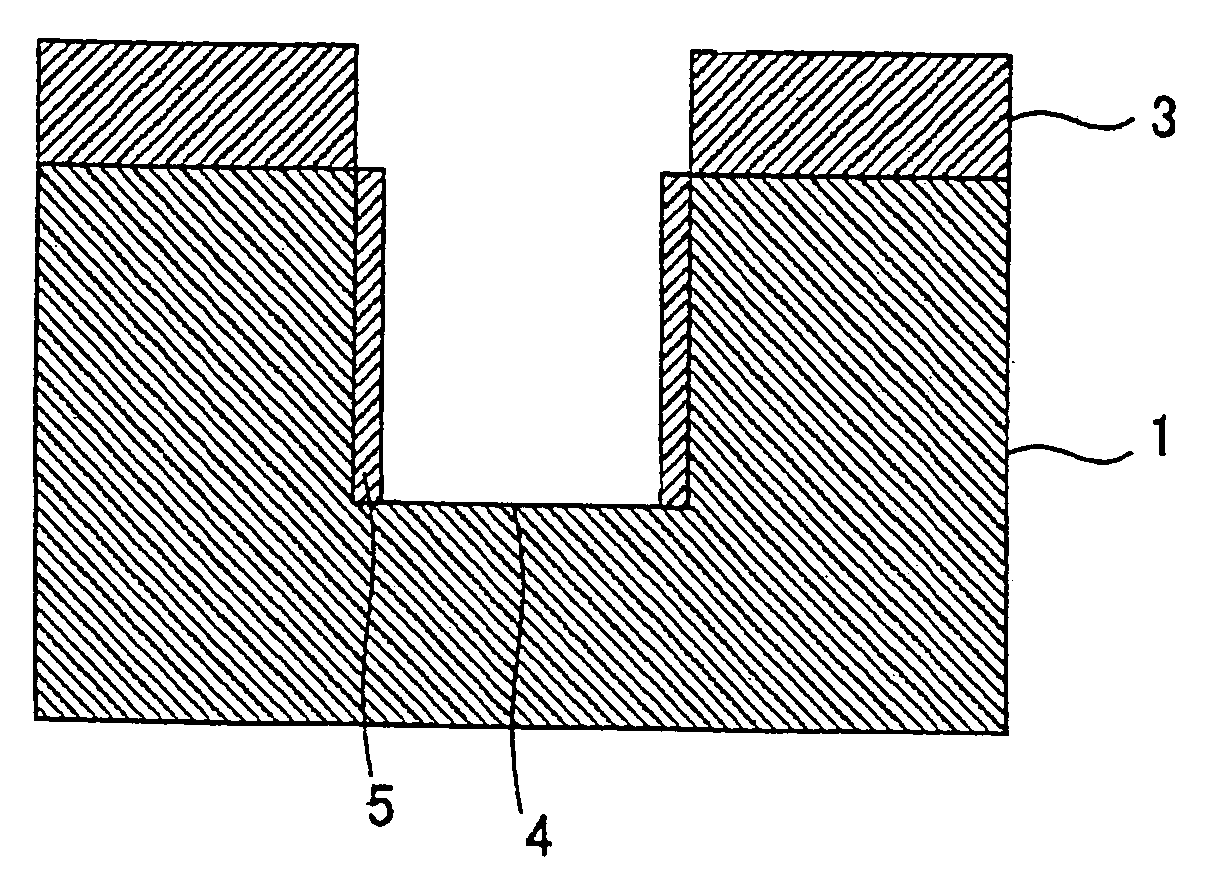

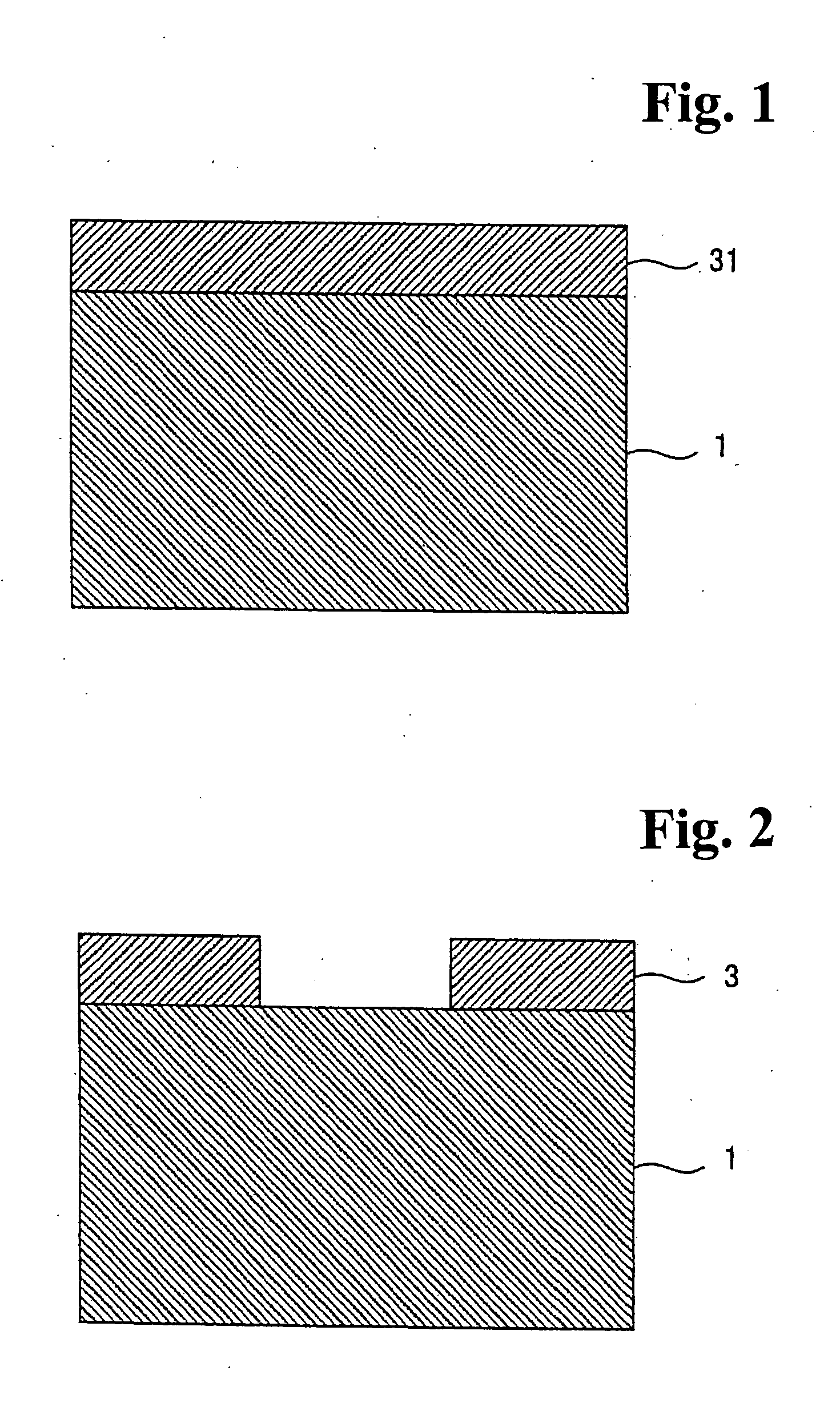

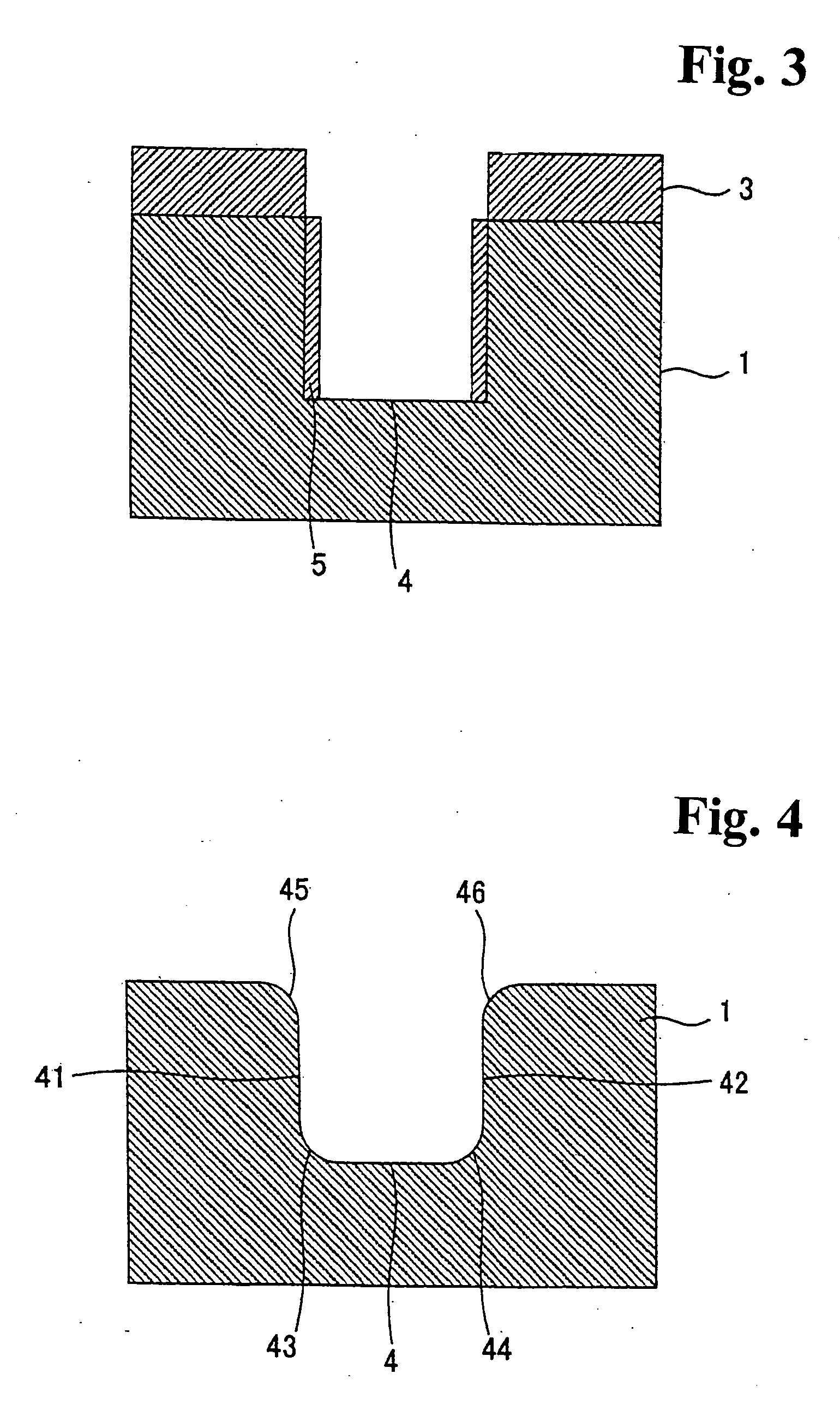

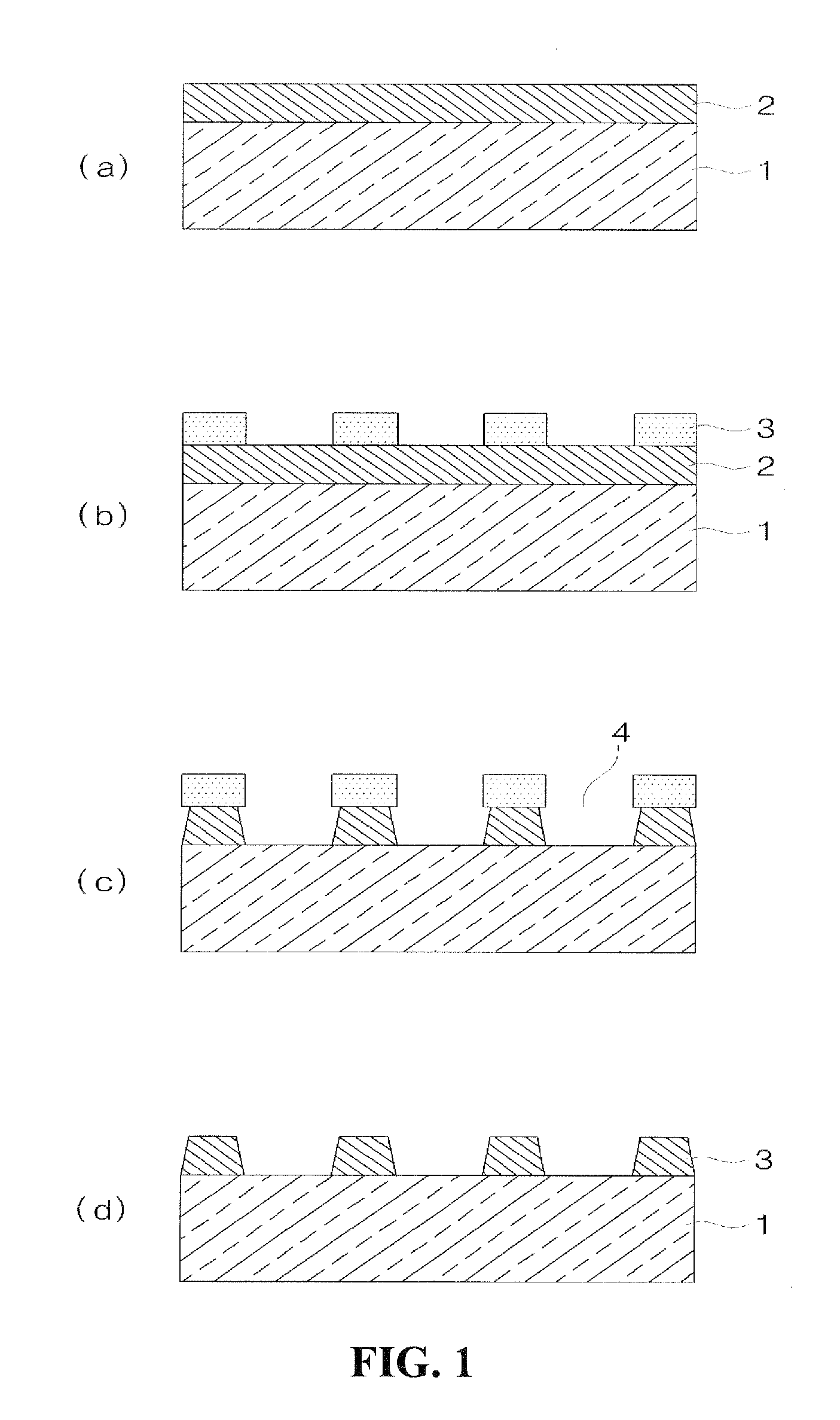

Method of manufacturing semiconductor device and method of treating semiconductor surface

InactiveUS20050106847A1Improve yield and reliabilityReduce variationSemiconductor/solid-state device manufacturingSemiconductor devicesHydrogen atmosphereGate insulator

A method of manufacturing a semiconductor device includes the steps of: exposing a semiconductor surface of a substrate; annealing the substrate in a hydrogen atmosphere at a hydrogen pressure between 200 Torr and 760 Torr and a temperature between 1000° C. and 1050° C. to planarize the exposed semiconductor surface; and forming a gate insulator film on the planarized semiconductor surface.

Owner:FUJI ELECTRIC CO LTD

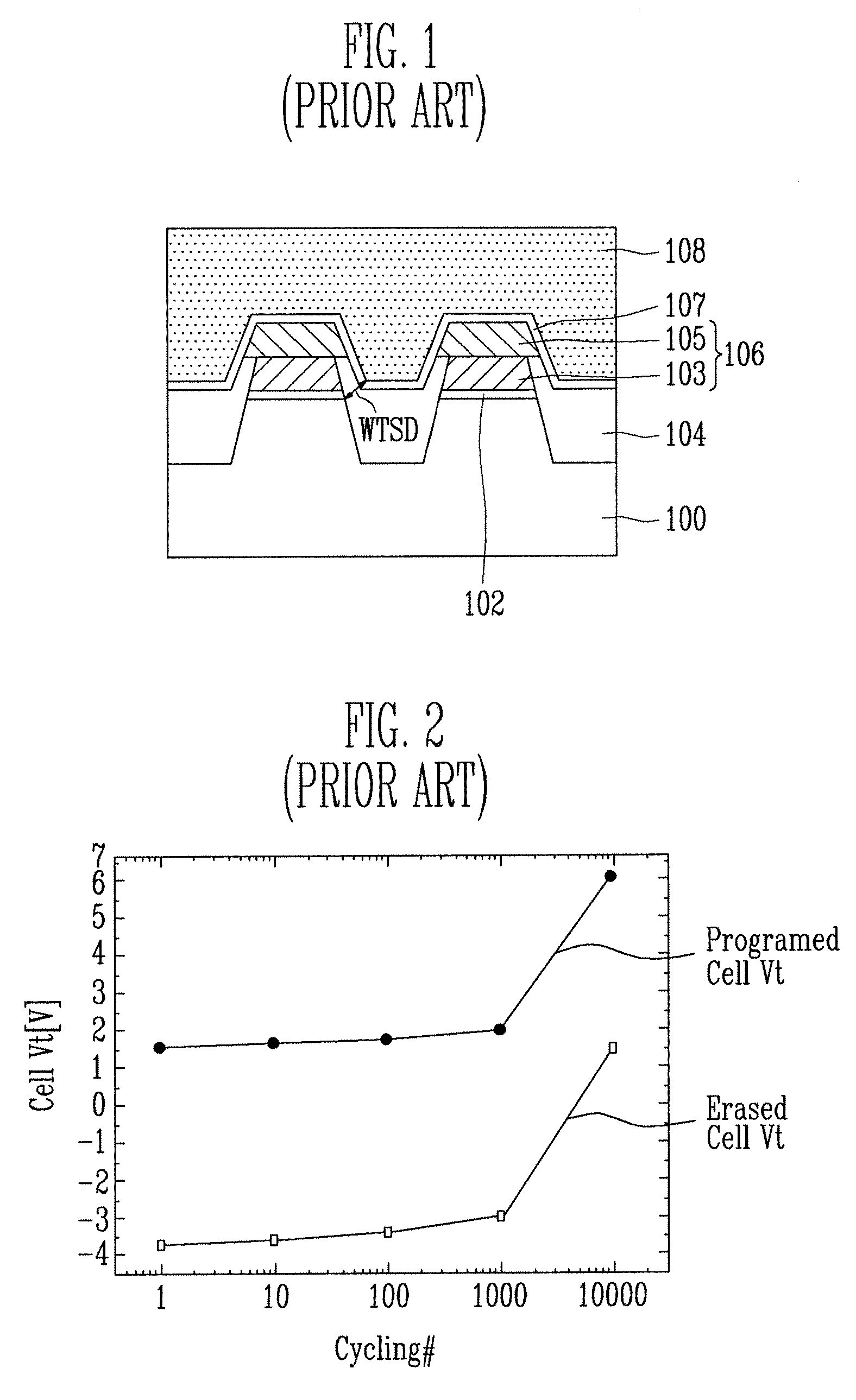

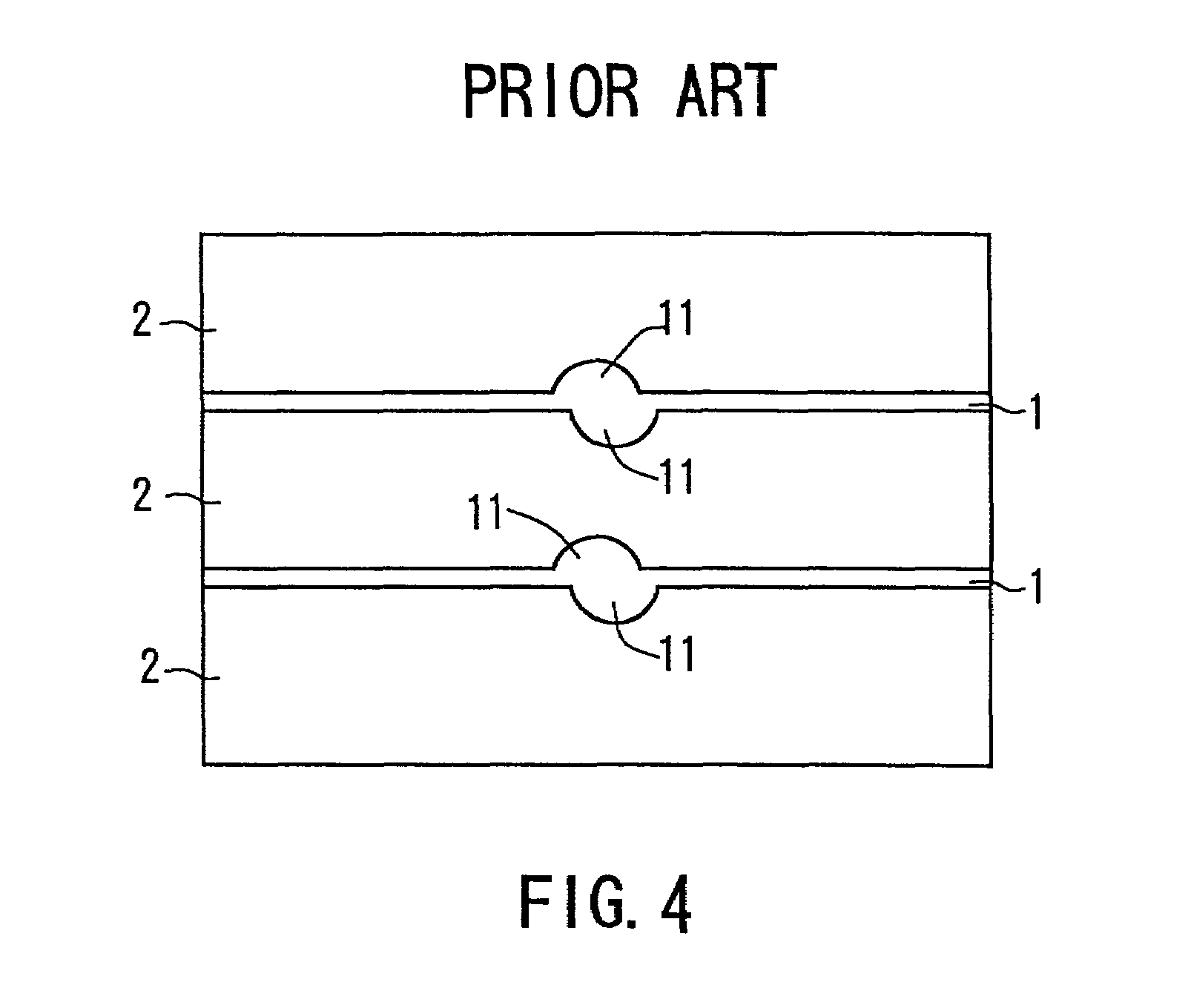

Semiconductor device and method of manufacturing the same

InactiveUS20050266668A1Improve yield and reliabilityImprove reliabilityPrinted circuit assemblingFinal product manufactureEngineeringSemiconductor components

A semiconductor device comprises a semiconductor element having first electrode pads and solder bumps, and a substrate having second electrode pads connected to the first electrode pads via the solder bumps. The semiconductor element has an insulating film with a low dielectric constant. The group of the solder bumps is provided with a solder bump in which a stress intensity factor K in a notch shape formed by the first electrode pad and the outline of the solder bump, when looking at a cross section through the center of the first electrode pad and the solder bump, is such that on the chip edge side it is less than or equal to its value on the chip center side. Thereby, cracking or delamination of the semiconductor element due to the insulating film with a low dielectric constant can be restrained.

Owner:KK TOSHIBA

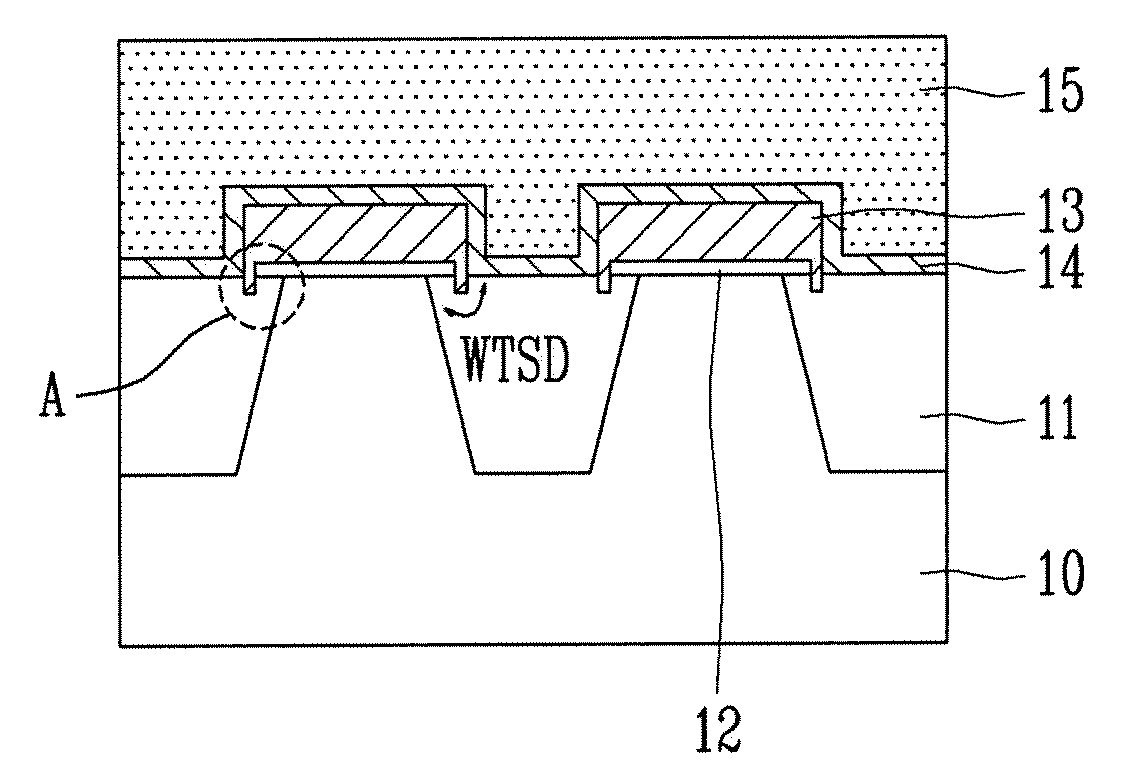

Flash Memory Device

ActiveUS20070001211A1Improve featuresImprove reliabilityTransistorSolid-state devicesEngineeringElectric field

A floating gate of a flash memory device is formed in a moat formed in an isolation film. Therefore, an electric field applied between a control gate and a channel region upon cycling can be precluded or mitigated. A distance between the control gate and the channel region is set greater than a predetermined value. Therefore, an electric field applied between the control gate and the channel region upon cycling can be mitigated. As a result, a data retention characteristic and an endurance characteristic can be improved.

Owner:SK HYNIX INC

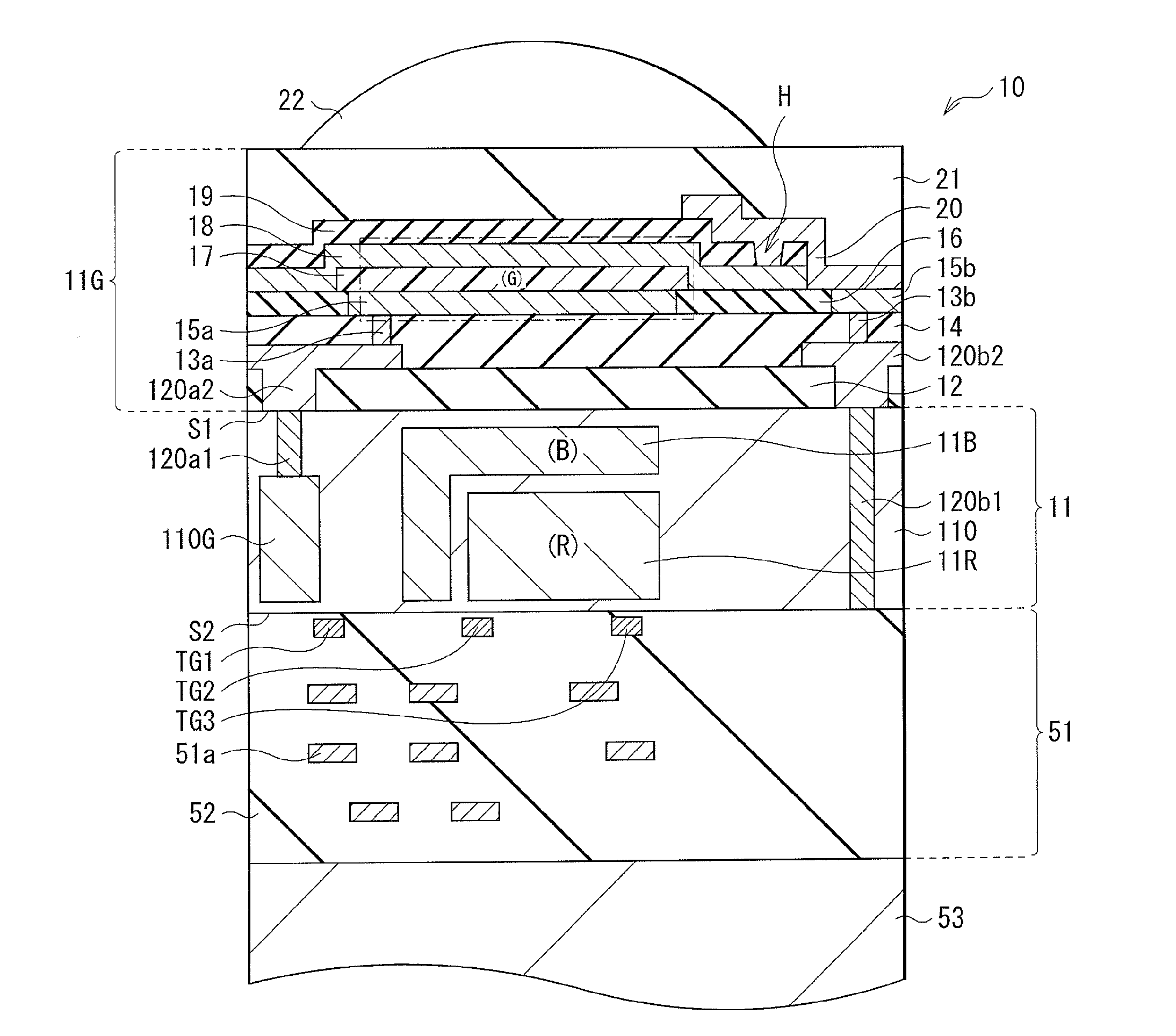

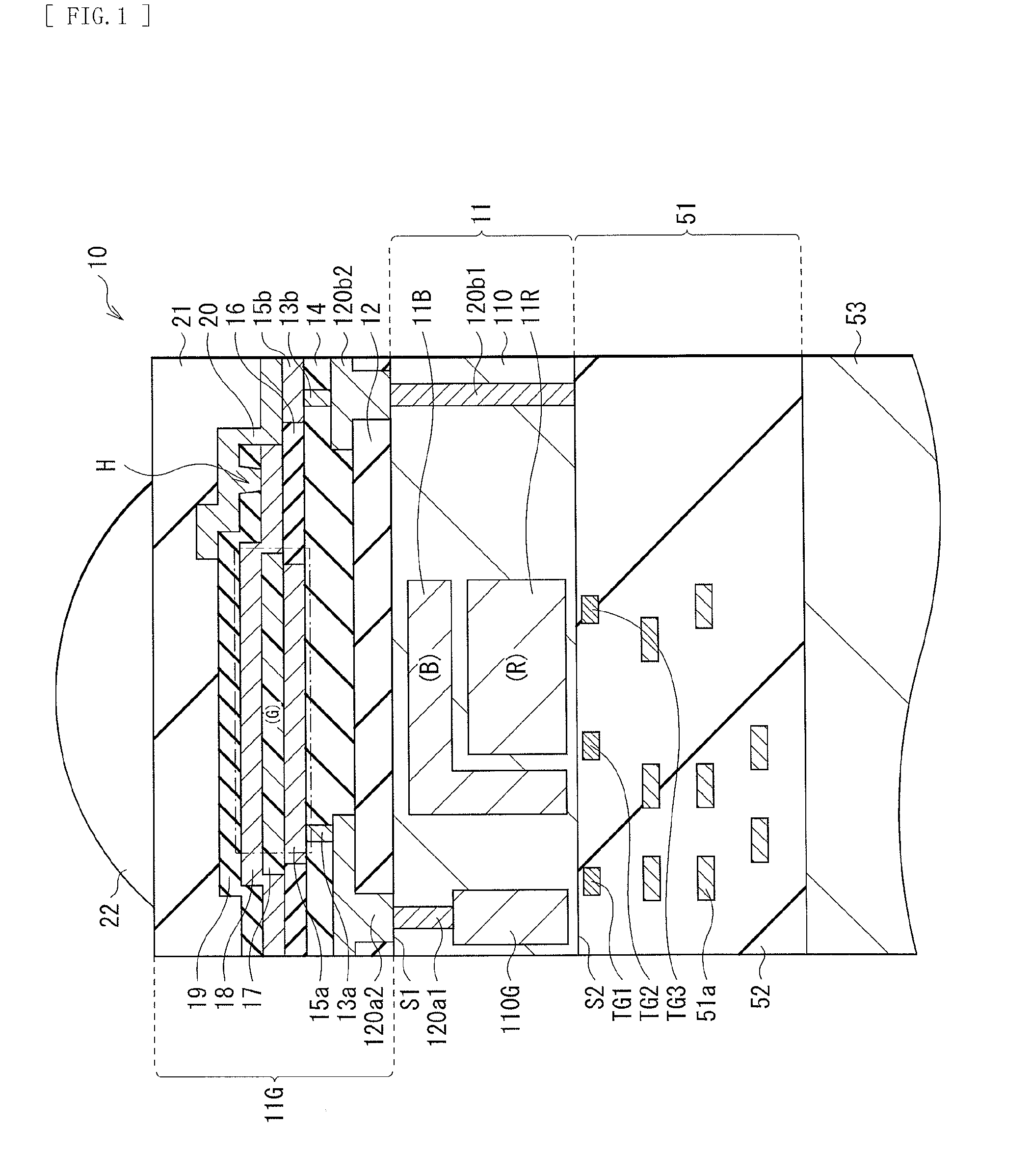

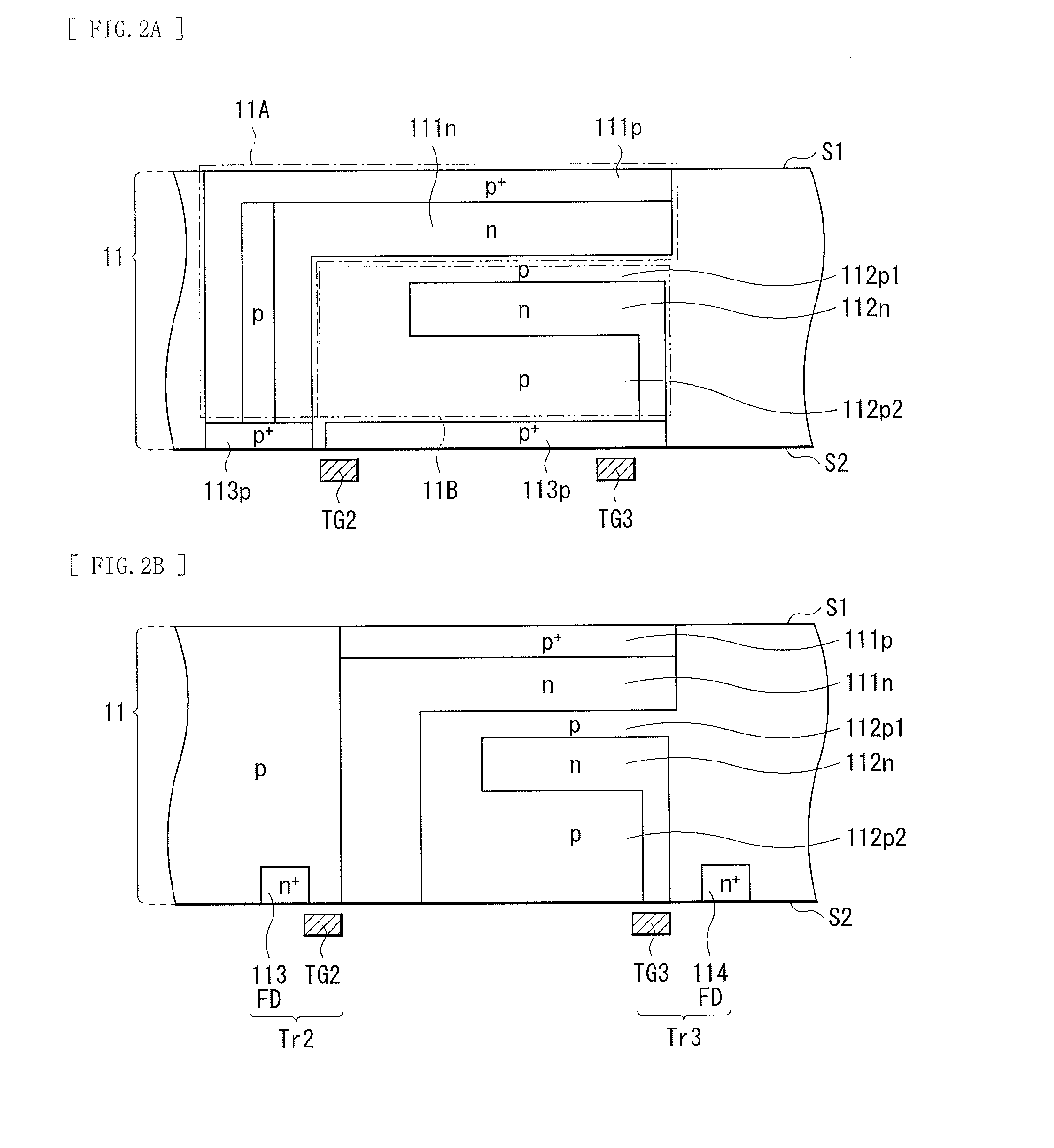

Semiconductor device, method of manufacturing semiconductor device, solid-state imaging unit, and electronic apparatus

ActiveUS20140353651A1Suppress damageImprove yield and reliabilityFinal product manufactureSolid-state devicesSolid-stateOrganic semiconductor

A semiconductor device includes, in order on a substrate, an organic semiconductor layer, an inorganic film, and a protective film. The inorganic film and the protective film each have a peripheral edge portion that is formed in an outer region compared to a peripheral edge portion of the organic semiconductor layer.

Owner:SONY CORP

Stacked chip package structure and manufacturing method thereof

ActiveUS20170287874A1Improve reliabilityLow production costSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerEngineering

A stacked chip package structure includes a first chip, pillar bumps, a first encapsulant, a first redistribution layer, a second chip, a second encapsulant, a second redistribution layer and a through via. The pillar bumps are disposed on a plurality of first pads of the first chip respectively. The first encapsulant encapsulates the first chip and exposes the pillar bumps. The first redistribution layer is disposed on the first encapsulant and electrically connects the first chip. The second chip is disposed on the first redistribution layer. The second encapsulant encapsulates the second chip. The second redistribution layer is disposed on the second encapsulant and electrically coupled to the second chip. The through via penetrates the second encapsulant and electrically connects the first redistribution layer and the second redistribution layer.

Owner:POWERTECH TECHNOLOGY

Structure and method for placement, sizing and shaping of dummy structures

InactiveUS20050064634A1Improve yield and reliabilitySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingEngineeringSizing

A material layer on a substrate being processed, e.g. to form chips, includes one or more functional structures. In order to control pattern density during fabrication of the chip, dummy fill structures of different sizes and shapes are added to the chip at different distances from the functional structures of the material layer. In particular, the placement, size and shape of the dummy structures are determined as a function of a distance to, and density of, the functional structures of the material layer.

Owner:INFINEON TECH AG

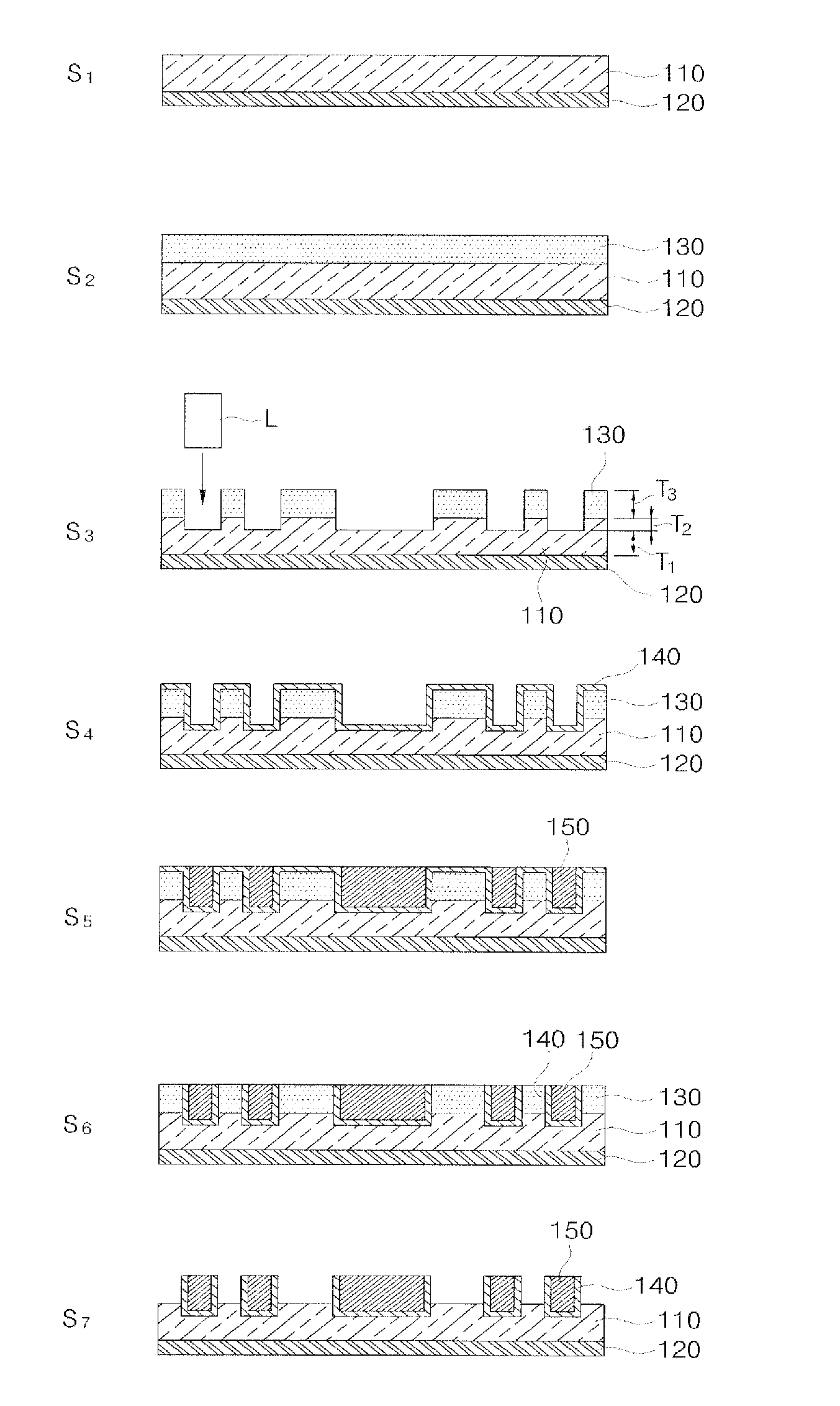

Embedded printed circuit board, multi-layer printed circuit board and manufacturing method thereof

ActiveUS20110127070A1Improve yield and reliabilitySimplify manufacturing processRadiation applicationsPretreated surfacesPhotoresistMicro pattern

An embedded PCB, a multi-layer PCB using the embedded PCB, and a method of manufacturing the same are provided. The method of manufacturing an embedded PCB includes a first step of patterning an insulating layer on which a photoresist layer is formed using a laser such that parts of the insulating layer are selectively etched to form a circuit pattern region and a second step of filling the circuit pattern region with a plating material to form a circuit pattern. Accordingly, the method of manufacturing an embedded PCB can simultaneously or sequentially etch a photoresist layer and an insulating layer using a laser to form a circuit pattern so as to obtain a micro pattern and simplify a manufacturing process and achieve alignment accuracy in construction of a multi-layer PCB using the embedded PCB to thereby improve product reliability and yield.

Owner:LG INNOTEK CO LTD

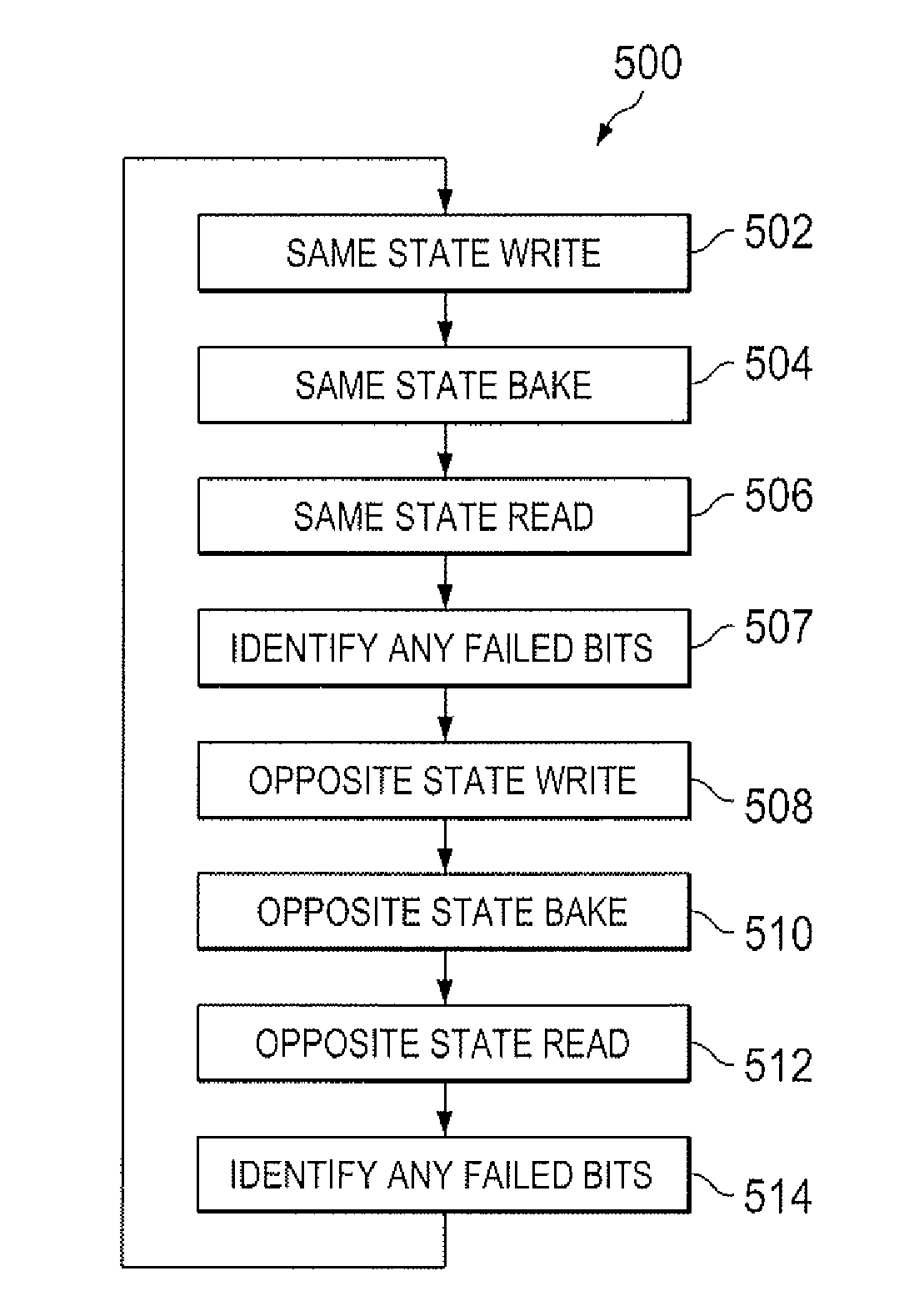

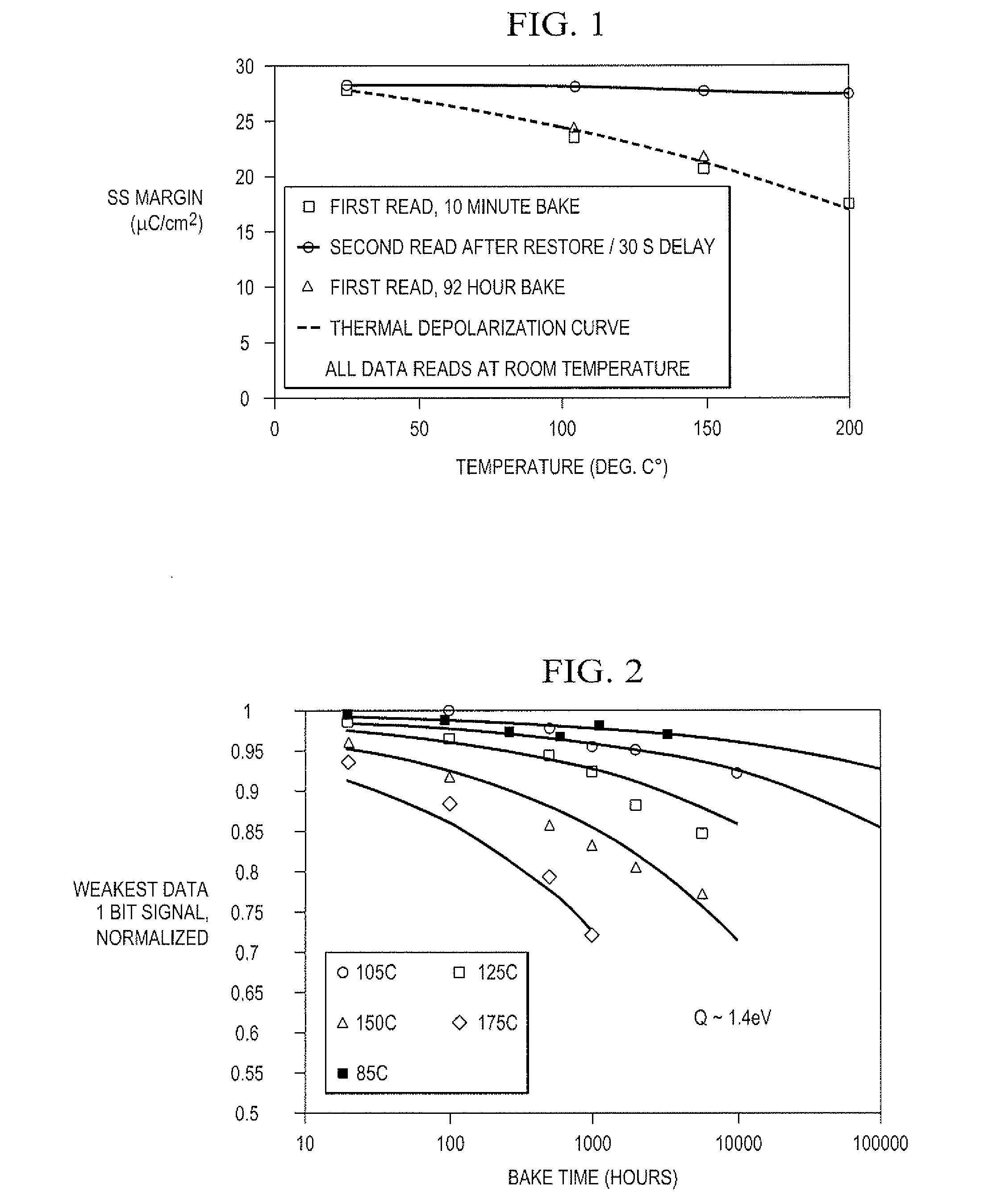

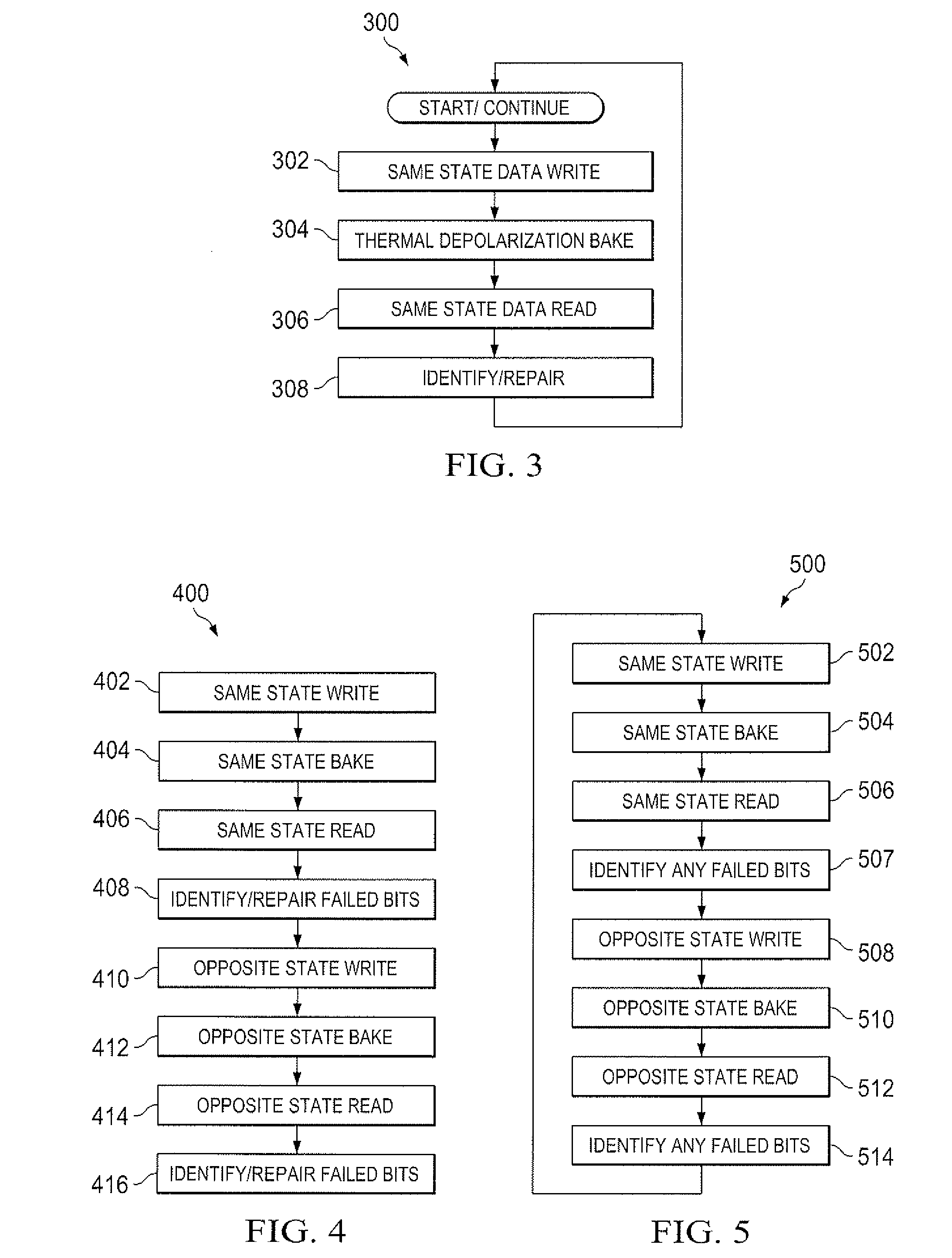

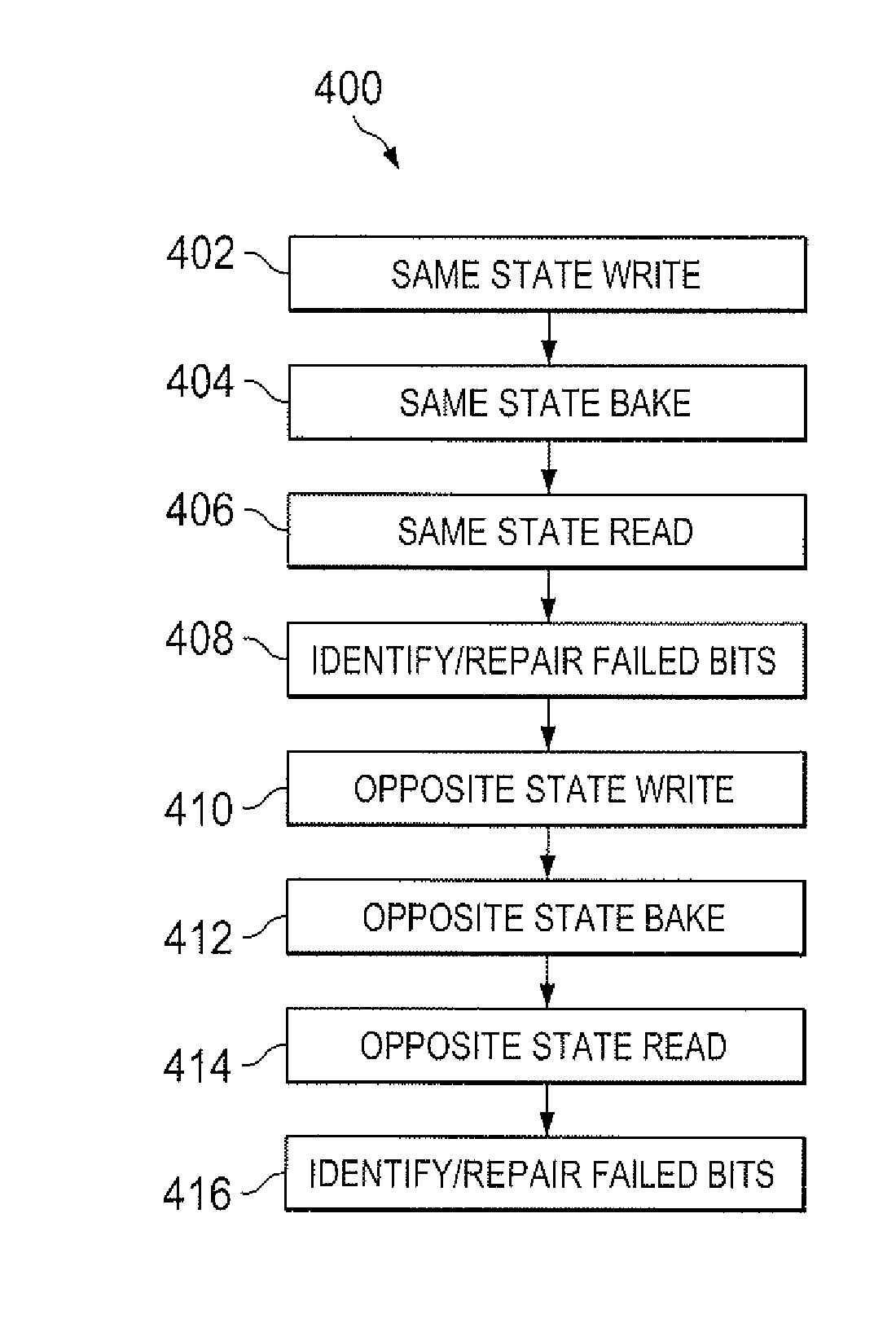

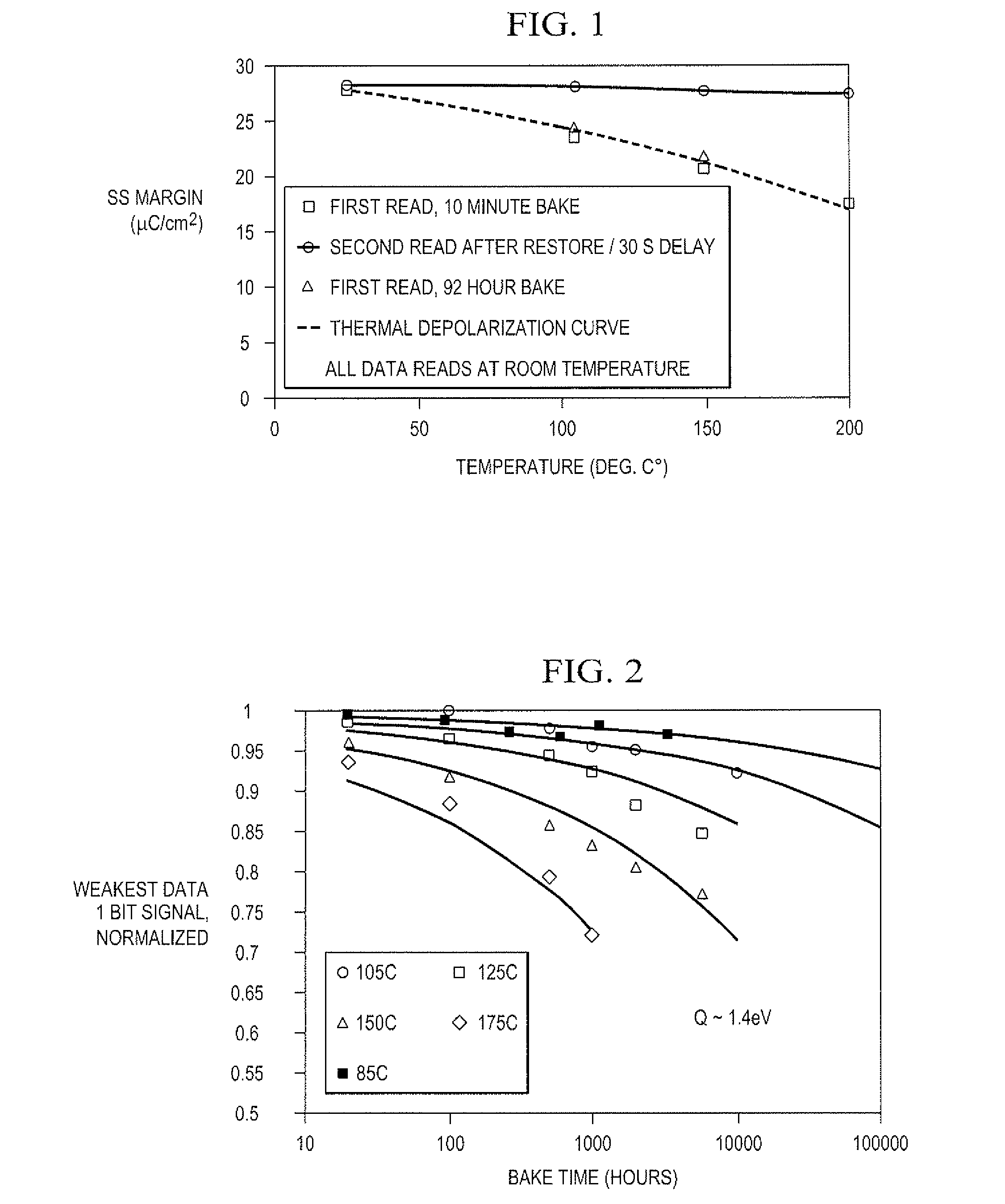

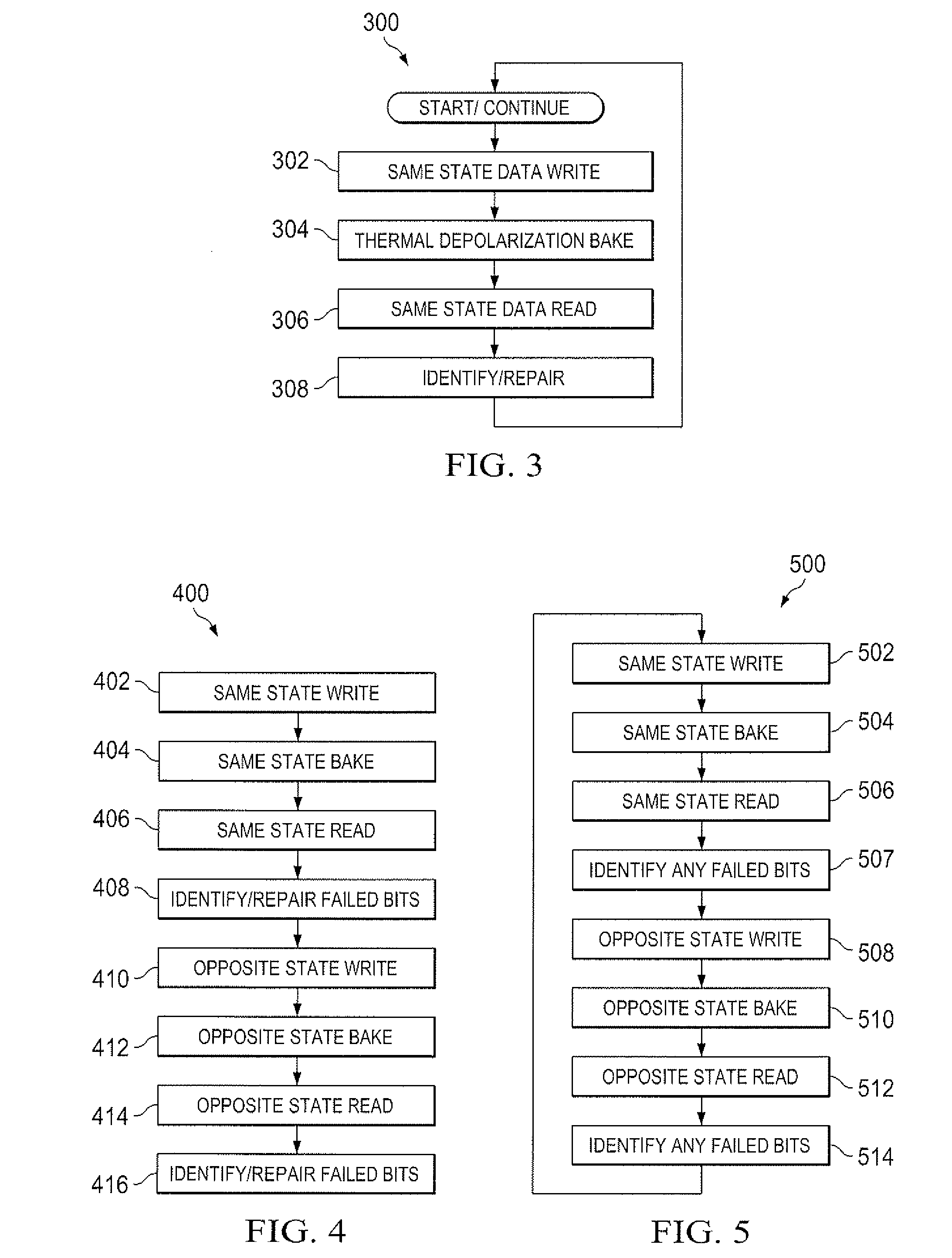

Ferroelectric memory brake for screening and repairing bits

A method (300) of identifying failing bits in a ferroelectric memory device including at least one ferroelectric capacitor includes (302) writing same state data to the first capacitor, and (304) baking the first capacitor for a first specified period of time at a first selected temperature. A same state read (306) is performed on the first capacitor after the baking. Based on the results from the same state read, it is determined whether an error occurred. The first specified period of time can be from 10 minutes to 2 hours and the first selected temperature can be in a range from 85° C. to 150° C. A repair can be performed (310) to corrected detected errors. A related method (500) can detect imprinted bits using a same state write (502), followed by a relatively high temperature bake (504), then a same state read (506). An opposite state date write (508) is performed followed by a relatively low temperature bake (510), and then an opposite state data read (512) to identify opposite state error or imprint.

Owner:TEXAS INSTR INC

Display device

InactiveUS7825877B2Improve yield and reliabilityReduce manufacturing costCathode ray tubes/electron beam tubesStatic indicating devicesActive matrixLow voltage

Owner:SEMICON ENERGY LAB CO LTD

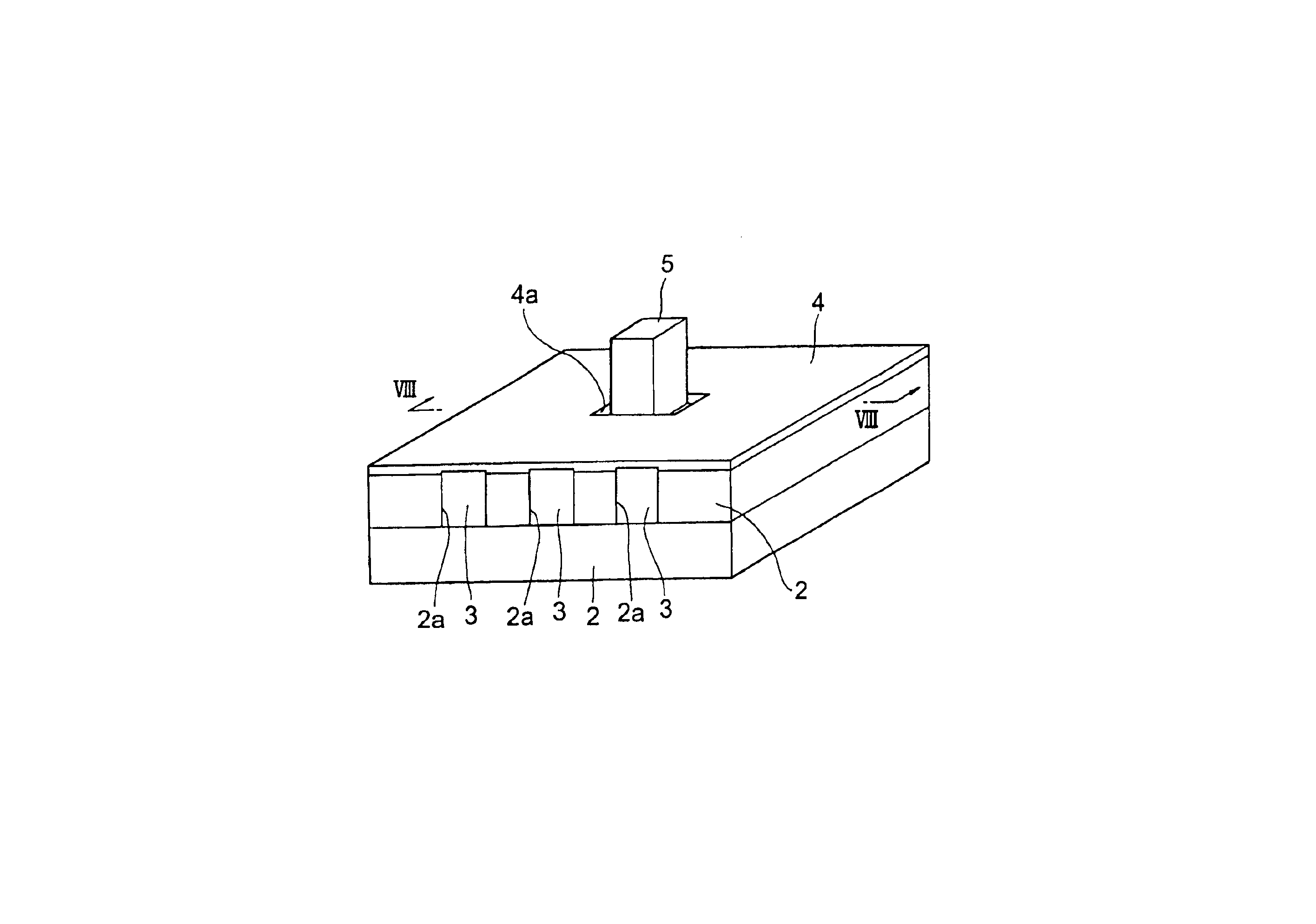

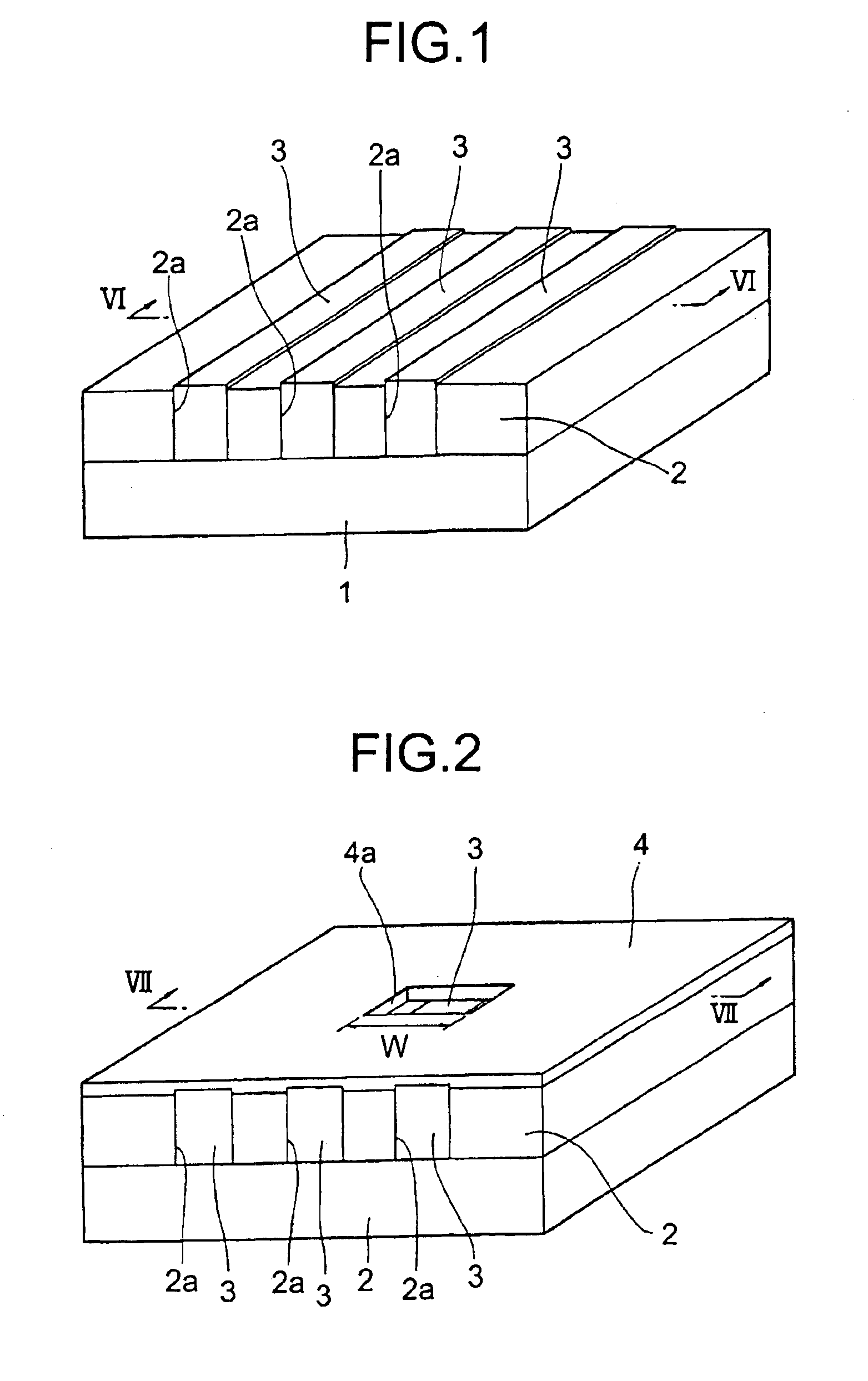

Power MOSFET with reduced dgate resistance

ActiveUS7019362B2Reduce gate resistanceImprove yield and reliabilityTransistorSemiconductor/solid-state device detailsGate resistancePower semiconductor device

The gate resistance of a power MOSFET in a semiconductor chip is reduced and the reliability and yield of the gate of the power MOSFET are improved The semiconductor chip includes two or more control electrode pads functioning as control electrodes for a power semiconductor device formed within a semiconductor chip. The two or more control electrode pads are distributed within the periphery of the gate area of the power semiconductor device such that the gate resistance of the power semiconductor device can be reduced. The two or more control electrode pads are connected via bumps or a conductive bonding material to an electrode layer of a multilayer circuit board disposed outside the semiconductor chip.

Owner:RENESAS ELECTRONICS CORP

Encapsulated semiconductor package free of chip carrier

InactiveUS6897566B2Reduce fabrication cost and structural profileImprove yield and reliabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringChip carrier

A semiconductor package and a method for fabricating the same are proposed. A chip has an active surface, and an opposing non-active surface. A plurality of conductive elements are mounted on the active surface and electrically connected to the chip. A first encapsulant is formed on the active surface of the chip, for encapsulating the active surface and conductive elements, wherein end portions of the conductive elements are exposed to outside of the first encapsulant, and adapted to be recessed in position with respect to an exposed surface of the first encapsulant. A plurality of conductive media are implanted at end portions of the conductive elements, allowing the chip to be electrically connected to an external device by the conductive elements and conductive media. A second encapsulant is formed on the non-active surface of the chip, and cooperates with the first encapsulant to provide mechanical strength for the semiconductor package.

Owner:UTAC HEADQUARTERS PTE LTD

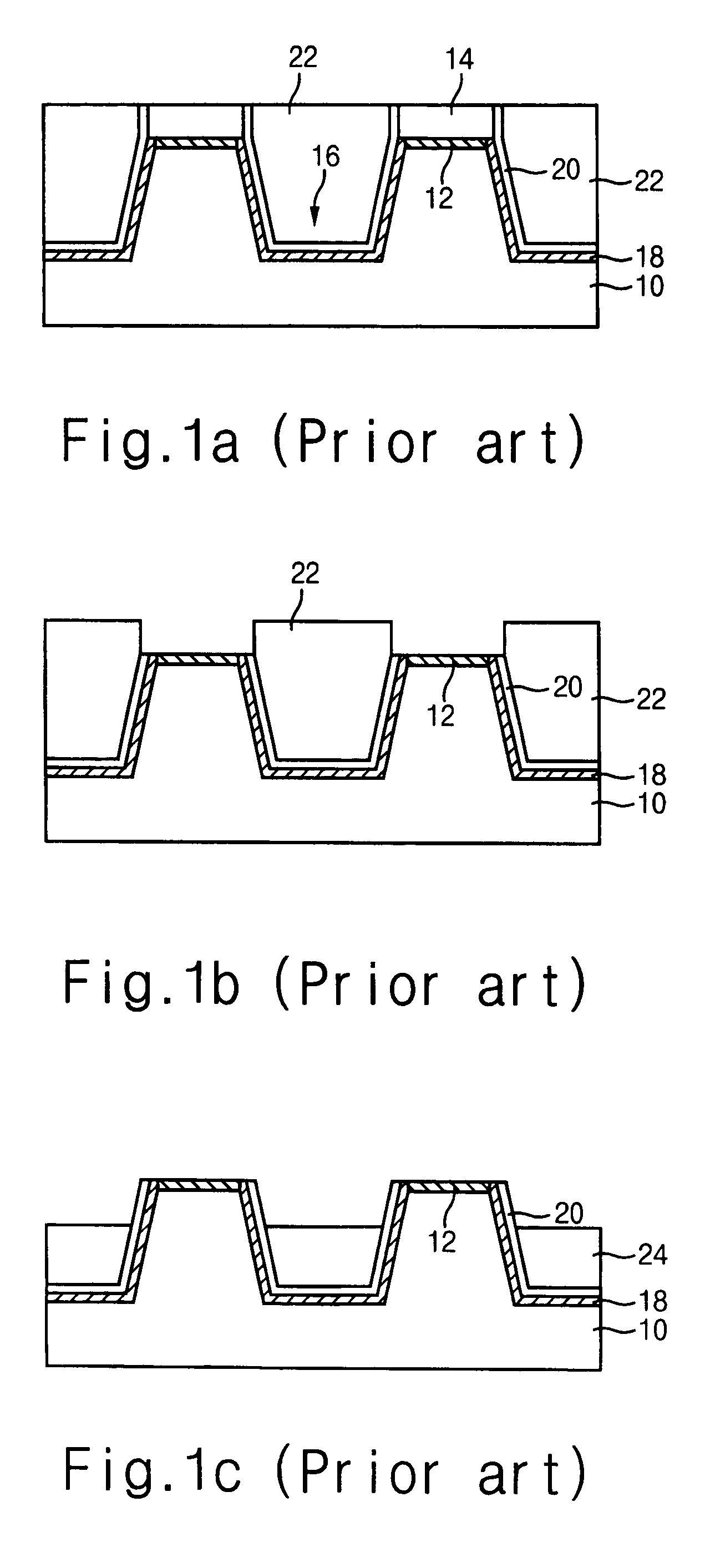

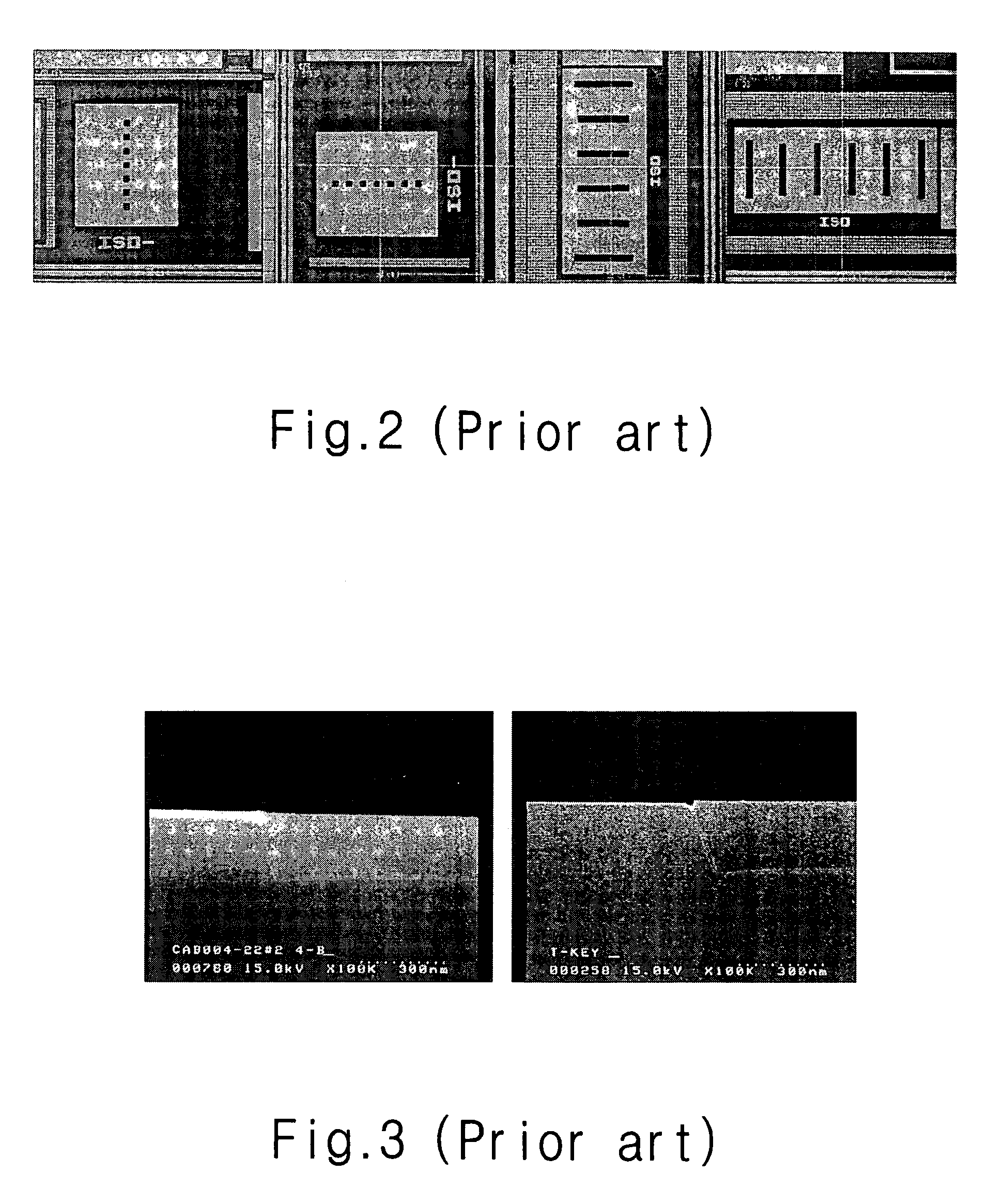

Method for manufacturing alignment mark of semiconductor device using STI process

InactiveUS6958280B2Increase contrastImprove yield and reliabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringOxide

The present invention discloses method for manufacturing alignment mark wherein a predetermined thickness of a device isolation film is etched prior to removing a pad nitride film during a shallow trench isolation process to increase contrast. In accordance with the method, a pad nitride film pattern and a pad oxide film pattern exposing a predetermined portion of the semiconductor substrate are formed. The semiconductor substrate is etched using the pad nitride film pattern as a mask to form an alignment mark trench. A device isolation film is formed in the trench and a predetermined thickness of the device isolation film is etched to form an alignment mark. The pad nitride film pattern is then removed.

Owner:SK HYNIX INC

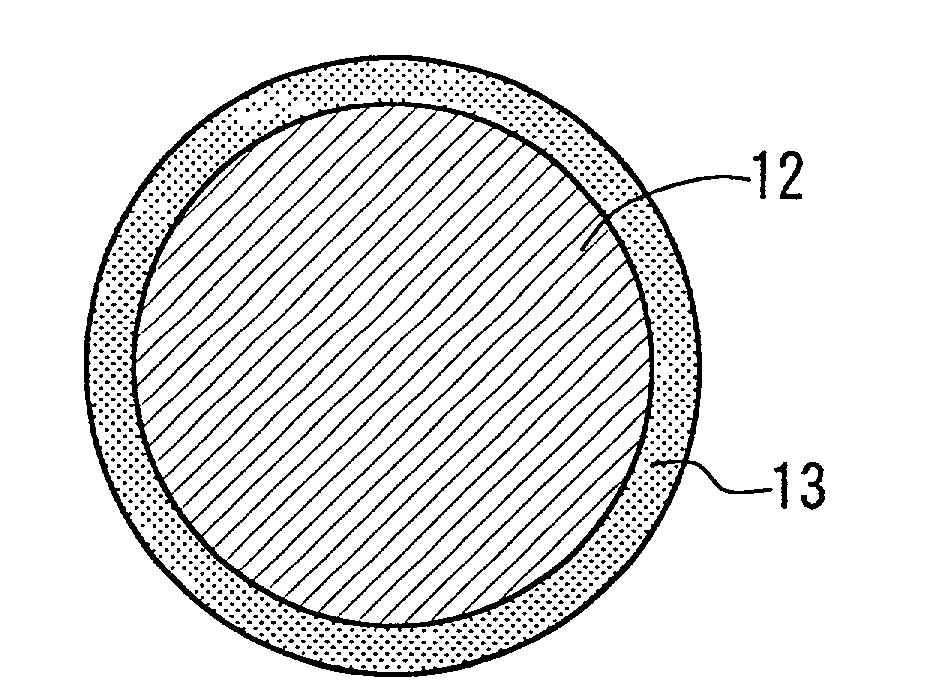

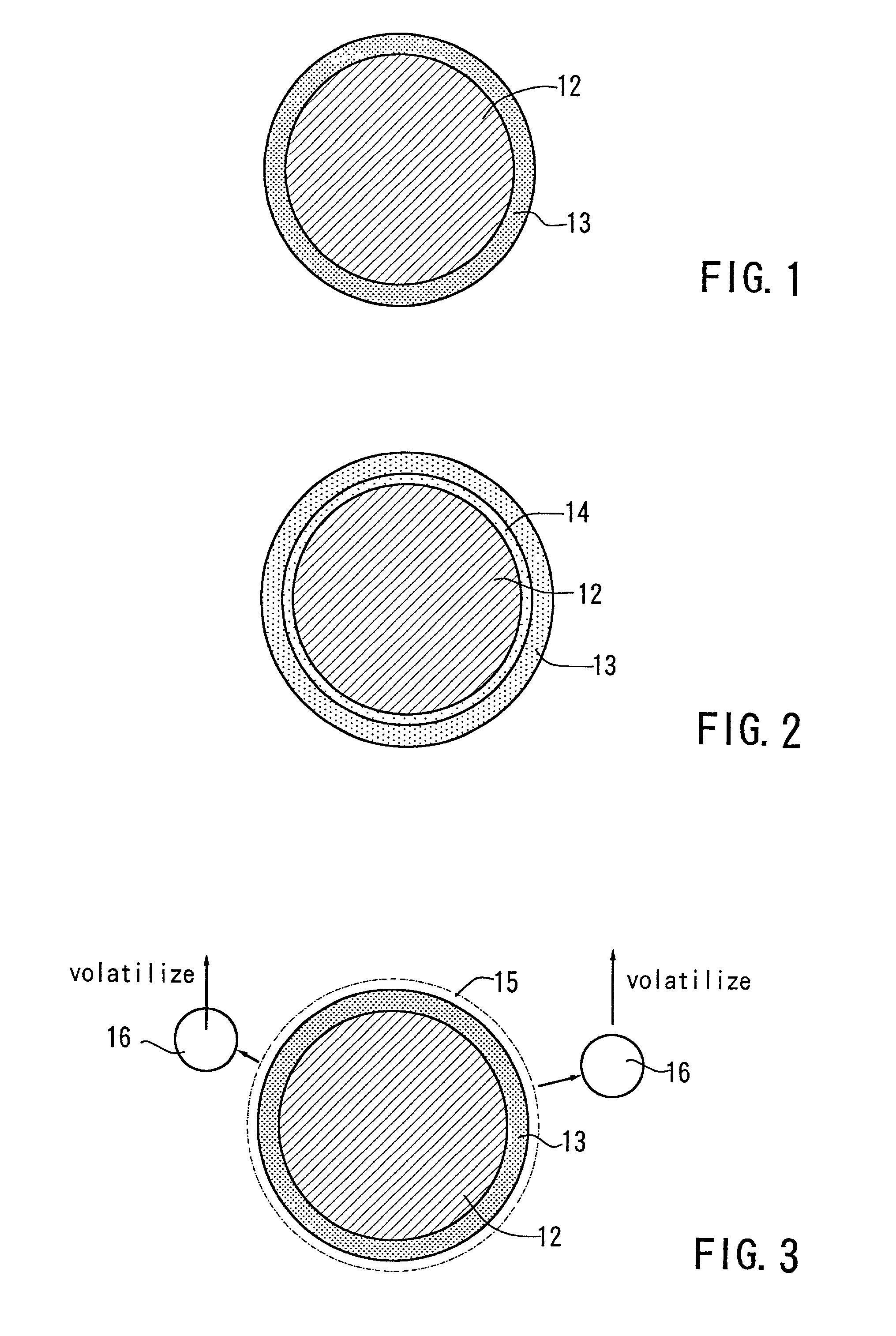

Composite substance containing metal particles, conductive paste and manufacturing method thereof

InactiveUS7001539B2Improve yield and reliabilityConductive materialNon-conductive material with dispersed conductive materialConductive pasteOrganic solvent

A composite substance for forming a conductive paste, comprises a solvent being compatible with an organic component included in the conductive paste, and metal particles wetted by the solvent. The conductive paste comprises an organic binder, the composite substance and an organic solvent mixed with the organic binder and the composite substance. The method for manufacturing the composite substance comprises the step of adding the solvent to undried metal particles having been washed with water, the solvent being compatible with the organic binder included in the conductive paste and incompatible with water so that the water is replaced by the solvent. The method for manufacturing the conductive paste comprises the step of mixing an organic binder and an organic solvent with the composite substance.

Owner:TDK CORPARATION

Sputtering target and manufacturing method therefor

ActiveUS20140318953A1High mechanical strengthImprove uniformityCellsElectric discharge tubesSputteringMiniaturization

A backing plate integrated sputtering target includes a flange part having a Vicker's hardness (Hv) of 90 or more and a 0.2% yield stress of 6.98×107 N / m2 or more. Enhancing the mechanical strength of only the flange part of the target inhibits the target from being deformed during sputtering, and further, does not vary the original sputtering characteristics. Consequently, the target can form a thin film having excellent uniformity. This can improve the yield and the reliability of semiconductor products, which have been progressing in miniaturization and integration.

Owner:JX NIPPON MINING& METALS CORP

Semiconductor device and method of manufacturing the same

InactiveUS6876079B2Improve coupling strengthHigh mechanical strengthSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor

The present invention is to improve yield and reliability in a wiring step of a semiconductor device. When an Al wiring on an upper layer is connected through an connection pillar onto an Al wiring on a lower layer embedded in a groove formed on an interlayer insulation film, a growth suppression film having an opening whose width is wider than that of the Al wiring is formed on the interlayer insulation film and the Al wiring. In this condition, Al and the like are grown by a selective CVD method and the like. Accordingly, the connection pillar is formed on the Al wiring within the opening, in a self-matching manner with respect to the Al wiring.

Owner:SONY CORP

Method of wafer level packaging and cutting

InactiveUS20070166958A1Easy to cutAvoid damageSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringElectrical and Electronics engineering

A packaging wafer having a plurality of cavities on an upper surface thereof is provided. A plurality of trenches is formed between the cavities, wherein the packaging wafer has a thickness greater than a depth of the trenches. The packaging wafer is bonded to an element wafer and a hermetical window is formed from each cavity. Then, a cutting process is performed and an unbound part of the packaging wafer is removed. Therefore, a wafer level package is formed. Finally, the wafer level package is divided into a plurality of individual packages.

Owner:TOUCH MICRO SYST TECH

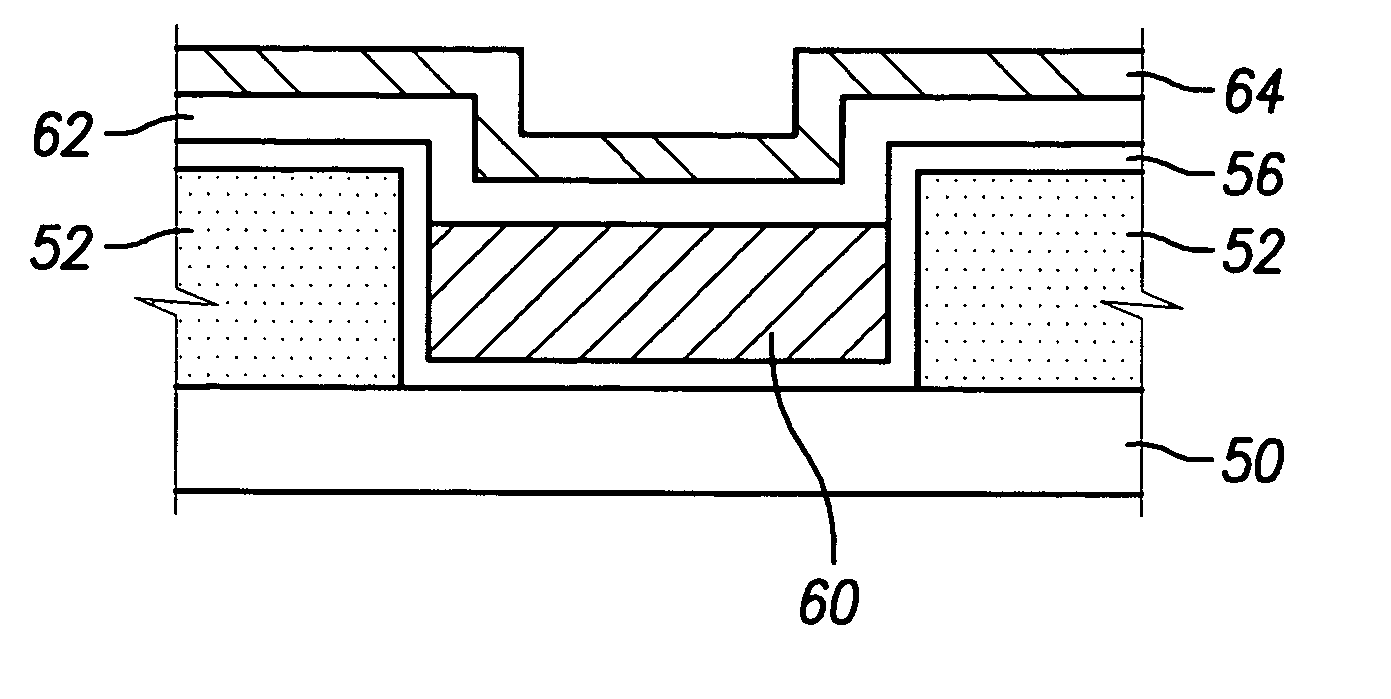

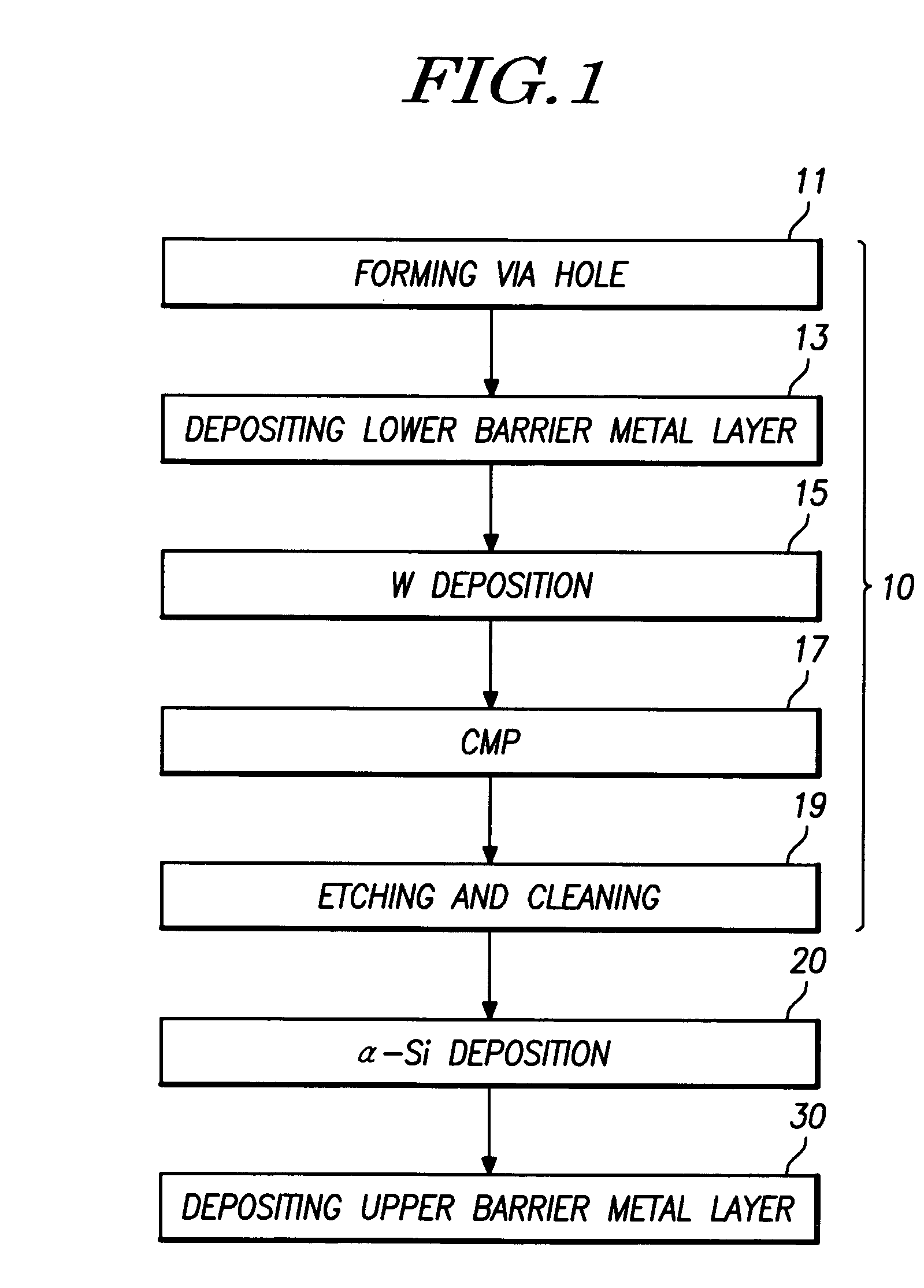

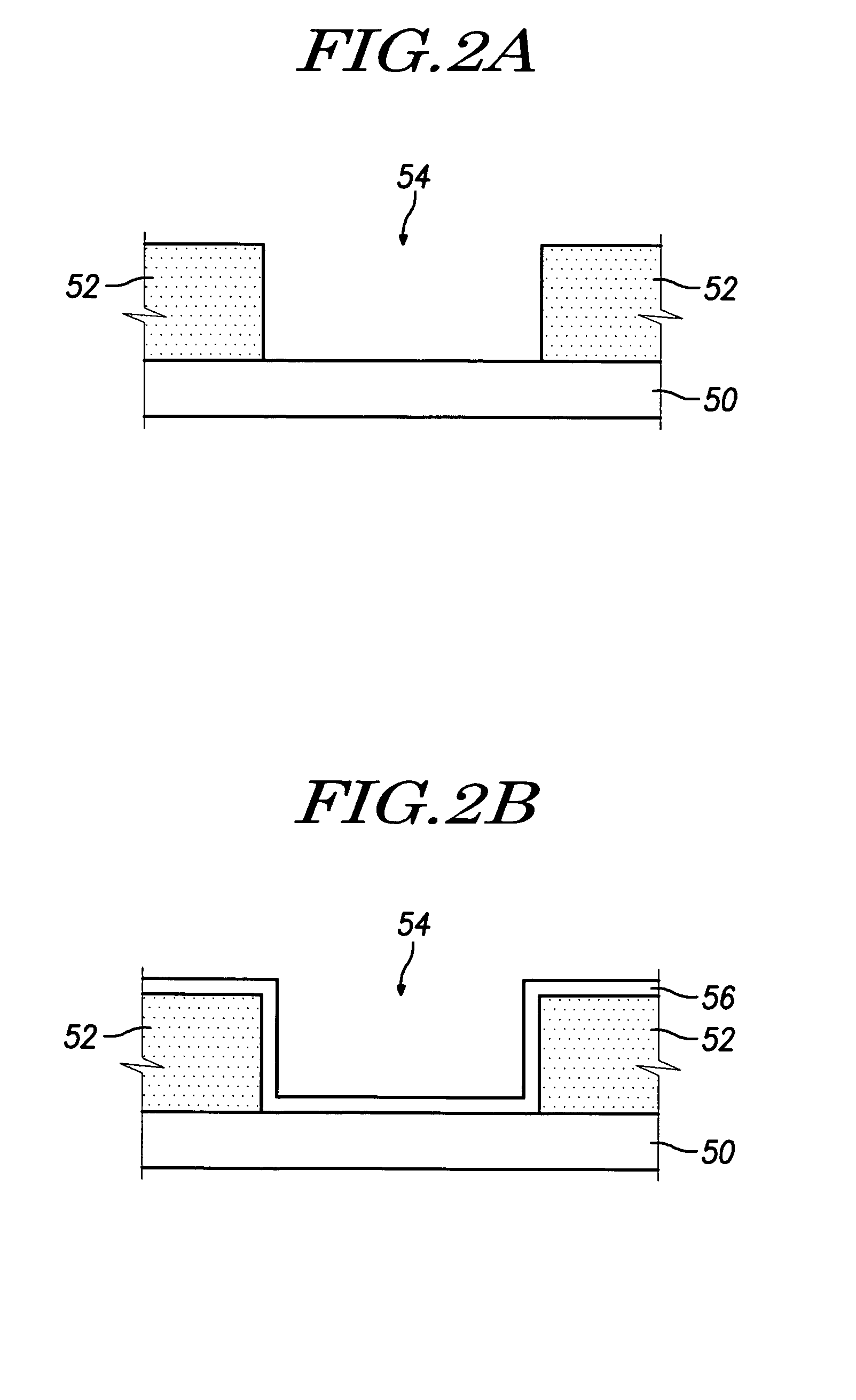

Antifuse having uniform dielectric thickness and method for fabricating the same

InactiveUS20060145292A1Facilitate formation of silicideImprove uniformitySemiconductor/solid-state device detailsSolid-state devicesAmorphous siliconAntifuse

Disclosed are an antifuse having a uniform amorphous silicon (antifuse material) thickness and a method for fabricating such an antifuse device. The antifuse is located between overlying and underlying conductive layers, and includes: a contact and / or via hole in an insulating layer on the underlying conductive layer; a lower metal layer contacting inner surfaces of the contact and / or via hole and a top surface of the insulating layer; a filling layer contacting the lower barrier metal layer and at least partially filling the contact and / or via hole; an antifuse material layer contacting a top surface of the filling layer and a part of the lower metal layer; and an upper metal layer on the antifuse material layer.

Owner:DONGBU ELECTRONICS CO LTD

Ferroelectric memory brake for screening and repairing bits

A method (300) of identifying failing bits in a ferroelectric memory device including at least one ferroelectric capacitor includes (302) writing same state data to the first capacitor, and (304) baking the first capacitor for a first specified period of time at a first selected temperature. A same state read (306) is performed on the first capacitor after the baking. Based on the results from the same state read, it is determined whether an error occurred. The first specified period of time can be from 10 minutes to 2 hours and the first selected temperature can be in a range from 85° C. to 150° C. A repair can be performed (310) to corrected detected errors. A related method (500) can detect imprinted bits using a same state write (502), followed by a relatively high temperature bake (504), then a same state read (506). An opposite state date write (508) is performed followed by a relatively low temperature bake (510), and then an opposite state data read (512) to identify opposite state error or imprint.

Owner:TEXAS INSTR INC