Analog decision feedback equalization circuit for high-speed SerDes

A decision feedback equalization and circuit technology, applied in analog/digital conversion calibration/testing, electrical components, analog/digital conversion, etc., can solve the problems of large area and insufficient multiplier speed, reduce the device area and increase the maximum speed , the effect of fast speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] The technical solutions of the present invention are clearly and completely described below in conjunction with the accompanying drawings and specific embodiments. Obviously, the described embodiments are only a part of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by those skilled in the art without making creative work are all Belong to the protection scope of the present invention.

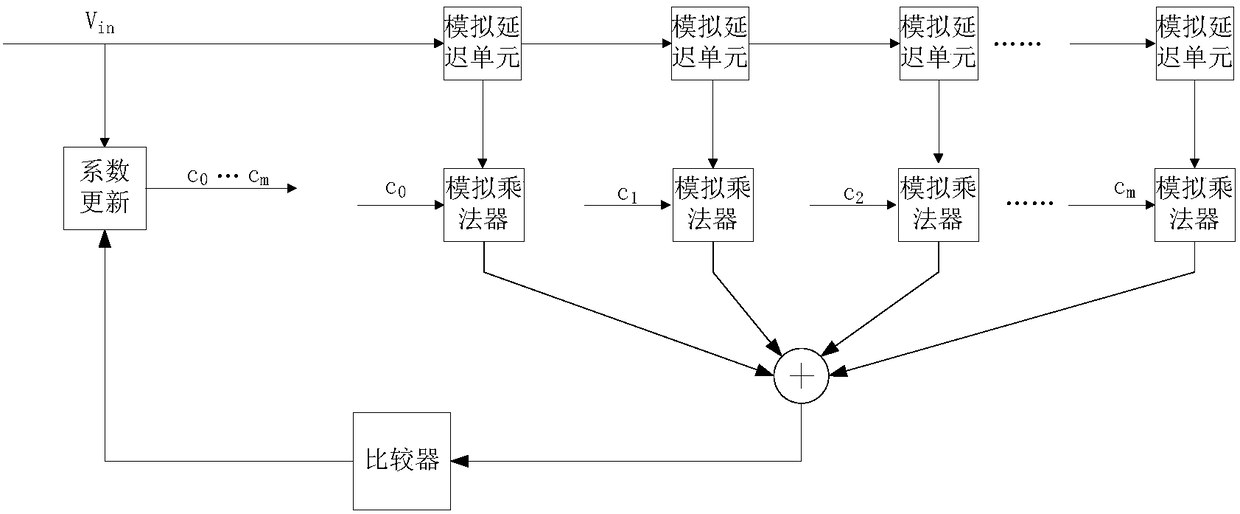

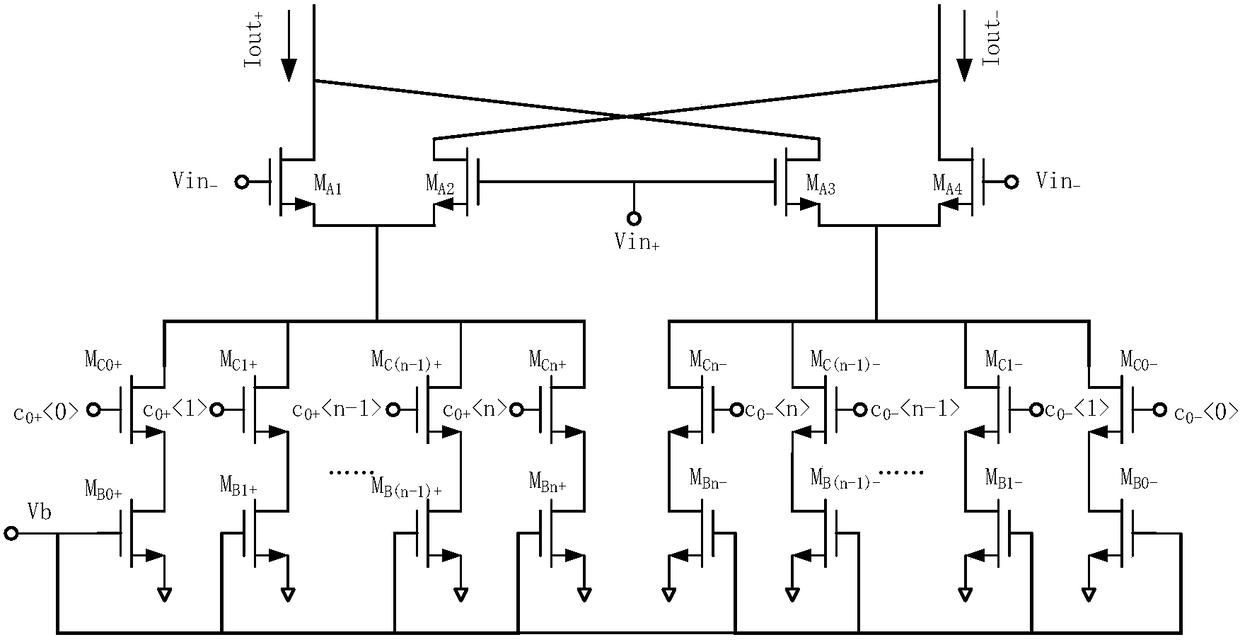

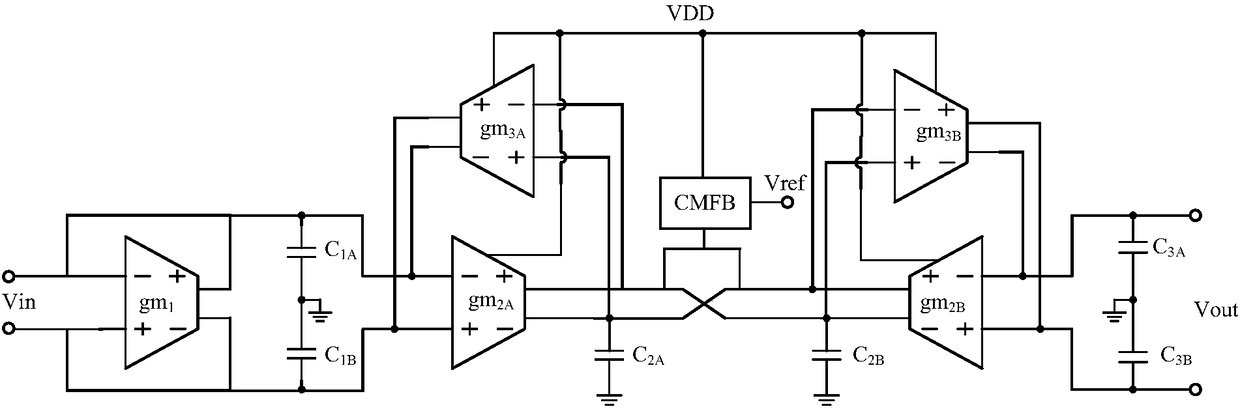

[0015] An analog DFE circuit for high-speed SerDes, including a delay unit, a multiplier, and a coefficient update circuit, the coefficient update circuit generates coefficients through a symbolic LMS algorithm; it is characterized in that: the delay unit and the multiplier are analog delay units and analog multiplication The signal delay is realized by an analog delay unit; the coefficient is multiplied by the output signal of the analog delay unit by an analog multiplier; the output of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More