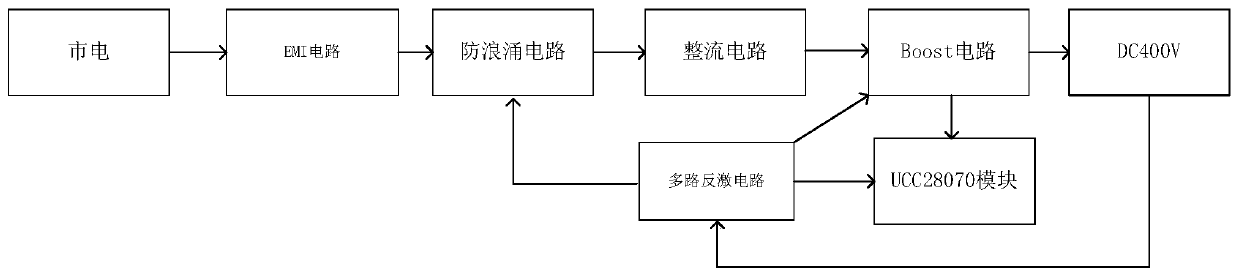

A 6-way interleaved parallel boost PFC circuit

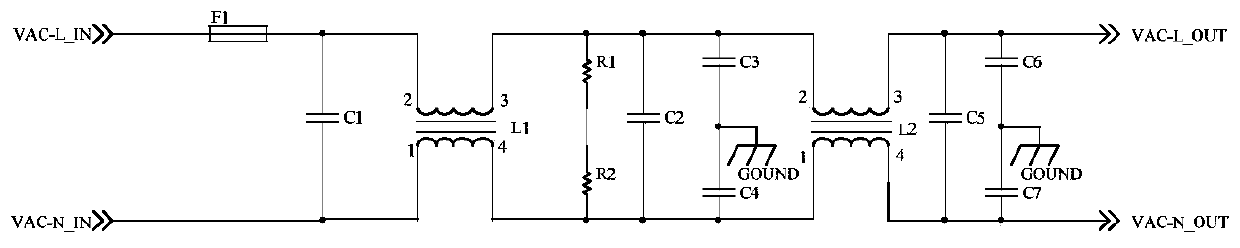

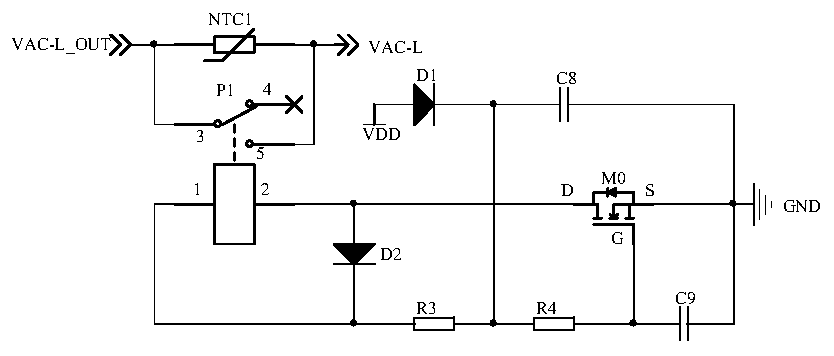

A circuit and parallel technology, applied in electrical components, regulating electrical variables, high-efficiency power electronic conversion, etc., can solve the problems of small output power, large current and voltage withstand of switching devices, large current ripple, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The technical solutions provided by the present invention will be further described below in conjunction with the accompanying drawings.

[0030] In the prior art, improving the power of PFC generally proceeds from the following aspects, one is the application of new power devices; Nowadays, two-stage interleaved parallel power factor correction can handle most applications, and its power can reach 5KW or even higher. For example, the UCC28070 chip produced by TI provides a two-stage interleaved circuit design. However, how to use the existing two-level interleave chip to realize multi-level interleave has become an urgent problem to be solved in the prior art.

[0031] The technical idea of the present invention is to use a synchronous clock signal to combine multiple PFC chips. For example, three UCC28070 chips are separated by providing synchronous signals for chip working periods. Because a single UCC28070 chip provides a two-stage interleaved circuit design, Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com