Design method of parallel pseudorandom sequence generator based on FPGA

A pseudo-random sequence and design method technology, applied in the field of pseudo-random sequence generators, can solve the problem that serial pseudo-random sequence generators cannot reach such a high rate, and achieve high clock operation speed, high clock operation frequency, and low occupancy The effect of less logic resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be described below in conjunction with the accompanying drawings.

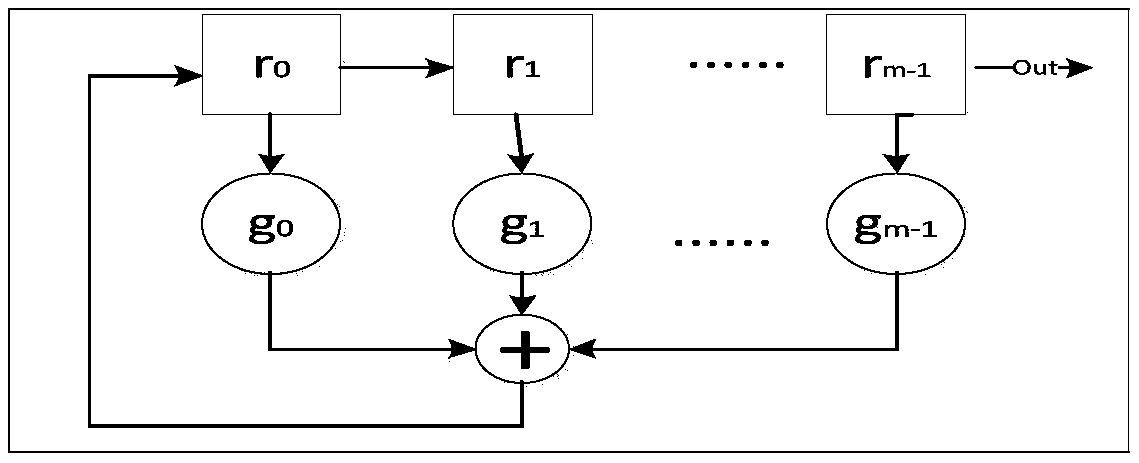

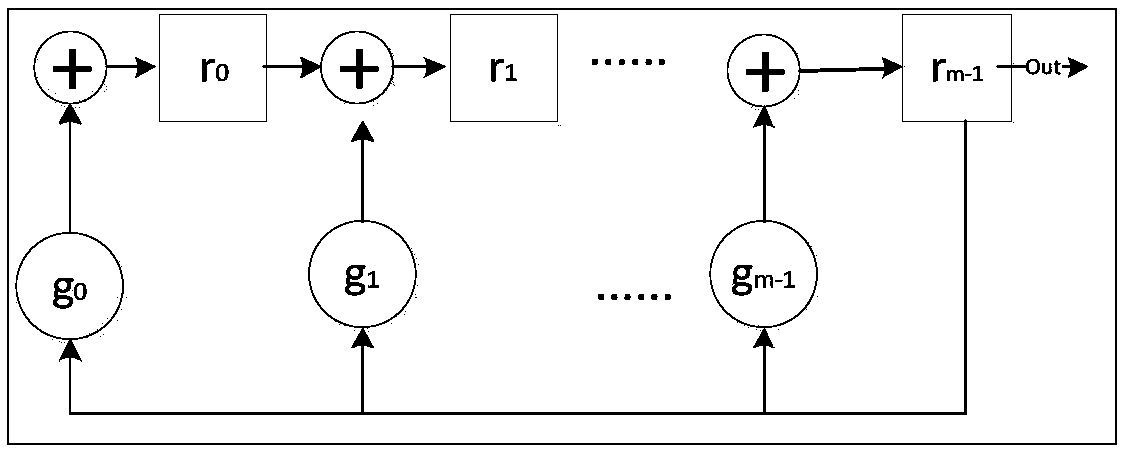

[0022] like figure 1 and figure 2 The two traditional LFSR structures are shown, and the generated pseudo-random sequence is expressed as: r m-1 (0), r m-1 (1), r m-1 (2), r m-1 (3), r m-1 (4)..., wherein, the pseudo-random sequence output of the Fibonacci LFSR structure can also be expressed as follows: r m-1 (0), r m-2 (0), r m-3 (0)...r 1 (0), r 0 (0), r m-1 (m), r m-2 (m), r m-3 (m)...r 1 (m), r 0 (m)..., that is, at the same time, the Fibonacci LFSR structure can output m continuous pseudo-random sequences in parallel.

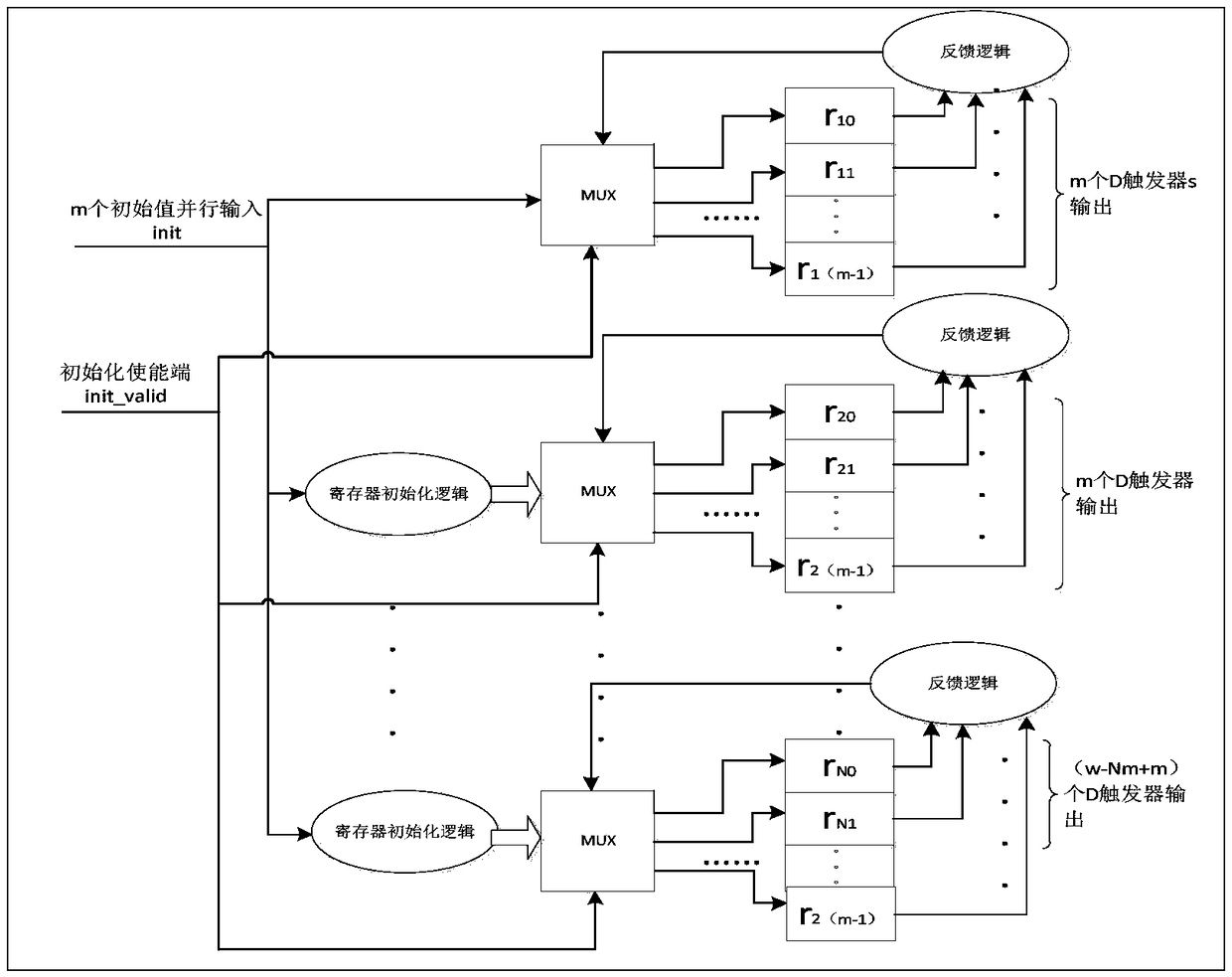

[0023] like image 3 as shown,

[0024] Considering w=8-bit parallel output, the output of each D flip-flop at the next moment should be the last wth sampling value of the corresponding serial output. At the i-th moment, the output states of the m D flip-flops in the Fibonacci LFSR structure are exactly w bits and output the first m bi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More