Shift register unit, driving method thereof, gate driving circuit, and display device

A technology of a shift register and a driving method, which is applied in the field of a gate drive circuit, a shift register unit and its drive, and a display device, and can solve problems such as poor display and tailing of a gate scanning signal

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

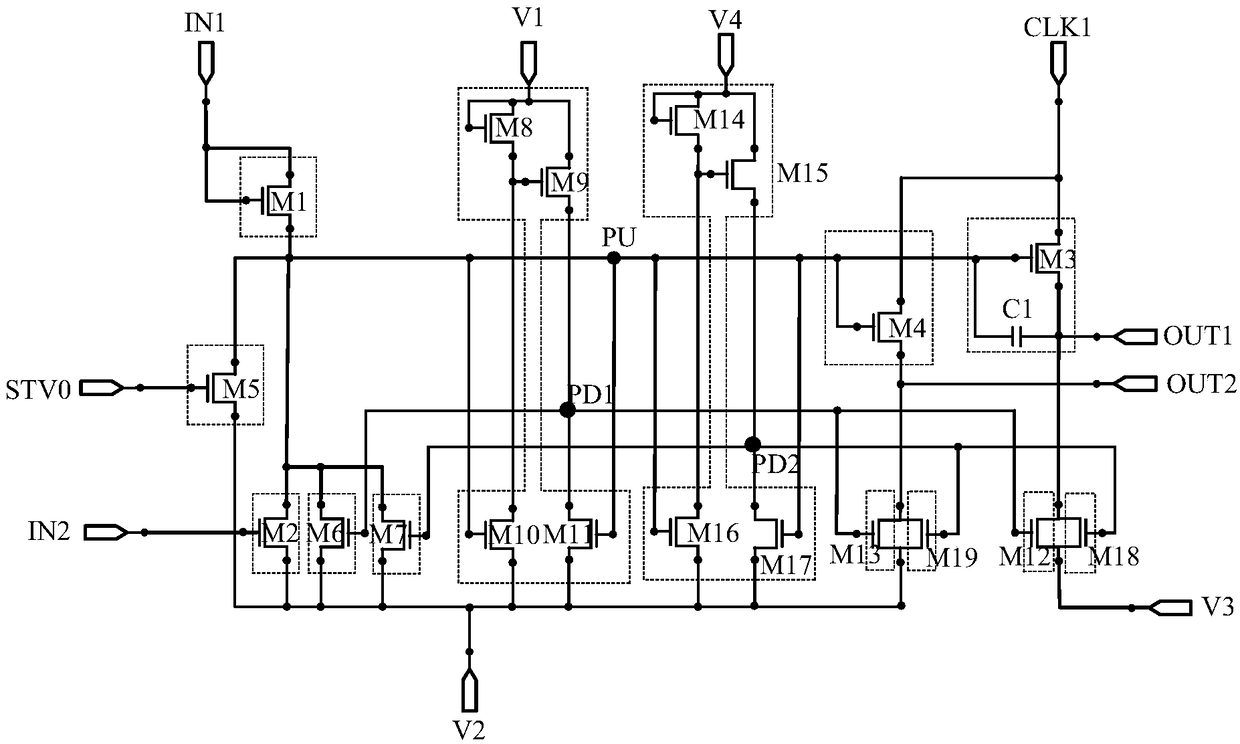

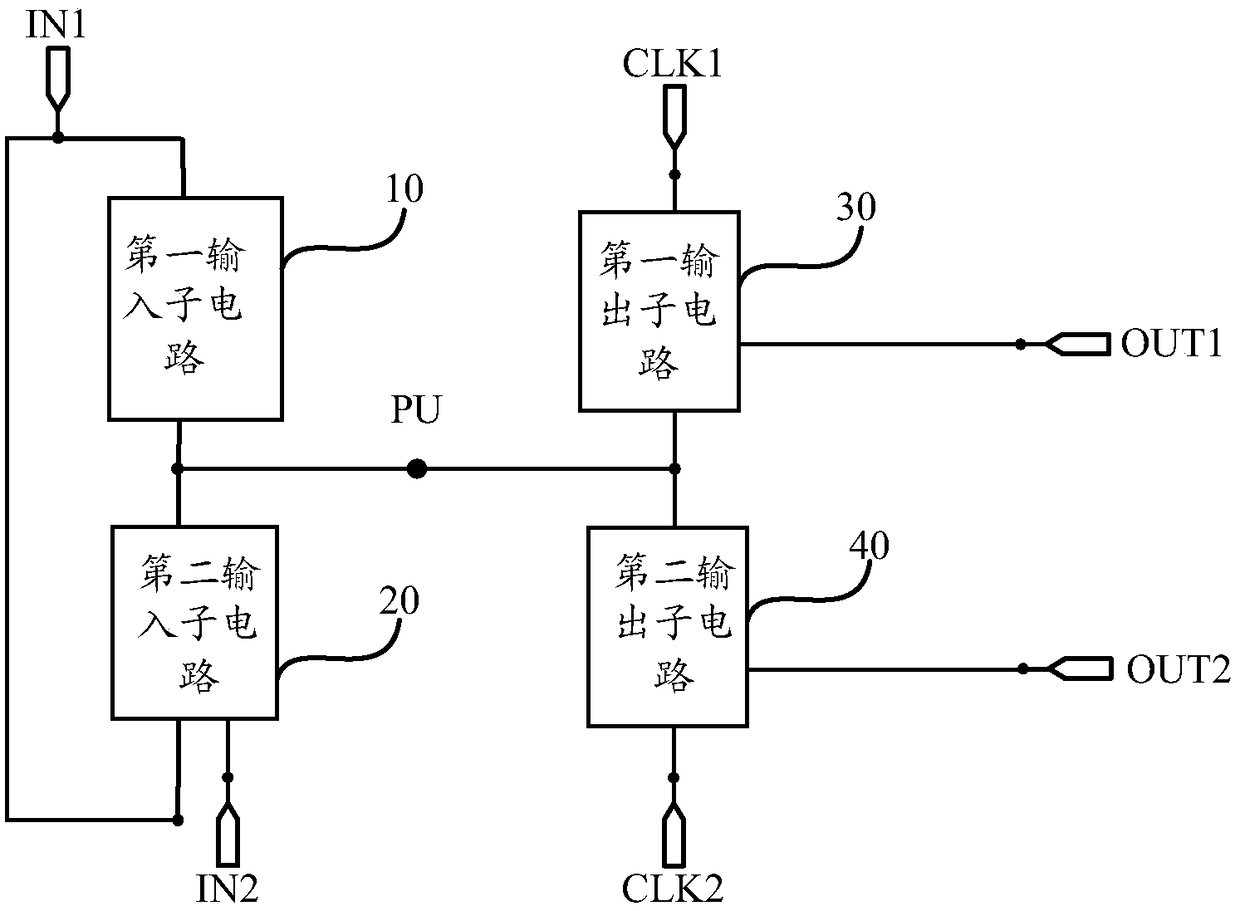

[0090] The first input sub-circuit 10 includes a first transistor M1, the gate of the first transistor M1 is connected to the first signal input terminal IN1, the first pole of the first transistor M1 is connected to the first signal input terminal IN1, and the second electrode of the first transistor M1 is connected to the first signal input terminal IN1. The pole is connected to the pull-up node PU.

[0091] The second input sub-circuit 20 includes a second transistor M2, the gate of the second transistor M2 is connected to the second signal input terminal IN2, the first pole of the second transistor M2 is connected to the pull-up node PU, and the second pole of the second transistor M2 is connected to The first signal input terminal IN1.

[0092] The first output sub-circuit 30 includes a third transistor M3 and a storage capacitor C, the gate of the third transistor M3 is connected to the pull-up node PU, the first pole of the third transistor M3 is connected to the first cl...

Embodiment 2

[0105] The first input sub-circuit 10 includes a first transistor M1, the gate of the first transistor M1 is connected to the first signal input terminal IN1, the first pole of the first transistor M1 is connected to the first signal input terminal IN1, and the second electrode of the first transistor M1 is connected to the first signal input terminal IN1. The pole is connected to the pull-up node PU.

[0106] The second input sub-circuit 20 includes a second transistor M2, the gate of the second transistor M2 is connected to the second signal input terminal IN2, the first pole of the second transistor M2 is connected to the pull-up node PU, and the second pole of the second transistor M2 is connected to The first signal input terminal IN1.

[0107] The first output sub-circuit 30 includes a third transistor M3 and a storage capacitor C, the gate of the third transistor M3 is connected to the pull-up node PU, the first pole of the third transistor M3 is connected to the first ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More