Display device

A display device and display panel technology, applied in static indicators, instruments, etc., can solve problems such as poor picture, and achieve the effect of reducing extra power consumption and saving circuit space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

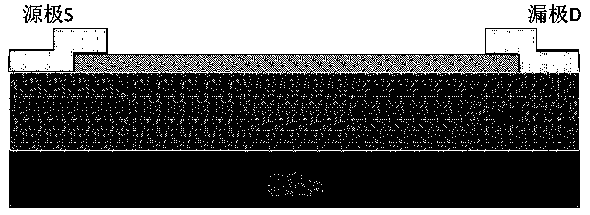

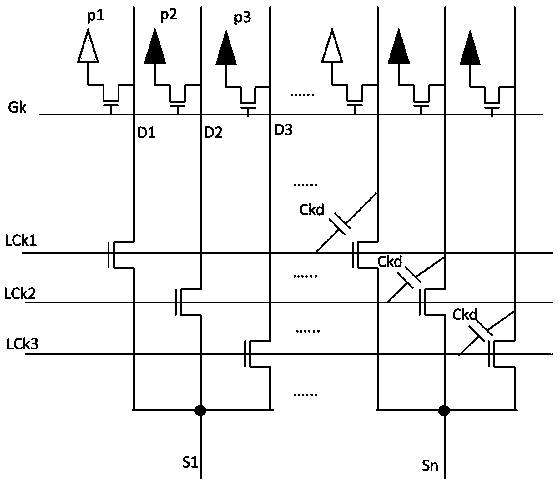

[0059] Figure 8 It is a schematic diagram of a partial structure of a display device in an embodiment of the present invention. The Mux ratio of the demultiplexing circuit in this embodiment is 1:3.

[0060] Taking the switch group connected to the first data line S1 and the corresponding multiple second data lines D1, D2, D3 as an example, the switch group includes 3 strobe switches M1, M2, M3, 3 strobe switches M1, The first channel ends of M2 and M3 are connected to each other and connected to the first data line S1, and the second channel ends of the gating switches M1, M2, M3 are respectively connected to three second data lines D1, D1, and D1 in the same second data line group. D2, D3, the control ends of the gating switches M1, M2, M3 are respectively connected to the switch control lines LCK1, LCK2, LCK3, and the gating parasitic capacitance Ckd1 is generated between the control ends of the gating switches M1, M2, M3 and the second channel end respectively , Ckd2, Ck...

Embodiment 2

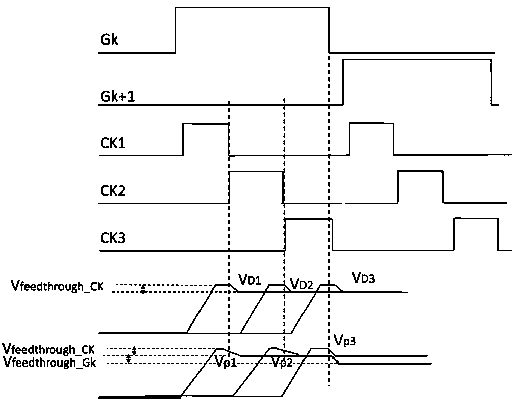

[0068] The difference between the second embodiment and the first embodiment is that the falling edge of the last switch signal (ie, the switch signal CK3 ) is no later than the falling edge of the high-level phase of the scanning signal Gk.

[0069] In Embodiment 2, the waveforms of scanning signals Gk, Gk+1, switch control signals CK1, CK2, CK3 and compensation signals CK1', CK2' are as follows Figure 13 shown. Since the closing of the gate switch M3 will not only affect the potential V of the second data line D3 D 3, it will also affect the pixel voltage Vp3. When the last strobe switch is closed, the falling edges of the compensation signals CK1' and CK2' occur at the same time, and the compensation signals CK1' and CK2' cause the pixel voltage Vp1 and Vp2 The generated compensation voltage difference and the gate feed-through voltage (V feedthrough_CK ) is consistent in magnitude and positive or negative, the compensation voltage difference and the gate feed-through vo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More