Fault simulation method of logic circuit single-particle double-fault

A logic circuit and fault simulation technology, applied in electronic circuit testing, measuring electricity, measuring electrical variables, etc., can solve the problems of inaccurate fault model analysis, incomplete processing, and low fault simulation efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

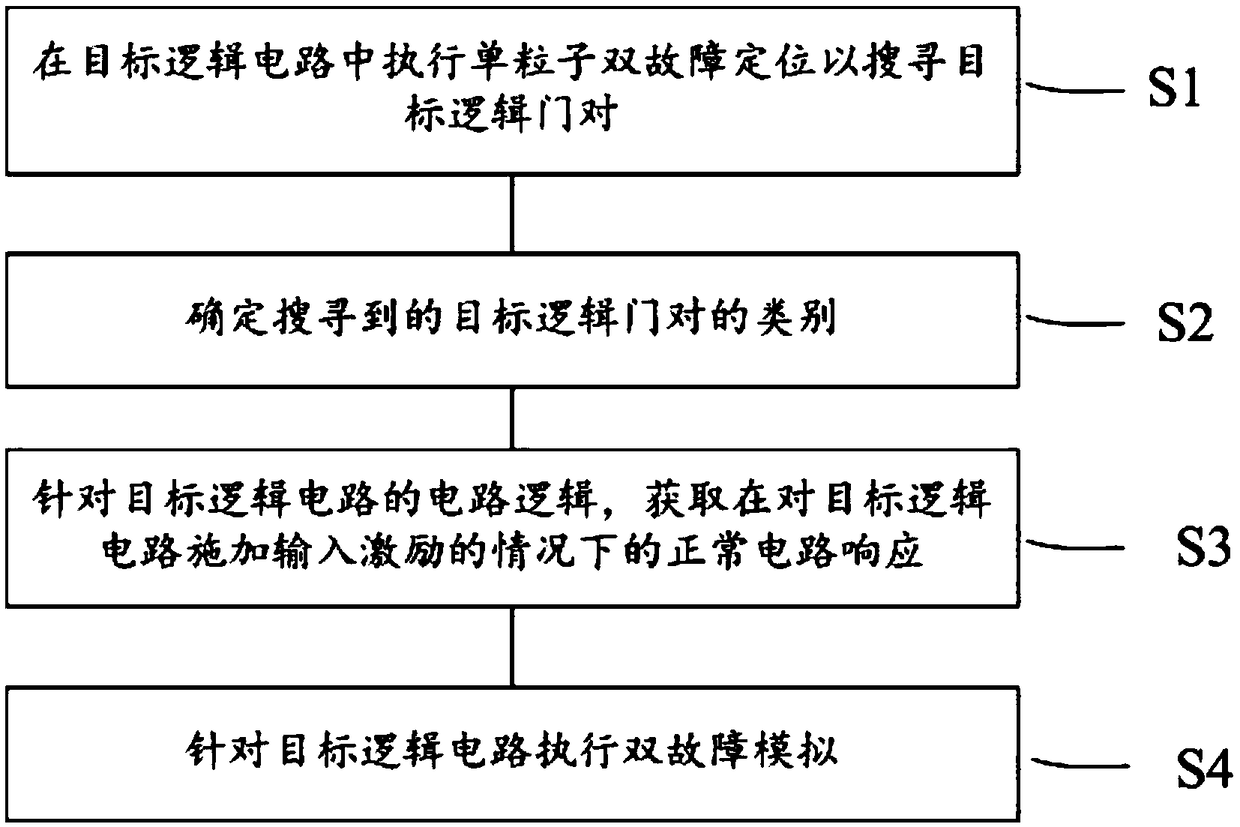

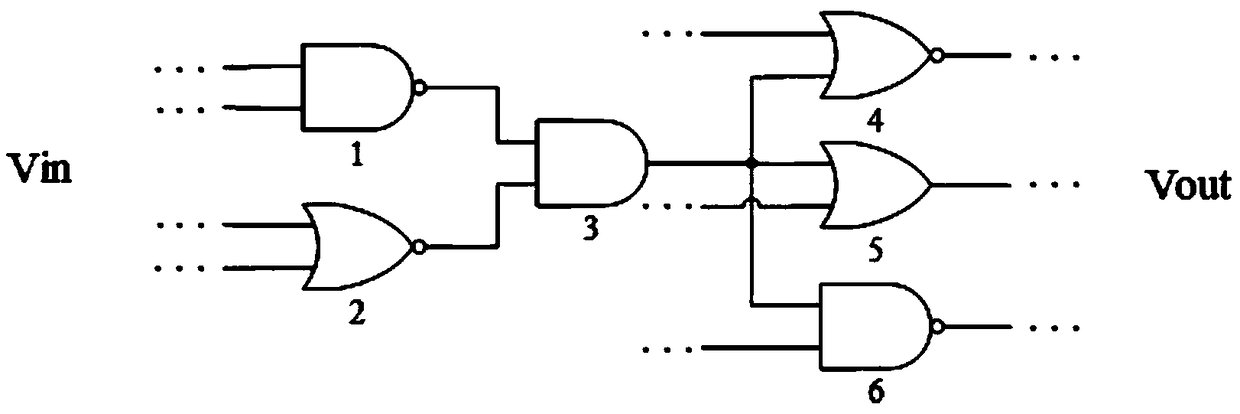

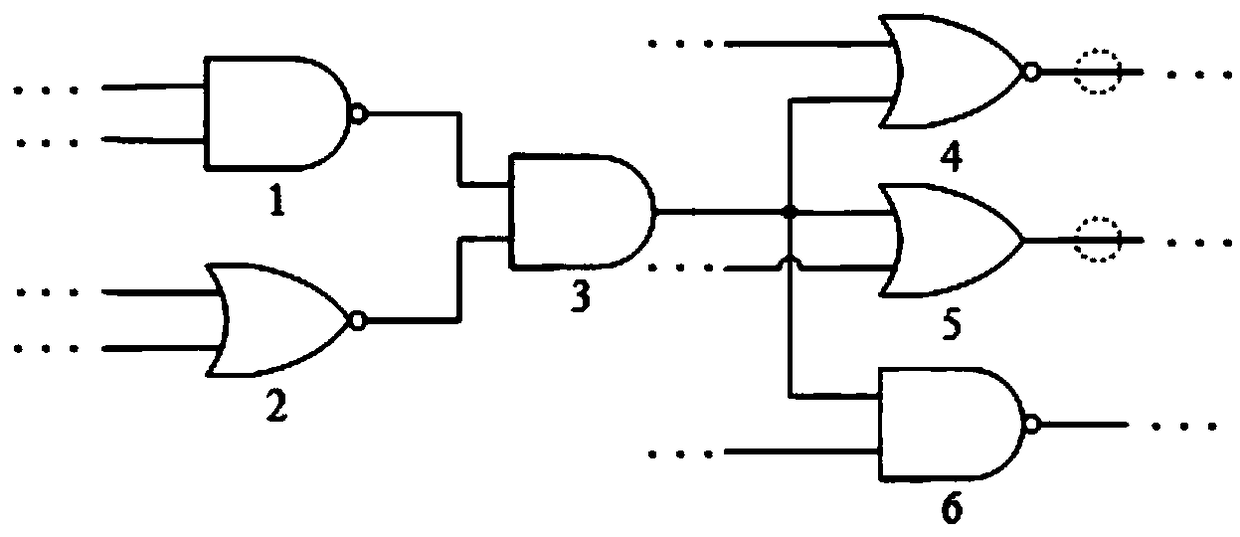

[0029] After the manufacturing process of integrated circuits enters the nanometer scale, due to the use of pipeline design and the continuous increase of the operating frequency of the circuit, the single event transient fault pulse caused by the impact of high-energy particles on the circuit is less and less affected by electrical shielding and time window shielding. Logic shielding effect occupies a dominant position among many factors affecting fault propagation. Based on this, the present invention is proposed. The invention establishes a fault model according to the actual situation, and performs fault location on a single particle and double faults. There are three types of double fault locations: the first type, the two fault target gat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More