Three-dimensional computing chip comprising three-dimensional memory array

A computing chip, three-dimensional storage technology, applied in electrical components, electrical solid-state devices, circuits, etc., can solve problems such as disadvantage of high-performance computing of processors, unsuitable for massive computing parameters, and slow external memory.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

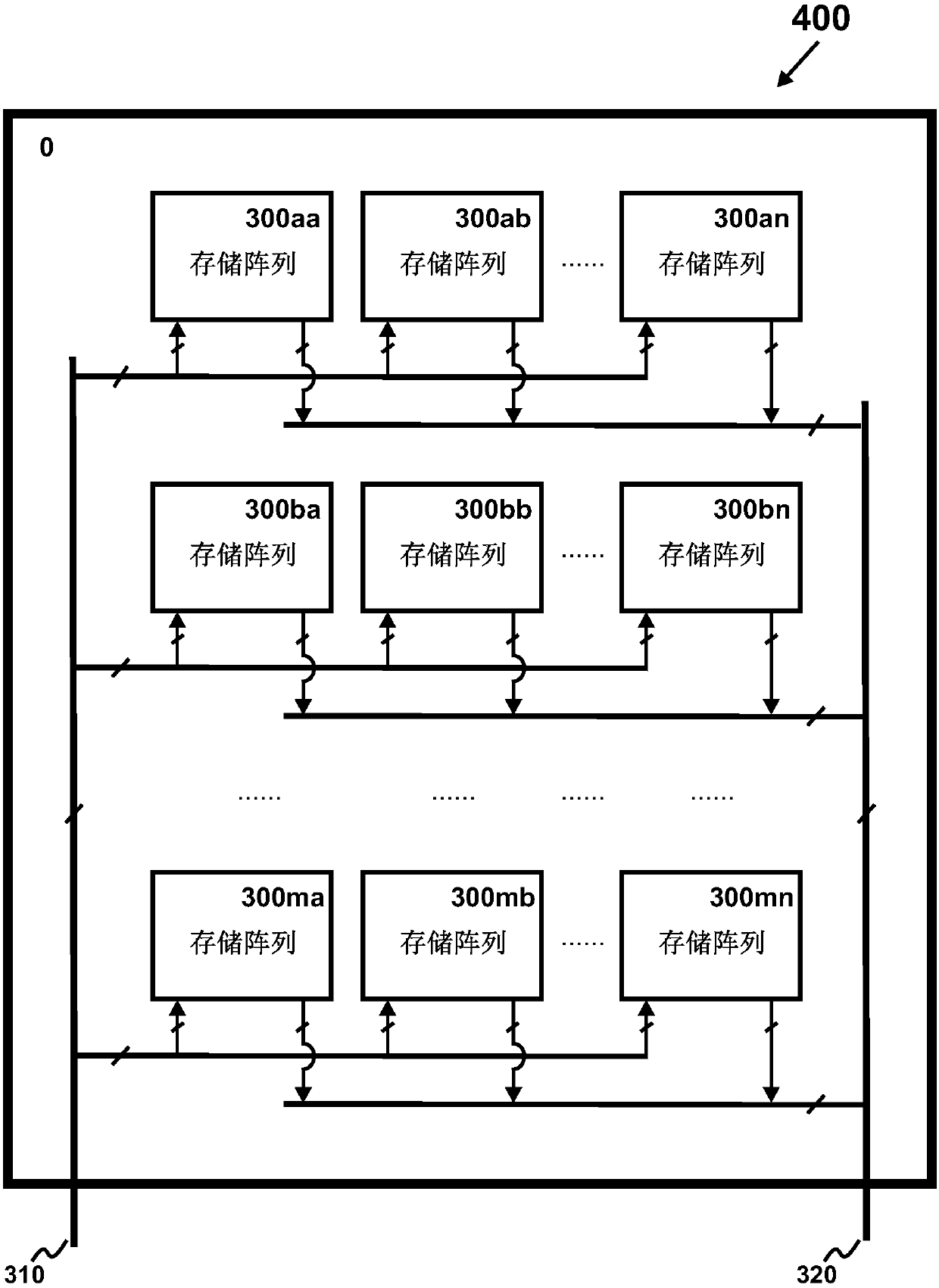

[0025] Figure 3AIt represents a three-dimensional computing (3D-COM) chip 200 , which stores massive computing parameters in the 3D-M array 170 inside the chip 200 . The 3D-COM chip 200 is formed in a semiconductor substrate 0 , which contains m x n storage units 100aa-100mn, and the storage unit is the smallest repeating unit of the 3D-COM chip 200 . Each storage unit is electrically coupled to an input 110 and an output 120 . Note that a 3D-COM chip 200 may contain thousands of storage units 100aa-100mn. For example, a 3D-COM chip 200 with a storage capacity of 128Gb contains 64,000 storage units. A large number of storage units guarantee ultra-large-scale parallel computing.

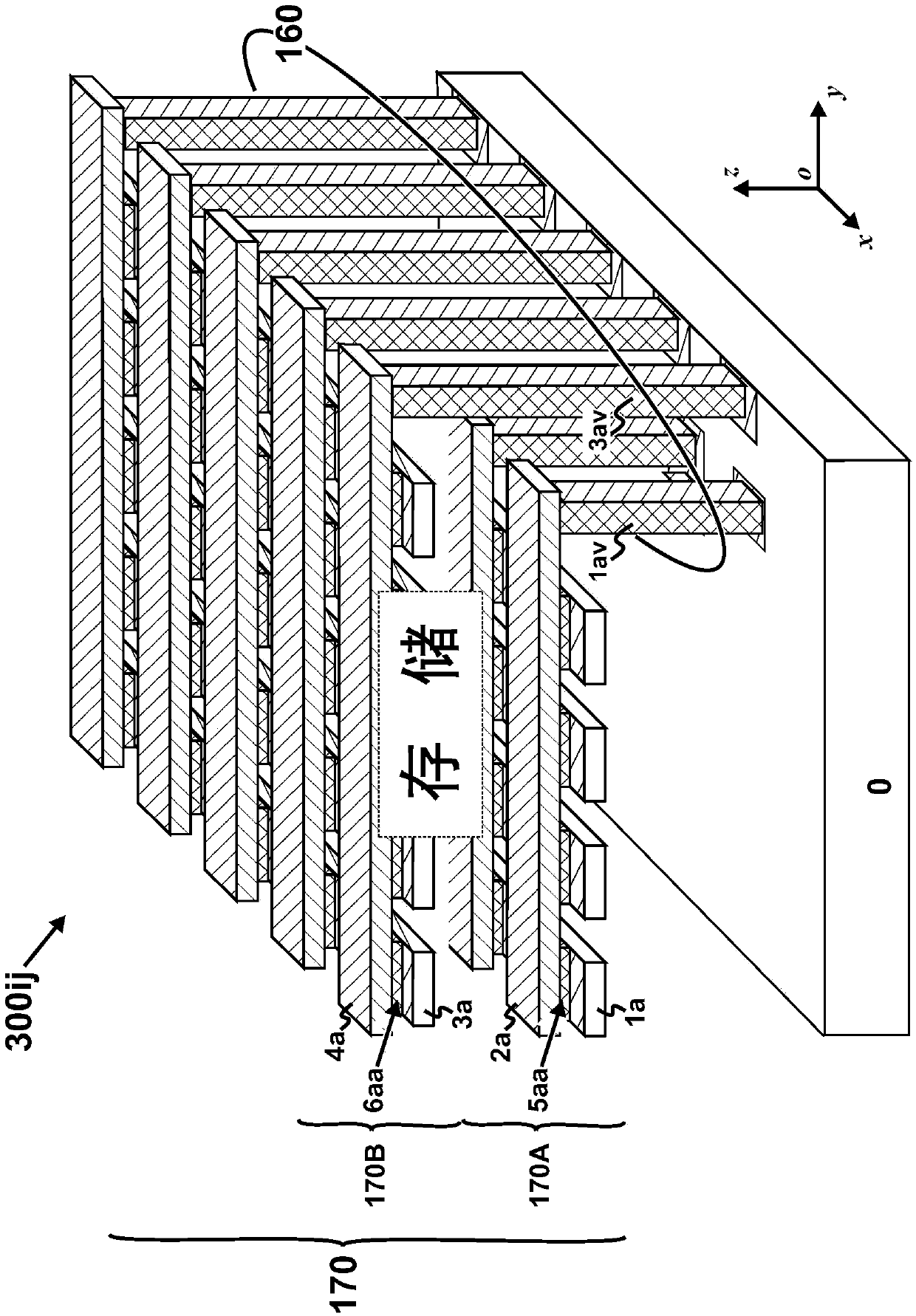

[0026] Figure 3B The structure of the storage unit 100ij is shown from another angle. Each storage unit includes a micro-computing core 180 and at least one 3D-M array 170 . A microcomputing core 180 is formed in substrate 0, which contains the computational logic. The 3D-M array 170 is stack...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More