A multifunctional and efficient dynamic chip verification simulation method and device

A simulation method and multi-functional technology, applied in functional inspection, instrumentation, error detection/correction, etc., can solve problems such as modifying incorrect functions, impossibility, and efficient completion, so as to shorten the return cycle, save time, and improve efficiency Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] Below will be combined with the attachment to describe multiple embodiments of the present invention.

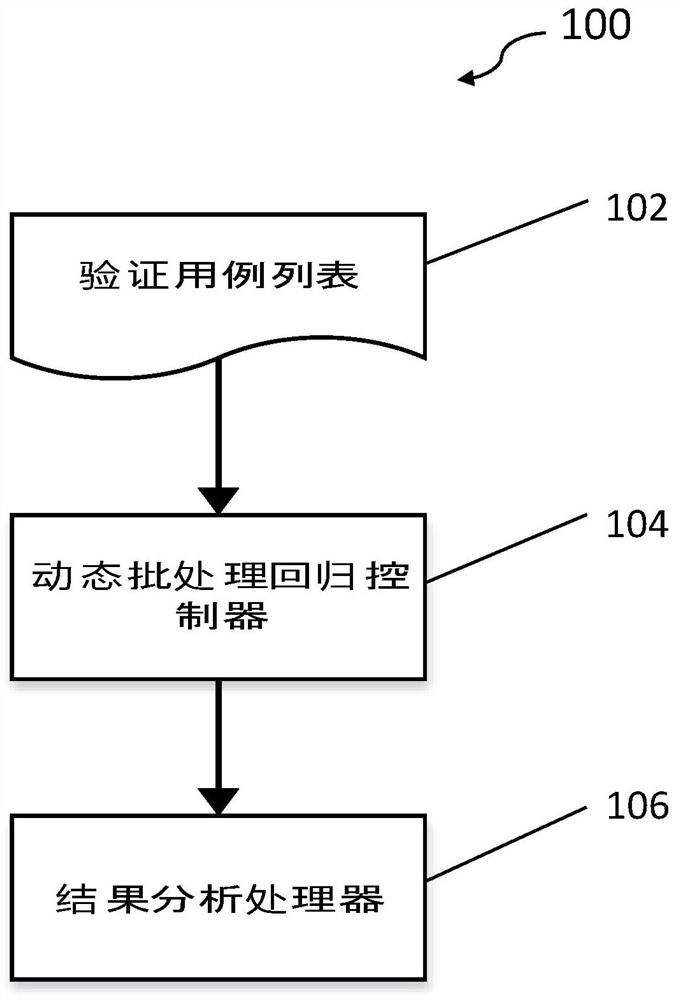

[0044] figure 1 It is the structural diagram of the multi -functional efficiency and efficient dynamic chip verification simulation system 100 based on the embodiment of the present invention. like figure 1 In the middle, the simulation system or device 100 includes a list of verification use case 102. In one embodiment, the list of authentication is a text file for managing all cases of chip verification, including use case identification, debugging mode switch, coverage switch, and return switch. Verification personnel can select the simulation parameter performed by each verification case by configure this list.

[0045] Further, the simulation system 100 also includes dynamic batch processing regression controller 104, which is the core processing module in the present invention. In one embodiment, the dynamic batch regression controller 104 can be implemented in scr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More