Parallel test device for semiconductor power device

A technology for power devices and testing equipment, which is applied in the field of parallel testing equipment for semiconductor power devices, can solve the problems of decreased test yield, waste of cost, and no disclosure of the specific structural design of the parallel testing device, so as to reduce testing costs and improve production capacity. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0082] Hereinafter, the present invention will be further described with reference to the drawings and specific embodiments.

[0083] Design concept of the present invention is as follows:

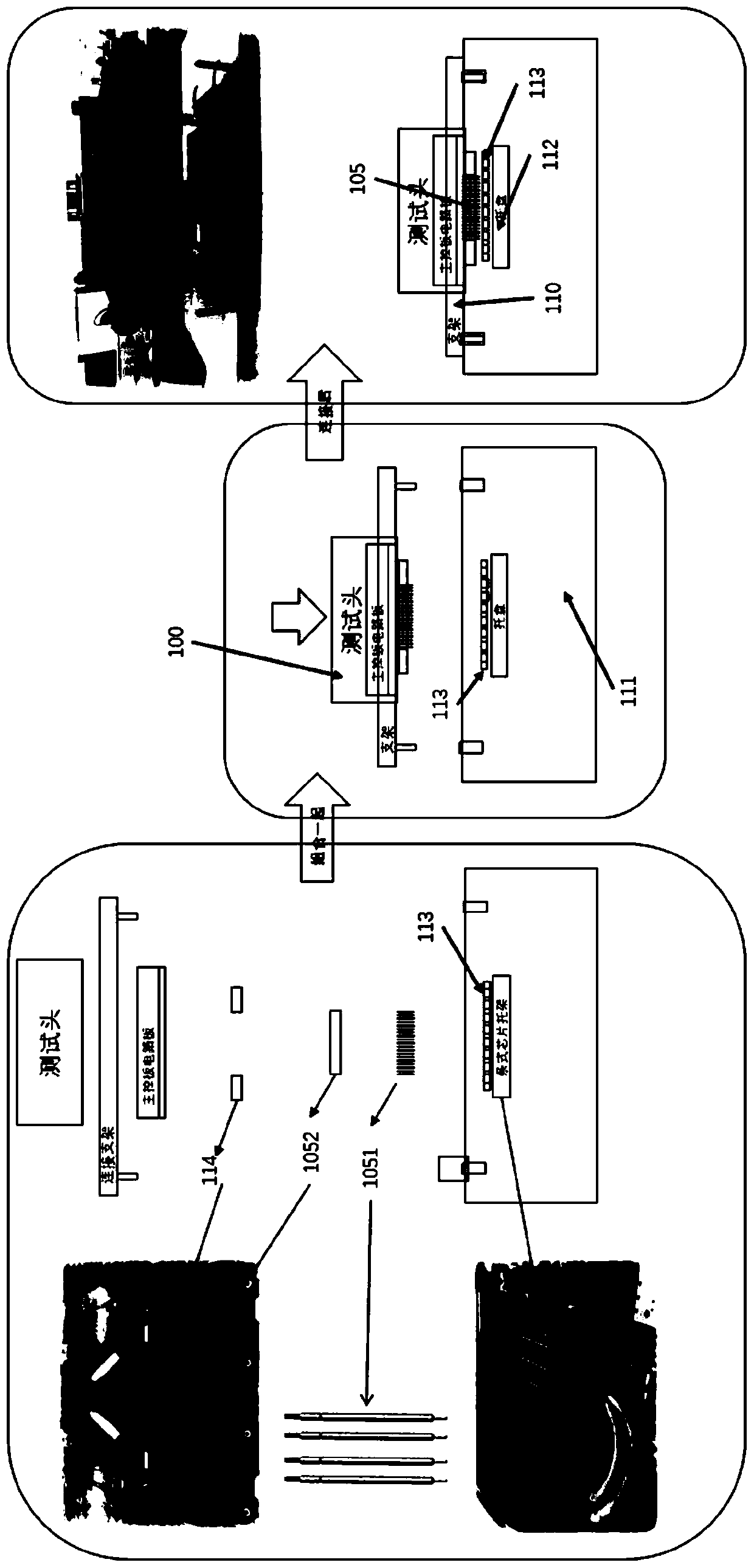

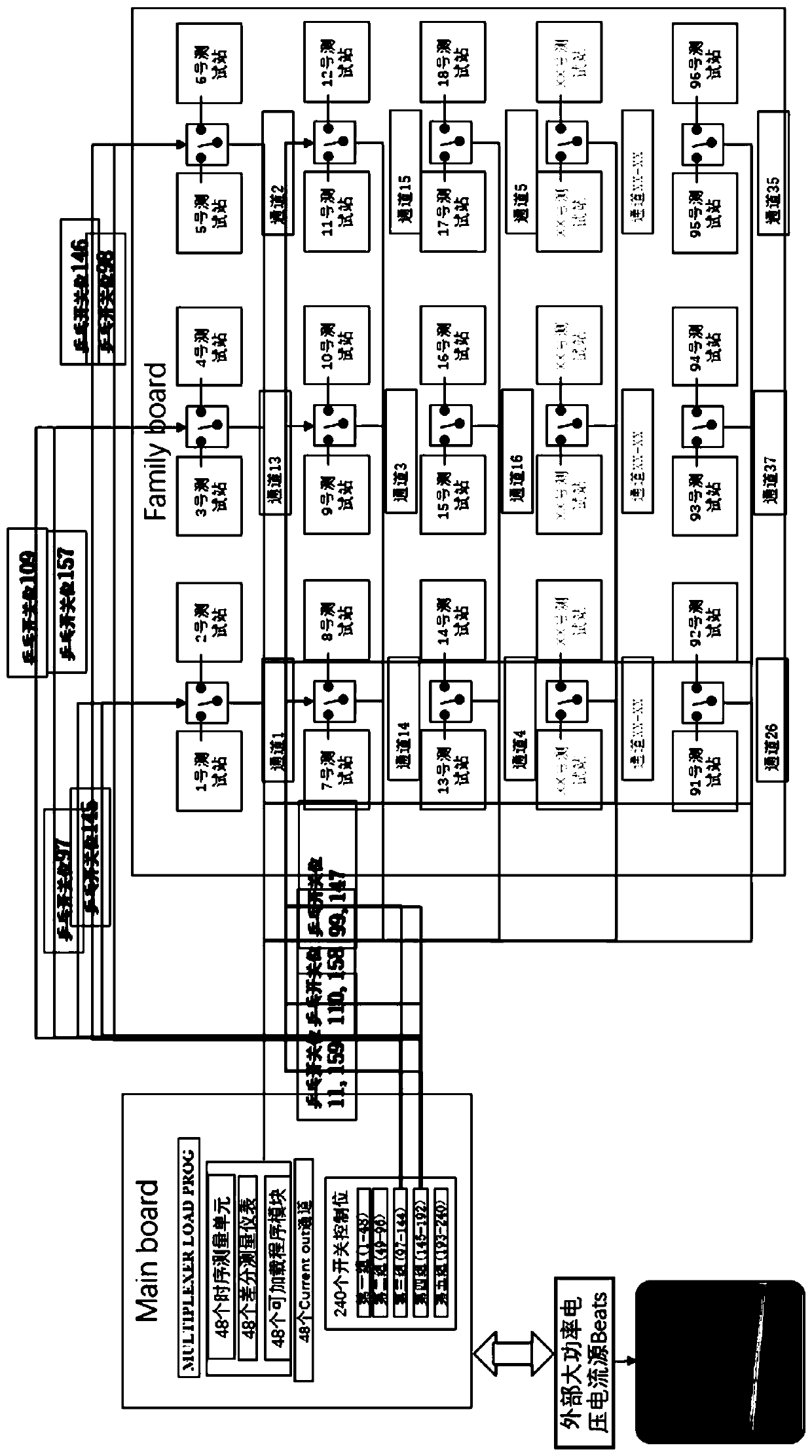

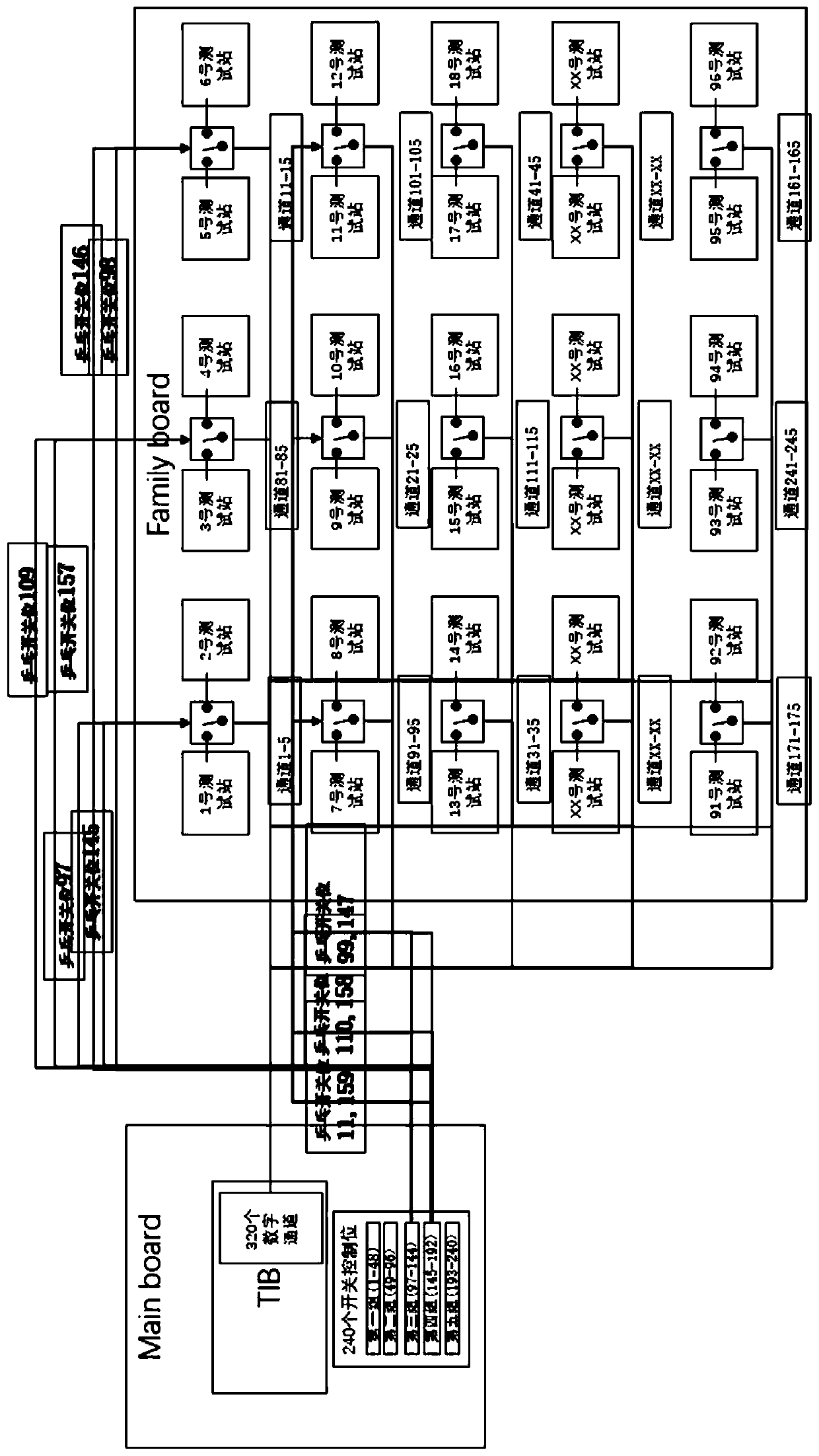

[0084] The present invention makes full use of the high-density chips on the lead frame for centralized processing, such as figure 1 As shown, after lead frame molding, plating, and baking, pre-cut ribs are performed, such as figure 2 As shown, the cutting of specific pins ensures the realization of the electrical test. Part of the chip pins of each package unit are cut and separated from the lead frame. With the unique two-dimensional identification code on the frame and the corresponding vertical and horizontal coordinates, the package unit is overall Parallel testing.

[0085] Parallel testing is implemented by connecting the chip tip to the lead frame.

[0086] The chip packaging and testing device includes a test processing unit, a contactor support and a plurality of contactor un...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com