Digital circuit function modeling method and system based on internal entity state transition

A digital circuit and state transfer technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as difficult automatic generation of incentives, poor applicability and scalability, and inability to model and describe digital circuit functions. Achieve good scalability and applicability, avoid redundancy, and facilitate engineering applications

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

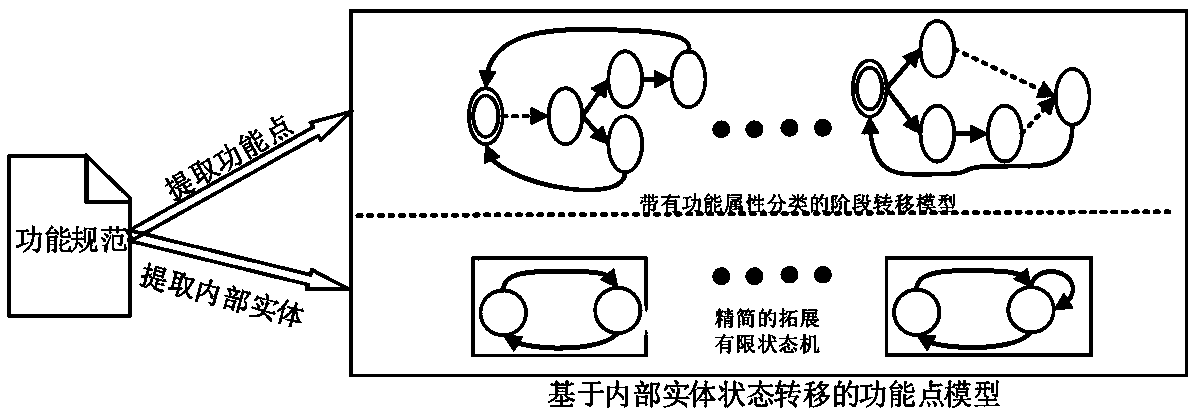

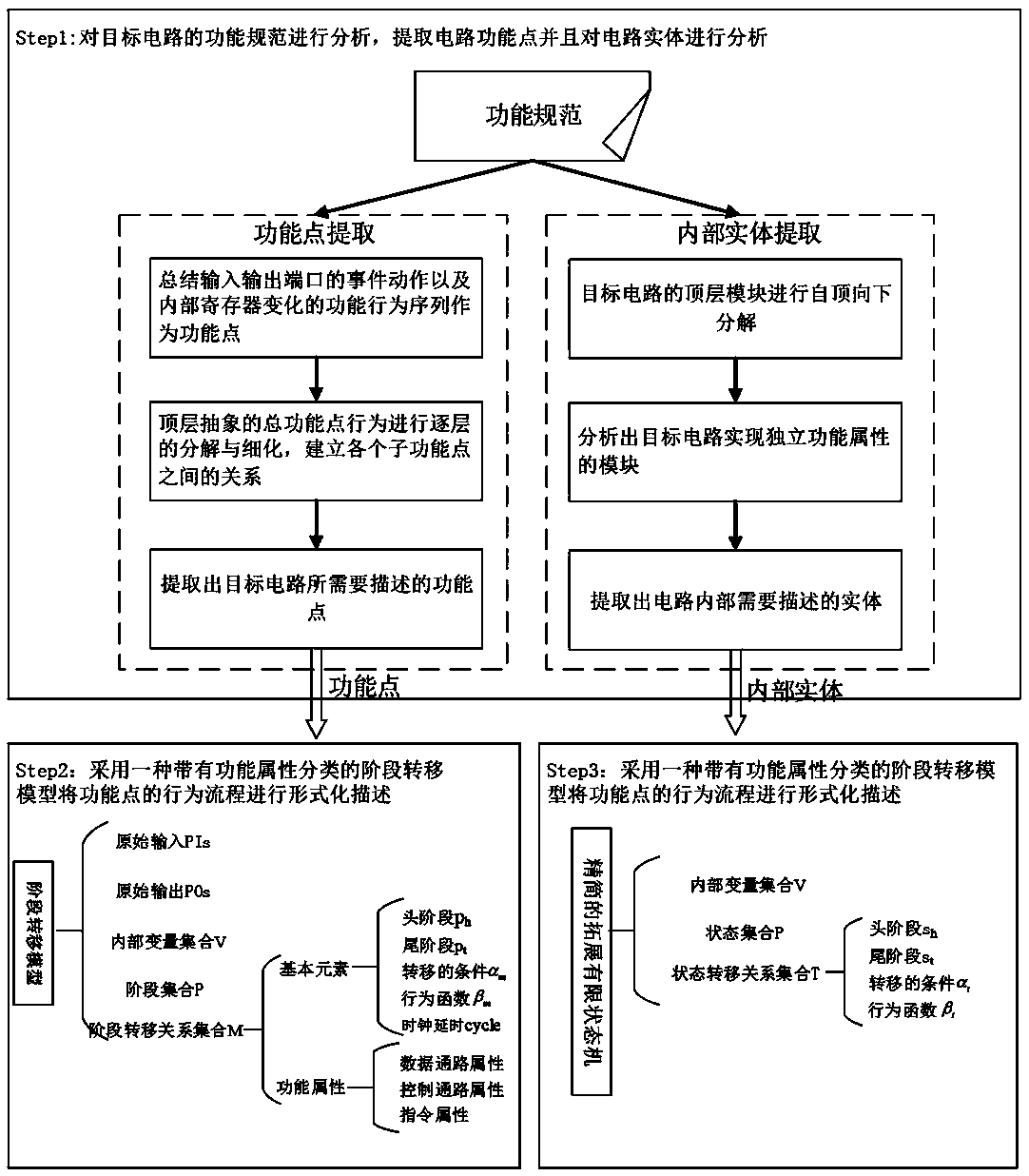

[0026] Such as figure 1 As shown, the implementation steps of the digital circuit function modeling method based on internal entity state transition in this embodiment include:

[0027] 1) Analyze and extract function points and internal entities according to the functional specification of the target digital circuit;

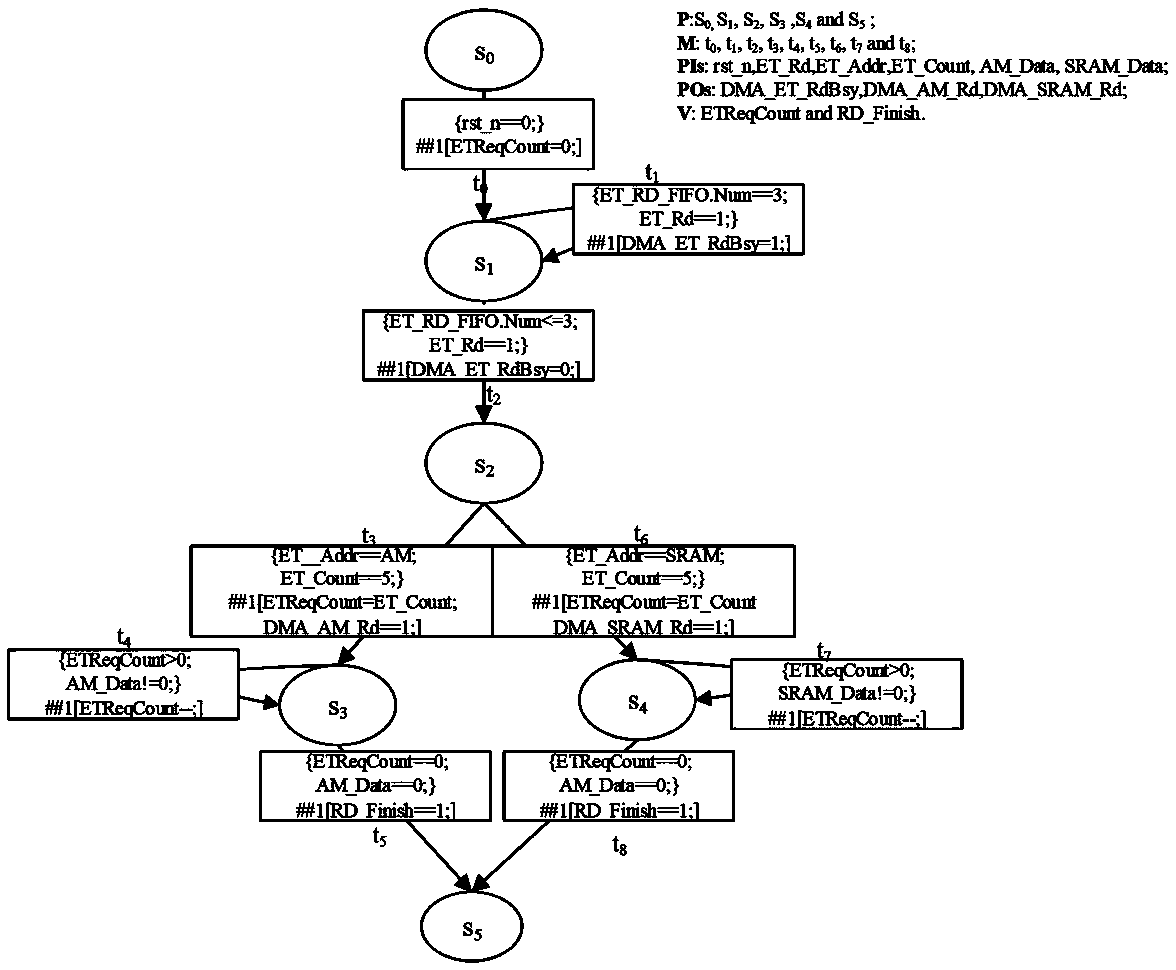

[0028] 2) Use the stage transition model with functional attribute classification to formally describe the behavior flow of the function points, and use the extended finite state machine to formally describe the internal entities of the circuit, so as to obtain the stage transfer model and the extended finite state machine. Functional model of the target digital circuit;

[0029] 3) Output the stage transfer model and expand the finite state machine.

[0030] see figure 1In this embodiment, the digital circuit function modeling method based on internal entity state transition specifically adopts a stage transition model with functional attribute classificati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More