Method and device for achieving variable bit width division method through FPGA

A division and variable technology, applied in the FPGA field, can solve problems such as the inability to achieve efficient calculations, and achieve the effect of making up for limitations and maintaining the speed of calculations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

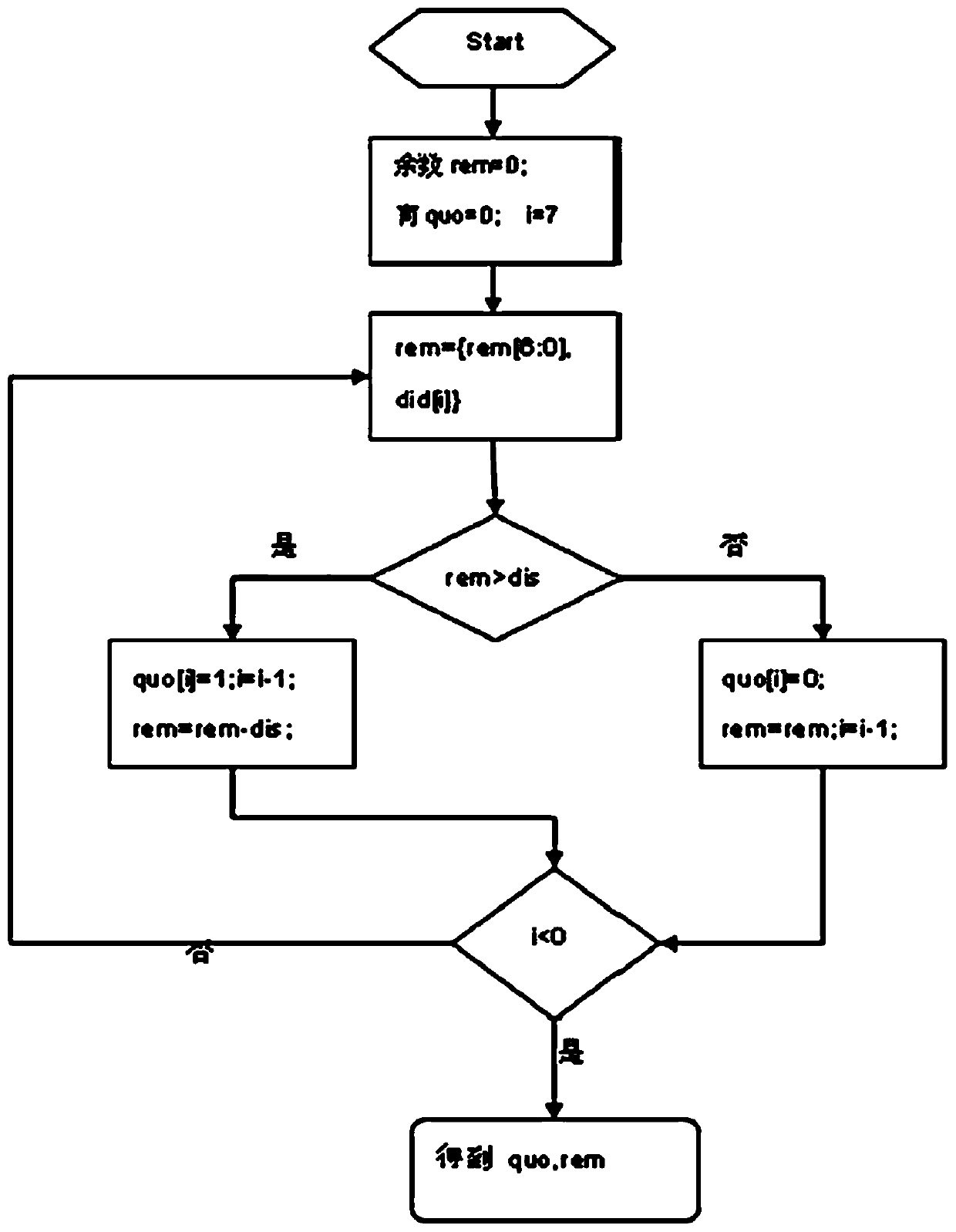

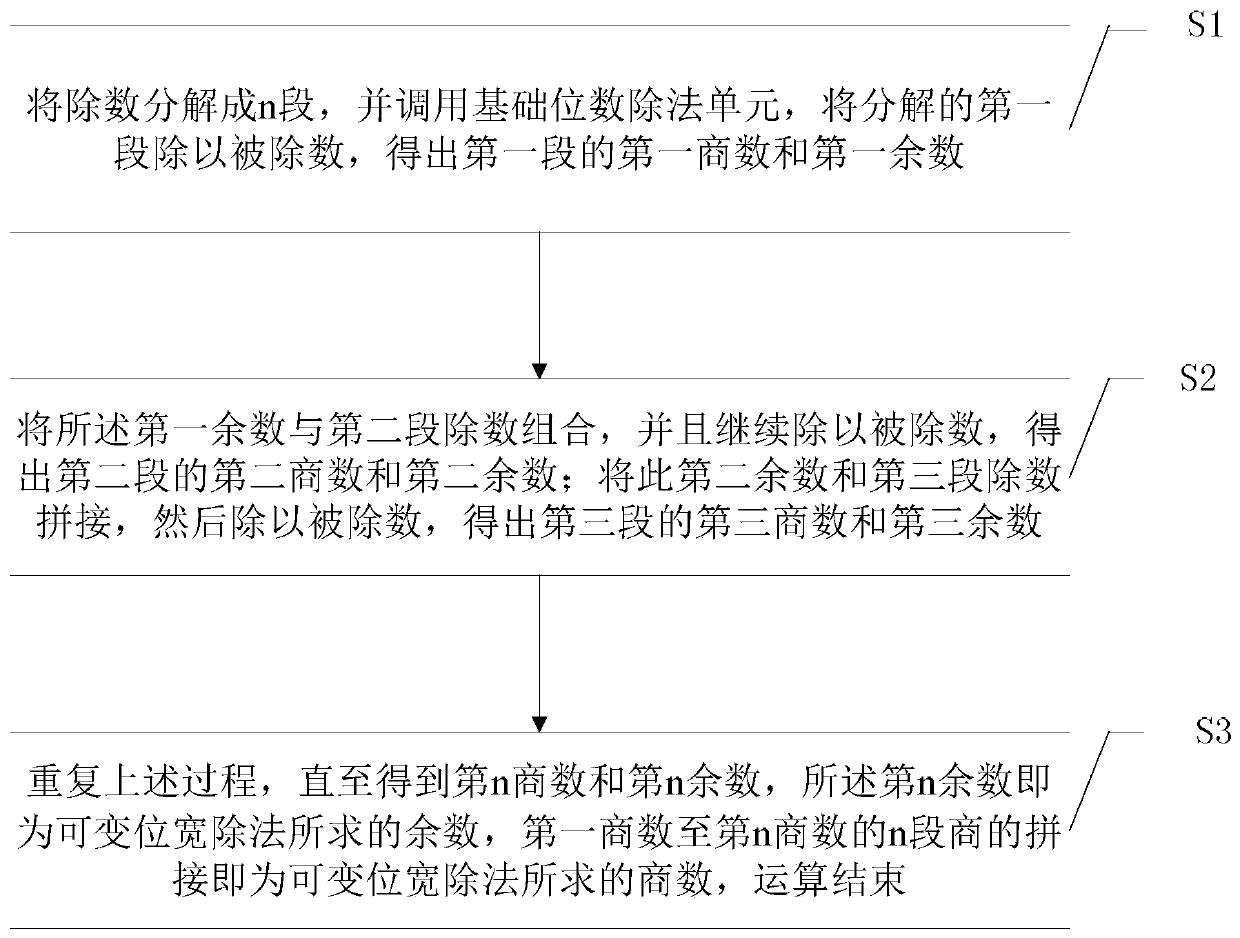

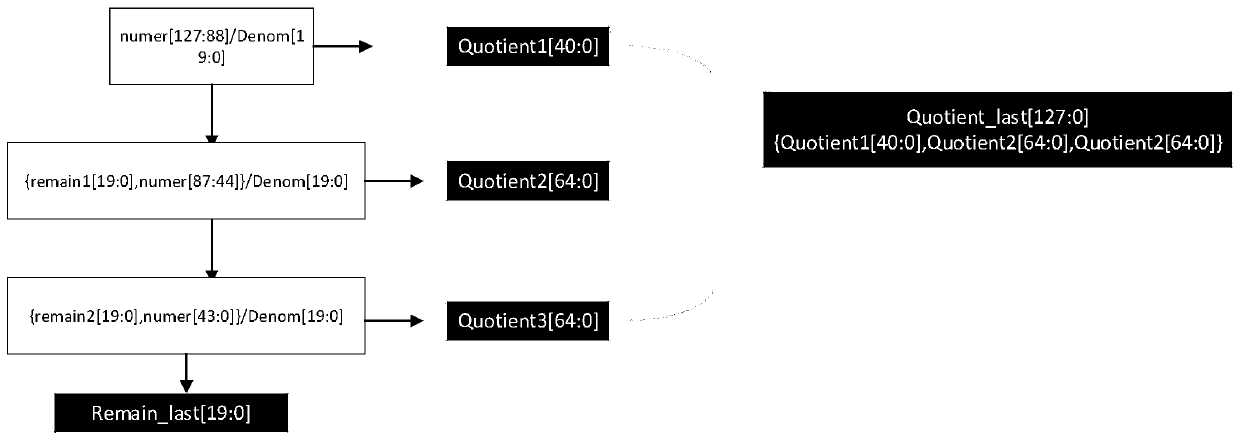

[0033] The present disclosure provides a method for FPGA to implement variable bit-width division, aiming to realize faster and more efficient FPGA division with arbitrary bit width than shift division by using a new operation method.

[0034] In order to make the purpose, technical solutions and advantages of the present disclosure clearer, the present disclosure will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

[0035] Certain embodiments of the present disclosure will be described more fully hereinafter with reference to the accompanying drawings, in which some but not all embodiments are shown. Indeed, various embodiments of the disclosure may be embodied in many different forms and should not be construed as limited to the embodiments set forth herein; rather, these embodiments are provided so that this disclosure will satisfy applicable legal requirements.

[0036] In an exemplary embodime...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More