Design method of FPGA IP core

A design method and user-designed technology, applied in computing, special data processing applications, instruments, etc., can solve the problems of resource redundant IP core area, low IP core resource occupancy rate, layout and wiring failure, etc., to avoid redundant IP core area. resources, avoid redesign, avoid the effect of redundancy of resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

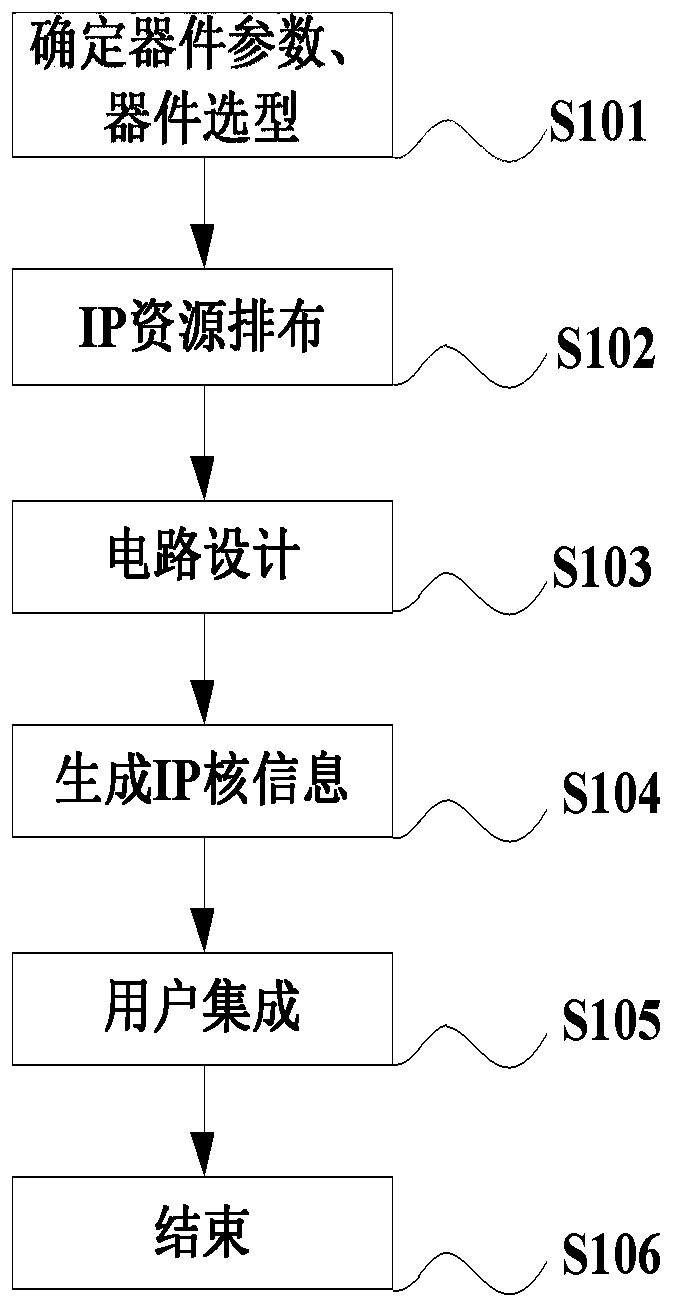

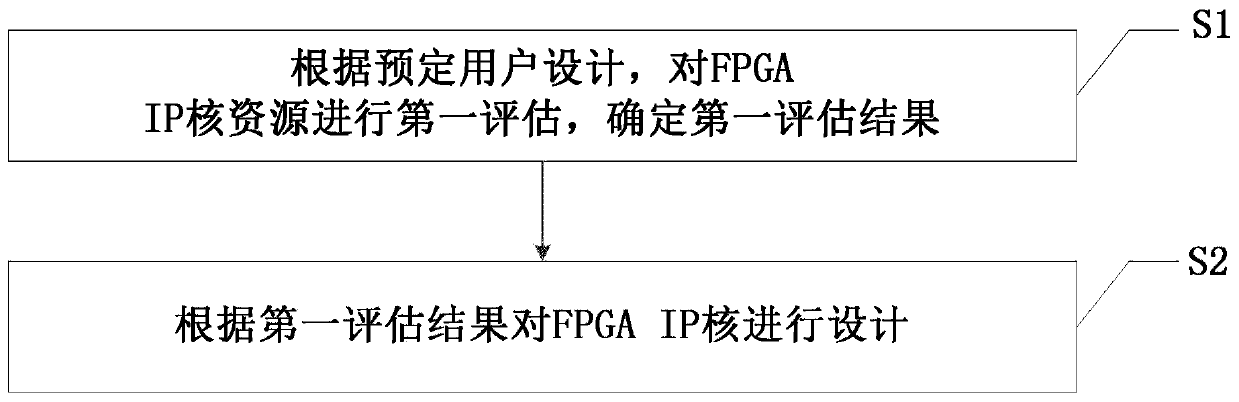

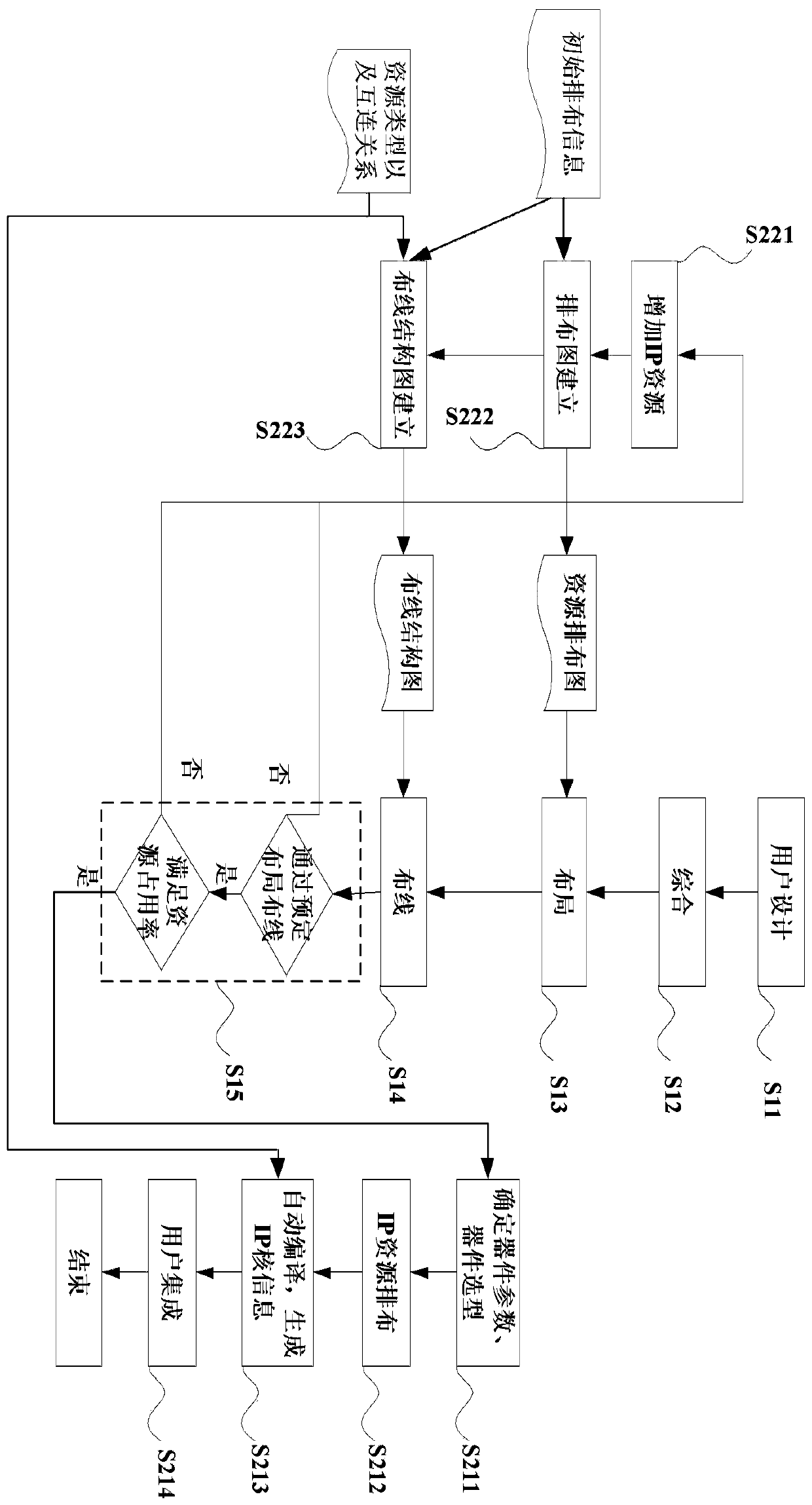

[0051] In the prior art, the determination of FPGA IP parameters is generally determined by estimating user needs, which may result in the failure of user-designed layout and routing, resulting in an extension of the design cycle; or when the resources occupied by the design are far lower than the maximum resources of the IP , will cause the resource occupancy rate of the IP core to be too low, resulting in resource redundancy and an increase in the area of the IP core. In view of this, the present invention provides a kind of design method of FPGA IP core, has added the flow process that the resource occupancy rate of predetermined user design is evaluated in the IP design flow of prior art, because in evaluation flow, to predetermined user design The pre-evaluation of layout and routing is carried out, and the layout and routing results and resource occupancy rate are given. Therefore, a reasonable IP core resource scale and arrangement can be given according to the predete...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More