Four-pin integrated circuit packaging structure with heat dissipation

A technology of integrated circuits and packaging structures, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of difficult chip process size, inability to meet the signal transmission speed of smaller chips, anti-interference ability and heat dissipation performance, and achieve reduction Difficulty in wire bonding, maximizing the utilization rate of copper strips, and the effect of preventing separation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

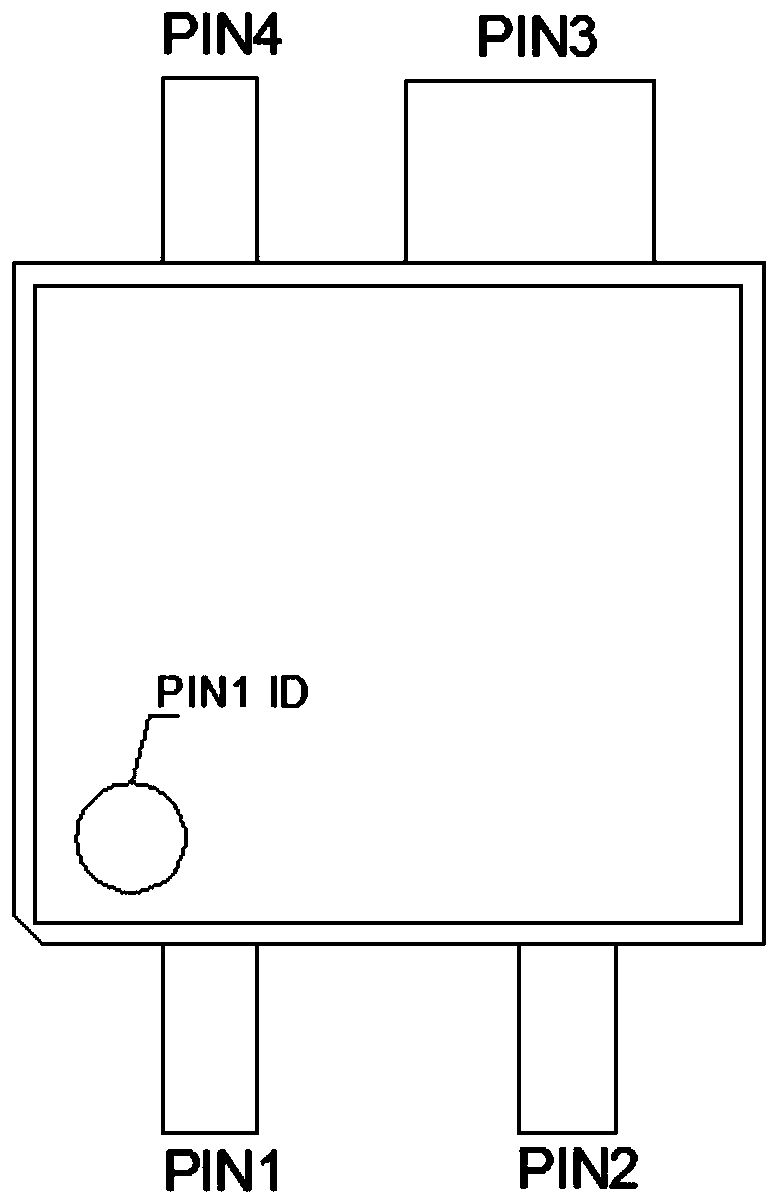

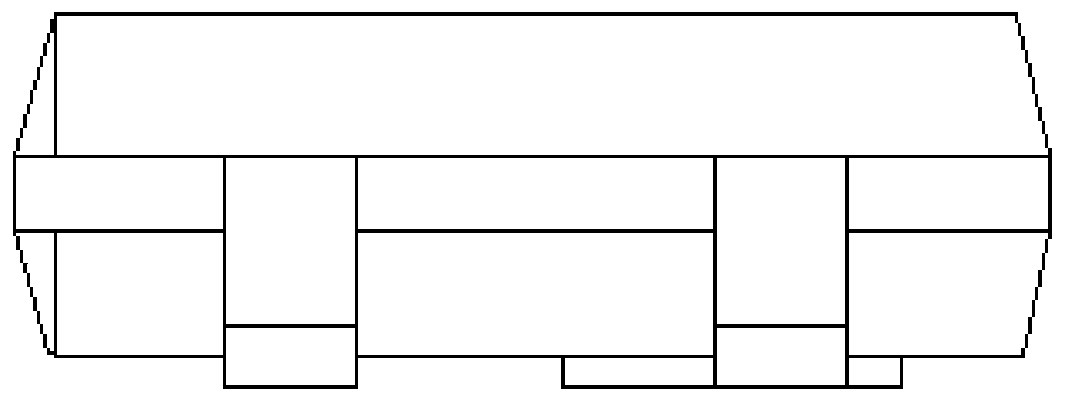

[0034] The five-pin SMT package with heat dissipation proposed by the present invention is different from any existing package form, we call it Score4L package, it is smaller and thinner than the current SOP and SSOP, and is more suitable for large-scale SMT operations . Embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

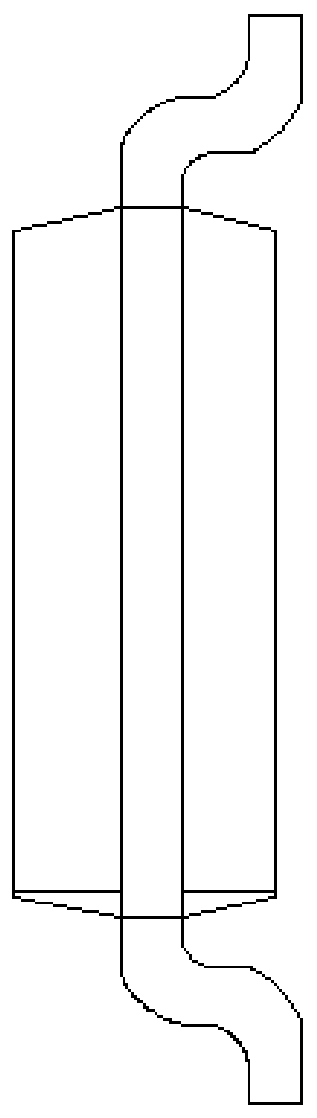

[0035] Such as figure 1 As shown, the length, width and thickness of ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Length and width | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More