Analog circuit multi-objective optimization design method based on multi-objective Bayesian optimization

A technology of multi-objective optimization and circuit simulation, applied in the direction of specific mathematical model, calculation, calculation model, etc., can solve the problem of high computational cost, and achieve the effect of reducing the number of circuit simulations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

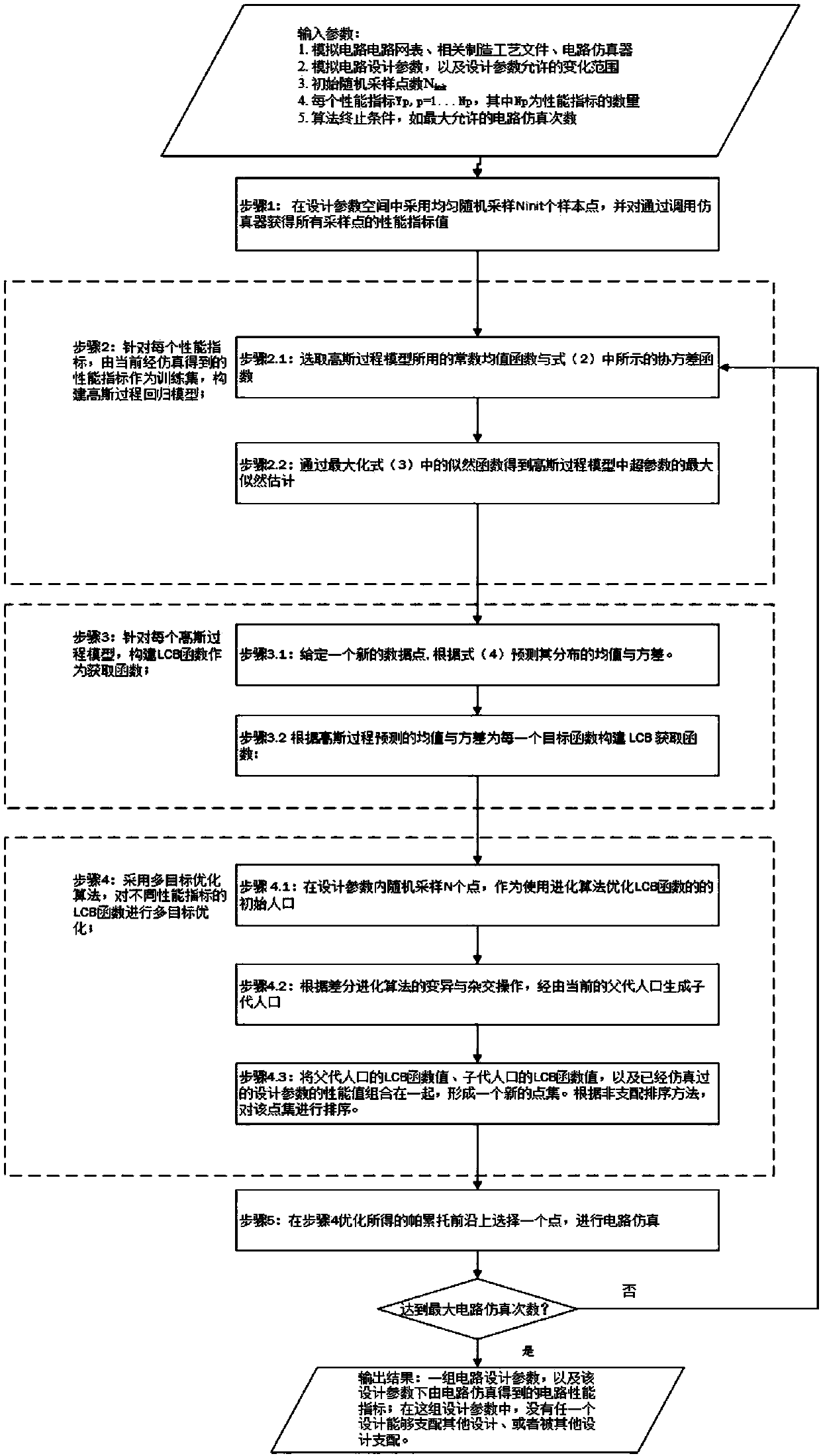

Method used

Image

Examples

test Embodiment 24

[0090] The present invention compares the proposed MOBO algorithm with the simulation-based MOEA / D algorithm [11] and GPMOOG algorithm [14]. ], the PFs of ZDT1 and ZDT2 have analytical solutions, so the ZDT1 and ZDT2 functions can verify the difference between the Pareto front obtained by the algorithm and the real Pareto front; in addition, the ZDT function can also verify the realization of MOEA / D and GPMOOG , because these two functions are also used in [14]; then, three real circuits / devices were tested, including a three-stage operational amplifier, a transformer operating at 60 GHz and a 2.5 GHz power amplifier.

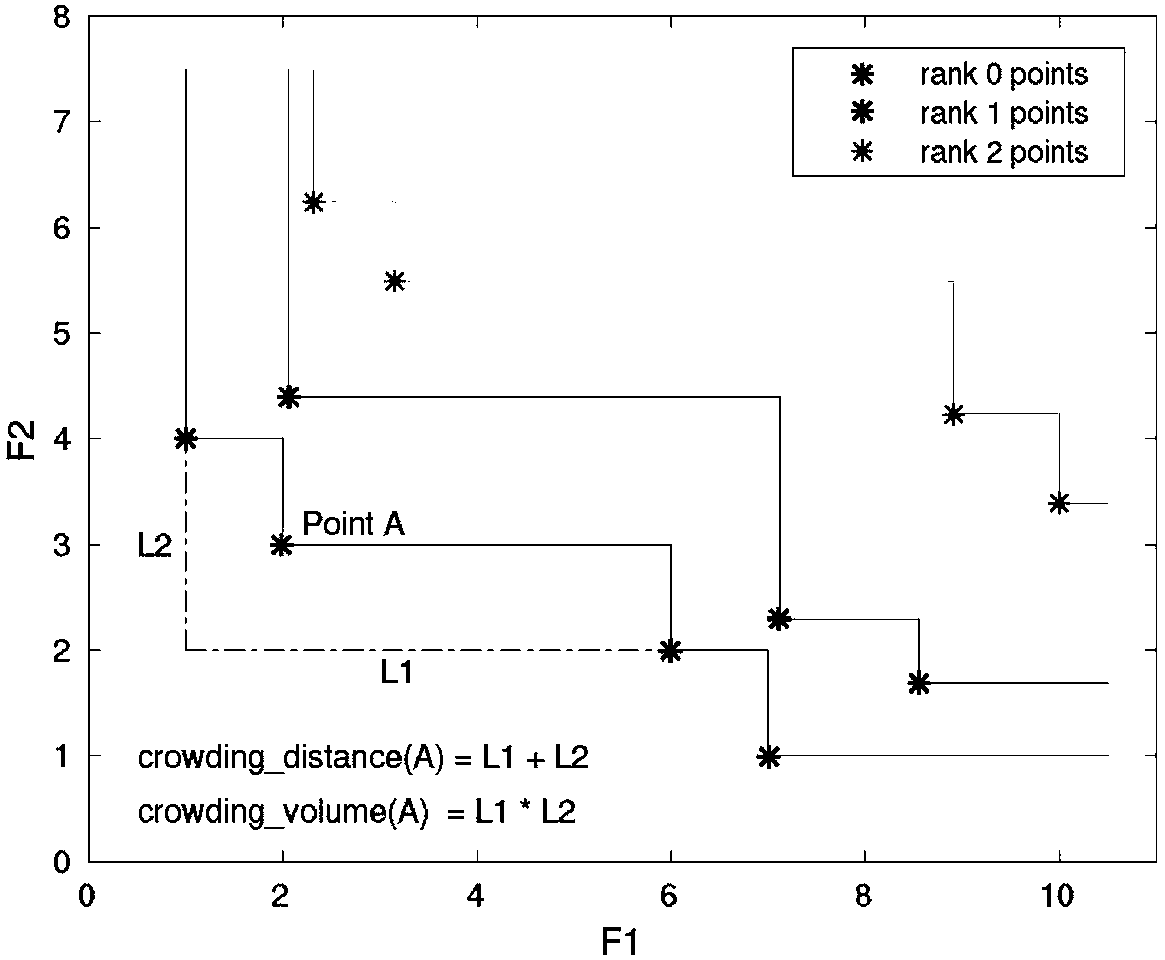

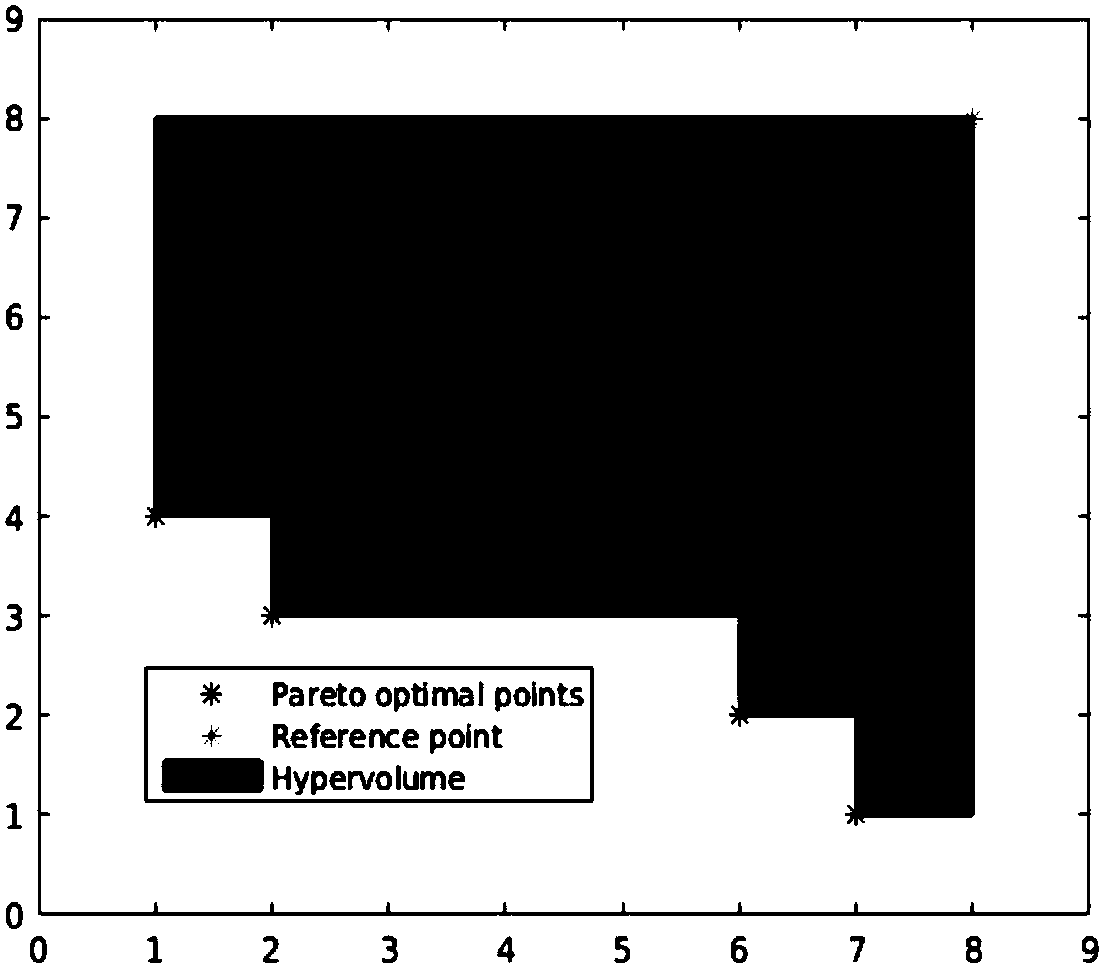

[0091] Based on the fact that a large number of evaluation indicators have been proposed in the world to compare the performance of multi-objective optimization algorithms [25]. The present invention uses Hypervolume Difference Metric Compare the MOBO method that the present invention proposes and the performance of existing GPMOOG method and MOEA / D [11] met...

Embodiment 1

[0099] This example uses the ZDT1 and ZDT2 test functions proposed in [24] to test the MOBO algorithm, GPMOOG, and MOEA / D. Both ZDT1 and ZDT2 are dual-objective optimization problems, and the design space is a 5-dimensional variable; for the MOBO algorithm, the maximum The number of executions of the function is 300, and for GPMOOG and MOEA / D, two different tests are carried out: first, the maximum number of simulations of GPMOOG and MOEA / D is limited to 600, and the optimization results are compared with MOBO; then, GPMOOG is limited The maximum number of simulations with MOEA / D is 3600, and the optimization results are also compared with MOBO, each test is repeated 10 times, and the median The optimization results of , draw the resulting Pareto front, such as Figure 4 shown;

[0100] It can be seen that the MOBO algorithm can give an optimization result close to the real Pareto front with only 300 function evaluations, while GPMOOG and MOEA / D still have a large gap with t...

Embodiment 2

[0102] In this calculation example, the low-power operational amplifier proposed in [26] is optimized. The circuit is designed and simulated in the SMIC 55nm process, and there are 24 design variables, including the size of the transistor, the value of the resistor and capacitor, and The size of the bias current, etc., the circuit diagram is as follows Figure 5 shown;

[0103] The indicators to be optimized include gain (Gain), unity gain bandwidth (Unit gain frequency, UGF) and phase margin (Phase margin, PM). When optimizing the circuit, five process corners (TT / FF / SS / SF / FS), and three temperature conditions (25°C, 40°C, 125°C), so for a set of design parameters, 15 circuit simulations are required, and the worst value of each performance index in these 15 simulations to optimize, i.e.:

[0104] maximize(Gain c , UGF c , PM c ) (9)

[0105] Among them, Gain c , UGF c and PM c Indicates minimum gain, minimum unity-gain bandwidth, and minimum phase margin over all p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More