Lookup table type convolution operation hardware structure based on FPGA

A hardware structure and convolution operation technology, applied in the field of deep learning, to achieve the effect of simple operation, saving on-chip resources, and avoiding multiplication operations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

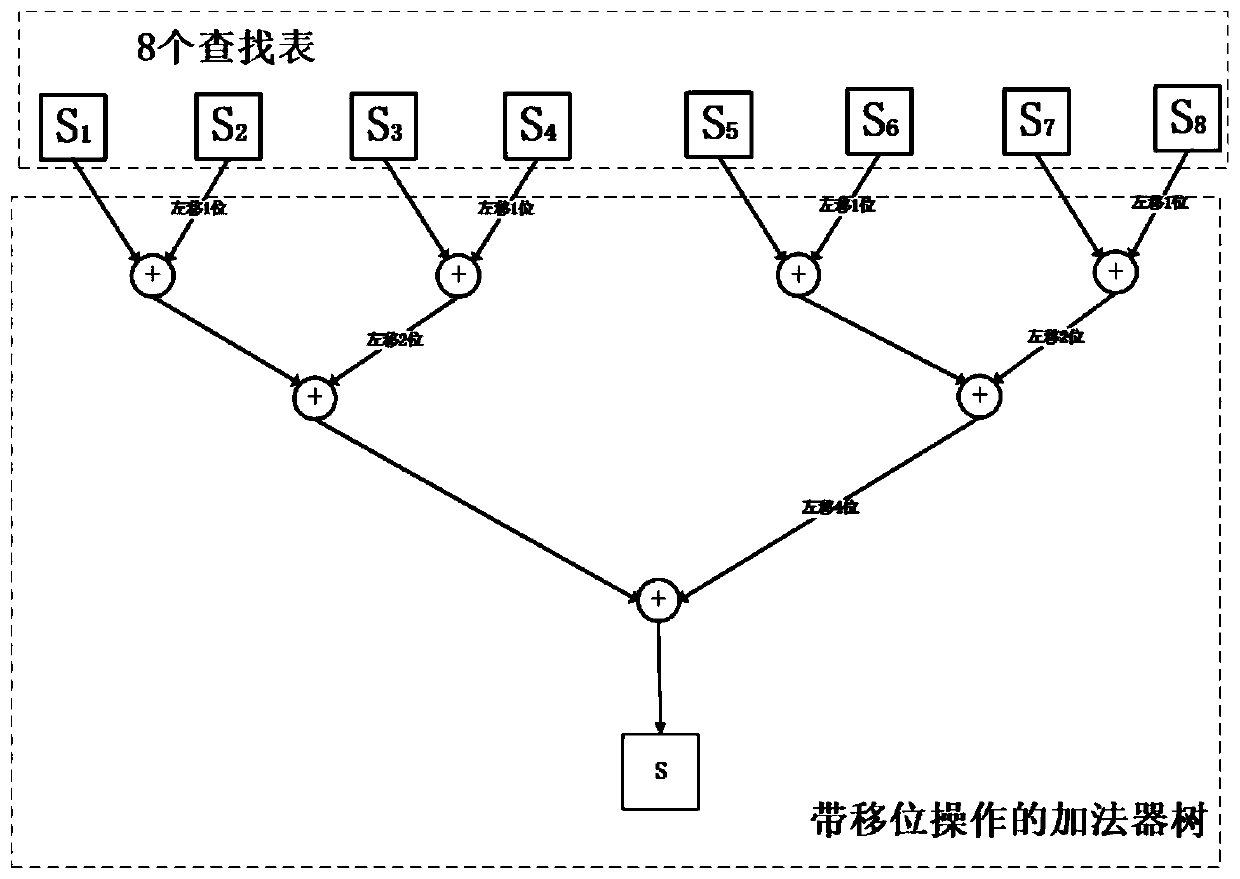

[0027] Such as figure 1 As shown, a FPGA-based lookup table convolution hardware structure includes M lookup tables and an adder tree with a shift operation;

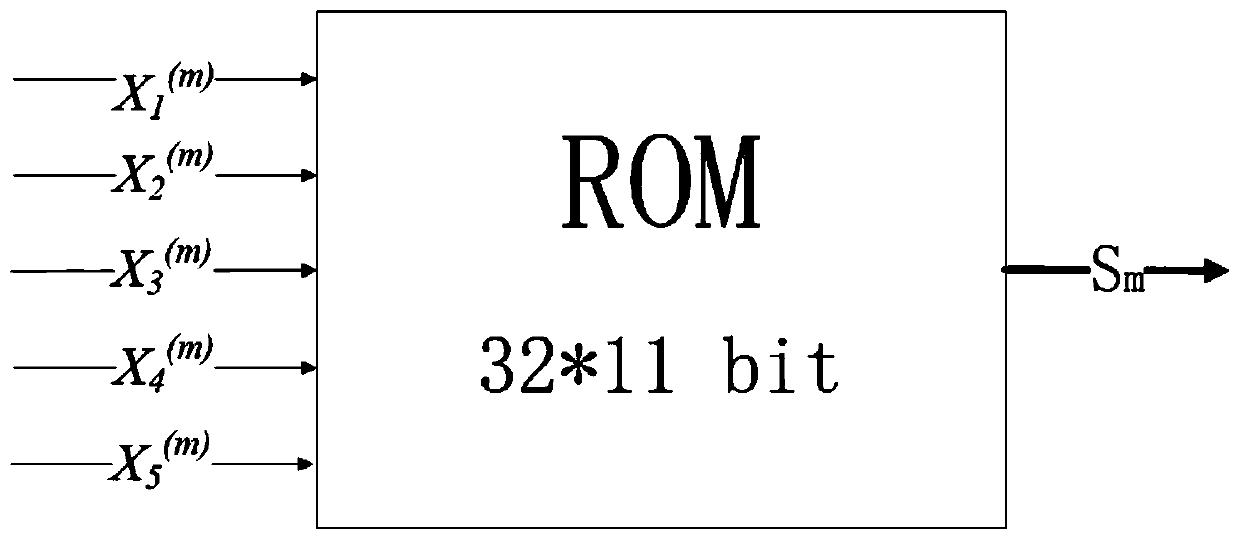

[0028] The size of each lookup table is The data of each row in the lookup table is The corresponding address index is x j , where x j =j(0≤j≤2 N -1), stands for x j The value of the i-th bit in the binary expression; a i Indicates the weight data, each lookup table stores the same data, a total of M, M lookup tables are established on the FPGA, and the data is queried in order; the lookup table is based on the input data x i To index the data stored internally, the address input is in means x N The value of the mth bit of , the corresponding output is recorded as s m ;

[0029] An addition tree with a shift operation contains M input nodes and M-1 adder nodes, the input of each node is the output of the lookup table, the size is bit data, output of M lookup tables {s 0 ,s 1 ,s 2 ,...,s M-1} are i...

Embodiment 2

[0033] Such as figure 1 , figure 2 , image 3 , Figure 4 , Figure 5 as well as Figure 6 As shown, an FPGA-based lookup table convolution operation hardware structure includes 8 lookup tables{s 1 ,s 2 ,s 3 ,...,s 8} and an adder tree with shift operations, structured as figure 1 , each lookup table is of size 2 5 ×11, that is, store 2 5 An 11-bit data.

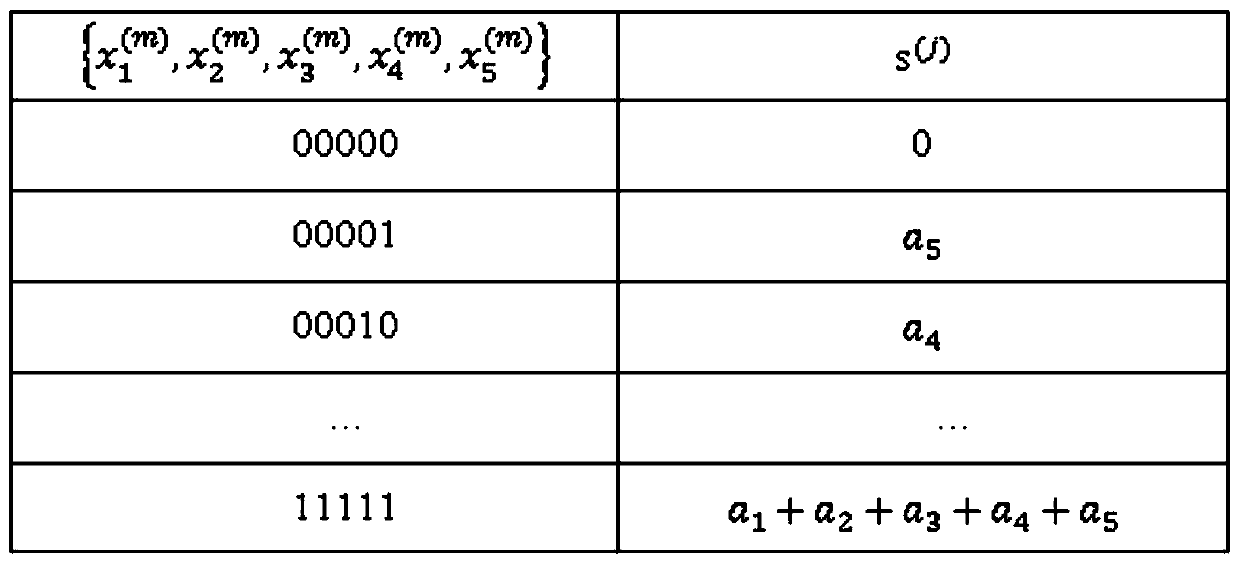

[0034] The data of each row in the lookup table is The corresponding address index is x j . where x j =j(0≤j≤31) stands for x j The value of the i-th bit in the binary expression. The address input for the mth lookup table is The data content stored in the lookup table is as follows figure 2 shown.

[0035] The hardware structure of the lookup table is as follows image 3 shown.

[0036] An addition tree with a shift operation contains 8 input nodes and 7 adder nodes, the input of each node is the output of the lookup table, and the output of the 8 lookup tables {s 0 ,s 1 ,s 2 ,...,s 7} are inp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com