A FPGA-based multitasking system and method

A processing system and task processing technology, applied in the computer field, can solve problems such as not supporting multi-channel data transmission and processing, unfavorable data transmission and processing hierarchical management, single-channel data transmission data congestion, etc., to solve data congestion and resource utilization The effect of maximizing efficiency and improving utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] In order to make the present invention more clear, the technical solutions of the present invention will be further described in detail below through specific embodiments.

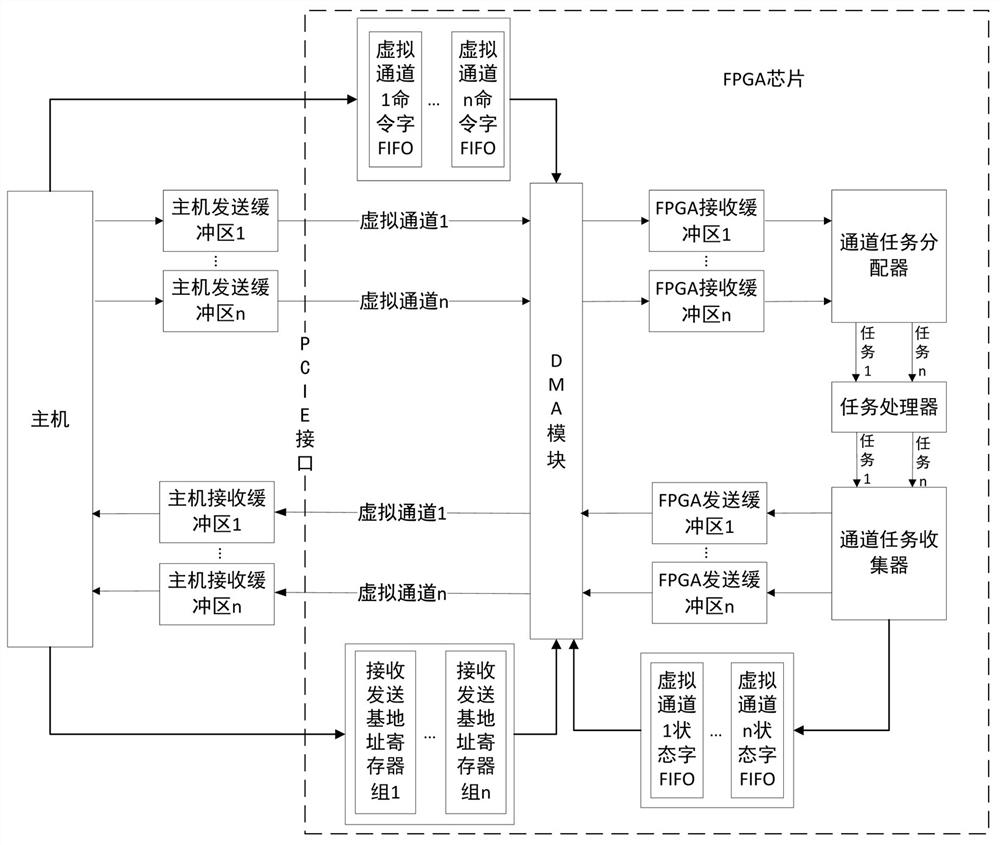

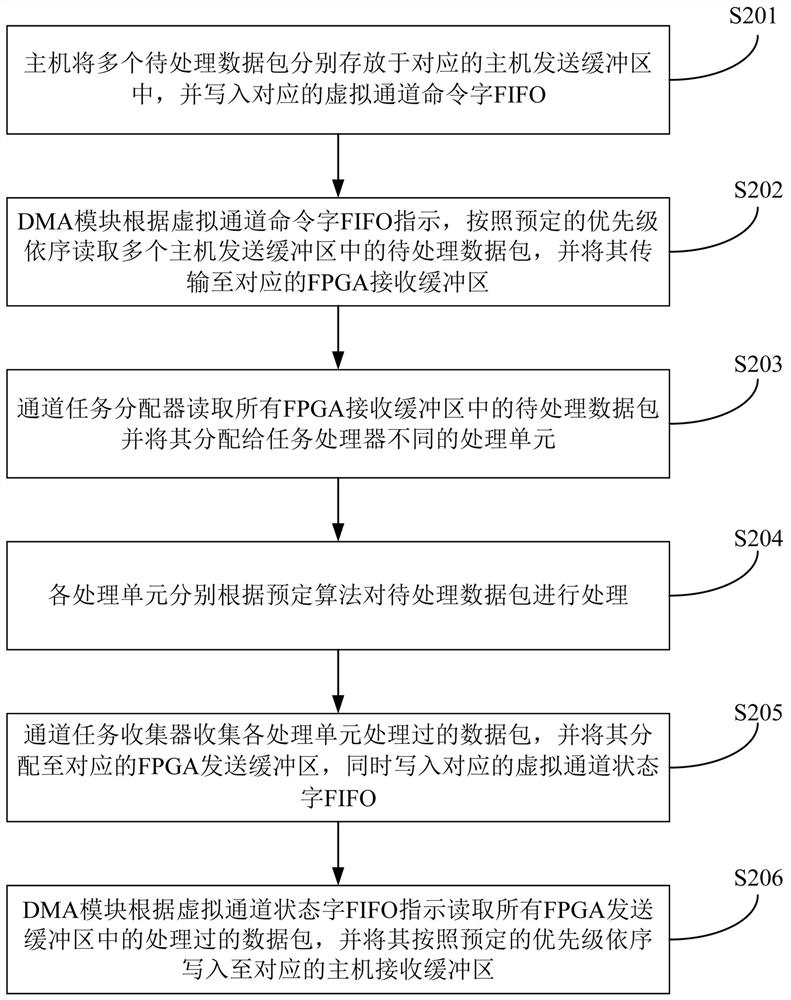

[0045] figure 1 A block diagram of an FPGA-based multitasking system of the present invention is shown.

[0046] Such as figure 1 As shown, the first aspect of the present invention proposes a multitasking system based on FPGA, comprising: FPGA chip, host computer and PCIE interface, described PCIE interface connects FPGA chip and host computer, and constructs multiple between FPGA chip and host computer virtual channel;

[0047] The FPGA chip includes: a DMA module, a channel task distributor, a task processor and a channel task collector;

[0048] The DMA module exchanges data with the host through multiple virtual channels, and controls the read / write requests of different virtual channels according to a predetermined priority relationship;

[0049]The channel task allocator is used to receiv...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More