Semiconductor device failure analysis method

A failure analysis and semiconductor technology, which is applied in the direction of single semiconductor device testing, instruments, measuring devices, etc., can solve the problem that the bias voltage cannot be applied to the test point, and achieve the effect of reducing manpower and time costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

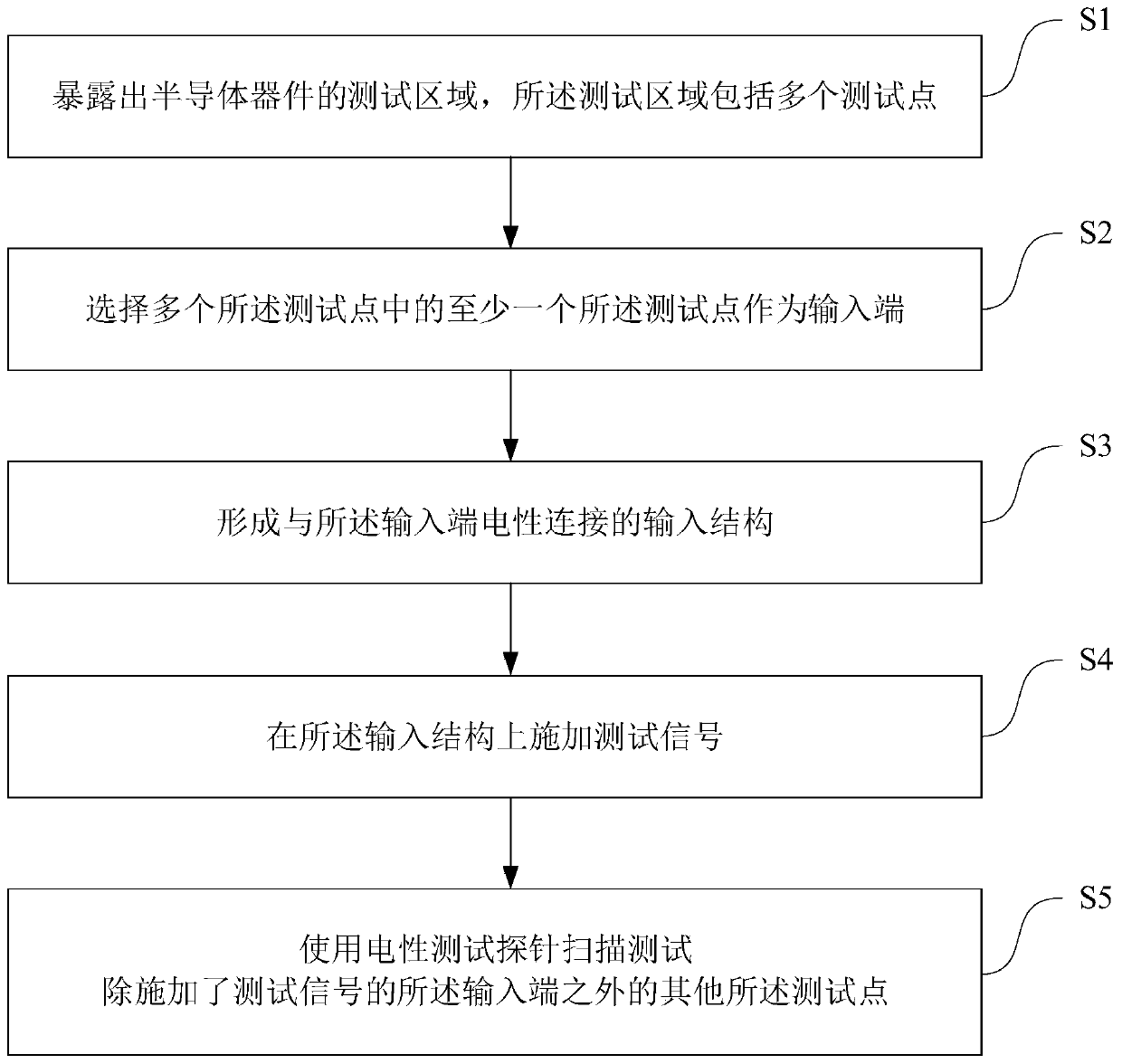

[0062] see Figure 1 to Figure 4 , the present embodiment provides a semiconductor device failure analysis method, comprising the following steps:

[0063] 1) Exposing the test area of the semiconductor device, the test area includes a plurality of test points;

[0064] 2) selecting at least one of the multiple test points as an input terminal;

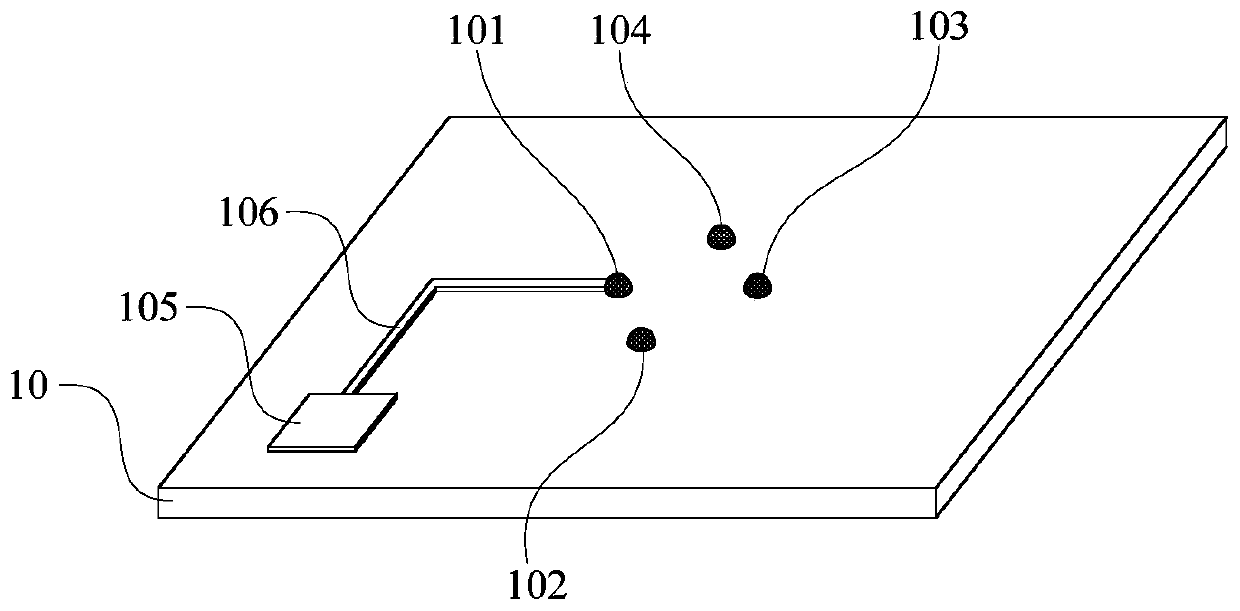

[0065] 3) forming an input structure electrically connected to the input end;

[0066] 4) applying a test signal on the input structure;

[0067]5) Use electrical test probes to scan and test the other test points except the input terminal to which the test signal is applied.

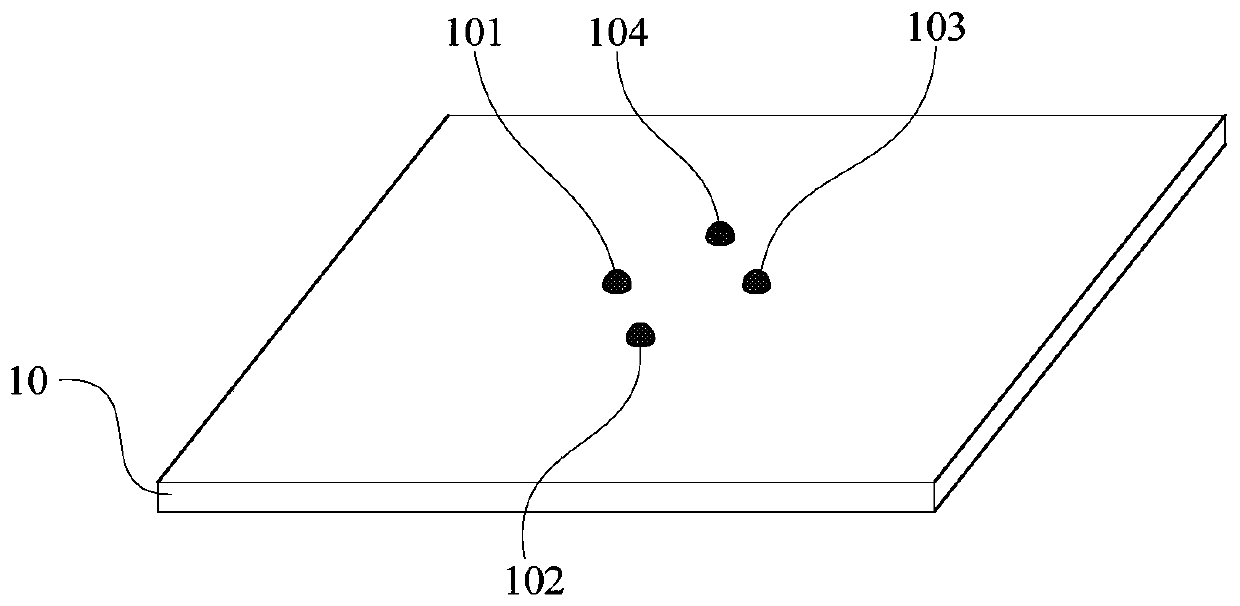

[0068] In step 1), if figure 1 S1 and figure 2 As shown, a test area 10 of a semiconductor device is exposed, and the test area 10 includes a plurality of test points. In this embodiment, the semiconductor device failure analysis method is used to test the leakage characteristics of the test point. There are four test points on the test area 10 of the...

Embodiment 2

[0076] see Figure 5 to Figure 9 , this embodiment provides a failure analysis method for a semiconductor device. Compared with the method in Embodiment 1, the difference of this embodiment is that all of the plurality of test points are used as the input terminals, and a plurality of the input terminals are formed to be electrically connected to the plurality of input terminals. input structures; applying a test signal to each of the input structures in turn, and using electrical test probes to scan and test other test points except the input terminals to which the test signals are applied. That is, this embodiment needs to test the leakage characteristics of each of the multiple test points and other test points.

[0077] As an example, such as Figure 5 to Figure 9 As shown, the four test points on the test area 20: the first test point 201, the second test point 202, the third test point 203 and the fourth test point 204 are all selected as input terminals, and test sign...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More