Memory testing method and device

A technology of memory testing and virtual memory, which is applied in the field of memory, can solve the problems that production time affects memory development time, etc., and achieve the effects of saving hardware production time, shortening development time, and improving development efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

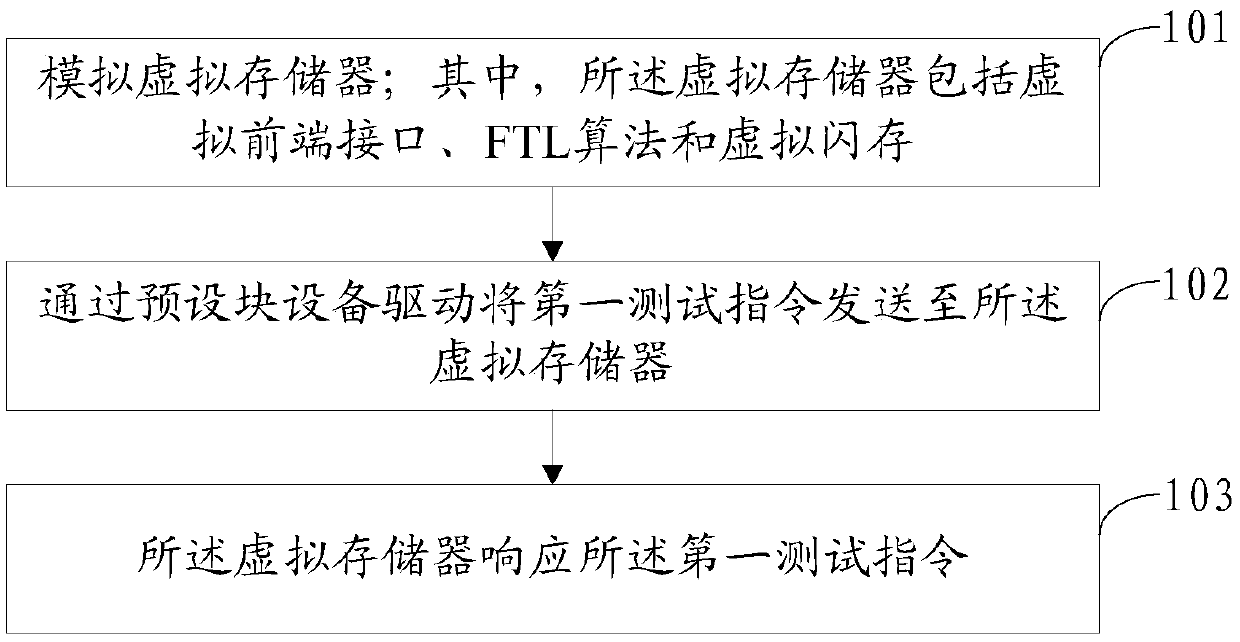

[0049] figure 1 A flow chart of steps of a memory testing method provided by an embodiment of the present invention is shown. Applied to a terminal, the method includes:

[0050] Step 101, simulating a virtual memory; wherein, the virtual memory includes a virtual front-end interface, an FTL algorithm, and a virtual flash memory.

[0051] In this embodiment, the memory hardware mainly includes a front-end interface, an FTL algorithm and a NAND chip, wherein the FTL algorithm is an important component module in the memory hardware, and the stability of the FTL algorithm determines the stability of the memory firmware. The FTL algorithm mainly maps the logical address to the physical address of the NAND chip. During this process, it will also trigger FTL's garbage collection, wear leveling, bad block management and other mechanisms. Since the FTL algorithm can be realized by software, the virtual memory can be realized by simulating the front-end interface as a virtual front-e...

Embodiment 2

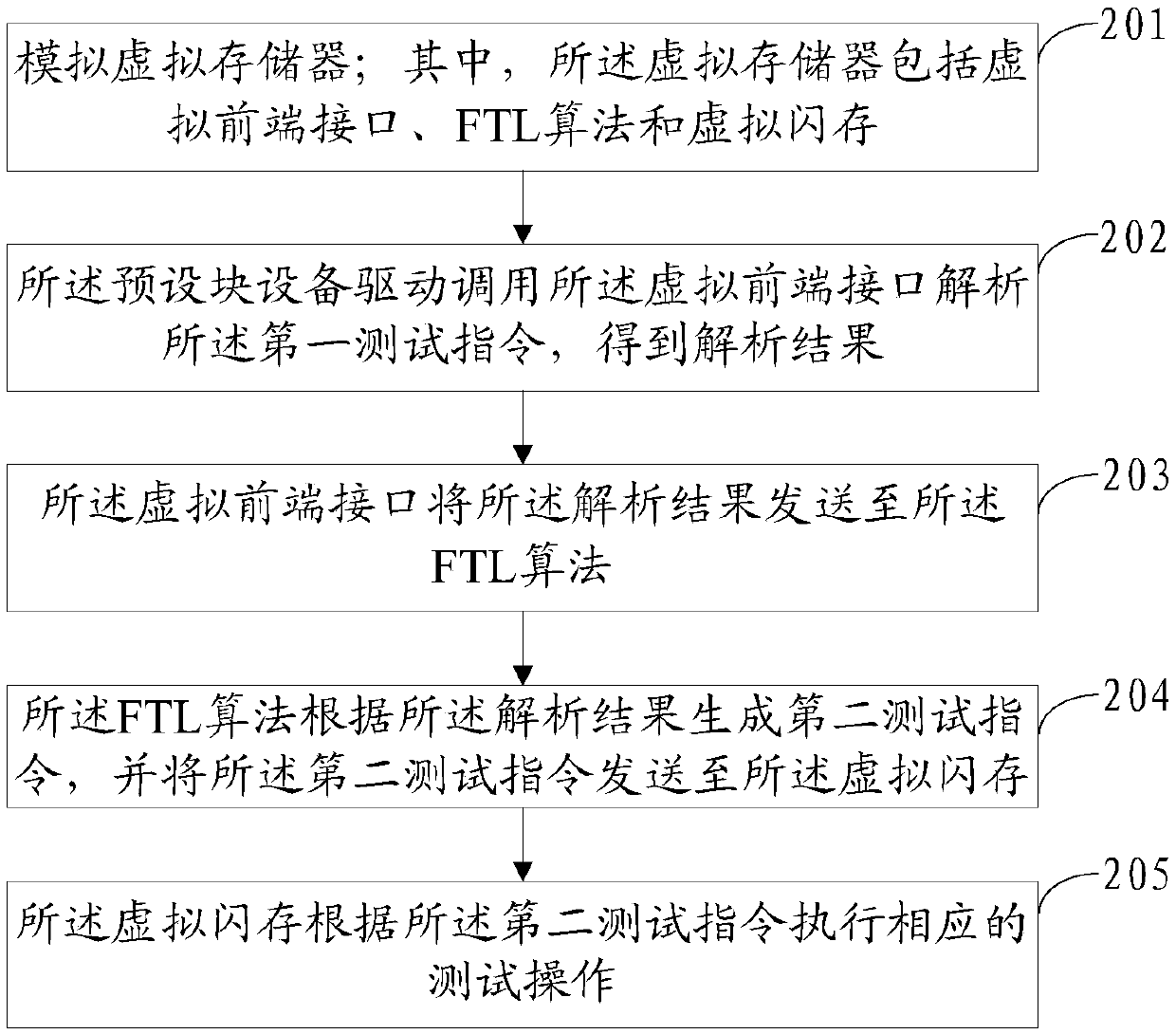

[0059] figure 2 A flow chart of steps of a memory testing method provided by an embodiment of the present invention is shown. Applied to a terminal, the method includes:

[0060] Step 201, simulating a virtual memory; wherein, the virtual memory includes a virtual front-end interface, an FTL algorithm, and a virtual flash memory.

[0061] Step 202, the preset block device driver invokes the virtual front-end interface to analyze the first test instruction, and obtains an analysis result; wherein, the analysis result includes at least an operation instruction, an LBA, and the number of LBAs, and the operation instruction includes At least one of reading, writing and erasing.

[0062] In this embodiment, after receiving the first test instruction, the preset block device driver invokes the virtual front-end interface to analyze the first test instruction and obtain the analysis result. Specifically, the operation instruction, LBA and the number of LBAs are analyzed from the ...

Embodiment 3

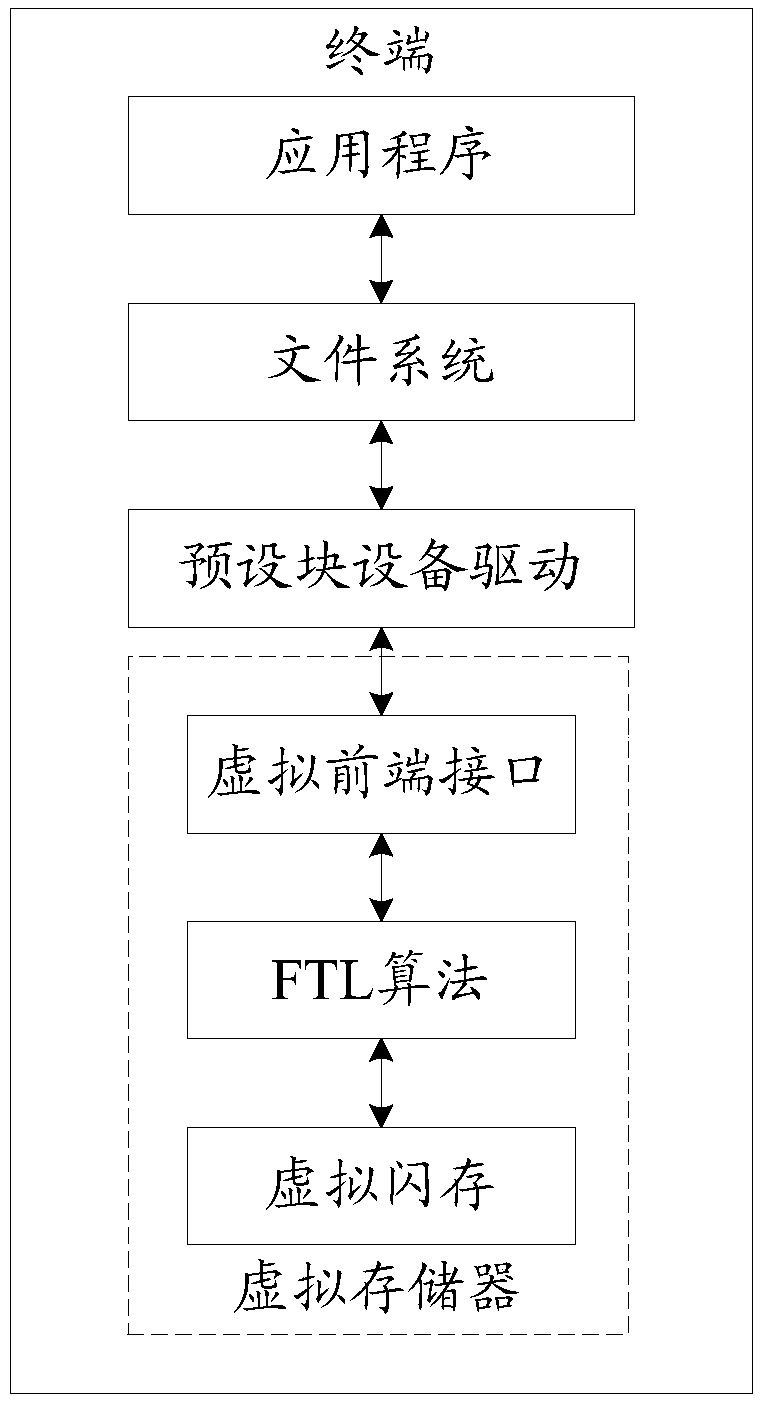

[0071] Figure 4 A structural block diagram of a memory testing device provided by an embodiment of the present invention is shown. Deployed at the terminal, the device includes:

[0072] A memory simulation module 301, configured to simulate a virtual memory; wherein, the virtual memory includes a virtual front-end interface, an FTL algorithm, and a virtual flash memory;

[0073] A test command sending module 302, configured to send a first test command to the virtual memory through a preset block device driver;

[0074] A test instruction response module 303, configured for the virtual memory to respond to the first test instruction.

[0075] Optionally, the test command sending module 302 is specifically used for the preset block device driver to invoke the virtual front-end interface to parse the first test command to obtain a parsing result;

[0076] Wherein, the parsing result at least includes an operation instruction, an LBA, and a quantity of the LBA, and the opera...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com