BIST and ECC combined memory detection device in system chip

A system chip and detection device technology, applied in static memory, instruments, etc., can solve problems such as increased processing overhead and system performance degradation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The technical solution of the present invention will be further described below in conjunction with the accompanying drawings.

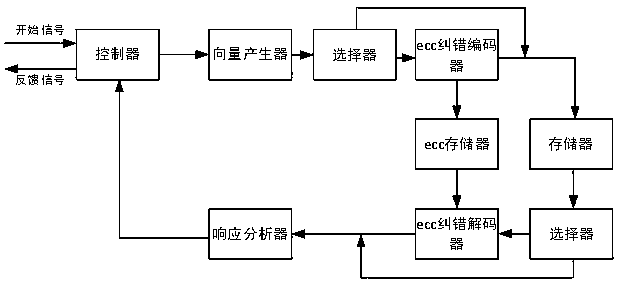

[0035] The memory detection device combining BIST and ECC proposed by the present invention is as follows: figure 1 shown. The whole device is composed of a BIST circuit module, a selector, a memory and an ECC module, and the ECC module includes an ECC memory, an error correction encoder and an error correction decoder. The BIST circuit module is used to receive external test control signals, initiate test operations, manufacture test vectors, test results, and give test result signals; the selector is used to select the ECC module, and the ECC module is used in combination by BIST in a multiplexed manner. The architecture of the system is reconfigurable.

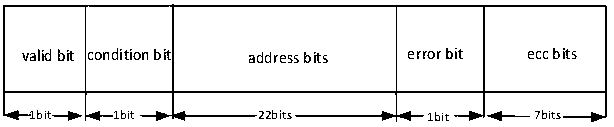

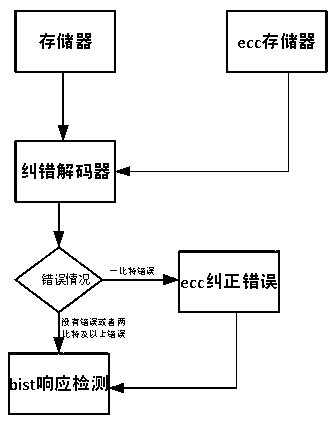

[0036] When the ECC module detects a problem, it cannot be used. At this time, BIST cannot reuse the ECC module, and the selector will not select the ECC module; figure 2 The shown ECC ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More