Data processing method and processing circuit

A processing circuit and data processing technology, which is applied in the field of image processing, can solve the problems of increasing CPU processing load and low processing efficiency, and achieve the effects of reducing CPU load, improving processing efficiency, and efficient outer filling operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

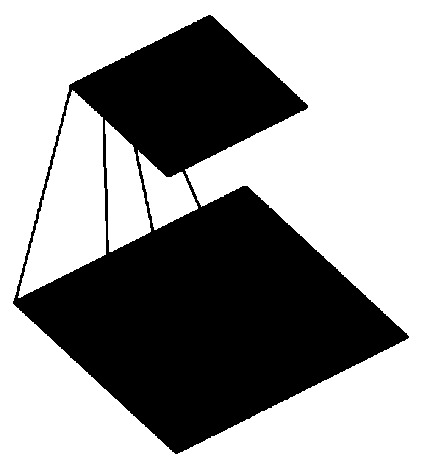

[0035] In the embodiment of the present invention, a data processing method is proposed, which is used to realize the function of variable input length alignment output (such as outer padding operation, etc., such as zero padding operation on the edge of the input feature map), see figure 2 Shown is a schematic flow chart of the data processing method, and the method may include the following steps:

[0036] Step 201, acquire first input data and a data length of the first input data. Wherein, the first input data may include but not limited to: image pixel values; and / or outer padding pixel values.

[0037] Step 202, obtain the first numerical value according to the byte offset and the data length, the first numerical value includes N bits, the value of each bit is the first identification (such as 1) or the second identification (such as 0), every Each bit corresponds to a storage queue, that is, there are N storage queues, and each bit corresponds to a storage queue.

[...

Embodiment 2

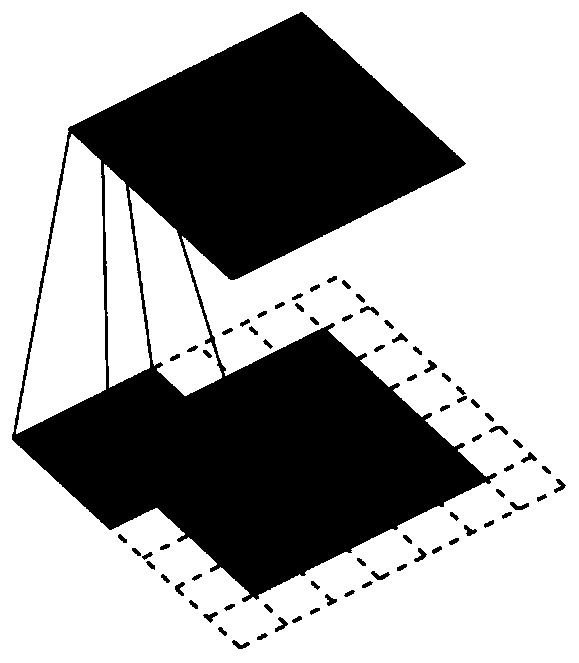

[0053] In the embodiment of the present invention, a data processing method is proposed, which can be applied to a processing circuit, and is used to realize the function of aligning output with variable input length (such as outer padding operation, etc., such as zero padding operation on the edge of the input feature map), to realize An asymmetric storage queue structure with variable transmission length and strong scalability.

[0054] see image 3 As shown, the processing circuit may include a first shift subcircuit, a storage queue, a byte enable subcircuit, a second shift subcircuit and an offset register. The storage queue may be an asymmetric storage queue, such as a FIFO queue. Among them, the number of storage queues is N, and the output data is aligned according to N bytes, that is, the number of storage queues can be configured according to the number of bytes of output data, and the data bit width of each storage queue is 1 byte. The depth is greater than or equa...

Embodiment 3

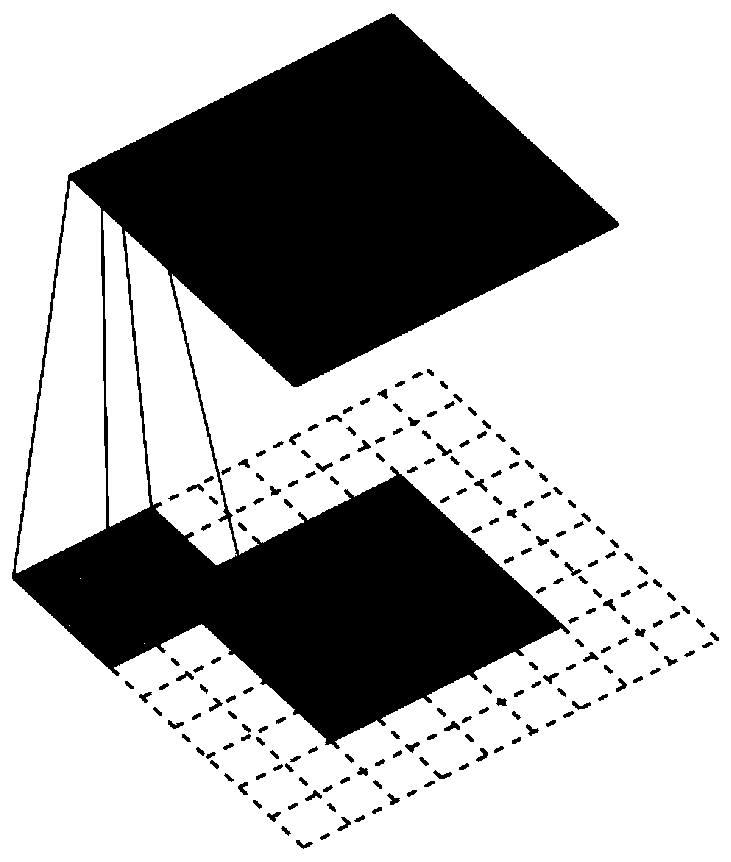

[0077] On the basis of Embodiment 2, the above data processing method will be described in detail below in combination with specific application scenarios. In this application scenario, the number N of storage queues is 16 as an example for illustration.

[0078] First, the first input data 0x11 is acquired, and the data length of the first input data is 1, which means that the length of the first input data is 1 byte, that is, 8 bits. The first input data 0x11 can be the image pixel value of the input feature map (that is, the effective value), it can be the outer padding pixel value of the input feature map (such as the padding value 0), and it can also be the image pixel value of the input feature map and the outer padding Pixel value, there is no limit to this.

[0079] Since the data length is 1, the second value is 0000000000000001. If the byte offset currently stored in the offset register is 0, each bit in the second value is rotated to the left by 0 bits to obtain th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com