A method and device for improving the utilization rate of DDR storage bus

A storage bus, utilization technology, applied in the field of data communication, can solve problems such as inability to adjust, waste of bandwidth and bus resources, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] It should be understood that the specific implementation manners described here are only used to explain the present invention, but not to limit the present invention.

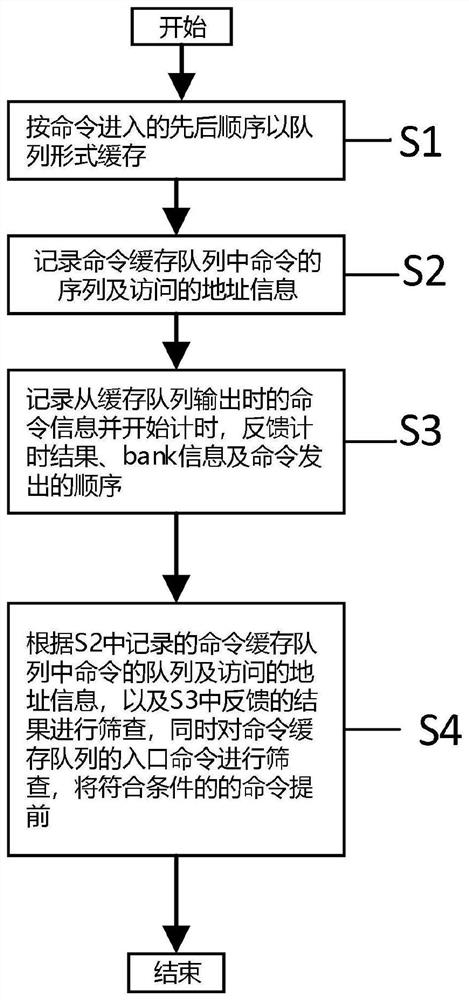

[0026] figure 1 A flow chart of a method for improving storage bus utilization in an embodiment of the present invention is shown, and the process includes the following steps:

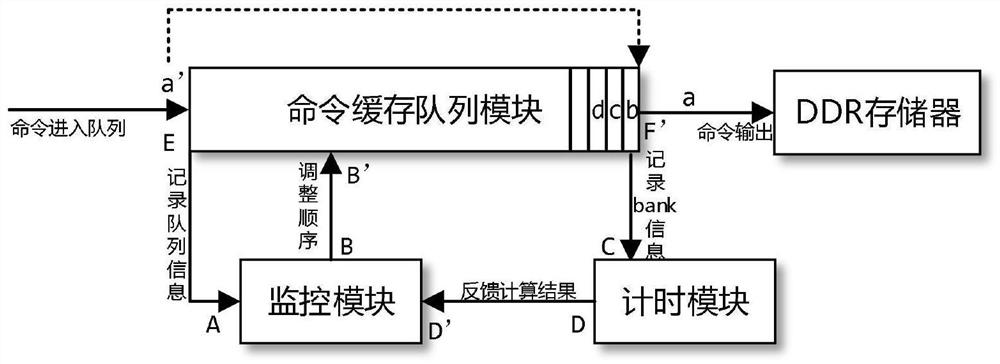

[0027] Step S1, receiving commands, and buffering them according to the order of command entries to form a command buffer queue, and outputting the commands to the DDR memory. In an embodiment, the command buffer queue can be buffered in the command buffer queue module.

[0028] Step S2, while forming the command buffer queue, record the sequence of the commands in the command buffer queue and the address information of the access. In an embodiment, the monitoring module can be used to record the command information in the command buffer queue. When a command is entered into the command cache queue module, the monitoring mod...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More