Method and system for recording working state of digital logic design engineering

A design engineering and digital logic technology, which is applied in the field of recording the working status of digital logic design engineering, can solve problems such as user difficulties, limited signal length, and FPGA debugging work difficulties, and achieve the effect of improving work efficiency and lasting for a long time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

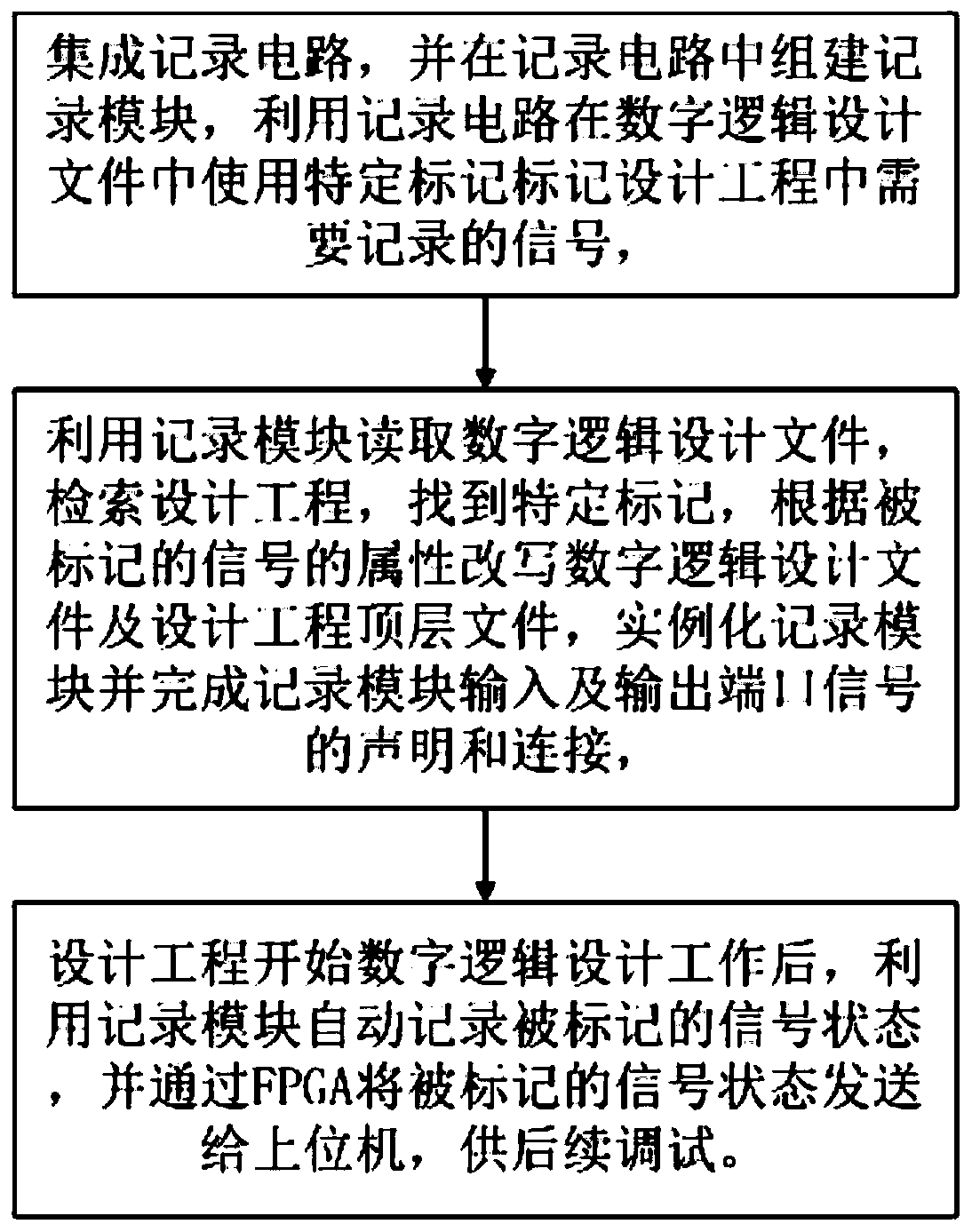

[0025] The invention provides a system for recording the working state of digital logic design engineering, which includes a recording circuit, and a recording module is built in the recording circuit, and the recording circuit uses specific marks in the digital logic design file to mark the signals that need to be recorded in the design project.

[0026] The recording module reads the digital logic design file, retrieves the design project, finds a specific mark, rewrites the digital logic design file and the top-level file of the design project according to the attributes of the marked signal, instantiates the recording module and completes the declaration of the input and output port signals of the recording module and connect,

[0027] After the design project starts the digital logic design work, the recording module automatically records the marked signal state, and sends the marked signal state to the host computer through the FPGA for subsequent debugging.

[0028] At ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More