A split-gate tigbt with self-biased pmos and its fabrication method

A split-gate, self-biased technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of unfavorable device miniaturization development, affecting device stability, uneven distribution of device surface current, etc., to achieve Improve the short-circuit safe working ability, save area, and improve the effect of conductance modulation ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

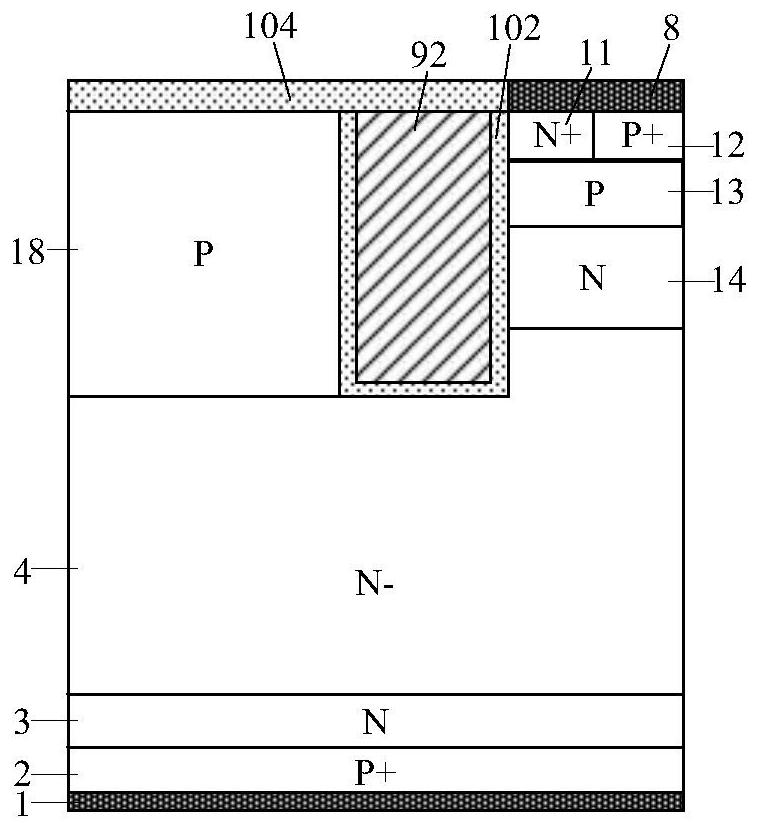

[0054] A split-gate TIGBT with self-biased PMOS, whose half-cell structure is as figure 2 As shown, it includes: back collector metal 1, P-type collector region 2 located on and connected to the back collector metal 1, N-type field stop layer 3 located on and connected to the P-type collector region 2 and The N-drift region 4 located on and connected to the N-type field stop layer 3; the P-type buried layer 5 located on the top of the N-drift region 4 and connected to it, and the P-type base layer located on and connected to the N-drift region 4 Region 13; the N-type doped layer 6 located on the top of the P-type buried layer and connected to it; the P-type doped layer 7 located on the top of the N-type doped layer 6 and connected to it; the upper part of the P-type base region 13 is independent and side by side Placed N+ emitter region 11 and P+ emitter region 12; located on the top of the P-type buried layer 5, the side walls of the N-type doped layer 6, the side walls of th...

Embodiment 2

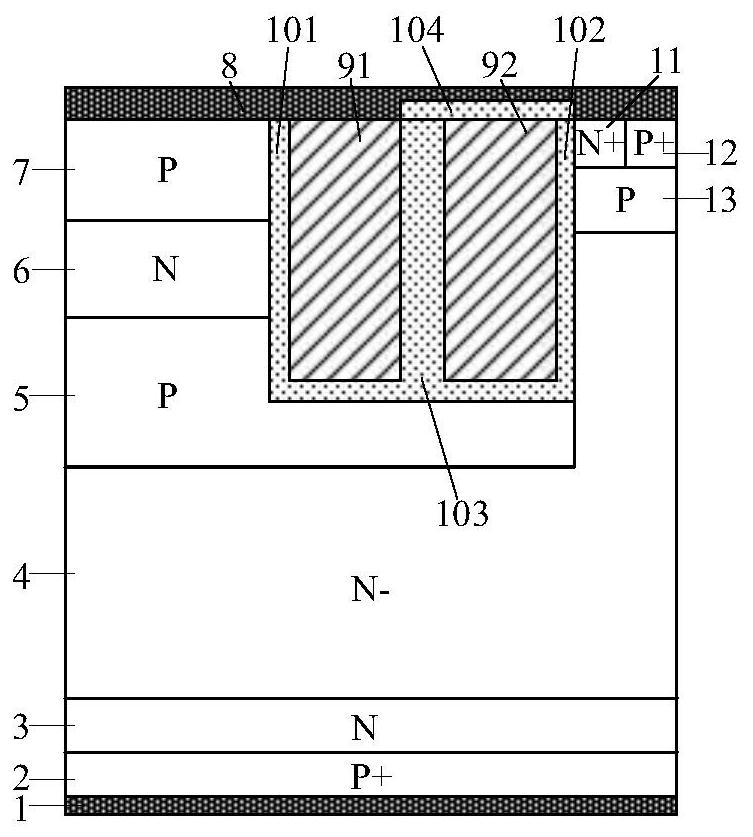

[0056] A split-gate TIGBT with self-biased PMOS, whose half-cell structure is as image 3 As shown, it includes: back collector metal 1, P-type collector region 2 located on and connected to the back collector metal 1, N-type field stop layer 3 located on and connected to the P-type collector region 2 and The N-drift region 4 located on and connected to the N-type field stop layer 3; the P-type buried layer 5 and the N-type charge storage layer 14 located on the upper part of the N-drift region 4 and connected to it; located on the upper part of the N-type charge storage layer The P-type base region 13 connected to it; the N-type doped layer 6 located on the top of the P-type buried layer and connected to it; the P-type doped layer 7 located on the top of the N-type doped layer 6 and connected to it; The N+ emitter region 11 and the P+ emitter region 12 that are independent and placed side by side in the upper part of the region 13; located on the upper part of the P-type buri...

Embodiment 3

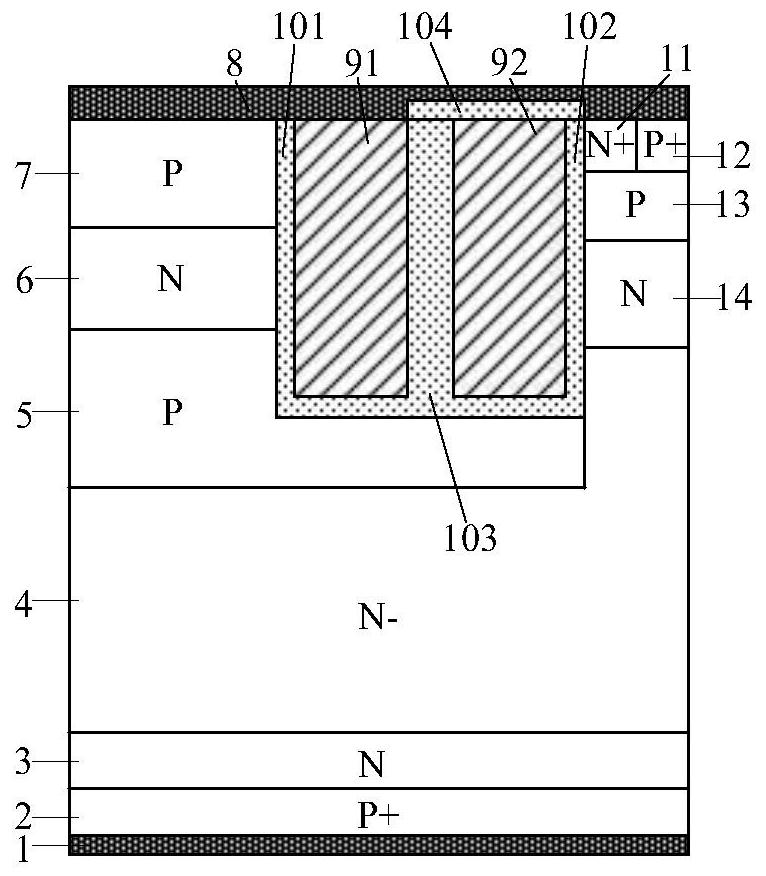

[0058] A split-gate TIGBT with self-biased PMOS, whose half-cell structure is as Figure 4 As shown, this embodiment introduces a Schottky contact metal 15 connected to the P-type doped region 7 on the basis of embodiment 1, and the rest of the structure is the same as that of embodiment 2.

[0059] The Schottky contact metal 15 introduced in this embodiment has the same potential as the emitter metal 1 , and the introduction of the Schottky contact metal 15 can reduce the conduction voltage drop of the PMOS and reduce the switching loss of the device.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More