Multichannel voltage difference sampling circuit and method

A voltage difference, sampling circuit technology, applied in the direction of measuring current/voltage, measuring electrical variables, measuring devices, etc., can solve the problems of large power consumption loop stability, cumbersome circuits, etc., to achieve strong adaptability, circuit power consumption, etc. Drop, the effect of simple circuit structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

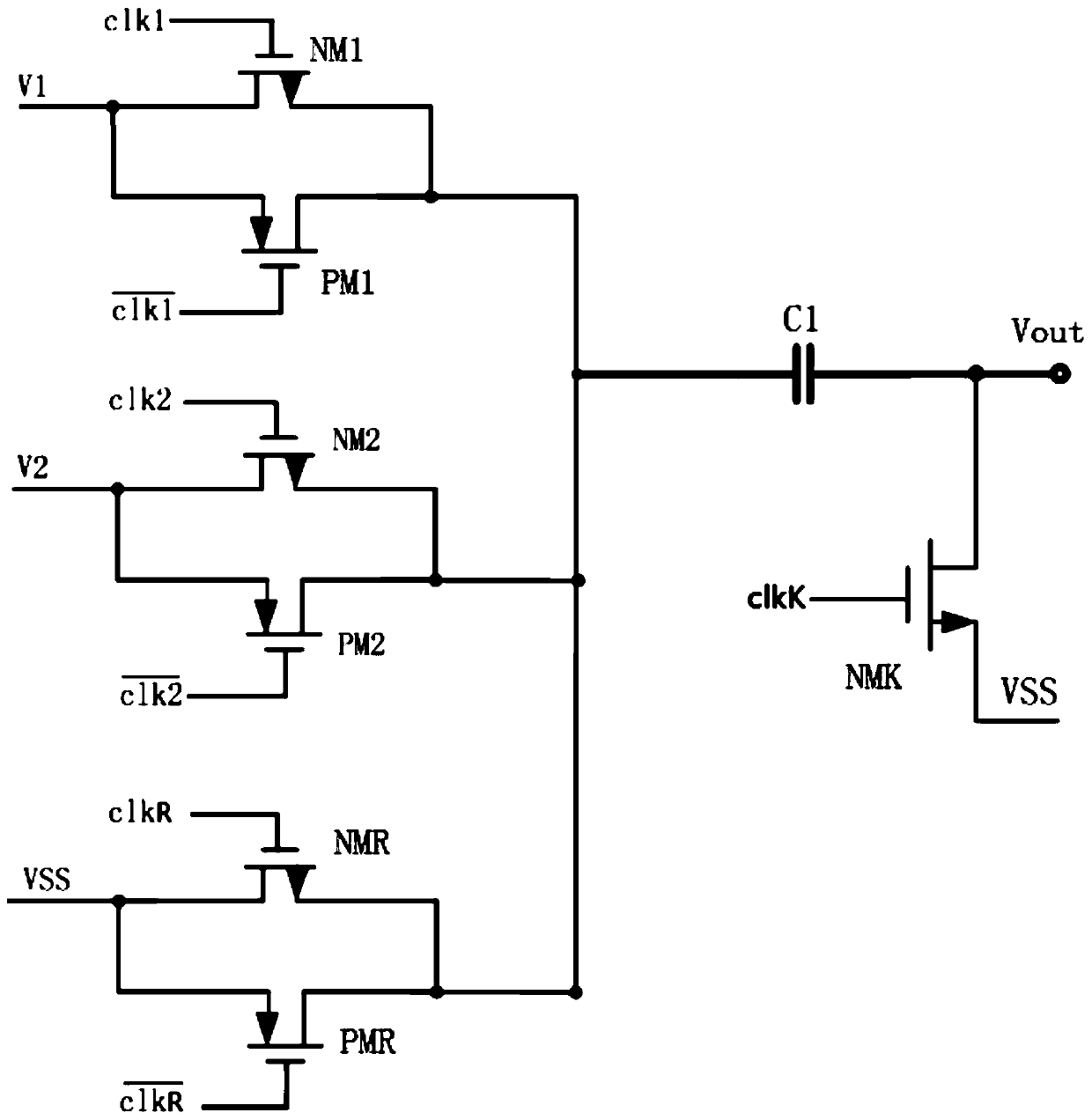

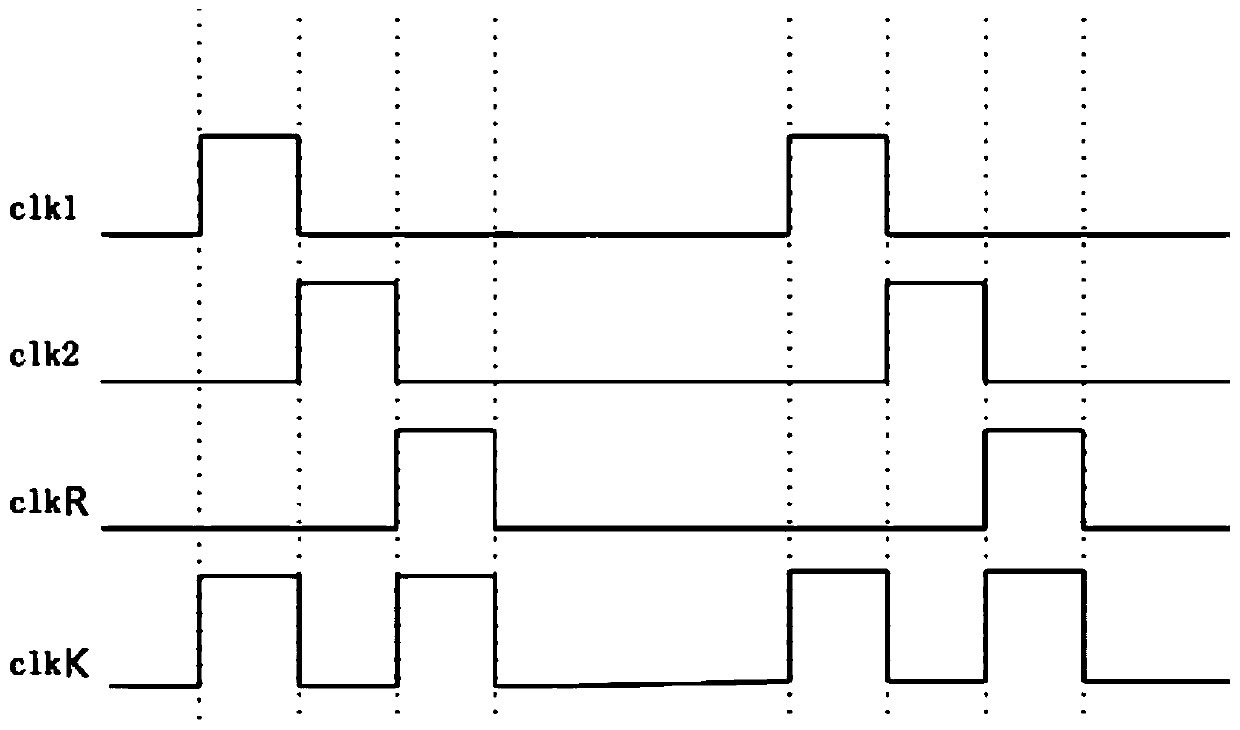

[0018] This embodiment is the simplest mode, there are only two voltage inputs to be sampled, such as figure 1 shown. The first NMOS transistor NM1 and the first PMOS transistor PM1, the second NMOS transistor NM2 and the second PMOS transistor PM2 are paired to form a gate unit, and the reset NMOS transistor and the reset PMOS transistor are paired to form a reset unit. After the output ends of all the gating units and the reset unit are at the same point, the sampling capacitor C1 and the drain of the switching transistor NMK are sequentially connected in series, and the source of the switching transistor NMK is common to the ground. The drain of the first NMOS transistor NM1 and the source of the first PMOS transistor PM1 are connected to the first voltage V1 to be sampled, and the drain of the second NMOS transistor NM2 and the source of the second NMOS transistor NM2 are connected to the second voltage to be sampled. The voltage V2, the drain of the reset NMOS transistor...

Embodiment 2

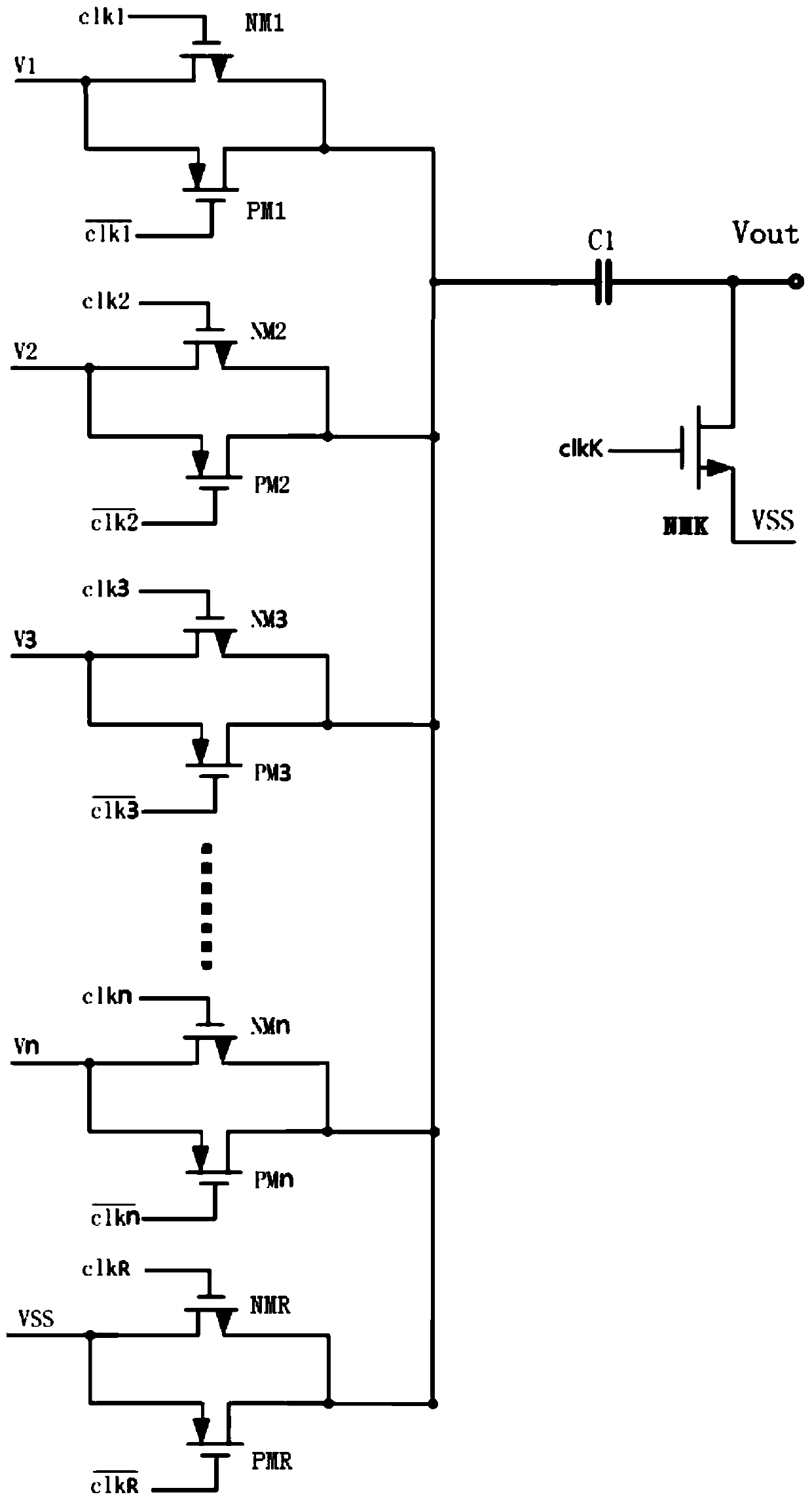

[0025] On the basis of Embodiment 1, a structure of gate expansion is provided, such as image 3 shown. A plurality of gating units with the same structure are added, each gating unit is respectively connected to a voltage to be sampled, and the output terminals of all gating units are connected to the sampling capacitor C1 at a common point.

[0026] By rationally configuring the clock signal, two different voltages to be sampled can be combined arbitrarily and the difference voltage between the two can be obtained for output. if used as Figure 4 The clock signal shown is taken as an example. First, as in the working process of the first embodiment, the differential output of V2-V1 and the reset work are completed in the first to third time sequence intervals. Then complete the V3-V2 differential output and reset work again in the fifth to seventh timing intervals. Finally, Vn-V is completed in the ninth to eleventh timing intervals n-1 differential output and its reset ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More