Dynamic register, data arithmetic unit, chip, computing power board and computing device

A register and latch unit technology, applied in the field of computing power board and computing equipment, chip, data operation unit, dynamic register, can solve the problems of dynamic leakage, data loss, etc., to increase the equivalent capacitance, improve stability, enhance The effect of safety and accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

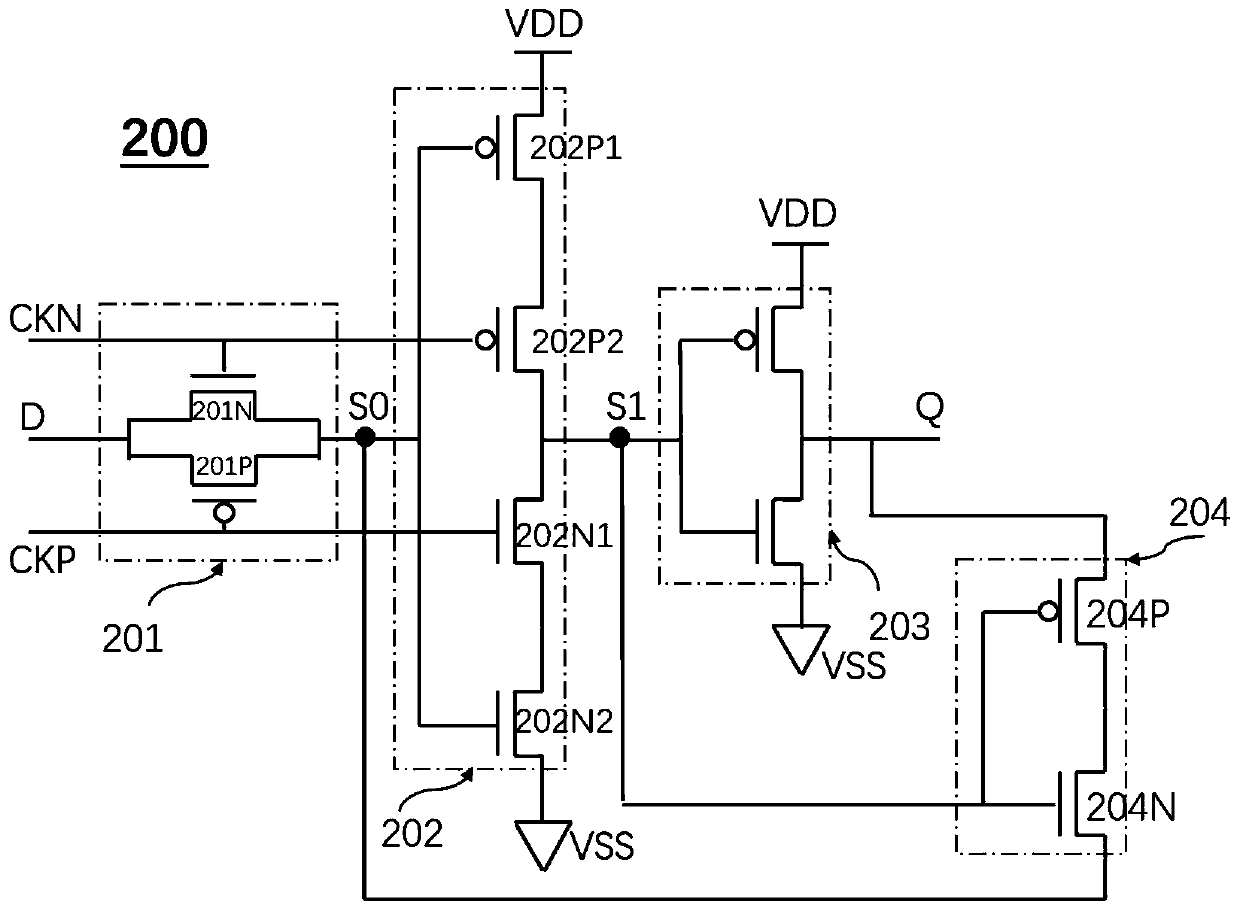

[0057] figure 2 It is a schematic diagram of the circuit structure of a dynamic register according to an embodiment of the present invention. Such as figure 2 As shown, the dynamic register 200 includes an input terminal D, an output terminal Q, a clock signal terminal CKN, a clock signal terminal CKP, a switch unit 201, a latch unit 202, an output drive unit 203, and a leakage compensation unit 204. The switch unit 201, the latch unit 202, and the output drive unit 203 are sequentially connected in series between the input terminal D and the output terminal Q. The switch unit 201 and the latch unit 202 form a first node S0, the latch unit 202 and the output drive A second node S1 is formed between the units 203. The leakage compensation unit 204 is electrically connected between the first node S0, the second node S1 and the output terminal Q. The input terminal D is used to input data, the output terminal is used to output data, the clock signal terminal CKN and the clock s...

Embodiment 2

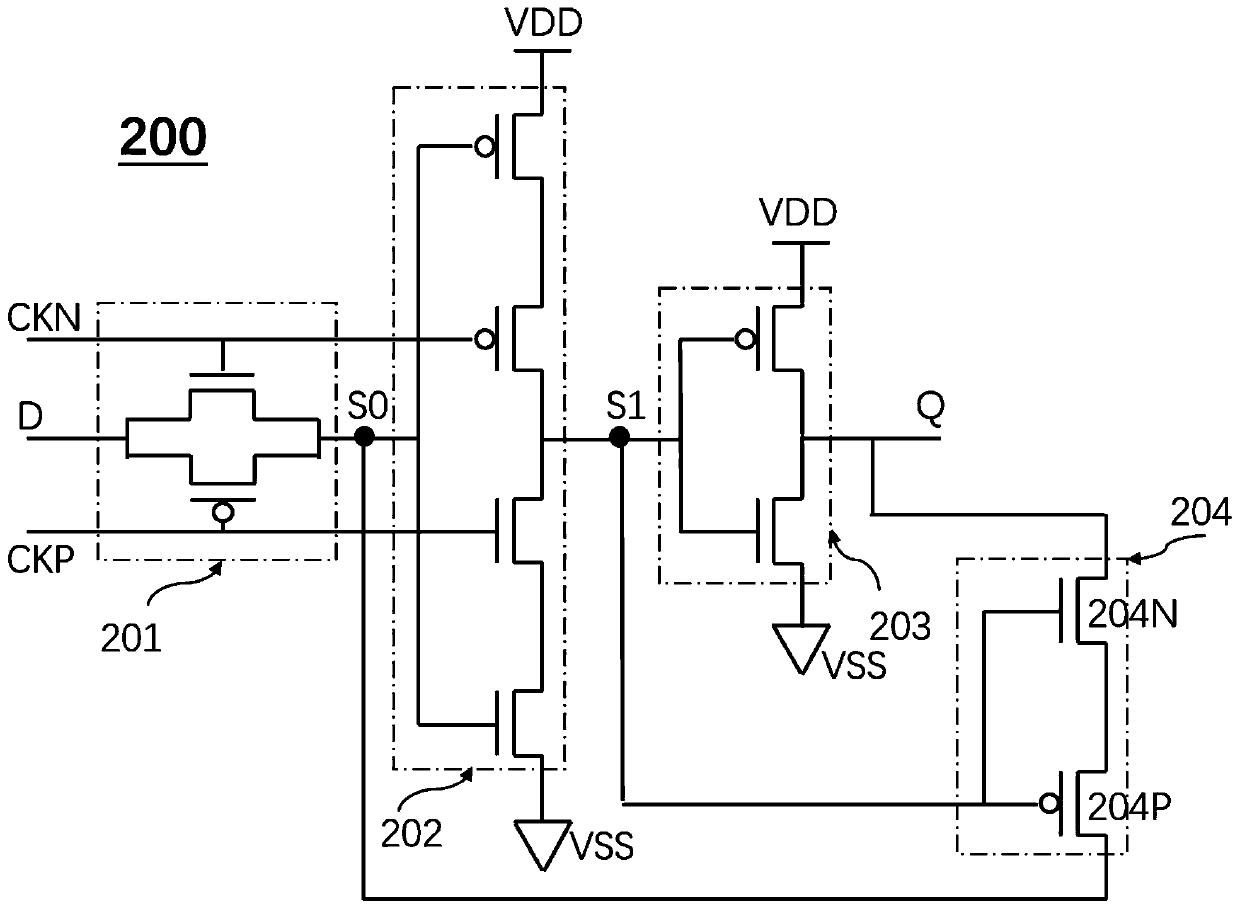

[0067] image 3 It is a schematic diagram of the circuit structure of a dynamic register according to another embodiment of the present invention. Such as image 3 As shown, the dynamic register 200 includes an input terminal D, an output terminal Q, a clock signal terminal CKN, a clock signal terminal CKP, a switch unit 201, a latch unit 202, an output drive unit 203, and a leakage compensation unit 204. The switch unit 201, the latch unit 202, and the output drive unit 203 are sequentially connected in series between the input terminal D and the output terminal Q. The switch unit 201 and the latch unit 202 form a first node S0, the latch unit 202 and the output drive A second node S1 is formed between the units 203. The leakage compensation unit 204 is electrically connected between the first node S0, the second node S1 and the output terminal Q. The input terminal D is used to input data, the output terminal is used to output data, the clock signal terminal CKN and the cloc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More