Formation method of metal gate and semiconductor device

A technology of metal gates and semiconductors, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as metal gates are prone to defects, reduce the control ability of metal gates, and achieve the effect of avoiding holes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

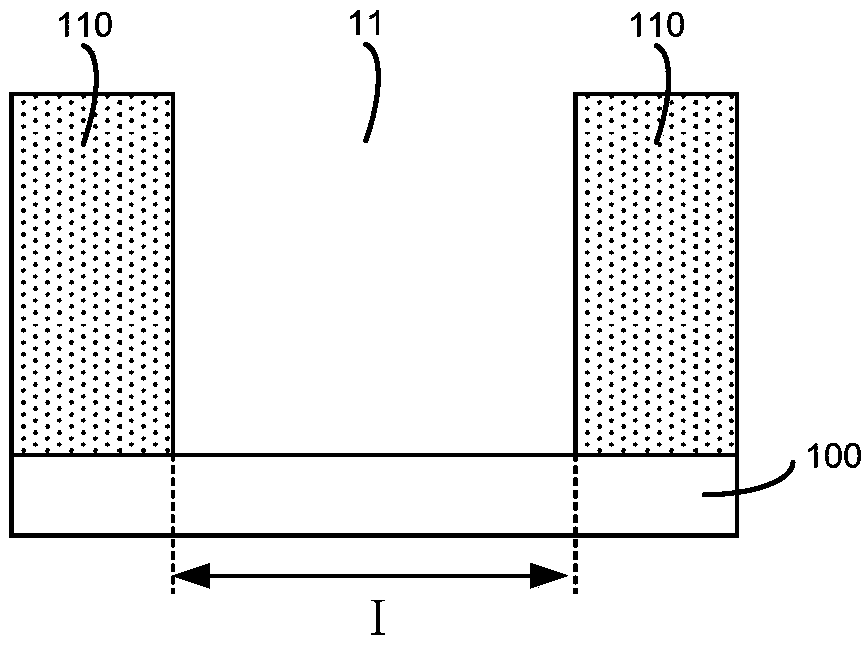

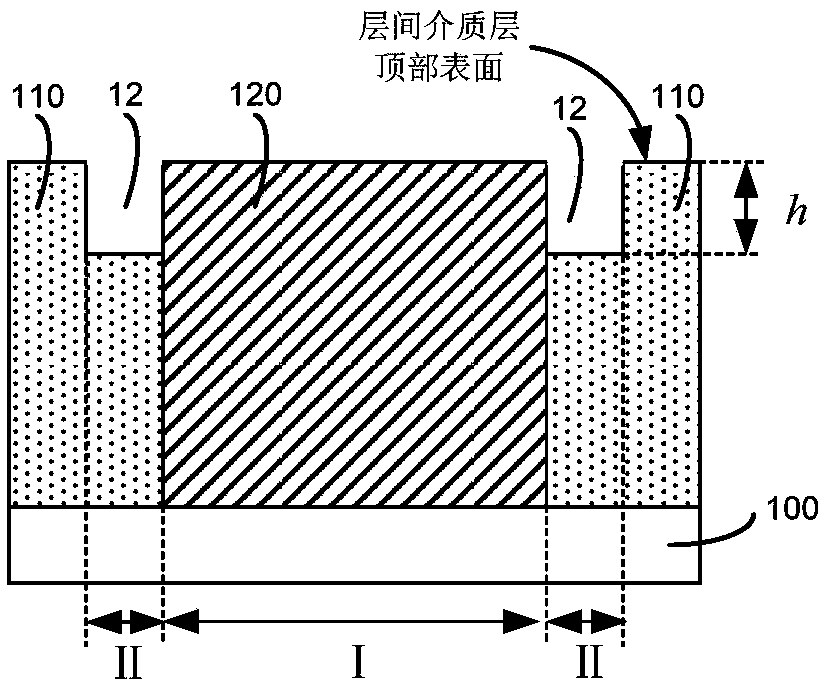

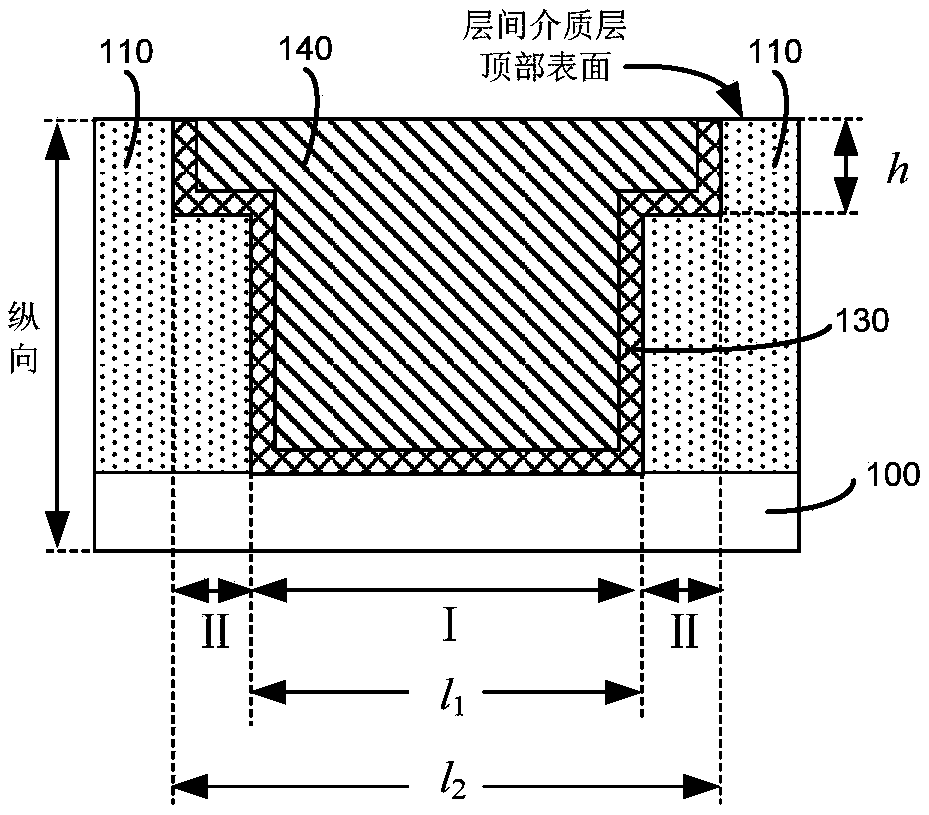

[0038] Please refer to figure 1 , an interlayer dielectric layer 110 is formed on the semiconductor substrate 100 , and a first groove 11 is formed in the interlayer dielectric layer 110 .

[0039] The semiconductor substrate 100 serves as a basis for semiconductor device processes. The material of the semiconductor substrate 100 is polysilicon. In an embodiment of the present invention, the semiconductor substrate 100 includes other semiconductor components (not shown).

[0040] The interlayer dielectric layer 110 plays an insulating role for isolating different structures in the device. In the embodiment of the present invention, the interlayer dielectric layer 110 is formed above the semiconductor substrate 100, and the material of the interlayer dielectric layer 110 is SiO 2 .

[0041] A first groove 11 is formed in the interlayer dielectric layer 110 for subsequent formation of a metal gate therein. figure 1 The area I in the center represents the area range of the...

no. 2 example

[0084] Compared with the first embodiment, the second embodiment of the present invention differs in that, in the method for forming the metal gate in the second embodiment, after forming the first groove and before forming the dummy gate, it also includes The groove sidewall forms a sidewall, and the second groove is formed above the sidewall. The formation method and positional relationship of the structures of other parts are consistent with the first embodiment.

[0085] Please refer to Figure 6 A side wall 211 is formed on the side wall of the first groove, and a second groove 22 is formed above the side wall 211 .

[0086] The formation method and positional relationship of the semiconductor substrate 200 , the interlayer dielectric layer 210 , the first groove, and the dummy gate 220 are consistent with those of the first embodiment, and will not be repeated here.

[0087] Forming the spacer wall 211 can further optimize the function of isolating subsequent metal gat...

no. 3 example

[0102] The difference between the metal gate forming method of the third embodiment of the present invention and the second embodiment is that the second groove is formed by etching part of the interlayer dielectric layer and the spacer. The formation processes of other structures are consistent with the second embodiment.

[0103] Please refer to Figure 8 , forming second grooves 32 on both sides of the dummy gate 320 .

[0104] The process conditions for forming the second groove 32 , and finally the position and size range of the second groove 32 are consistent with those of the second embodiment, and will not be repeated here.

[0105] Obviously, in the embodiment of the present invention, the second groove 32 is formed by etching the sidewall 311 and part of the interlayer dielectric layer 310 adjacent to the sidewall 311, so the bottom of the second groove 32 includes the sidewall 311 The top and part of the interlayer dielectric layer. The process conditions for for...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More