Chip verification auxiliary environment and chip verification system

A verification environment and chip technology, applied in computer-aided design, special data processing applications, instruments, etc., can solve the problems of error-prone, heavy workload, time-consuming and laborious, etc., to speed up the progress, improve the speed of verification, and reduce verification. effect of times

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In order to understand the technical solutions of the present invention more clearly, the present invention will be further described below in conjunction with the examples. The specific examples are only limited to the content of the solution for the convenience of explaining the present invention, and the protected content of the present invention is not limited to the content disclosed in the specific examples.

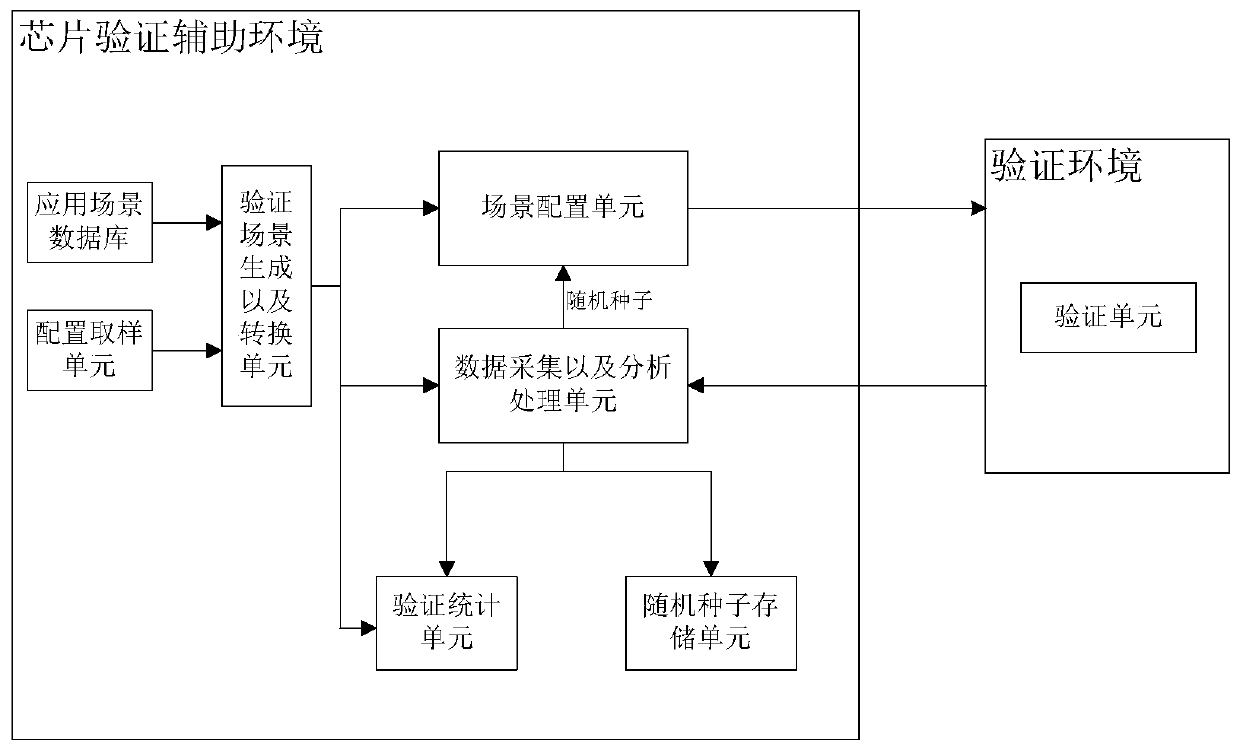

[0030] This embodiment provides a chip auxiliary environment, which is used to cooperate with the chip verification environment to perform automatic verification of the chip; the verification environment includes a verification unit, and the chip verification auxiliary environment includes an application scene database, a configuration sampling unit, A verification scenario generation and conversion unit, a scenario configuration unit, a data collection and analysis processing unit, a verification statistics unit, and a random seed storage unit.

[0031] The ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More