Write-back circuit and method for improving reading stability of sensitive amplifier

A sensitive amplifier and stability technology, which is applied in the field of write-back circuit to improve the reading stability of the sensitive amplifier, can solve problems such as data loss, and achieve the effect of improving reliability and reading stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

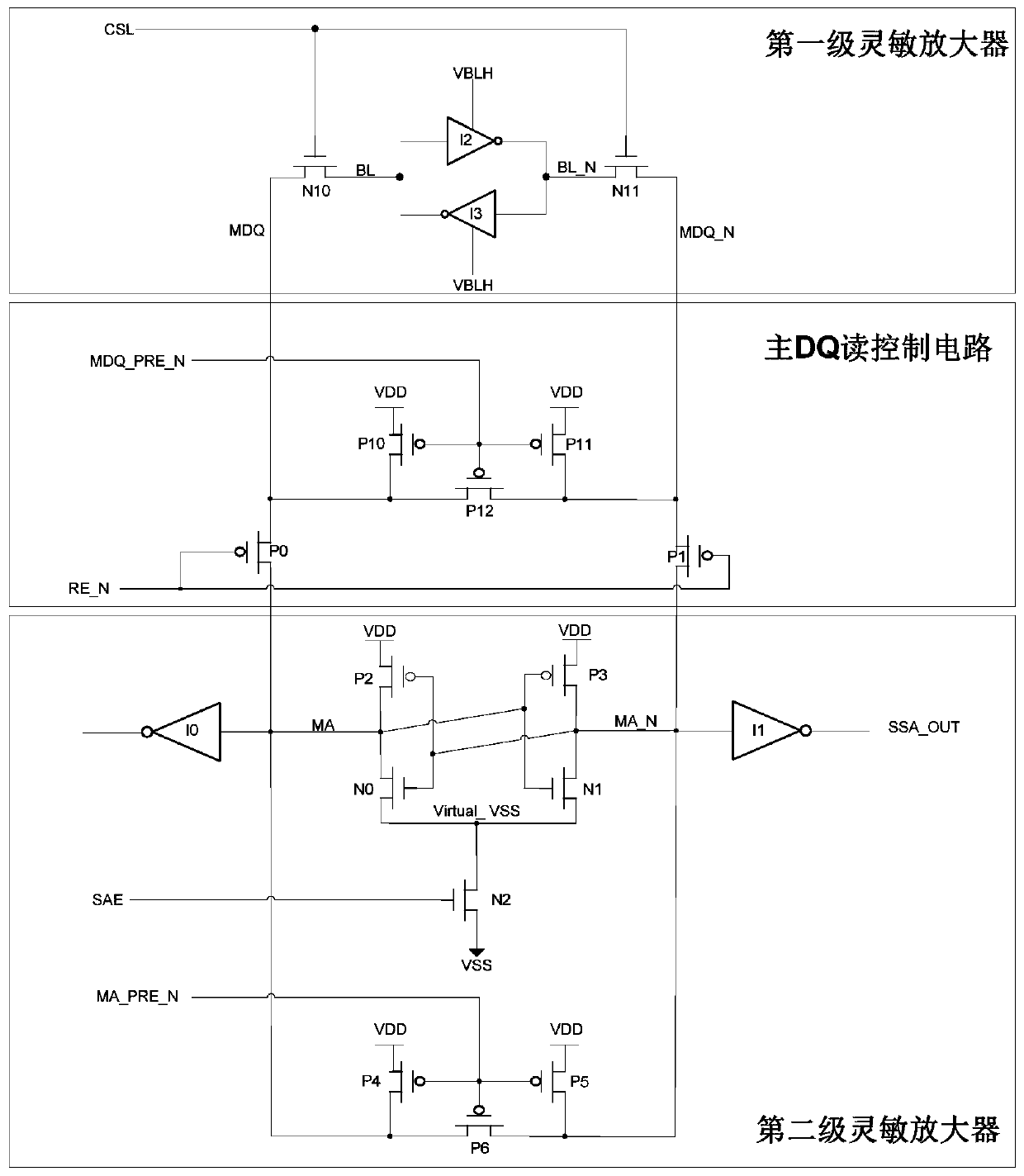

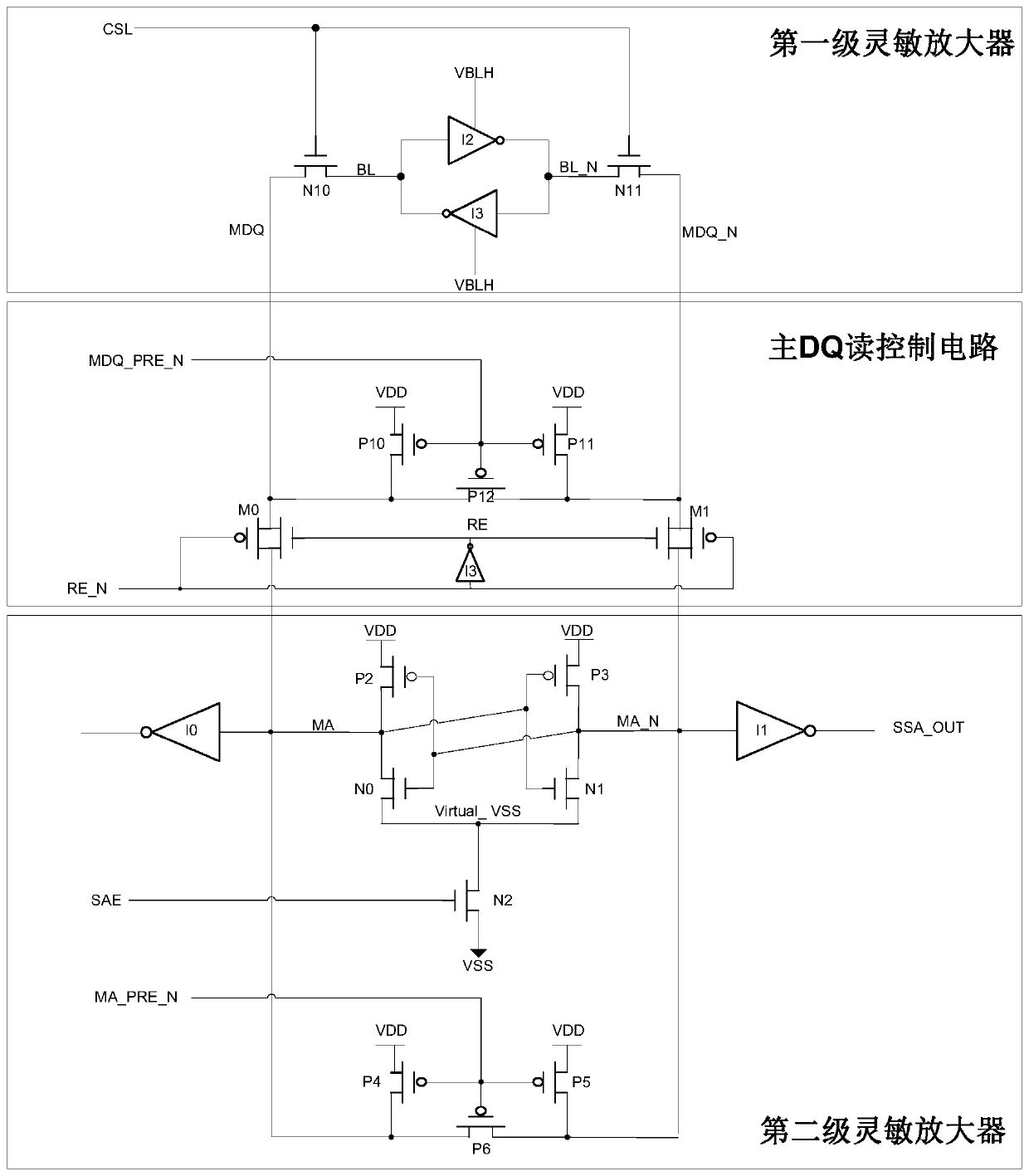

[0061] see figure 2 as shown, figure 2 A write-back circuit for improving the read stability of the sense amplifier of the present invention includes a first-stage sense amplifier, and the NMOS transistor N10 and the NMOS transistor N11 are connected to the first-stage sense amplifier and the main DQ read control circuit; the precharge PMOS transistor P10 and the PMOS The transistor P11 and the balance PMOS transistor P12 form the pre-charging circuit of the main DQ, and the transmission tube M0 and the transmission tube M1 are connected to the main DQ read control circuit and the second-stage sense amplifier.

[0062] The power supply of the first-stage sense amplifier is connected to VBLH, the sources of the NMOS transistor N10 and the NMOS transistor N11 are respectively connected to the bit line BL and the bit line inversion signal BL_N, and the gates of the NMOS transistor N10 and the NMOS transistor N11 are connected to the column selection line CSL signal, The drains...

Embodiment 2

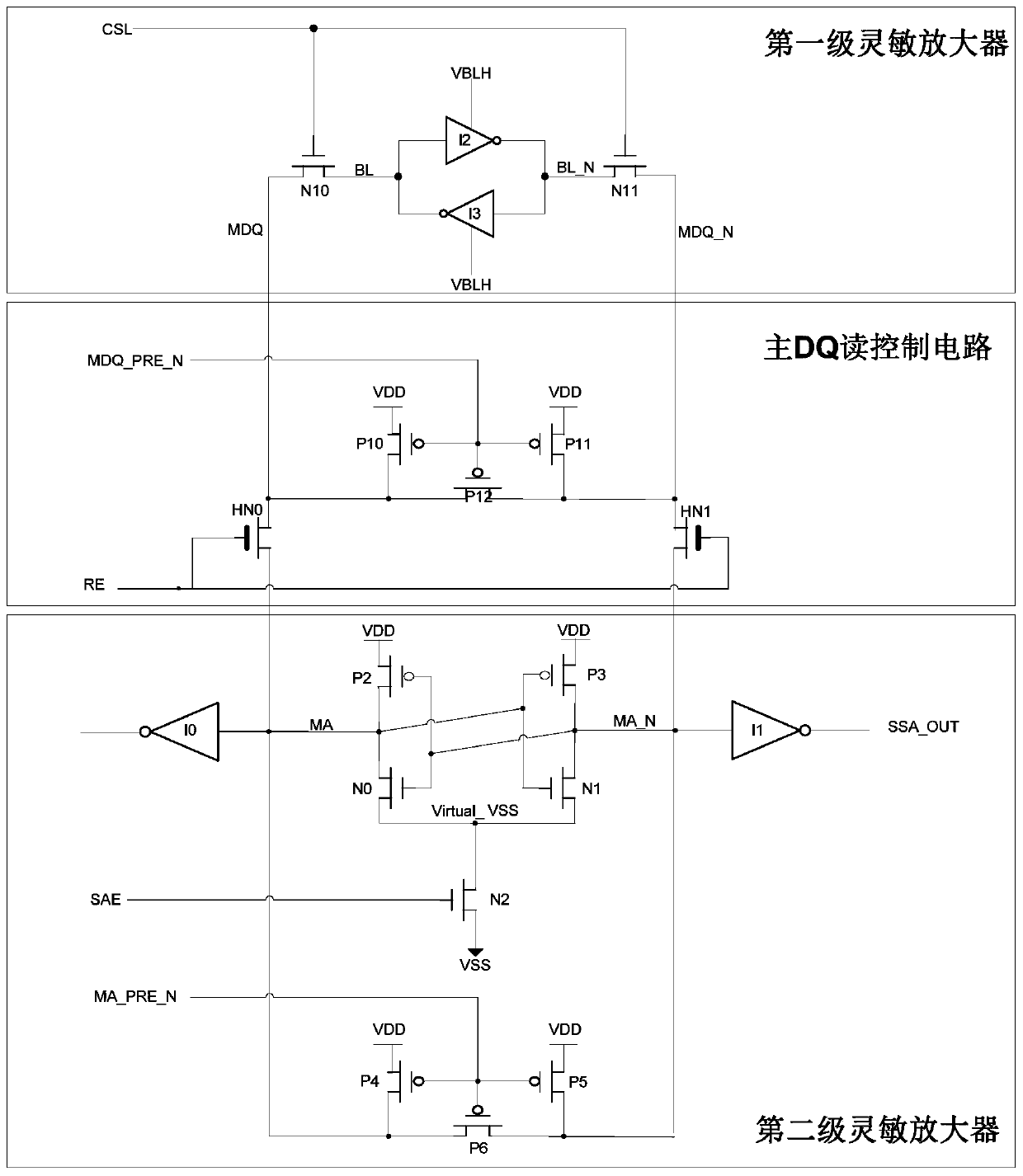

[0070] image 3 Shown is the schematic of the second write-back circuit to improve the read stability of the sense amplifier. Including the first-stage sense amplifier, the NMOS transistor N10 and NMOS transistor N11 are connected to the first-stage sense amplifier and the main DQ read control circuit; the pre-charge PMOS transistor P10, PMOS transistor P11 and equalization PMOS transistor P12 form the pre-charge circuit of the main DQ, thick The gate NMOS transistor HN0 and the transistor HN1 are connected to the main DQ and the second-stage sense amplifier.

[0071] The power supply of the first-stage sense amplifier is connected to VBLH, the sources of NMOS transistor N10 and NMOS transistor N11 are connected to the bit line BL and the bit line inverse signal BL_N, the gates of N10 and N11 are connected to the column selection line CSL signal, and the drains of N10 and N11 The poles are respectively connected to the amplification lines MDQ / MDQ_N.

[0072] The gates of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More