High-speed level conversion circuit applied to mixed voltage output buffer

A technology of output buffer and conversion circuit, which is applied in the direction of logic circuit coupling/interface, logic circuit, and logic circuit interface device using field effect transistors, and can solve the problems of slow conversion speed and the like

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The technical solutions in the embodiments of the present invention will be described clearly and in detail below with reference to the drawings in the embodiments of the present invention. The described embodiments are only some of the embodiments of the invention.

[0016] The technical scheme that the present invention solves the problems of the technologies described above is:

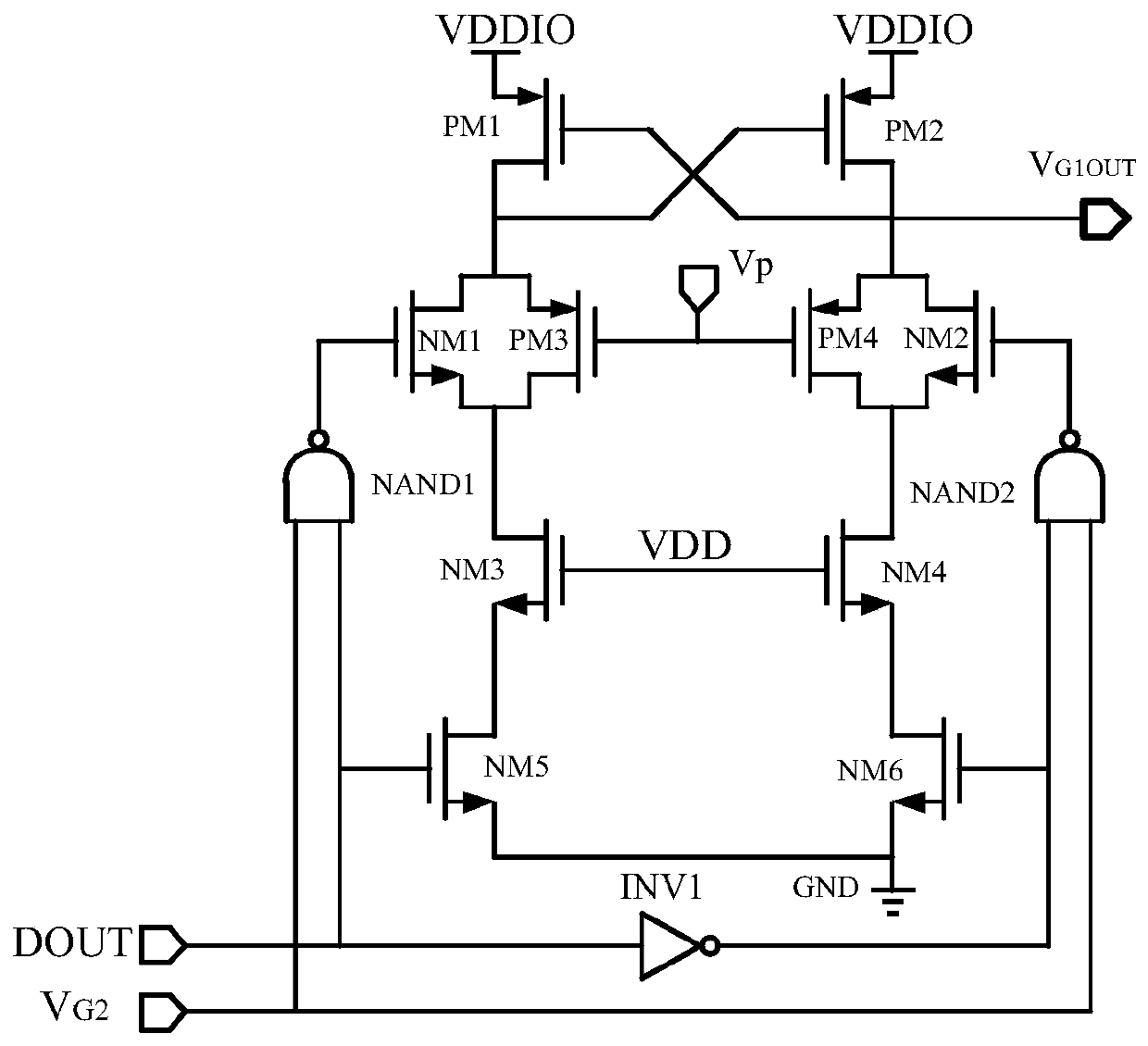

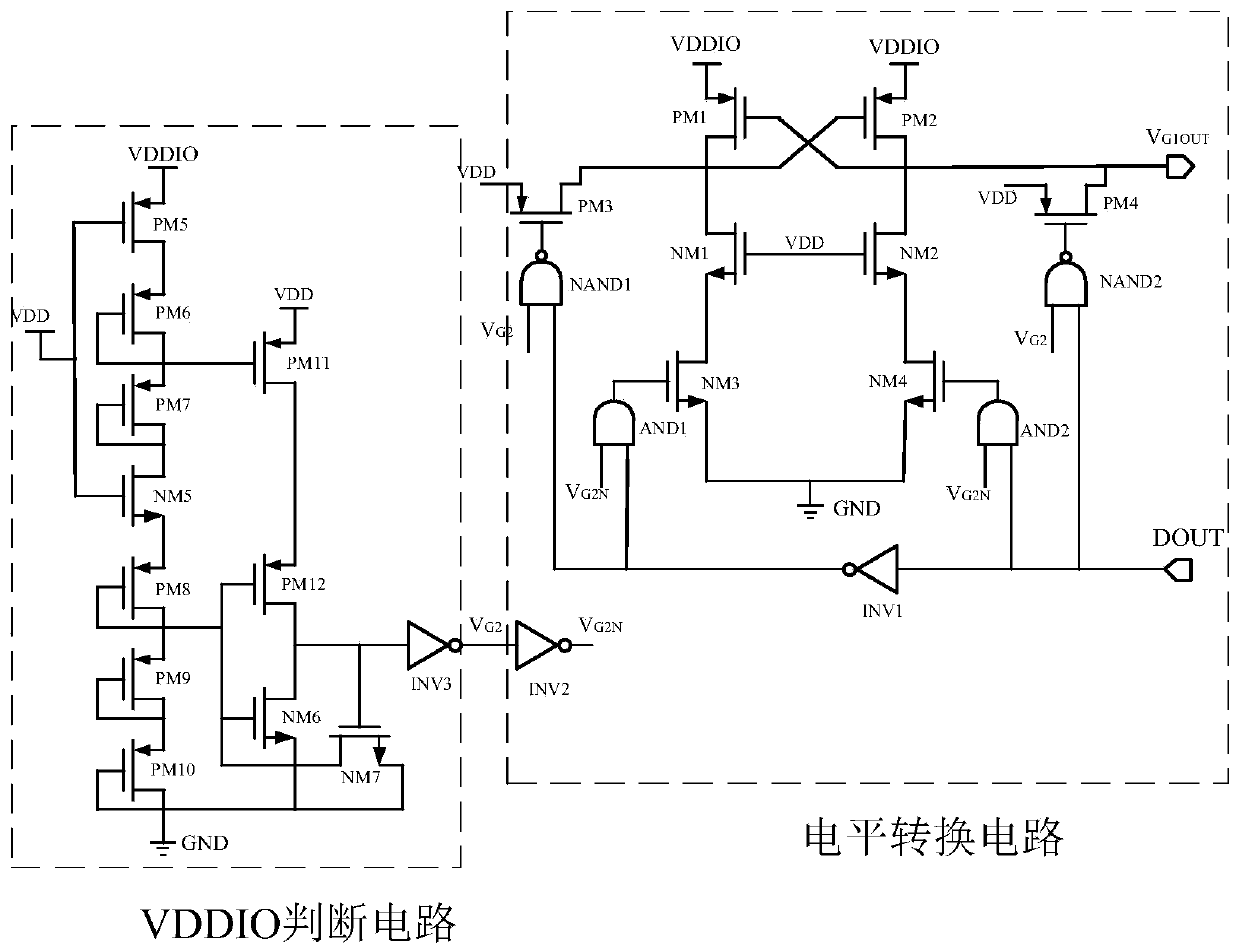

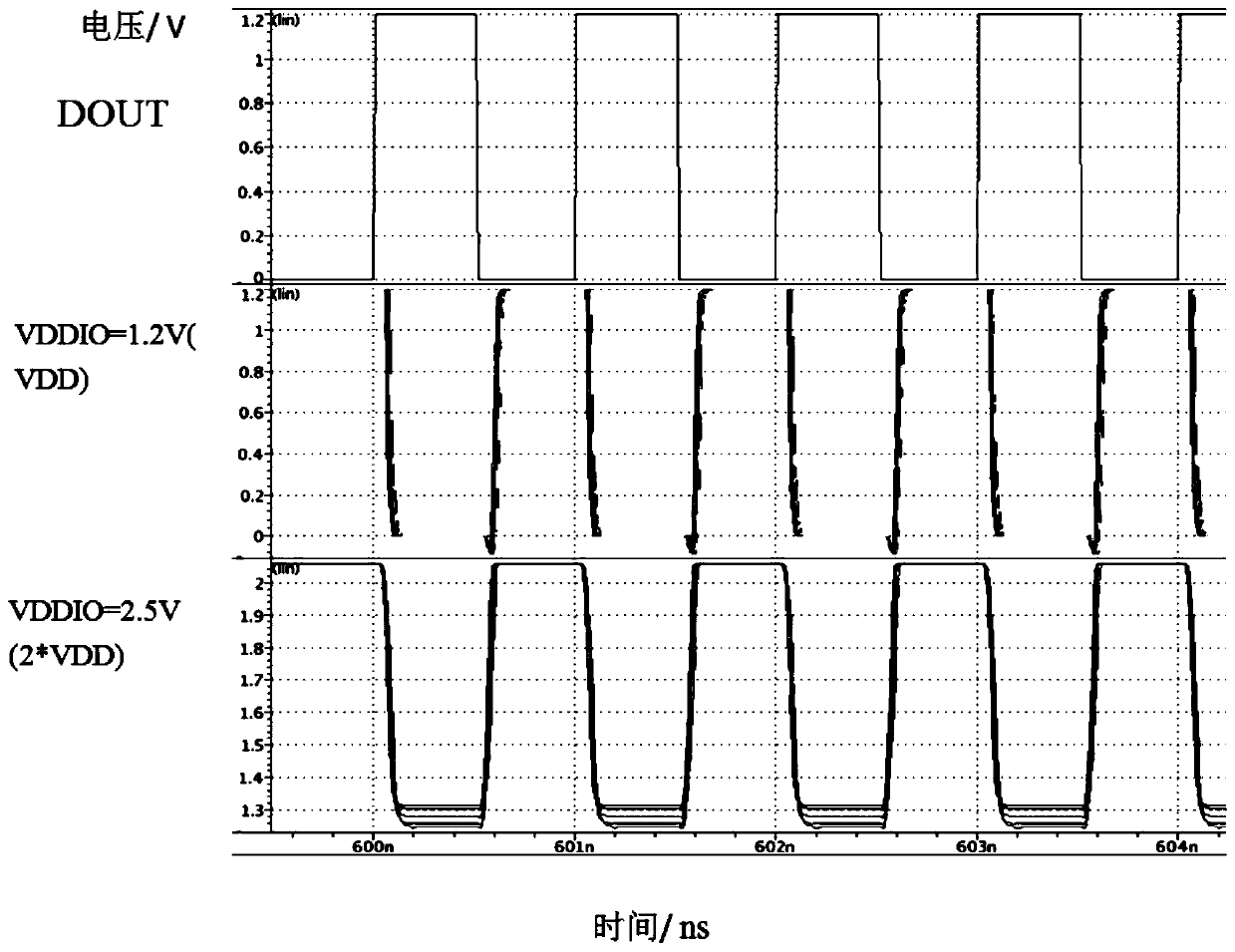

[0017] figure 1 Shown is a conventional mixed voltage level translation circuit. The circuit can realize the voltage conversion of VDDIO=VDD / 2*VDD, the input signal DOUT is the pulse signal for conversion and transmission, and VG2 is the judgment signal of the VDDIO voltage value. The circuit principle is as follows. In VDDIO=VDD mode, VG2 is logic "0", at this time, NMOS tubes NM1 and NM2 are kept on. When DOUT = "1", NM5 is on and NM6 is off, so the drain voltage of NM1 is GND. After turning on PM2, V G1OUT The voltage is VDDIO=VDD; similarly, when DOUT="0", NM5 is off and NM6 is on, s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com