Patents

Literature

32results about How to "Meet the delay requirements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Coding Approach For A Robust And Flexible Communication Protocol

ActiveUS20130114481A1Easy to implementEffective serviceNetwork traffic/resource managementAssess restrictionTransmission protocolNetwork Communication Protocols

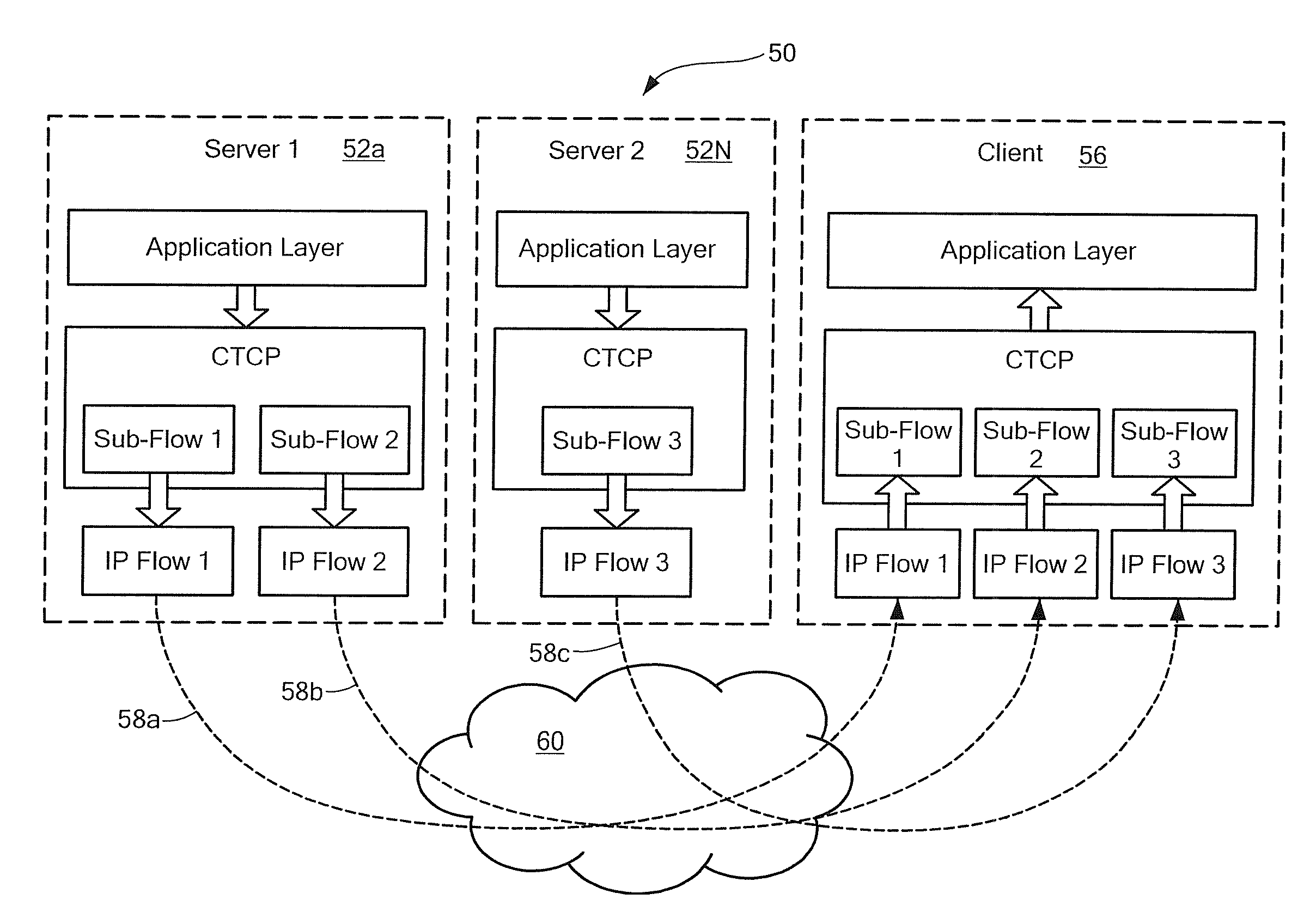

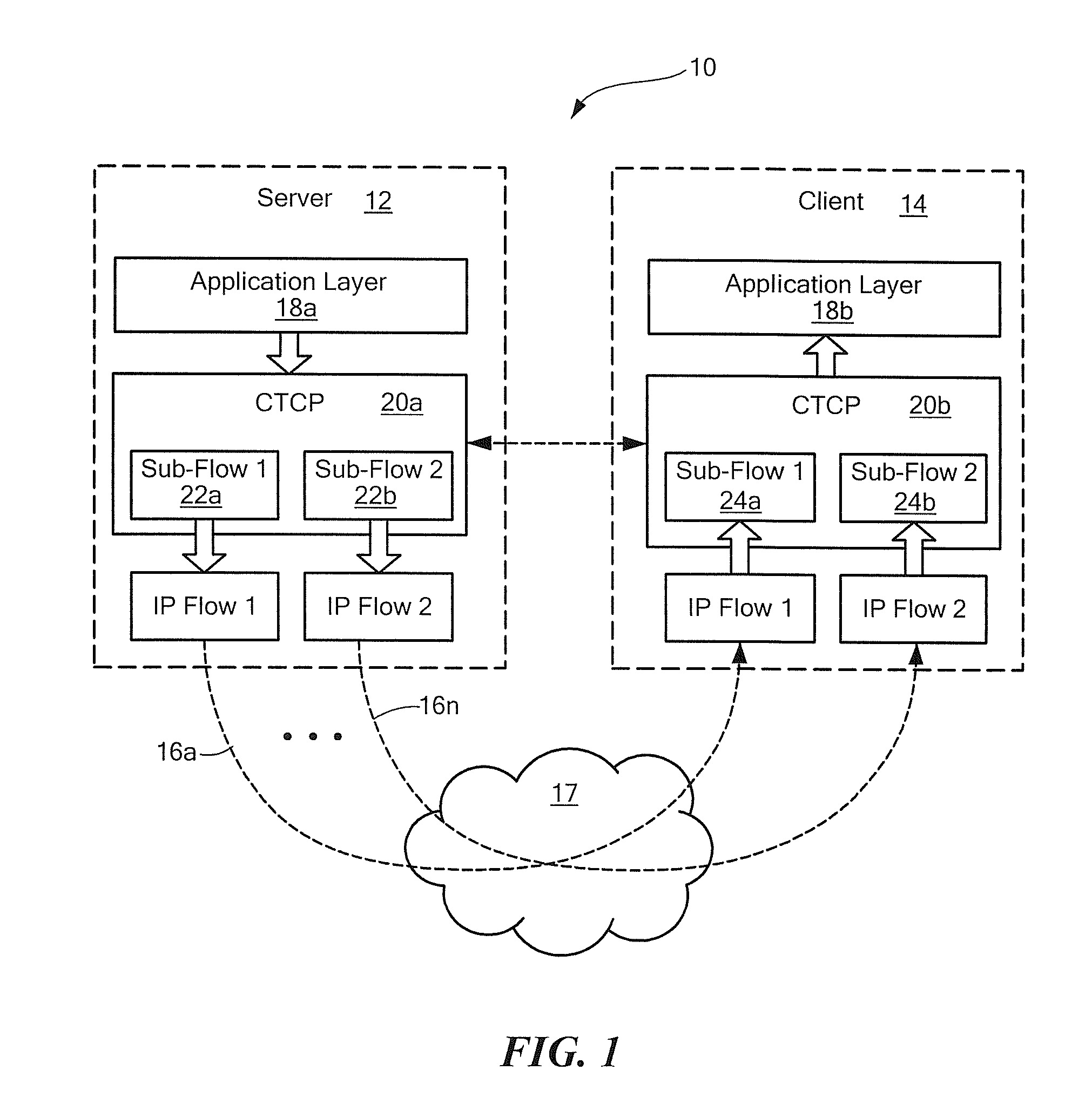

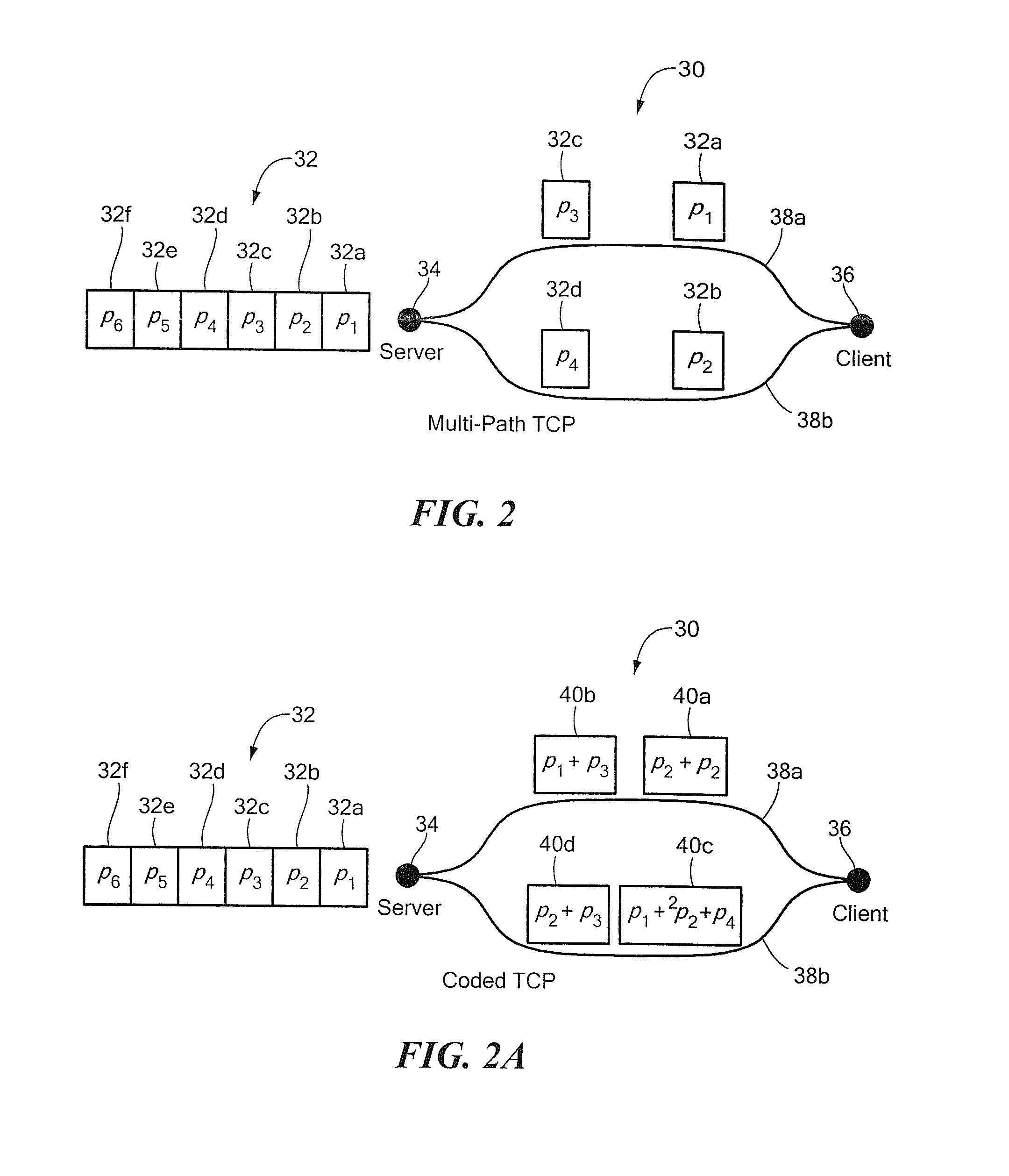

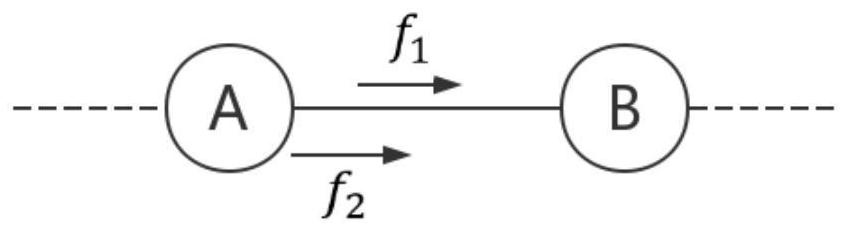

A coding approach for a robust and flexible network communication protocol is described. By using coding, it is possible to eliminate the need to track packet identities, and hence, it is possible to reduce coordination overhead associated with many conventional protocols. The method and system described herein takes advantage of multiple paths, interfaces, mediums, servers, and storage locations available in a network. The proposed protocol allows quick response to congestion by load balancing over different network resources. The method also enables soft vertical hand-overs across heterogeneous networks. In one embodiment, a media file is divided into chunks and transmitted using a transport protocol tailored to meet delay requirements of media streaming applications. Also described are different coding strategies for chunk delivery based upon an urgency level of each chunk.

Owner:MASSACHUSETTS INST OF TECH

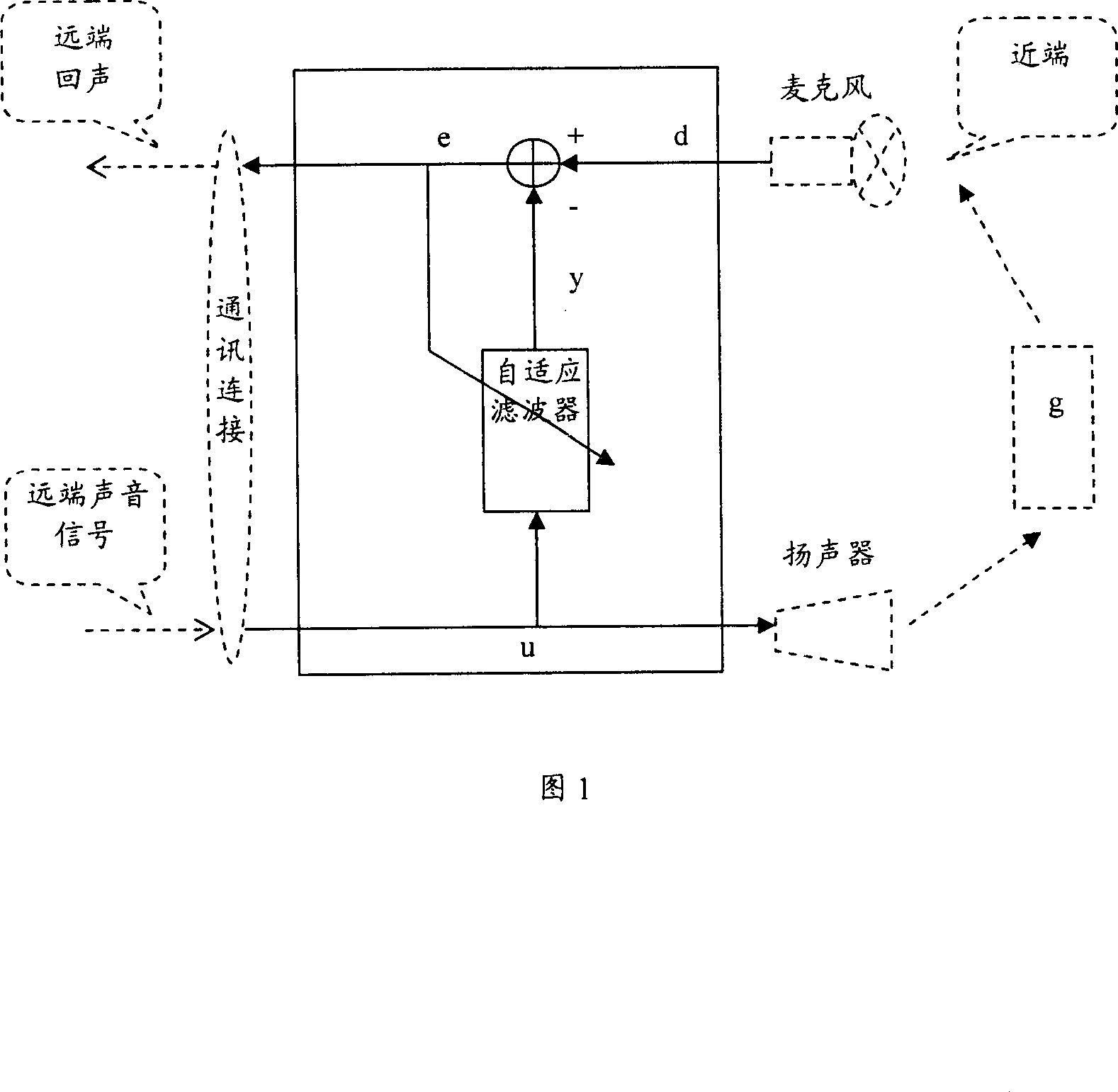

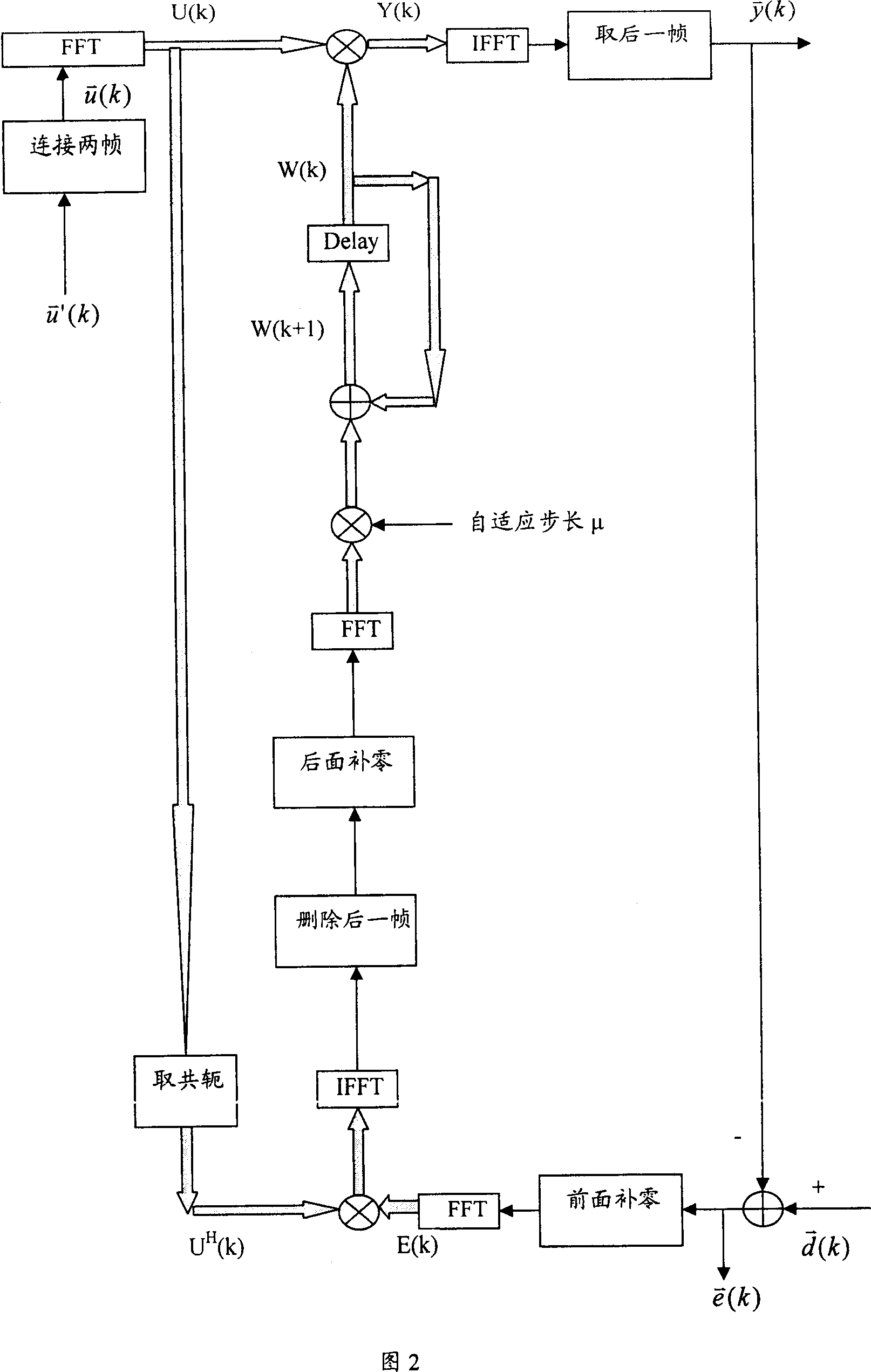

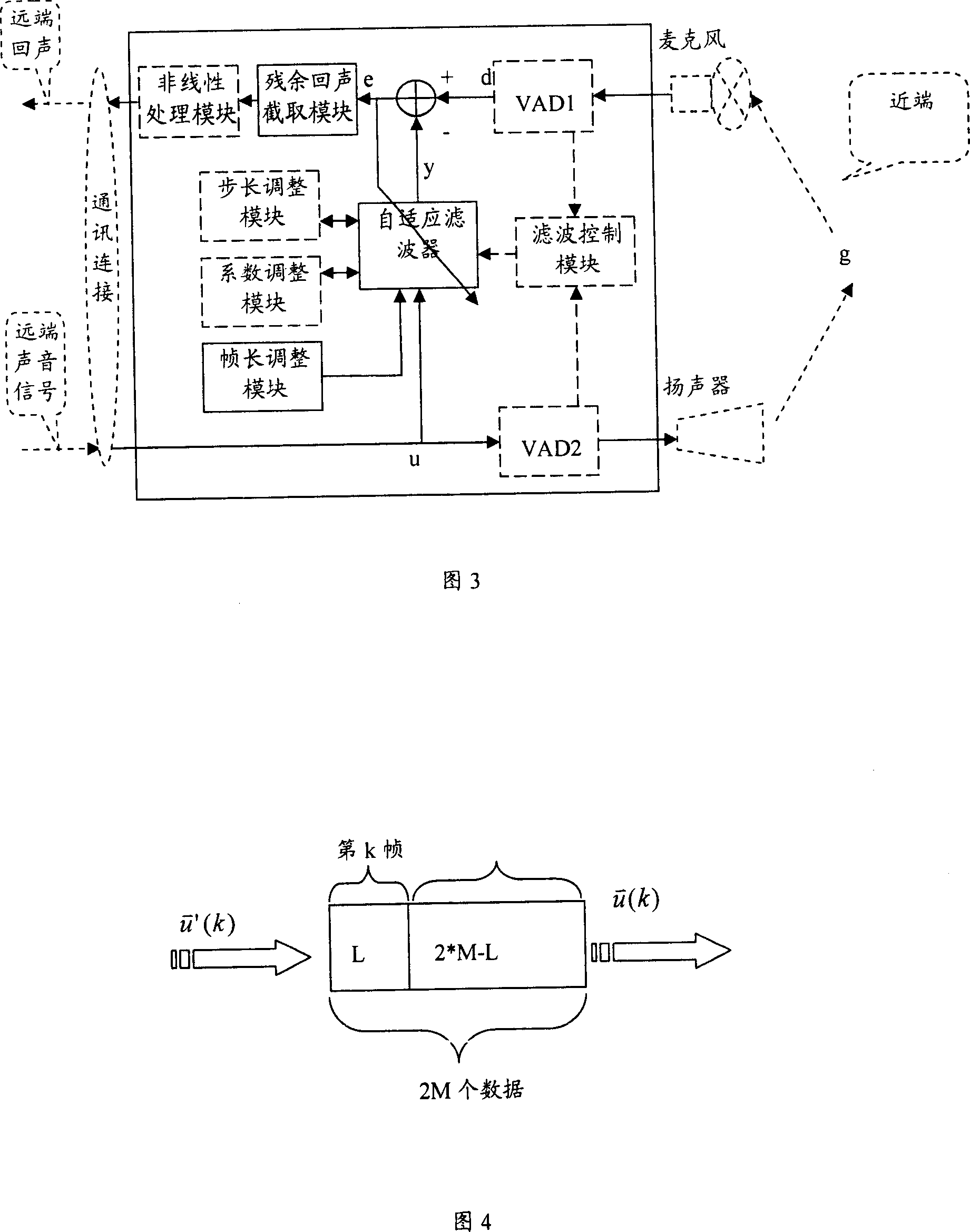

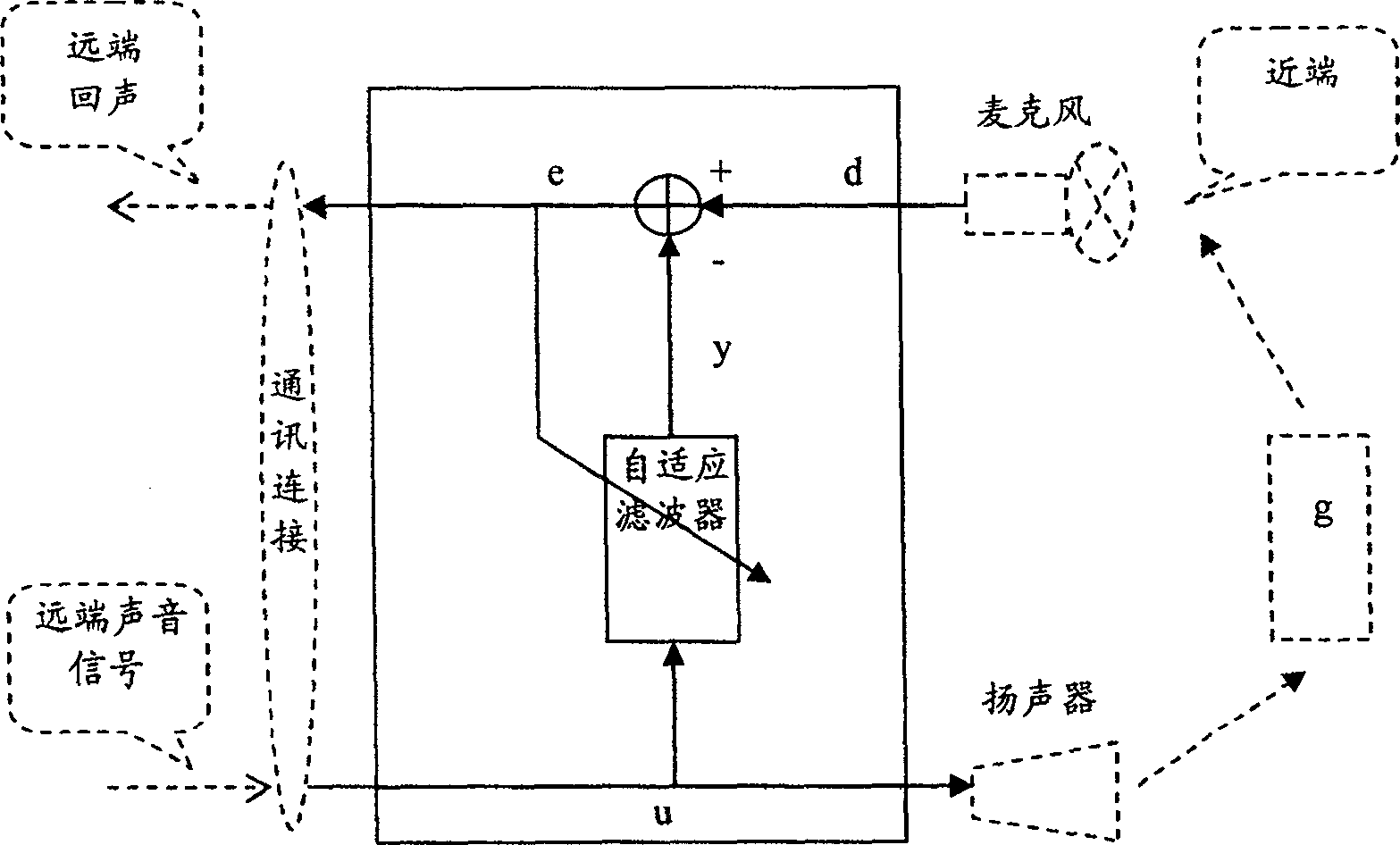

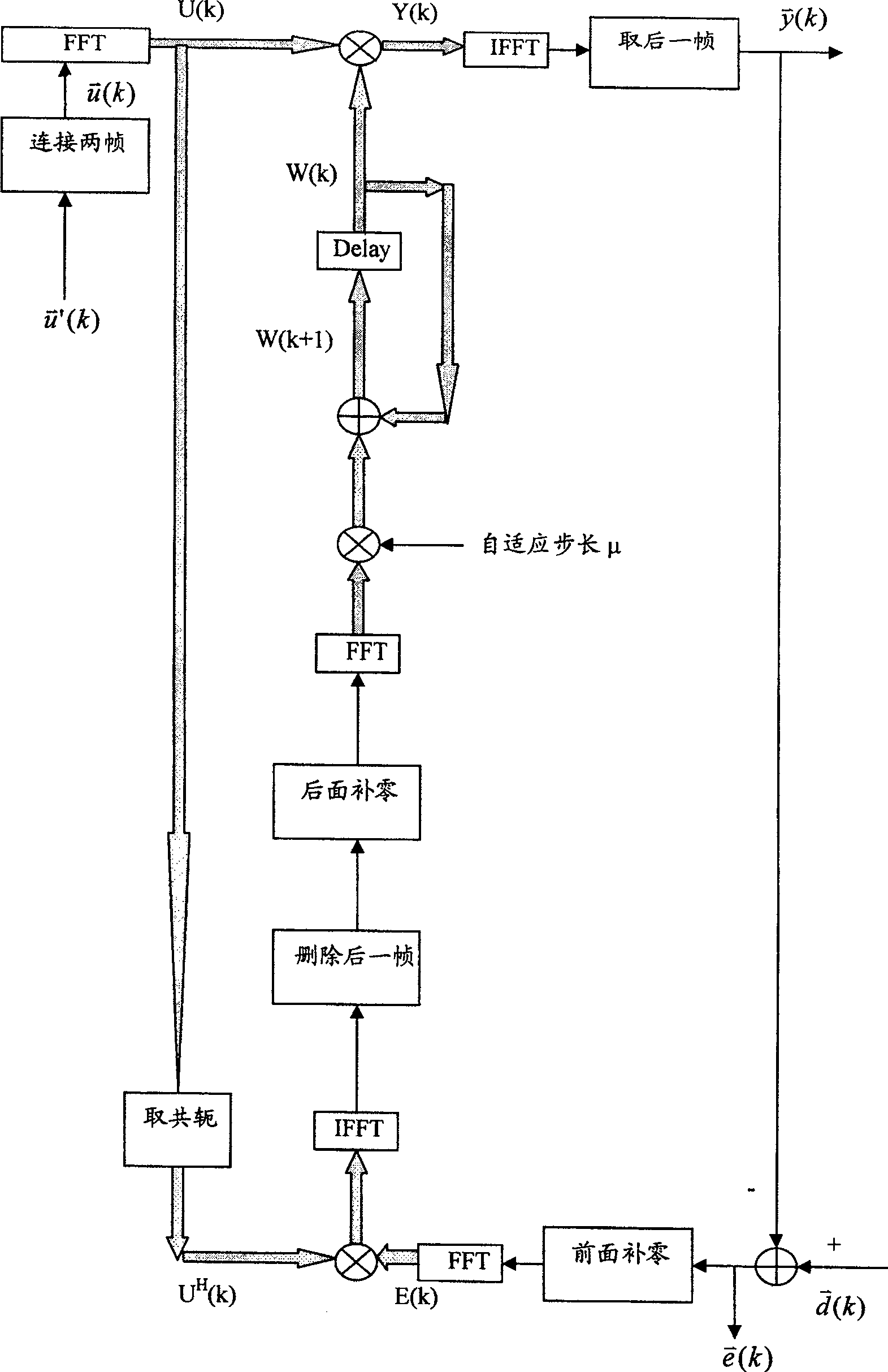

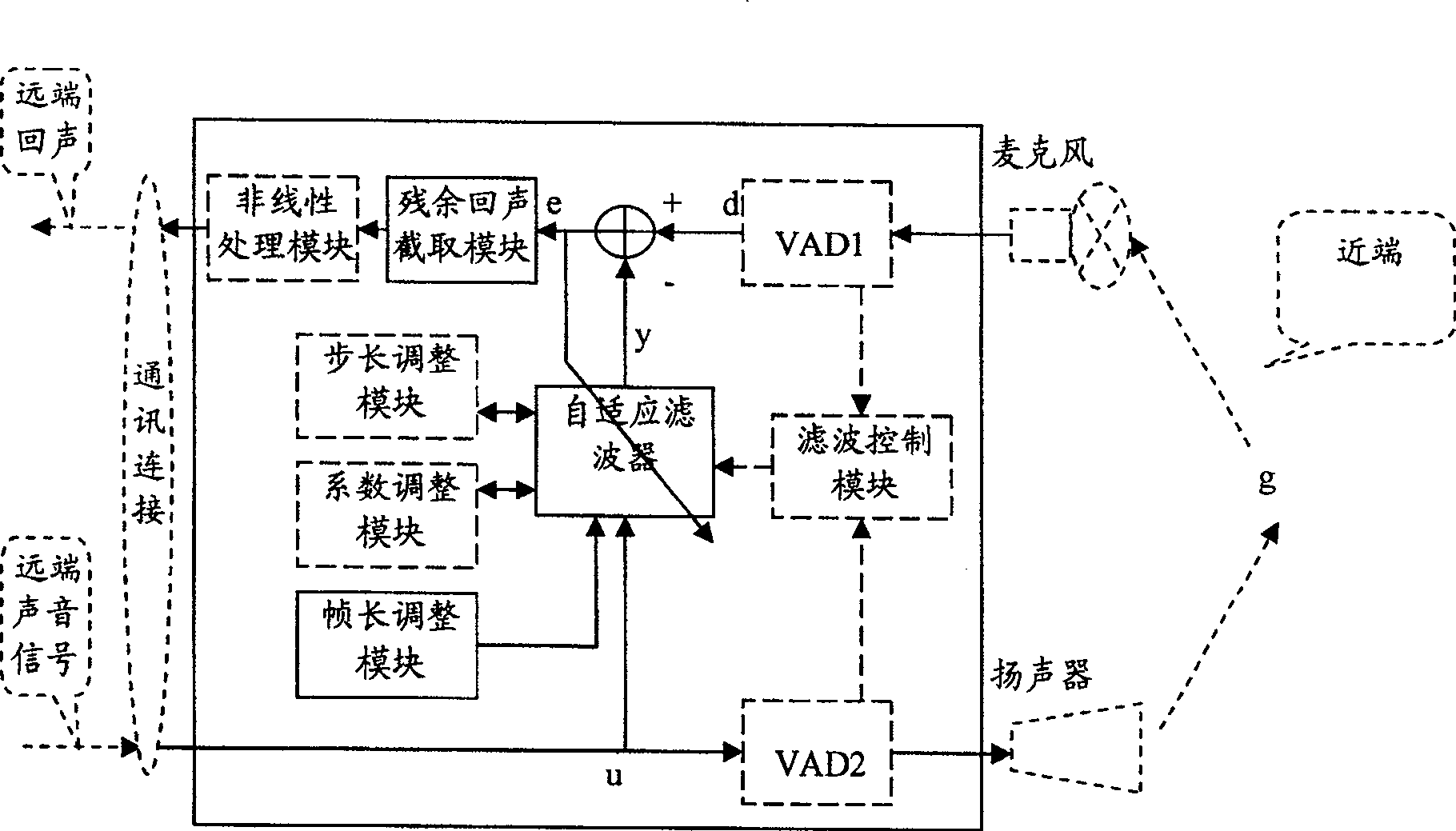

Echo elimination device for microphone and method thereof

InactiveCN1953060AMeet the delay requirementsGuaranteed to workAdaptive networkSpeech analysisComputer moduleSelf adaptive

This invention discloses a microphone echo elimination device and method, which eliminates echo between microphone and sound circuit, wherein, the device comprises long frame adjust module to combine one self adaptive filter parameter data frame for self adapting filter.

Owner:VIMICRO CORP

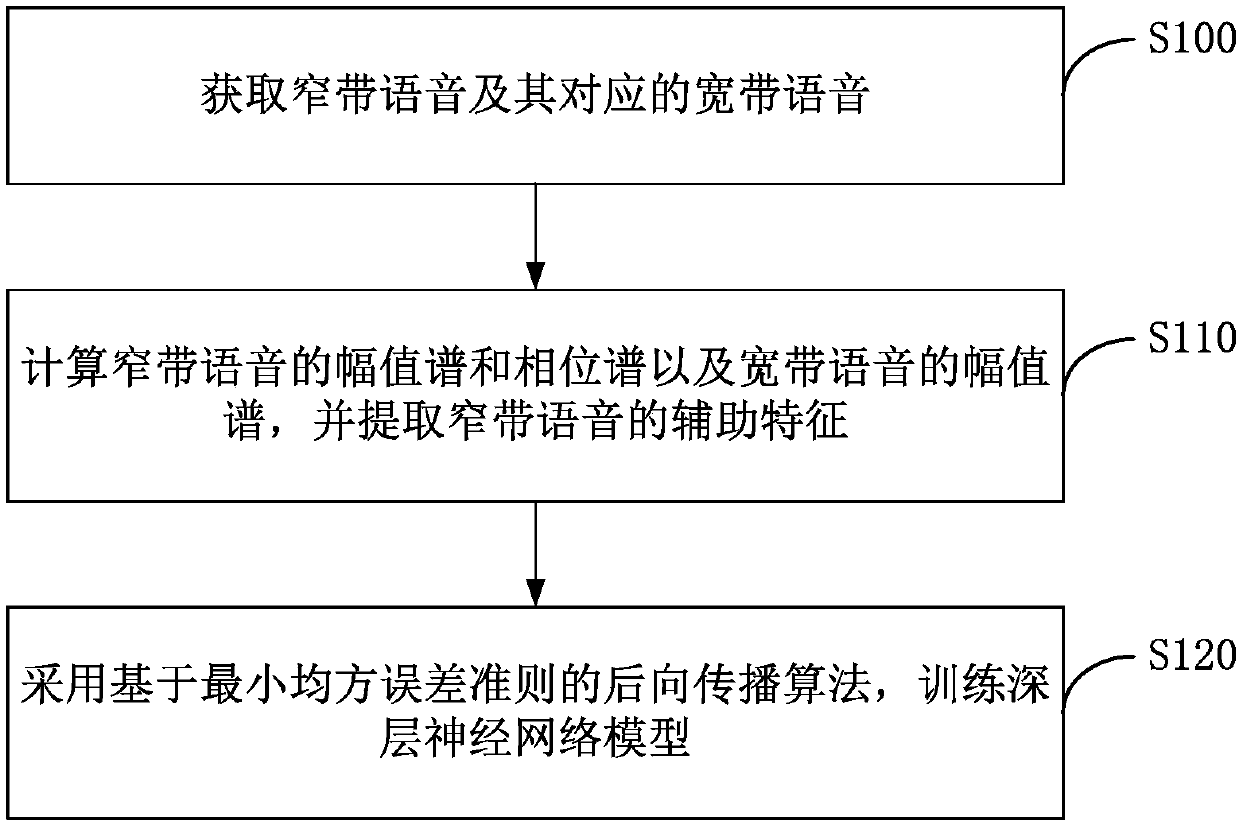

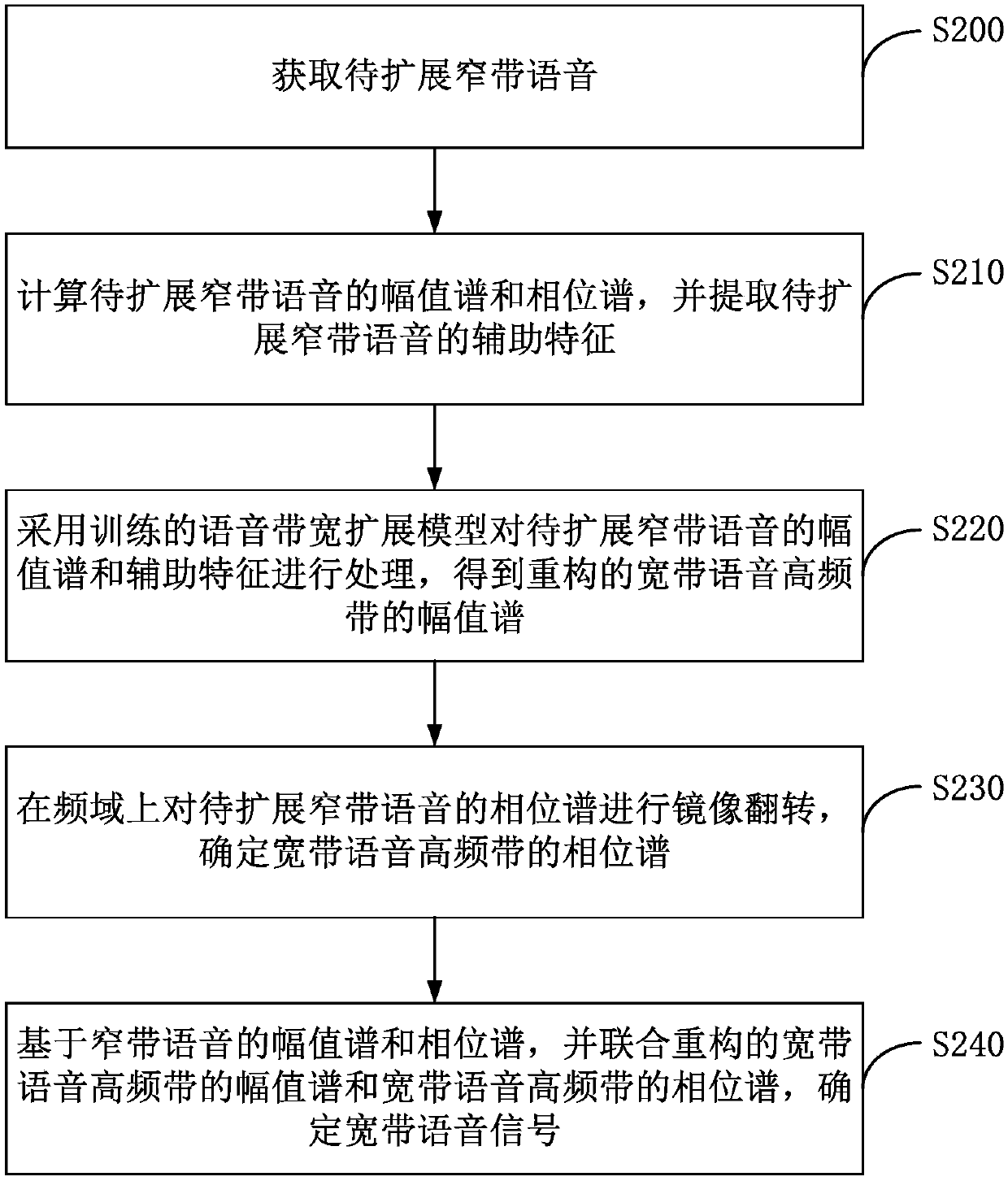

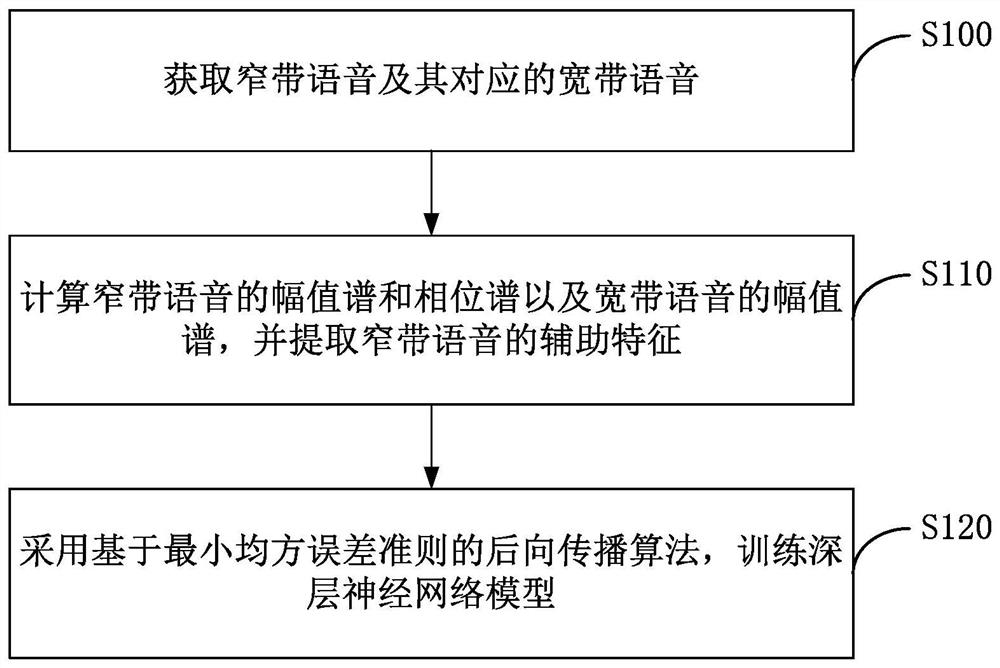

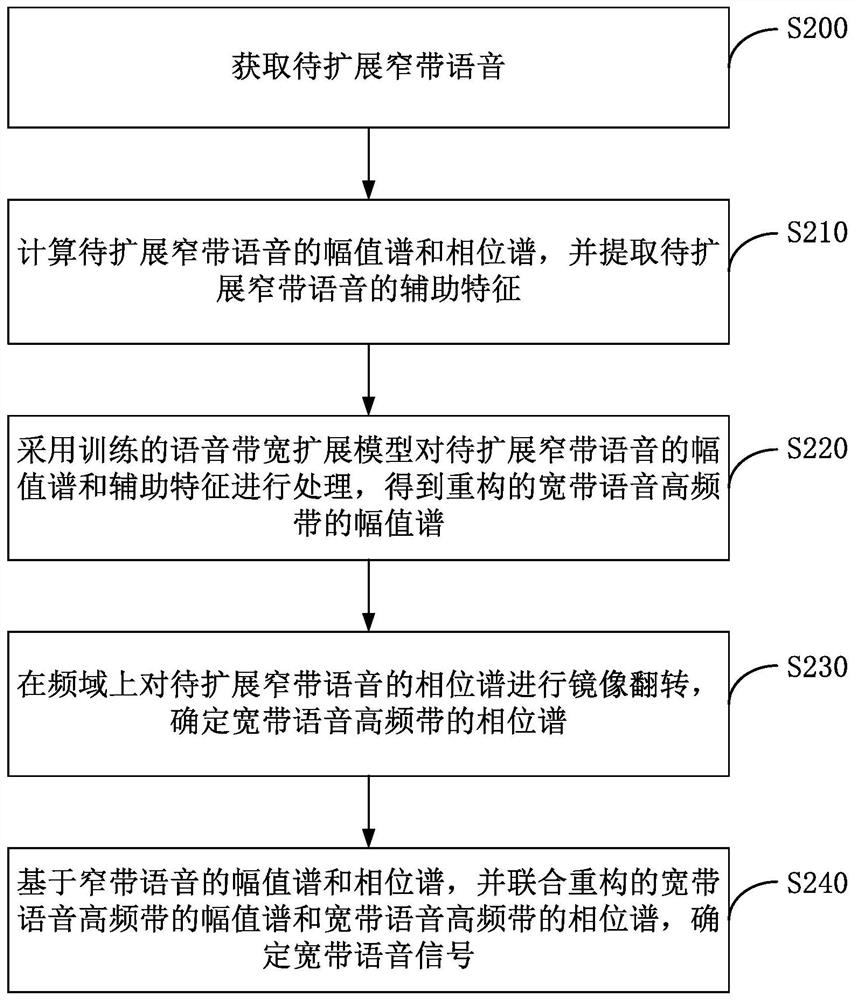

Training method of voice bandwidth expansion model and voice bandwidth expansion method

ActiveCN107705801AImprove sound qualityImprove naturalnessSpeech analysisMirror imageExtension method

The invention discloses a training method of a voice bandwidth expansion model and a voice bandwidth expansion method, wherein the voice bandwidth expansion method comprises the following steps: acquiring to-be-expanded narrowband voice; calculating an amplitude spectrum and a phase spectrum of the to-be-expanded narrowband voice, and extracting auxiliary characteristics of the to-be-expanded narrowband voice ; processing the amplitude spectrum and the auxiliary characteristics of the to-be-expanded narrowband voice by virtue of the voice bandwidth expansion model which is obtained from training, so that the amplitude spectrum of a reconstructed bandwidth voice high-frequency band can be obtained; conducting mirror image reversing on the phase spectrum of the to-be-expanded narrowband voice in a frequency domain, and determining the phase spectrum of the bandwidth voice high-frequency band; and on the basis of the amplitude spectrum and the phase spectrum of the narrowband voice, and in combination with the amplitude spectrum and the phase spectrum of the reconstructed bandwidth voice high-frequency band, determining a bandwidth voice signal. With the application of the voice bandwidth expansion method provided by the invention, an effect of improving the tone quality and naturalness of the narrowband voice can be achieved.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

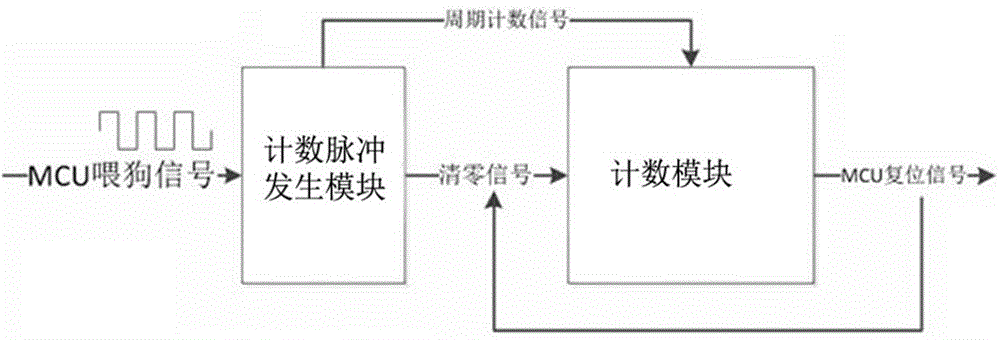

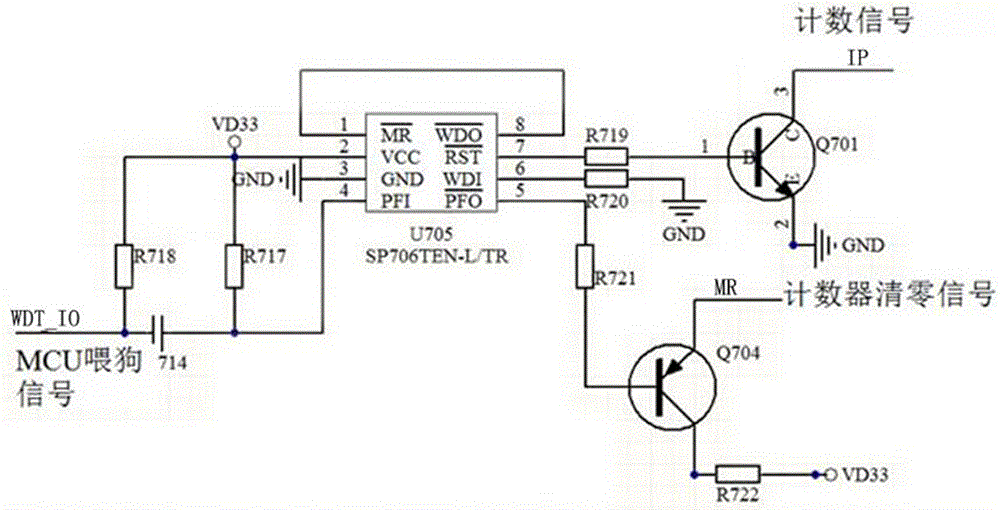

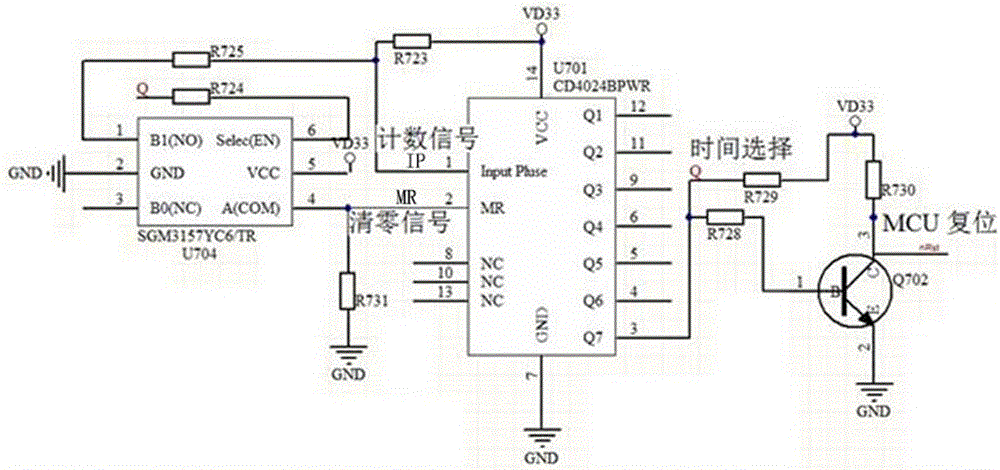

Watchdog circuit capable of configuring dog-feeding cycle

PendingCN106528319AMeet the delay requirementHighly integratedFault responseEnergy efficient computingBand countsInfinite loop

The invention discloses a watchdog circuit capable of configuring a dog-feeding cycle. The watchdog circuit comprises a counting pulse generating module and a counting module connected with the counting pulse generating module; the input end of the counting pulse generating module is connected with a MCU dog-feeding signal output end and used for receiving a dog-feeding signal sent by the MCU; the output end of the counting module is connected with a MCU reset signal input end and used for sending a reset signal to the MCU; different output ends of the counting module are connected to the MCU reset signal input end according to the difference of the dog-feeding cycles needing to be configured. The watchdog circuit can automatically set the watchdog feeding cycle, and can avoid the condition that a mater chip is continuously reset to enter the infinite loop in the starting process due to short dog-feeding cycle; and meanwhile, the delay requirement of the product on the market is satisfied.

Owner:山东有人物联网股份有限公司

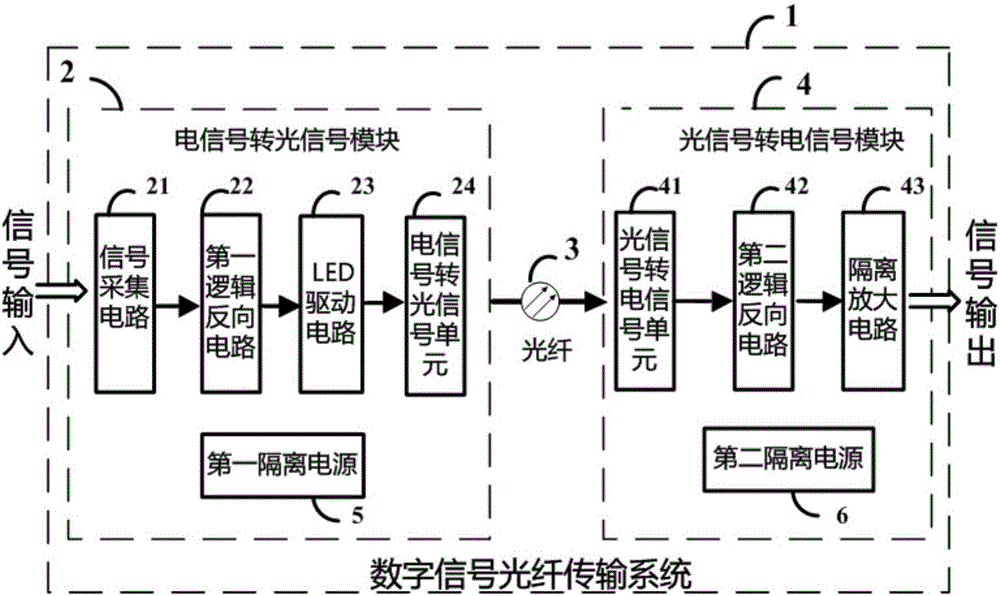

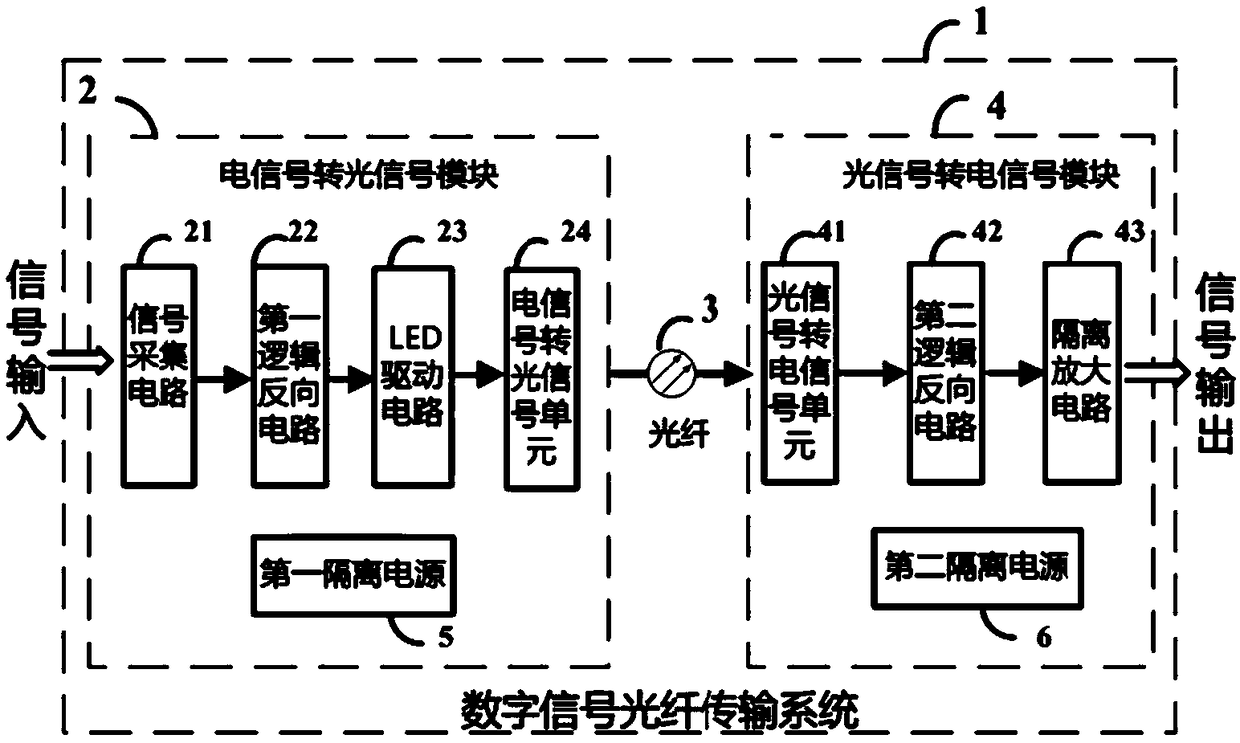

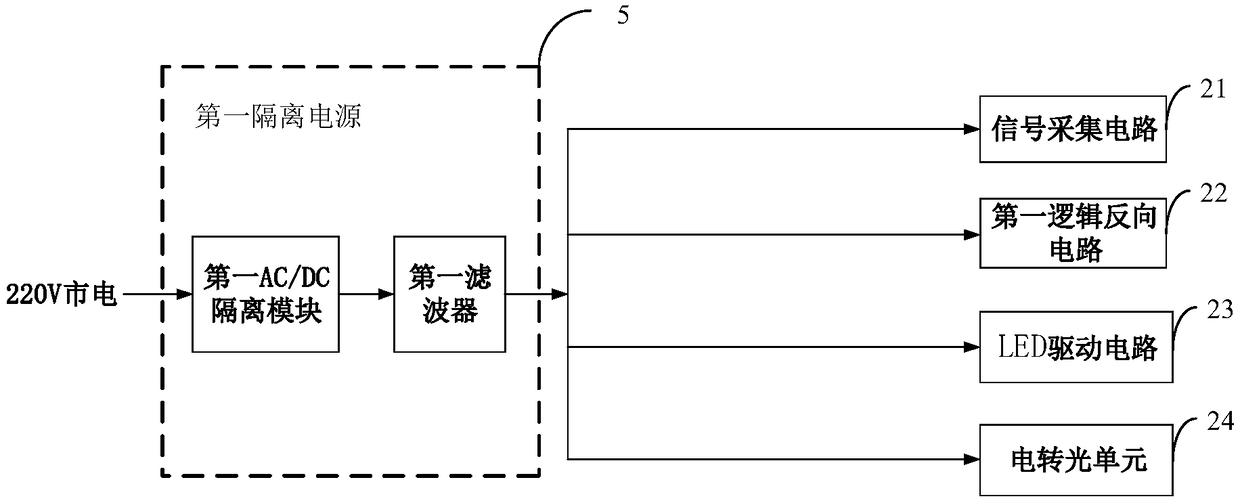

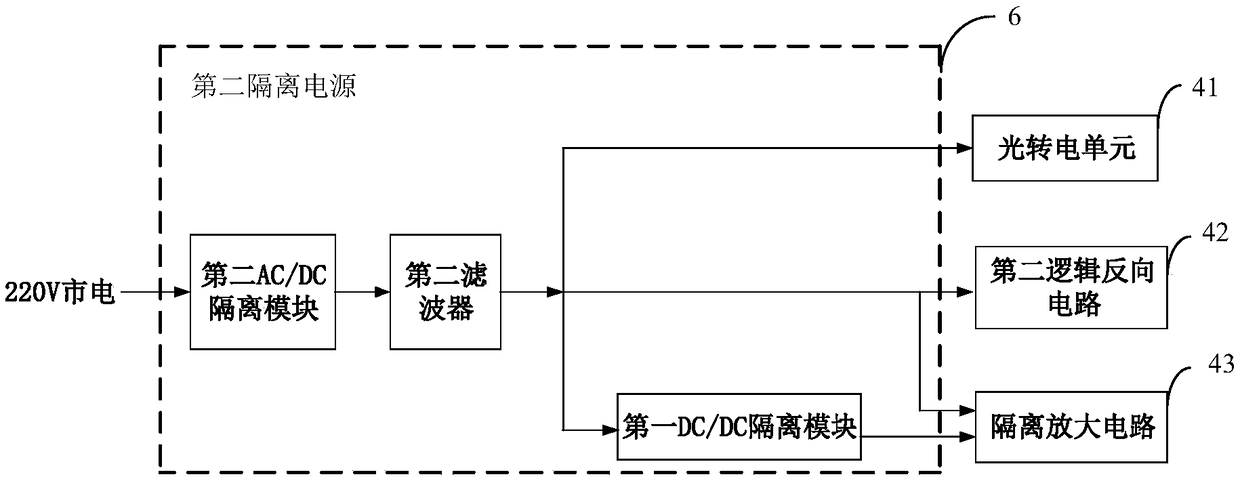

Digital signal fiber transmission triggering system

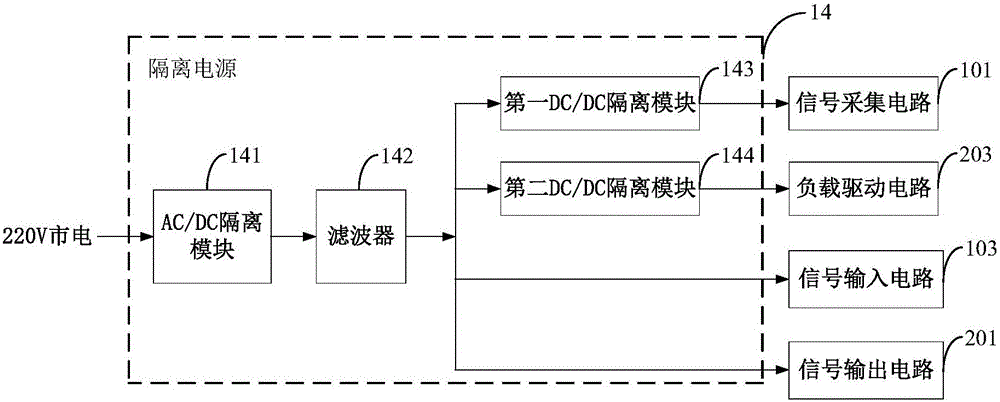

ActiveCN105790746AAcquisition stableAvoid false triggersElectronic switchingFibre transmissionCapacitanceElectricity

The present invention discloses a digital signal fiber transmission triggering system. The system comprises an electric signal-optical signal conversion module and an optical signal-electric signal conversion module which are connected through a fiber connection line; the electric signal-optical signal conversion module has an input end which is taken as the signal input interface of a digital signal fiber transmission triggering system and is configured to receive external digital triggering signals; and the optical signal-electric signal conversion module is configured to convert the digital signals through external input to optical signals, and the optical signal-electric signal conversion module is configured to convert the optical signals to high low-level digital triggering signals and realize opto-couplers isolation and power amplification of the digital triggering signals. The digital signal fiber transmission triggering system is able to overcome the defect of the inductor (or transformer) type isolation anti-interference capability and solve the problem of the common transmission channel of capacitive coupling noise and signals, is low in cost, extensive in applicability, high in reliability and high in carrying load ability and has long-distance fiber transmission signals, etc.

Owner:HUAZHONG UNIV OF SCI & TECH

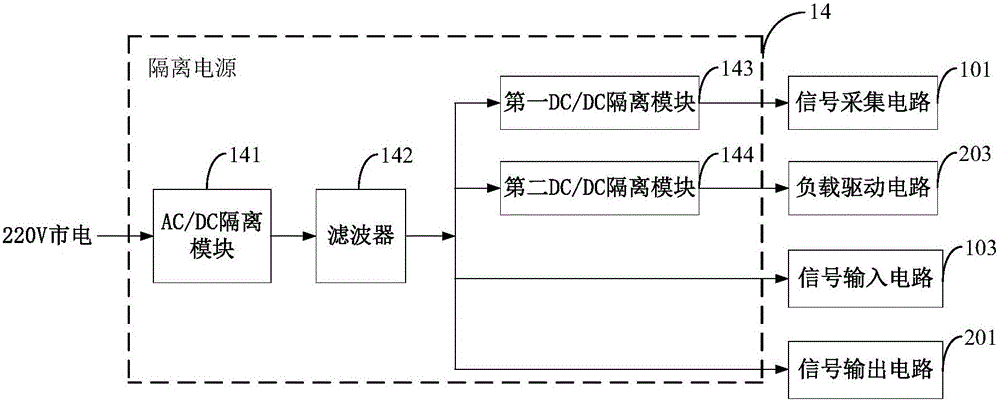

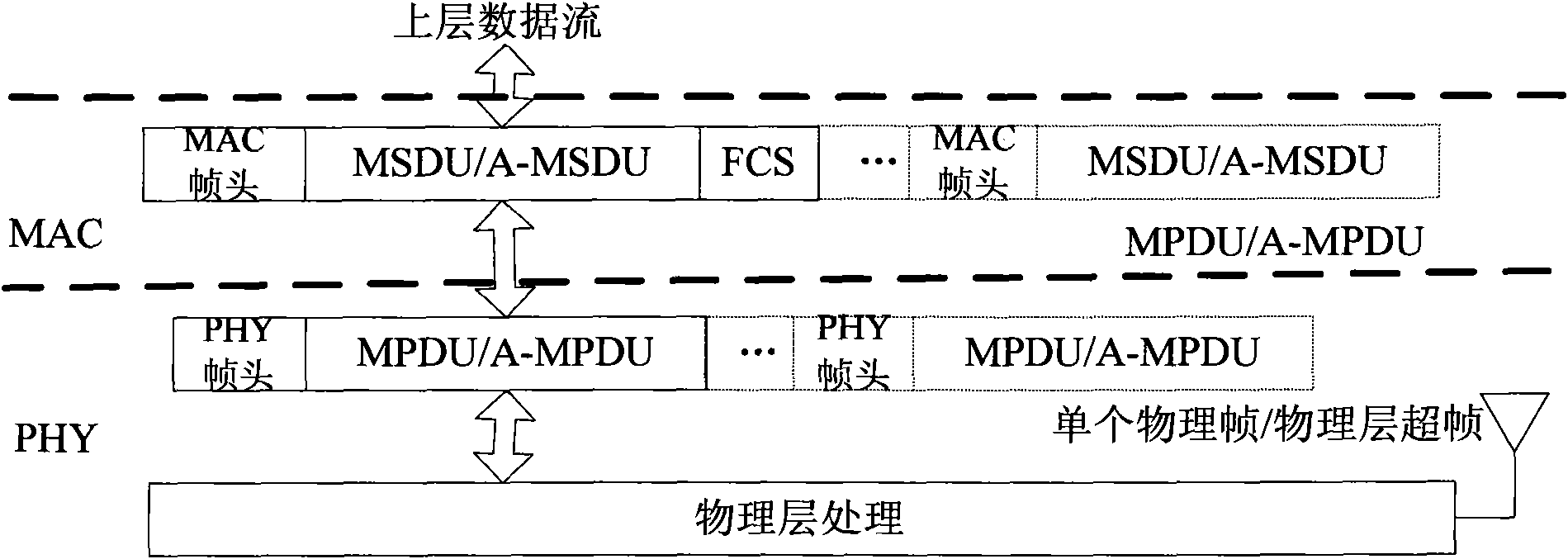

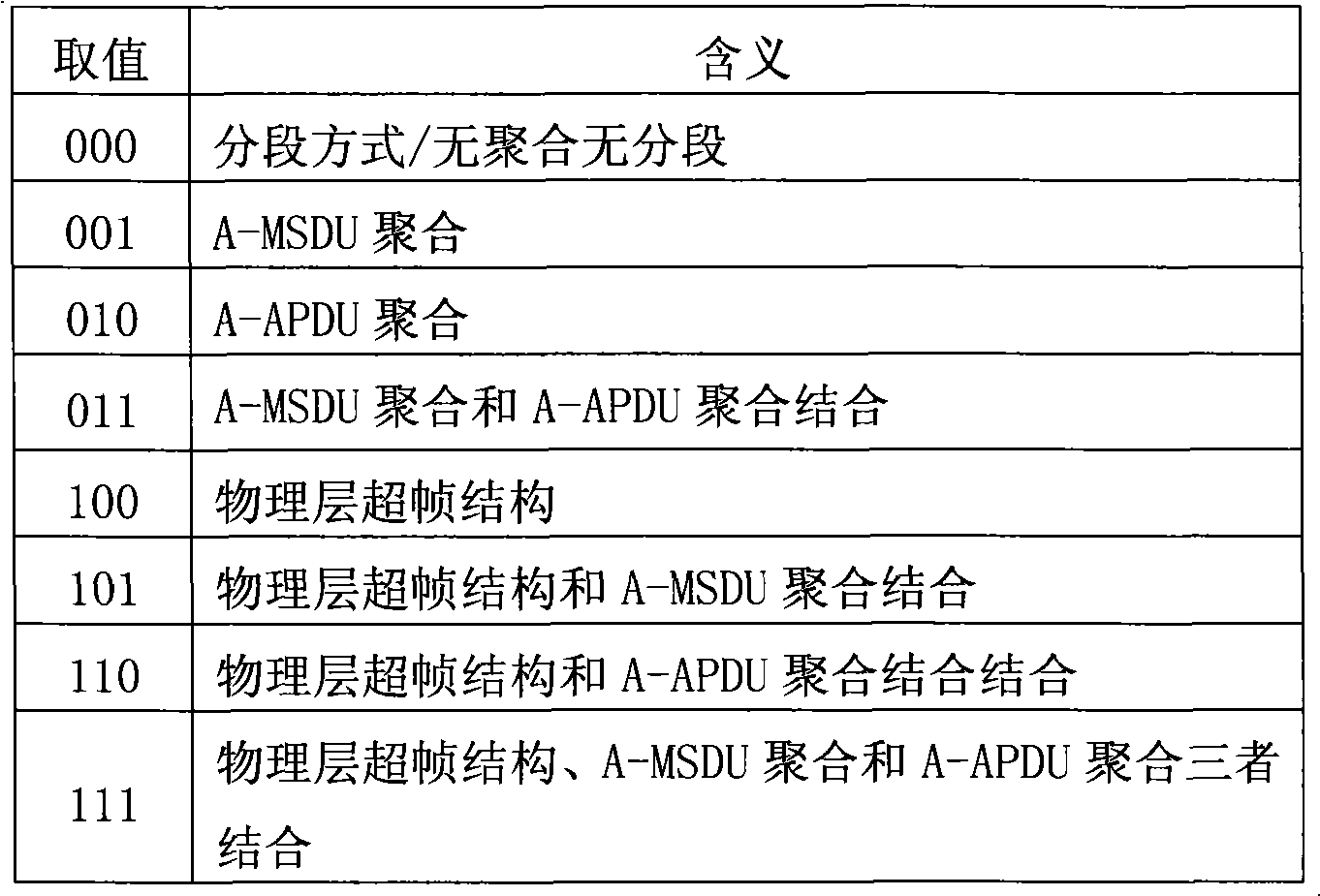

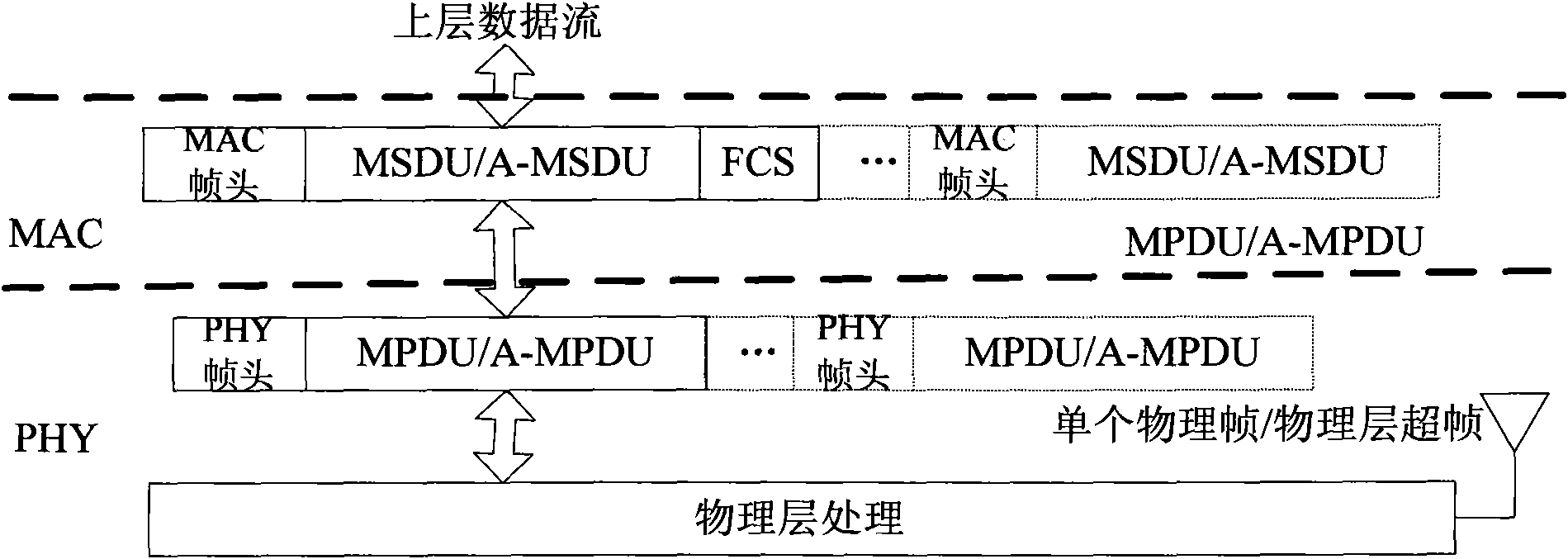

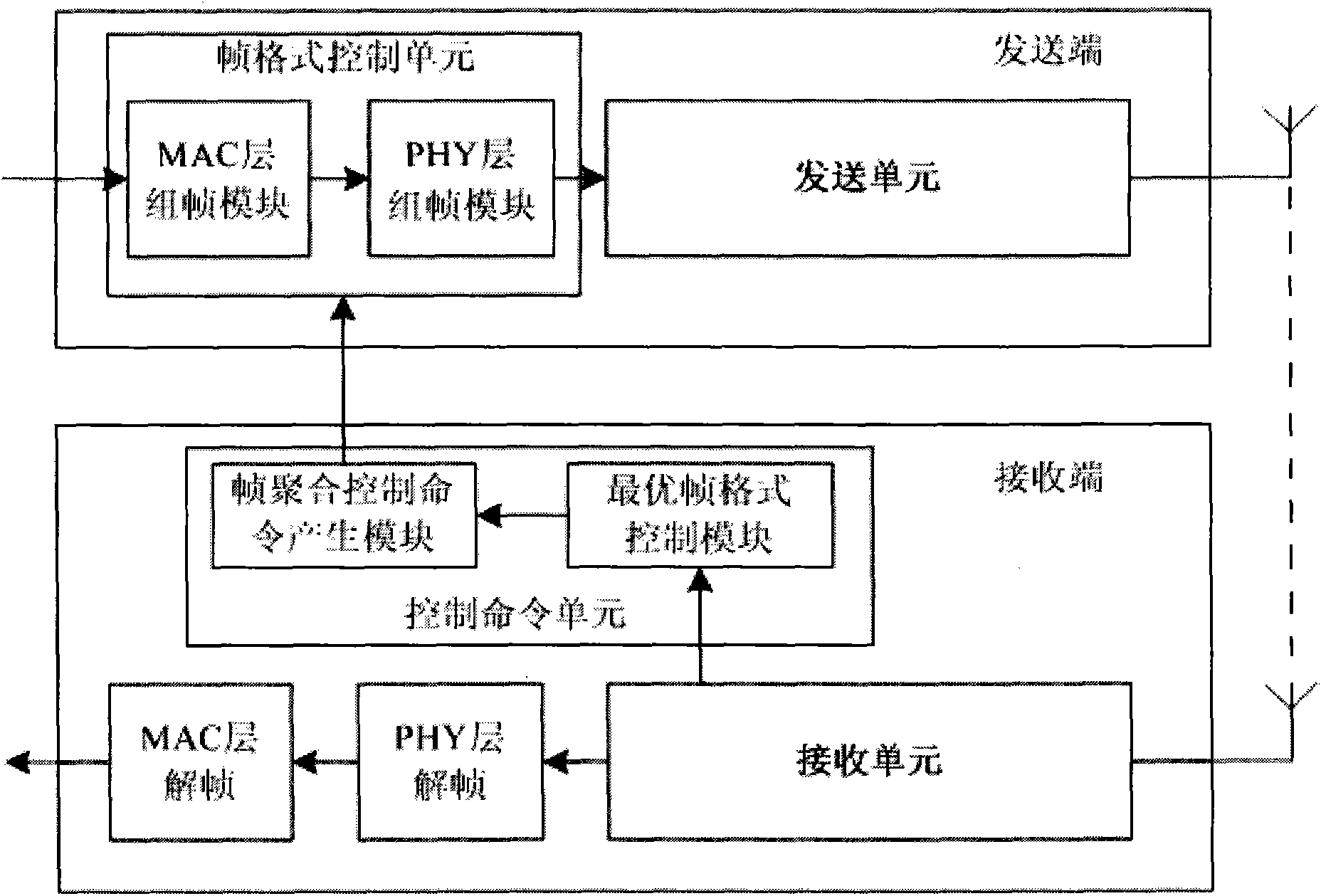

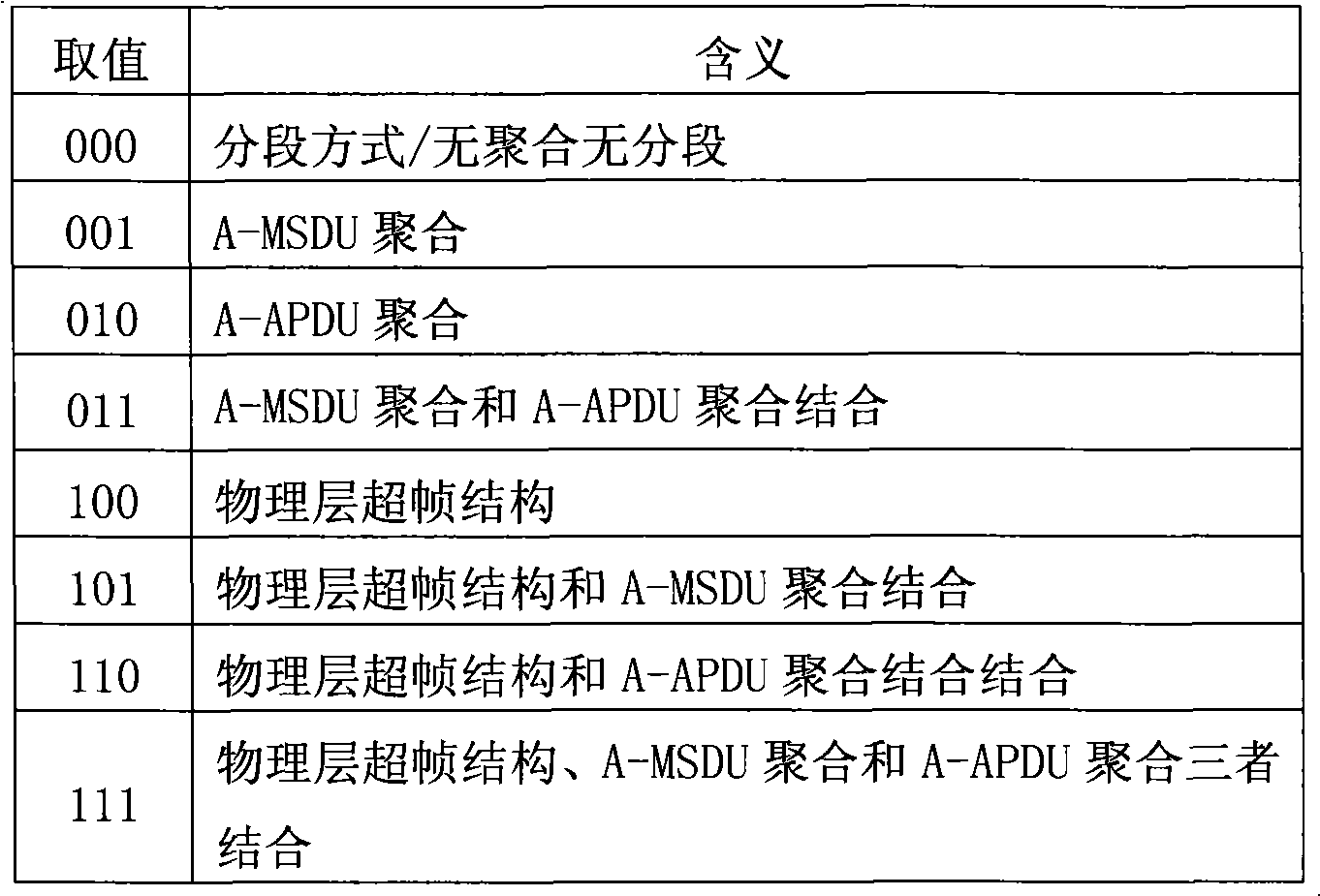

Superspeed wireless local area network frame polymerization device and control method thereof

InactiveCN101969665AImprove throughput performanceMeet the delay requirementNetwork traffic/resource managementNetwork topologiesTime errorTime delays

The invention discloses a superspeed wireless local area network frame polymerization device and a control method thereof. The device comprises a transmitting end and a receiving end, wherein the transmitting end comprises a frame format control unit and a transmitting unit; the receiving end comprises a receiving unit and a control command unit, and the control command unit controls a frame polymerization / segmentation mode and an access mode under different services and comprises an optimal frame format control module and a frame polymerization control command generation module; the optimal frame format control module receives real-time error rate information from the receiving unit, and compares the real-time error rate information with an error rate interval comparison table to select an optimal frame polymerization / segmentation mode and access mode; and according to the optimal frame polymerization / segmentation mode and access mode, the frame polymerization control command generation module generates a frame polymerization / segmentation control command for carrying out frame polymerization / segmentation control on the frame format control unit of the transmitting end. The method and the device provided by the invention can select proper polymerization modes and polymerization frame numbers in real time according to the service type and the error rate situation, and the wireless local area network is enabled to improve the throughput performance while satisfying time delay.

Owner:SOUTHEAST UNIV

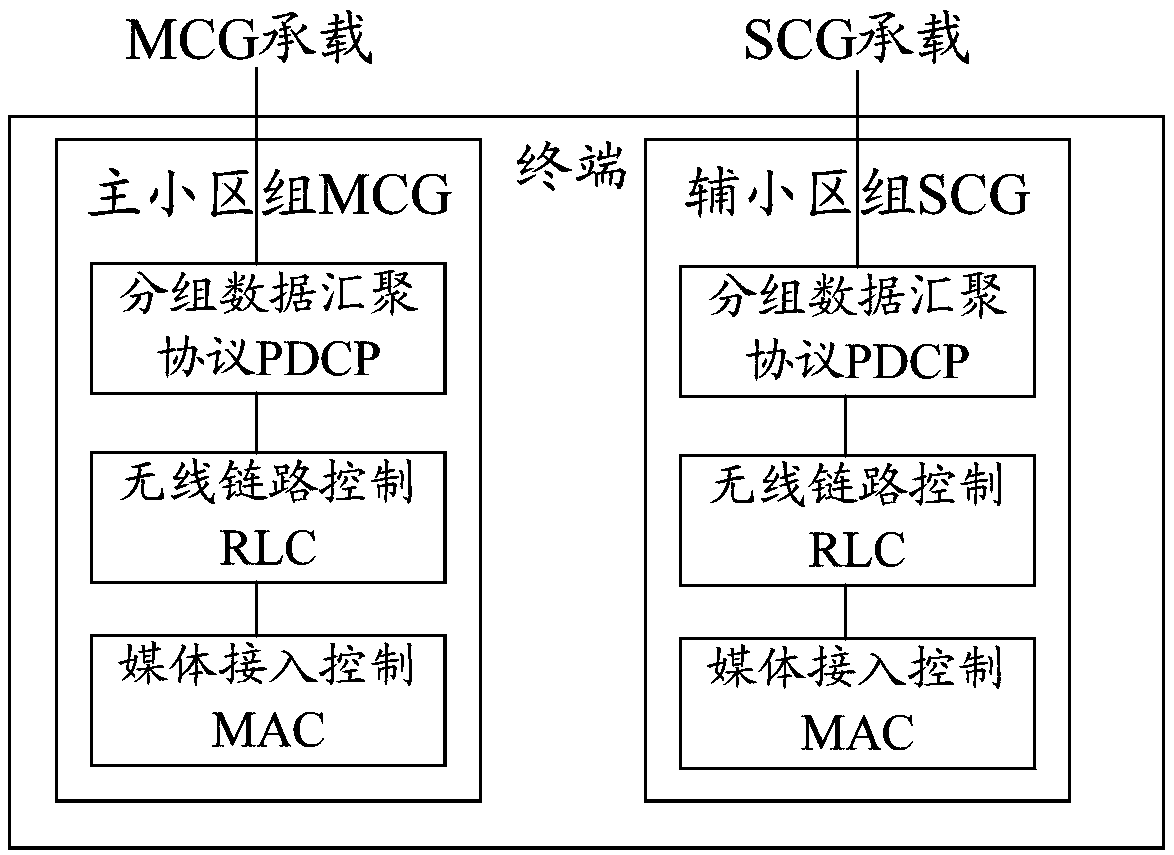

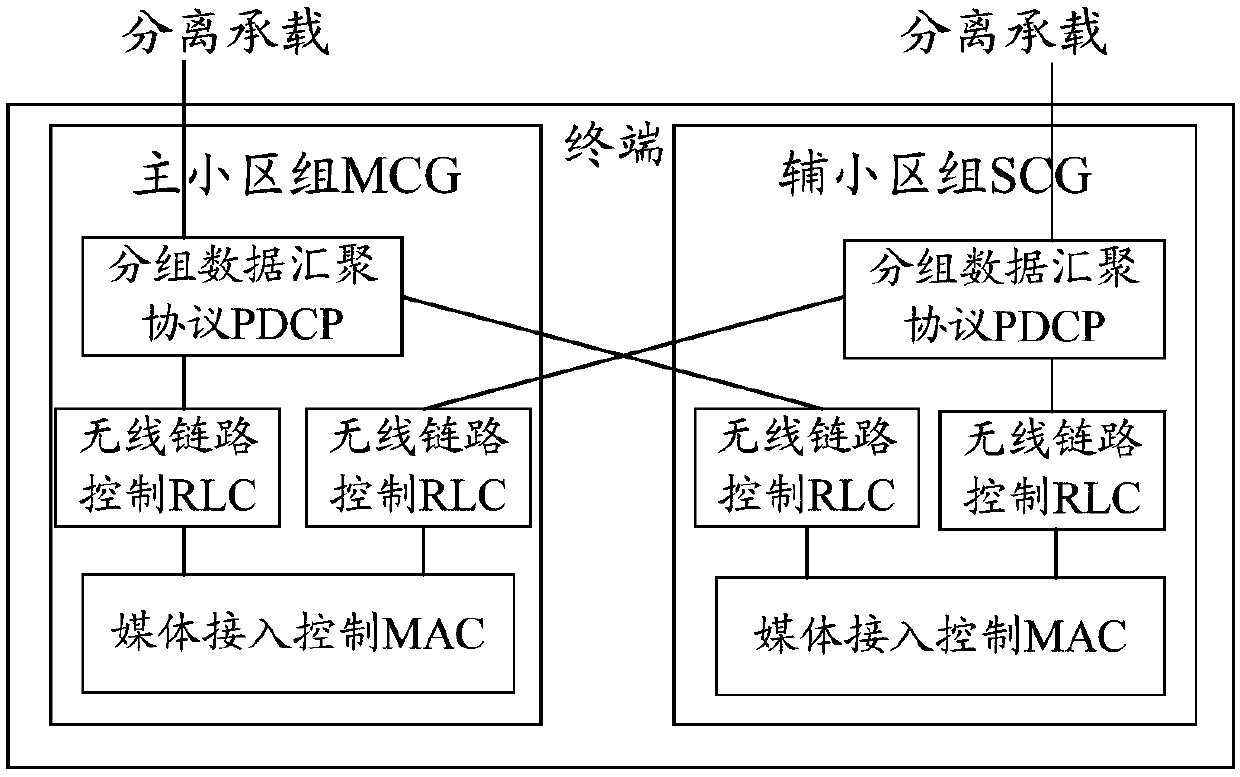

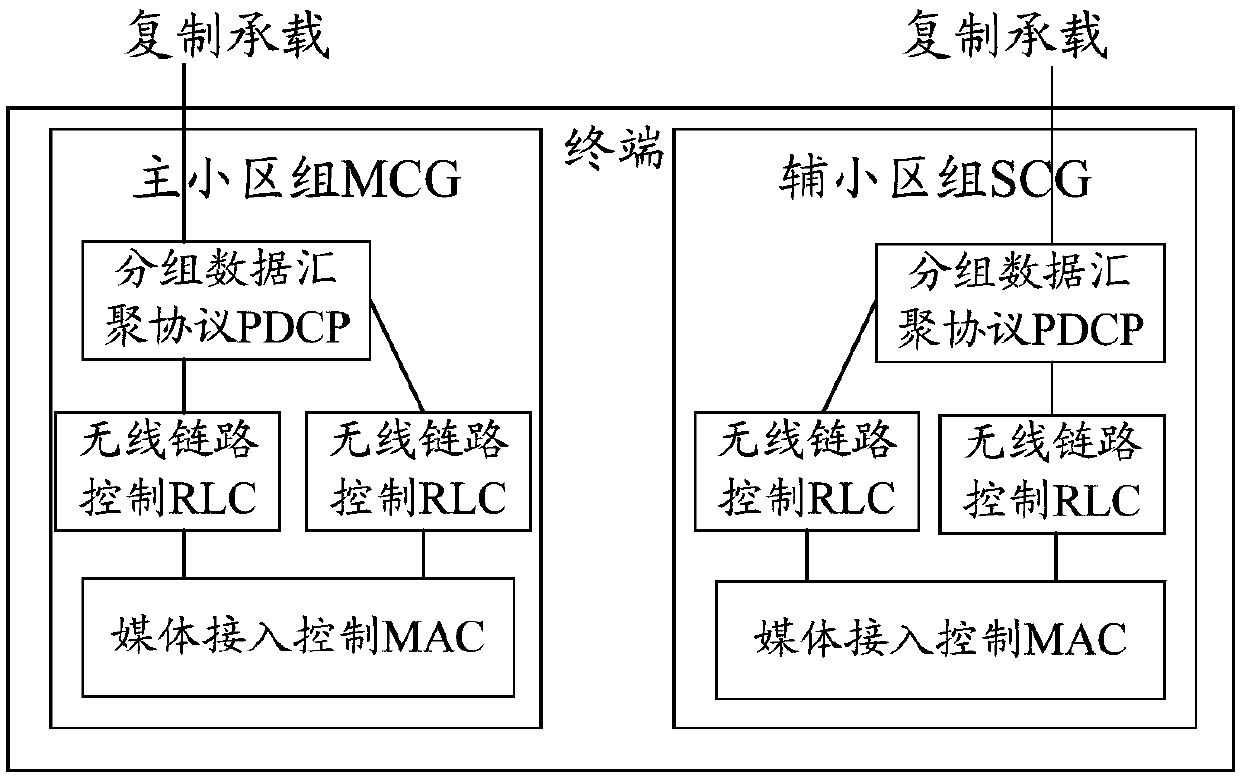

Dual-connection switching method, terminal and network equipment

The invention discloses a dual-connection switching method, a terminal and network equipment, and the method comprises the steps: receiving a switching command transmitted by a source node, wherein the switching command carries the dual-connection DC configuration information of the source node and a target node and the single-connection SC configuration information of the target node; when the DCconfiguration information is supported, establishing dual connection between the source node and the target node according to the DC configuration information; and disconnecting the connection with the source node in the dual connection according to the SC configuration information, and maintaining the single connection with the target node. According to the embodiment of the invention, the connection configuration in the DC HO process can be supported, and the normal operation of the DC HO process is ensured, so that the 0ms terminal delay requirement in the terminal moving process is met.

Owner:VIVO MOBILE COMM CO LTD

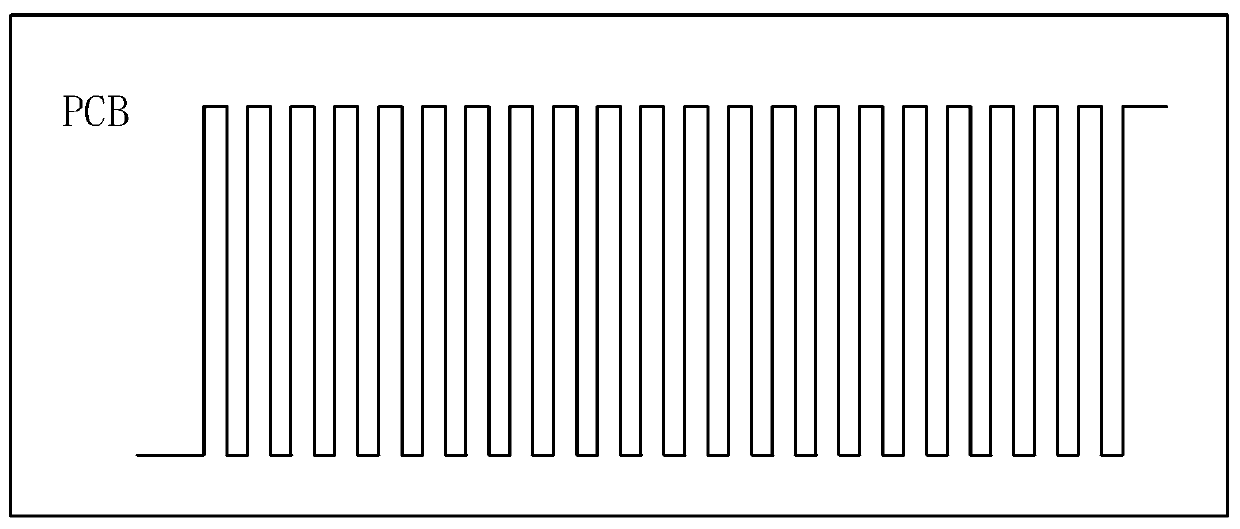

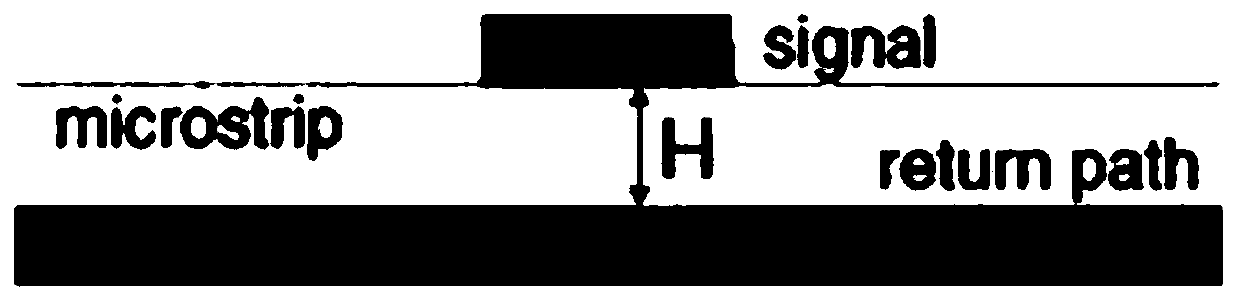

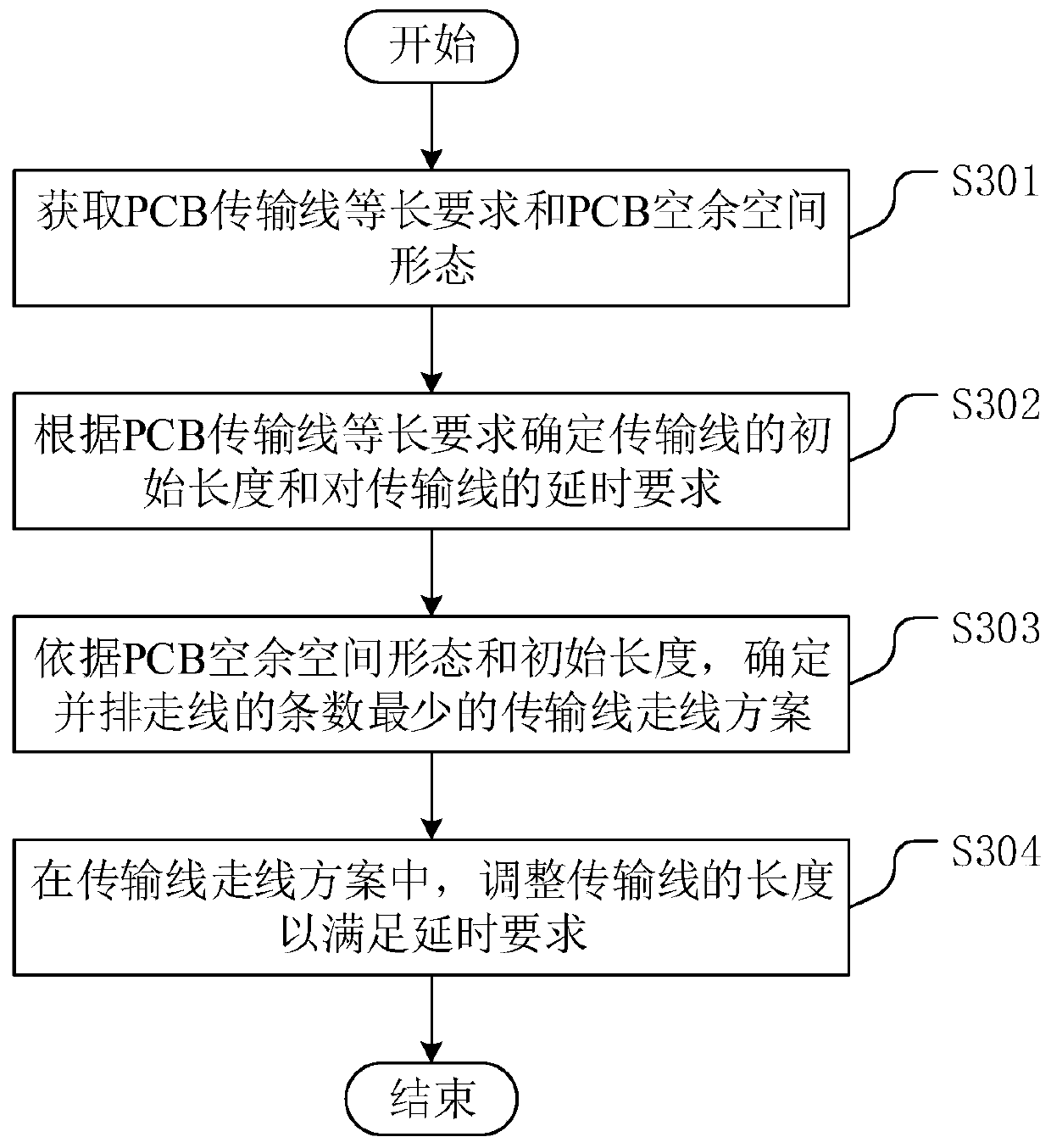

Wiring method, device and equipment for equilong arrangement of PCB transmission lines

The invention discloses a wiring method for equilong arrangement of PCB transmission lines. The initial length of the transmission line and the delay requirement for the transmission line are determined according to the equal-length requirement of the PCB transmission line, the transmission line routing scheme with the minimum number of side-by-side routing lines is determined according to the PCBspare space form and the initial length, and finally the length of the transmission line is adjusted to meet the delay requirement. Starting from a PCB unoccupied space form, the number of side-by-side wires is reduced; mutual coupling between side-by-side wiring is reduced; according to the transmission wiring scheme, under the same time delay requirement, the length of the required transmissionline can be reduced, the area occupied by the overall wiring space of the transmission line is reduced, and therefore the probability that the PCB transmission line meets the time delay requirement on the limited wiring space is increased, and the equal-length requirement is met. The invention also discloses a wiring device and equipment for equilong arrangement of the PCB transmission line, anda computer readable storage medium, which have the above beneficial effects.

Owner:GUANGDONG INSPUR BIG DATA RES CO LTD

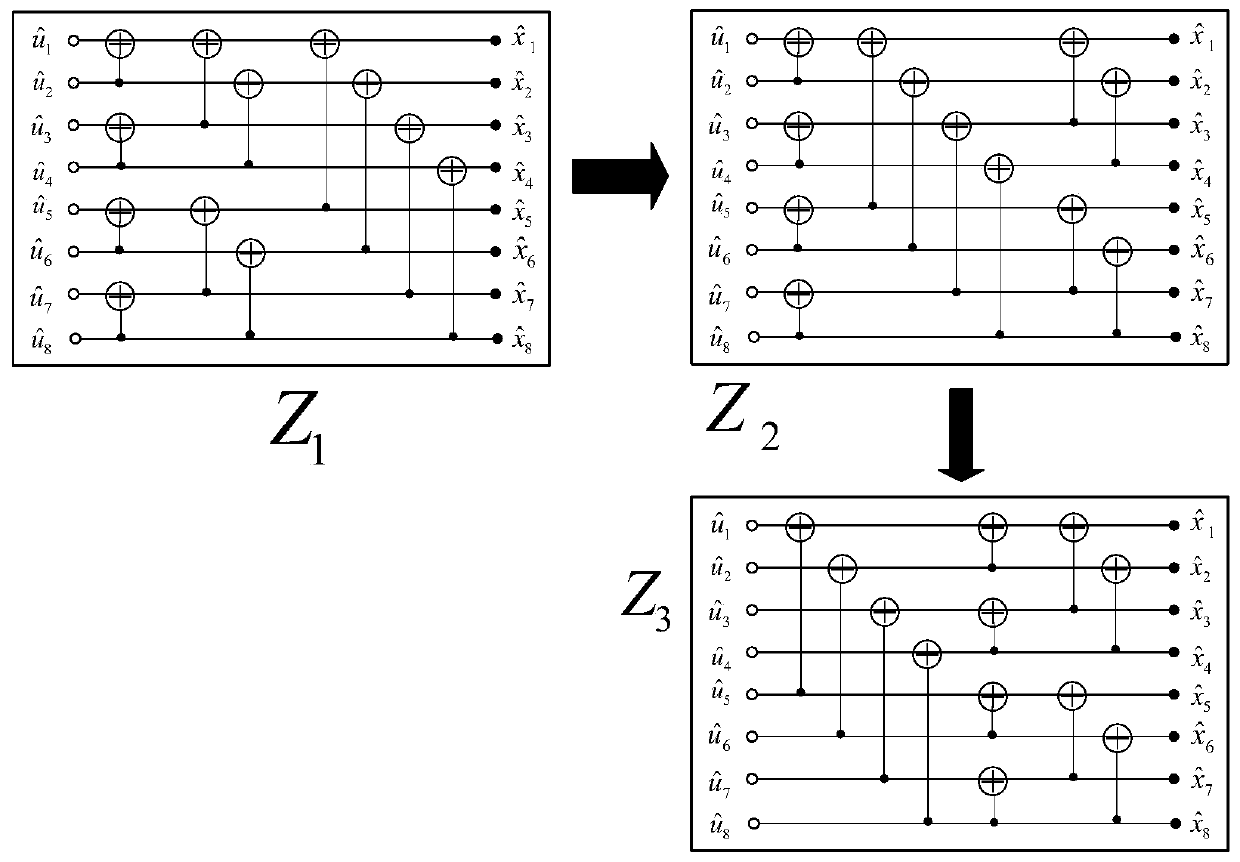

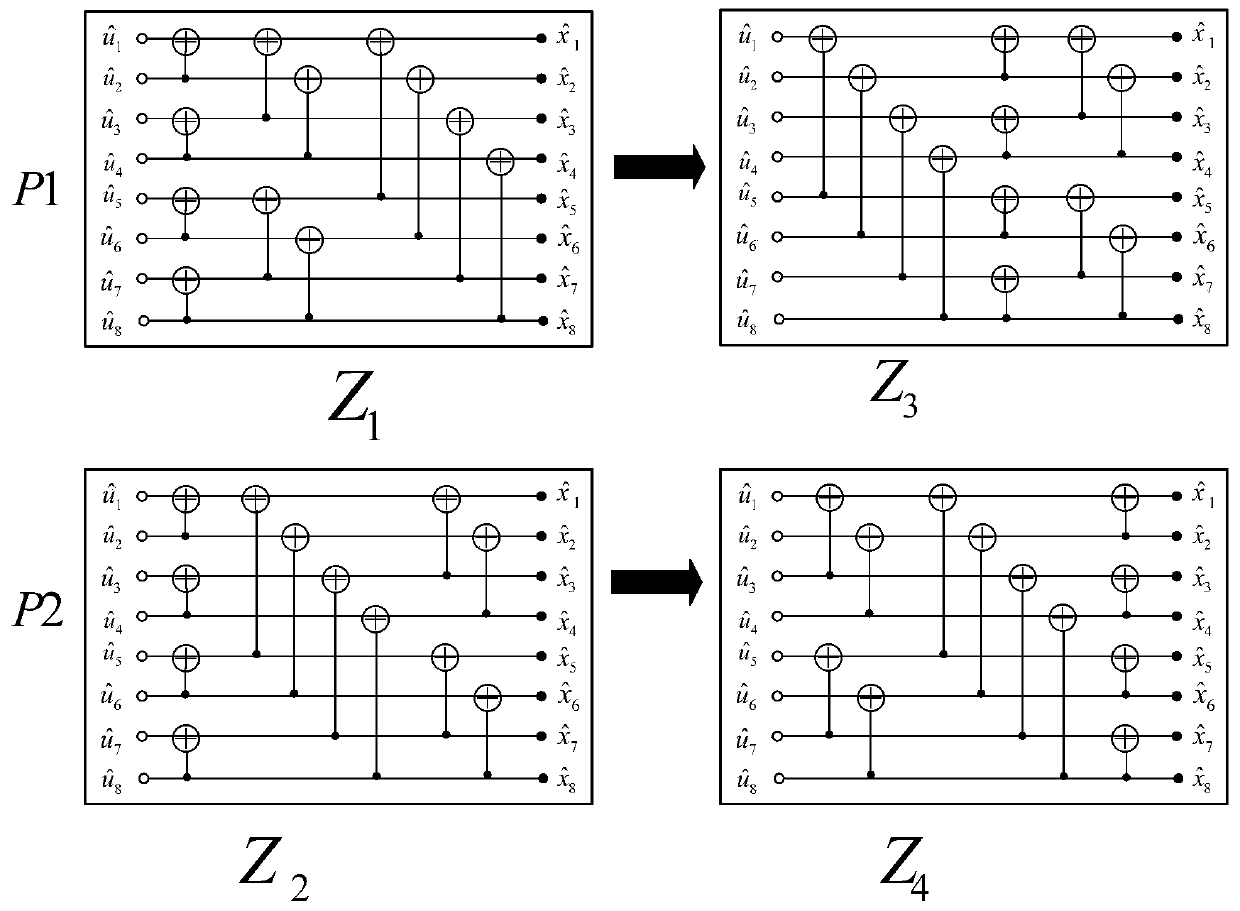

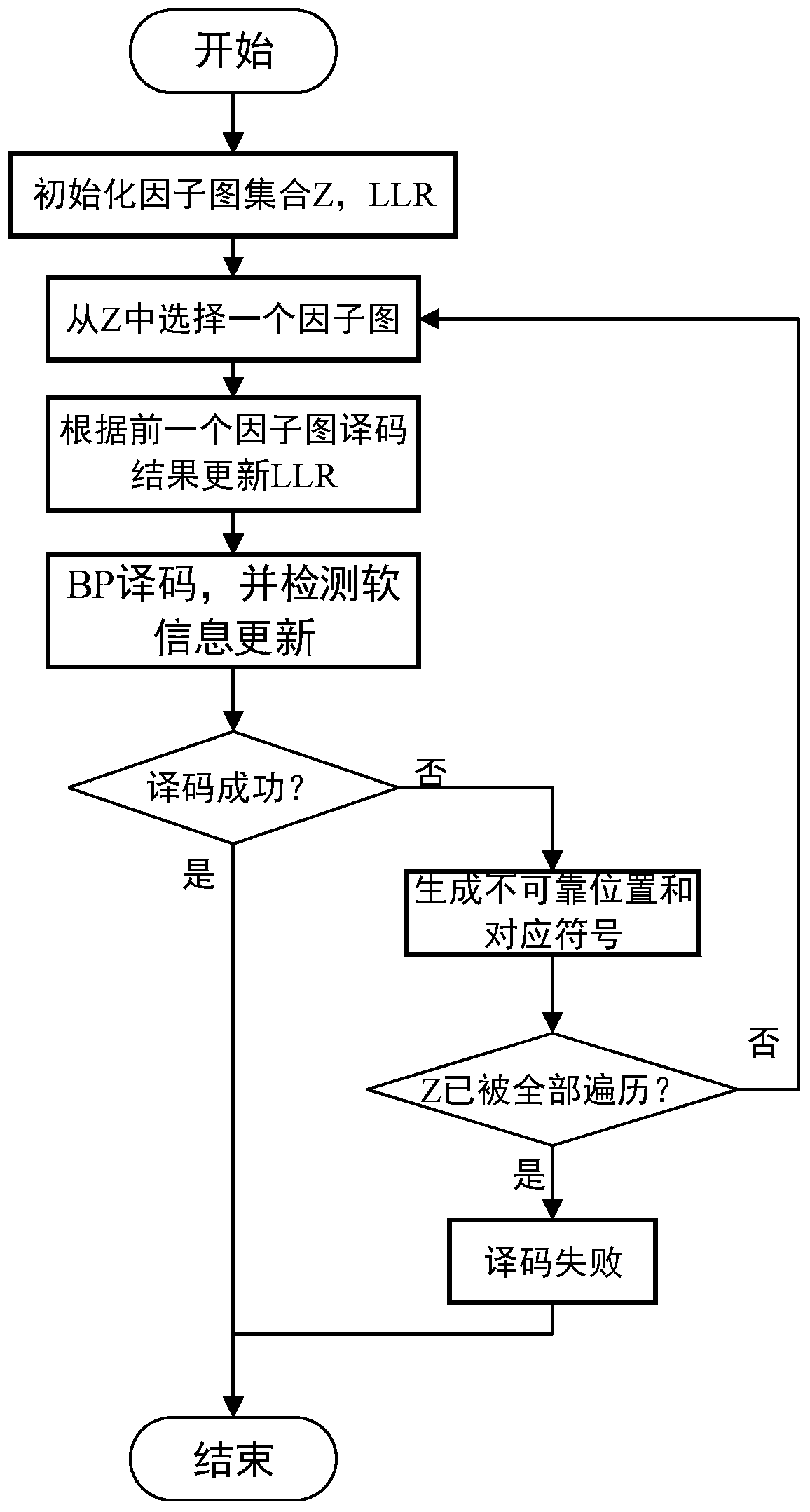

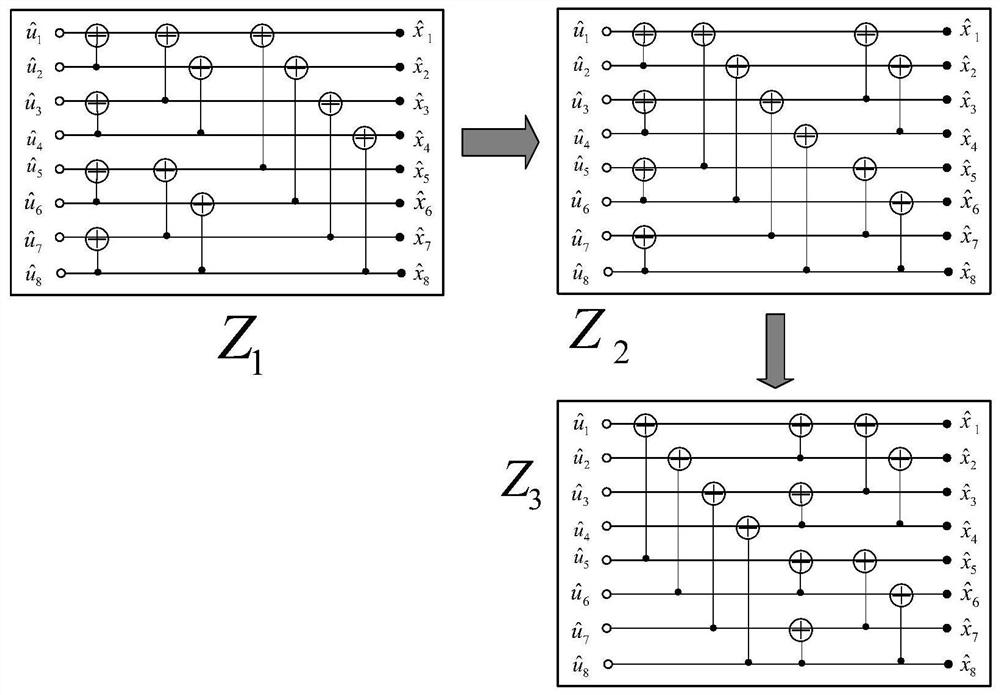

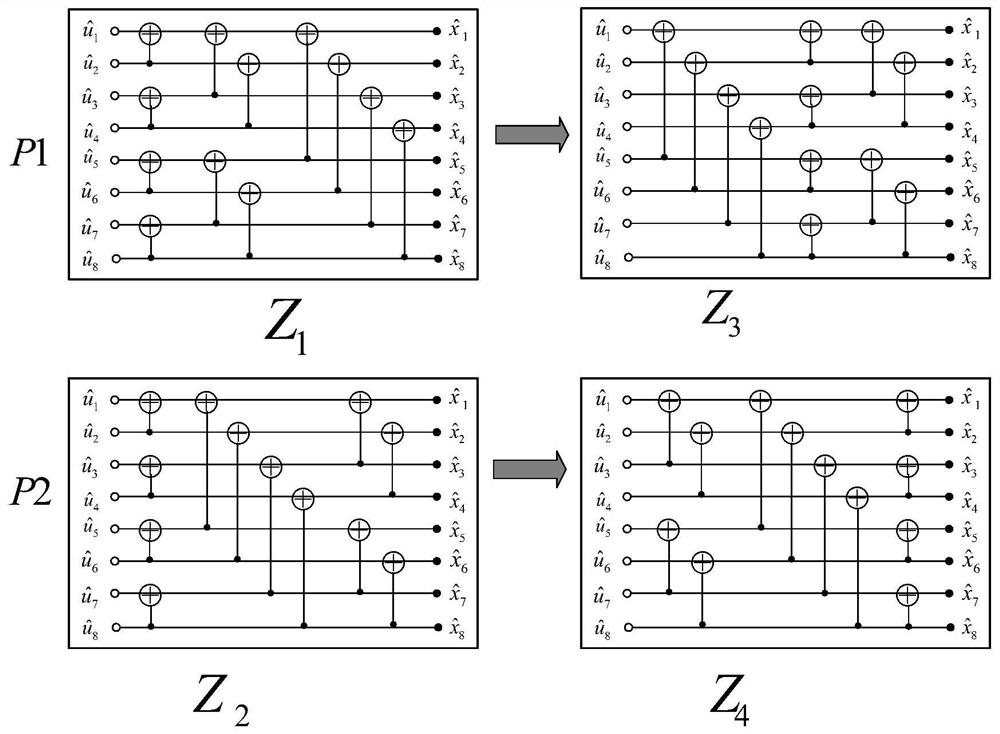

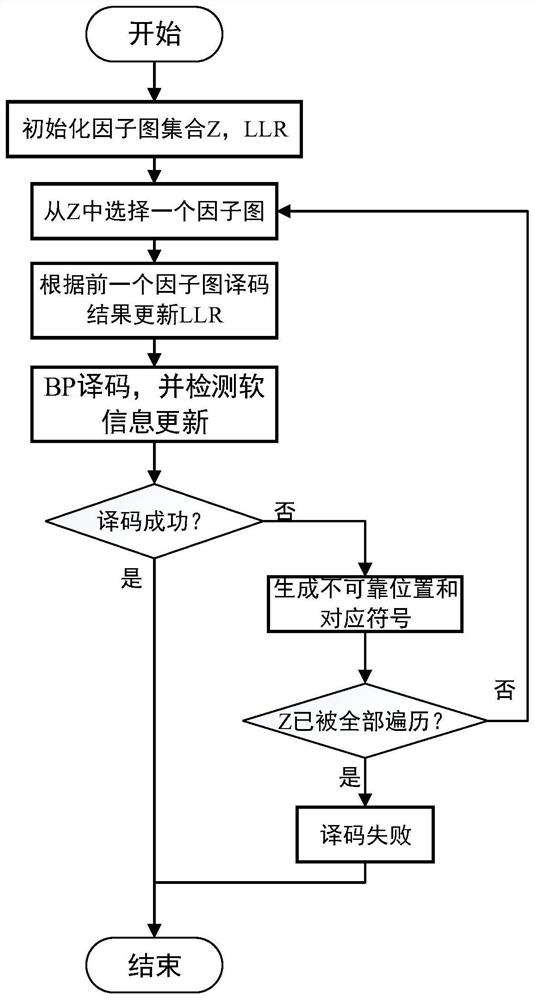

Improved polar code BP List decoding method

ActiveCN111010196ALower latencyMeet the needs of engineering applicationsError correction/detection using multiple parity bitsCode conversionTime delaysTheoretical computer science

The invention discloses an improved polar code BP List decoding method which comprises the following steps: 1, selecting a factor graph set according to a factor graph error probability method; 2, selecting one factor graph from the factor graph set Z in sequence to perform BP decoding; 3, if the decoding is correct, ending the decoding; otherwise, executing the step 4; 4, if the factor graph is the last factor graph, determining that the decoding fails, and ending the decoding; otherwise, executing the step 5; 5, selecting two positions with the lowest reliability in the x end according to adecoding result in the current factor graph, namely selecting an unreliable position; 6, selecting an unreliable position symbol; and 7, updating the channel initial information, and then turning to the step 2 for execution. According to the method, the performance of BP decoding is close to the performance of CASCL8, the requirement of engineering application is met, meanwhile, the time delay ofthe algorithm can be effectively reduced through parallelization, and the time delay requirement is met.

Owner:BEIHANG UNIV

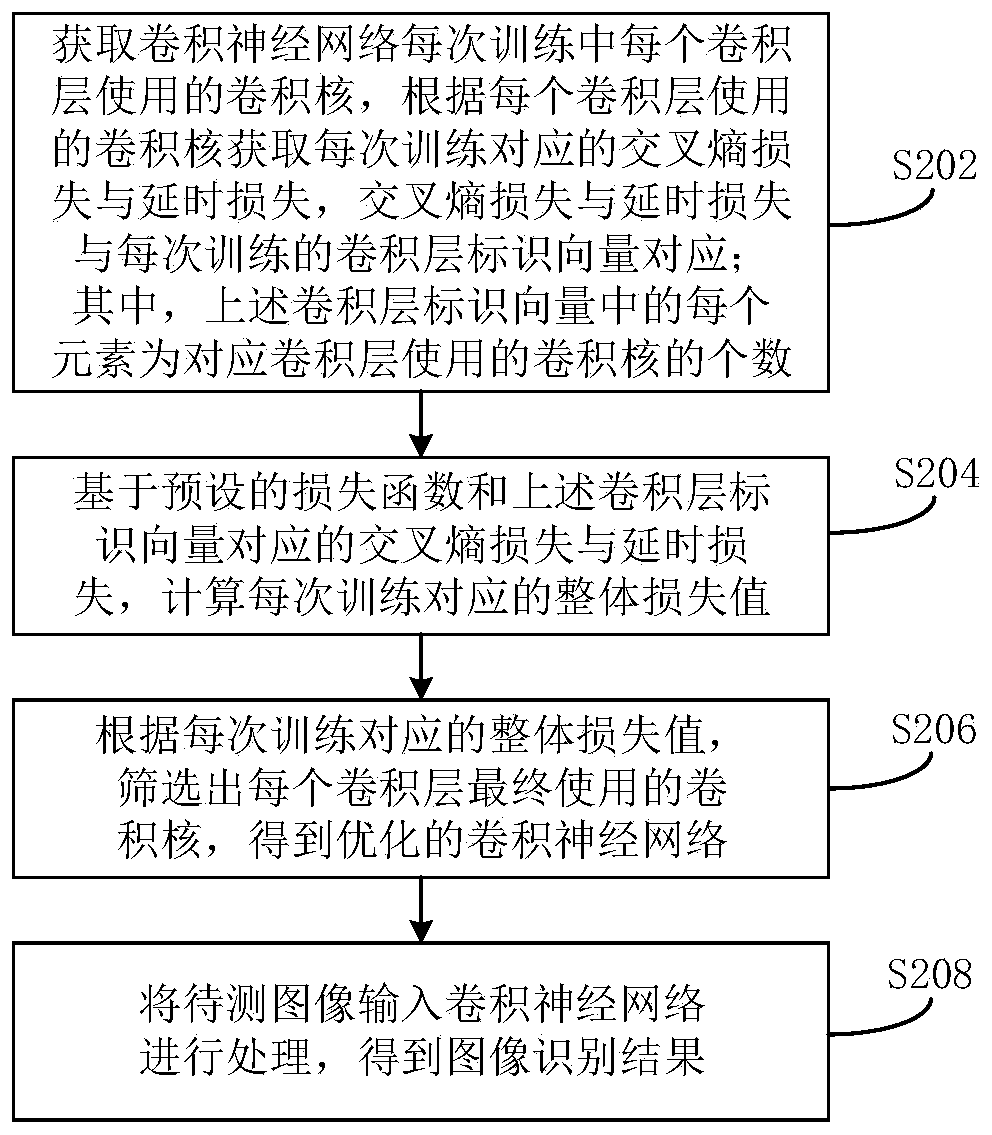

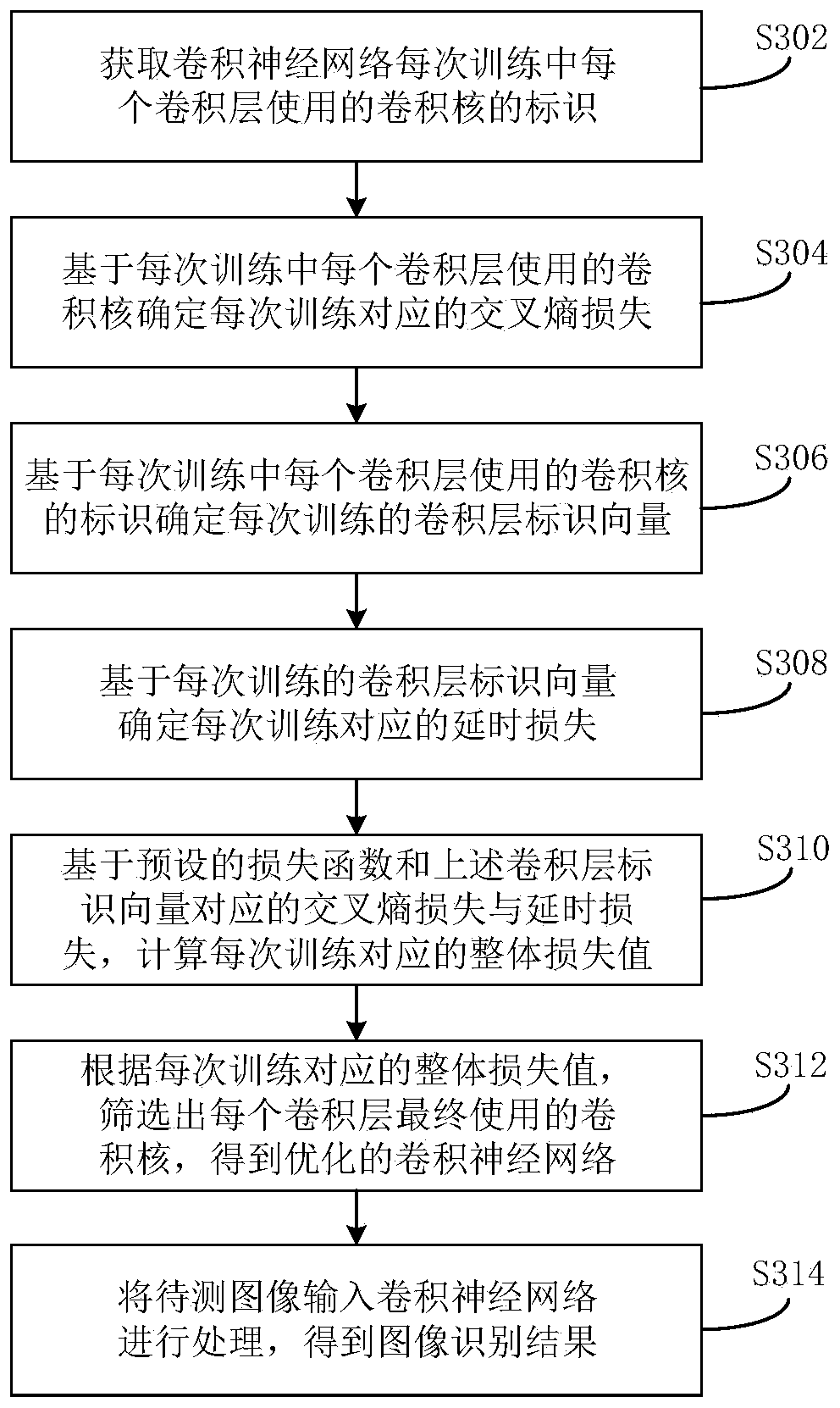

Processing method and device based on optimized neural network, and electronic system

InactiveCN110852425AMeet the delay requirementImprove accuracyNeural architecturesElectronic systemsAlgorithm

The invention provides a processing method and device based on an optimized neural network and an electronic system. The method comprises the steps of acquiring a convolution kernel used by each convolution layer in each time of training of the convolutional neural network, acquiring cross entropy loss and delay loss corresponding to each time of training according to the convolution kernel used by each convolution layer, wherein the cross entropy loss and the delay loss correspond to a convolution layer identification vector of each time of training; calculating an overall loss value corresponding to each training based on a preset loss function and the cross entropy loss and delay loss corresponding to the convolutional layer identification vector; and screening out a convolution kernelfinally used by each convolution layer according to the overall loss value corresponding to each training. According to the method, the overall loss value of the convolutional neural network is comprehensively considered based on the cross entropy loss and the delay loss corresponding to each time of training so as to perform dual-objective optimization on the accuracy and the delay of the convolutional neural network, and the convolutional neural network which meets the delay requirement and is relatively high in accuracy can be screened out.

Owner:MEGVII BEIJINGTECH CO LTD

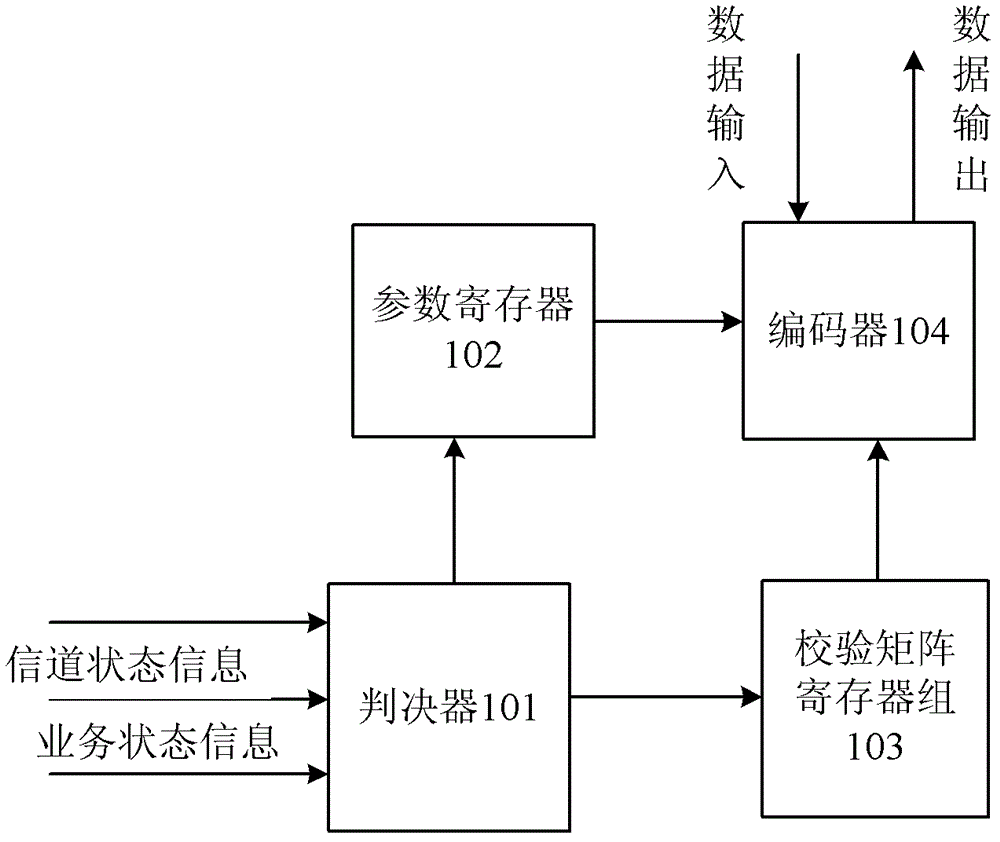

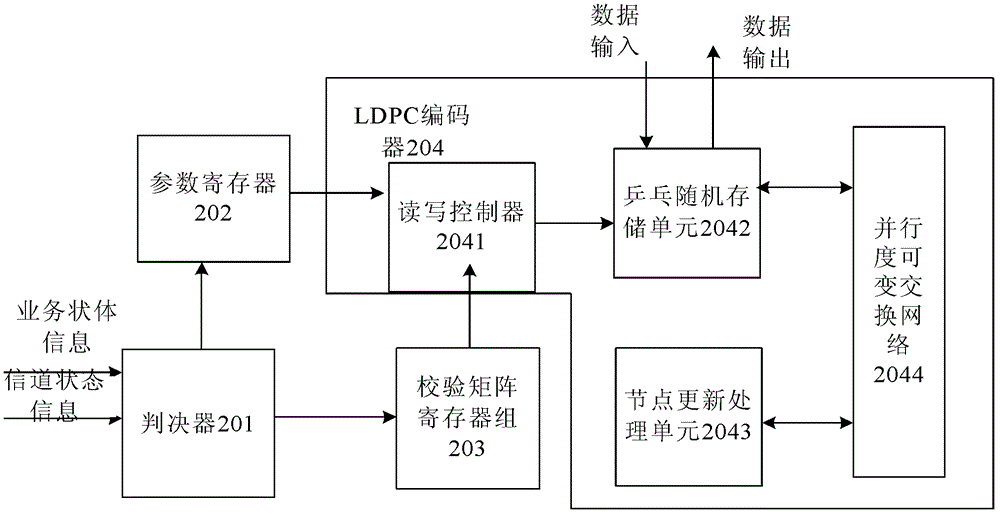

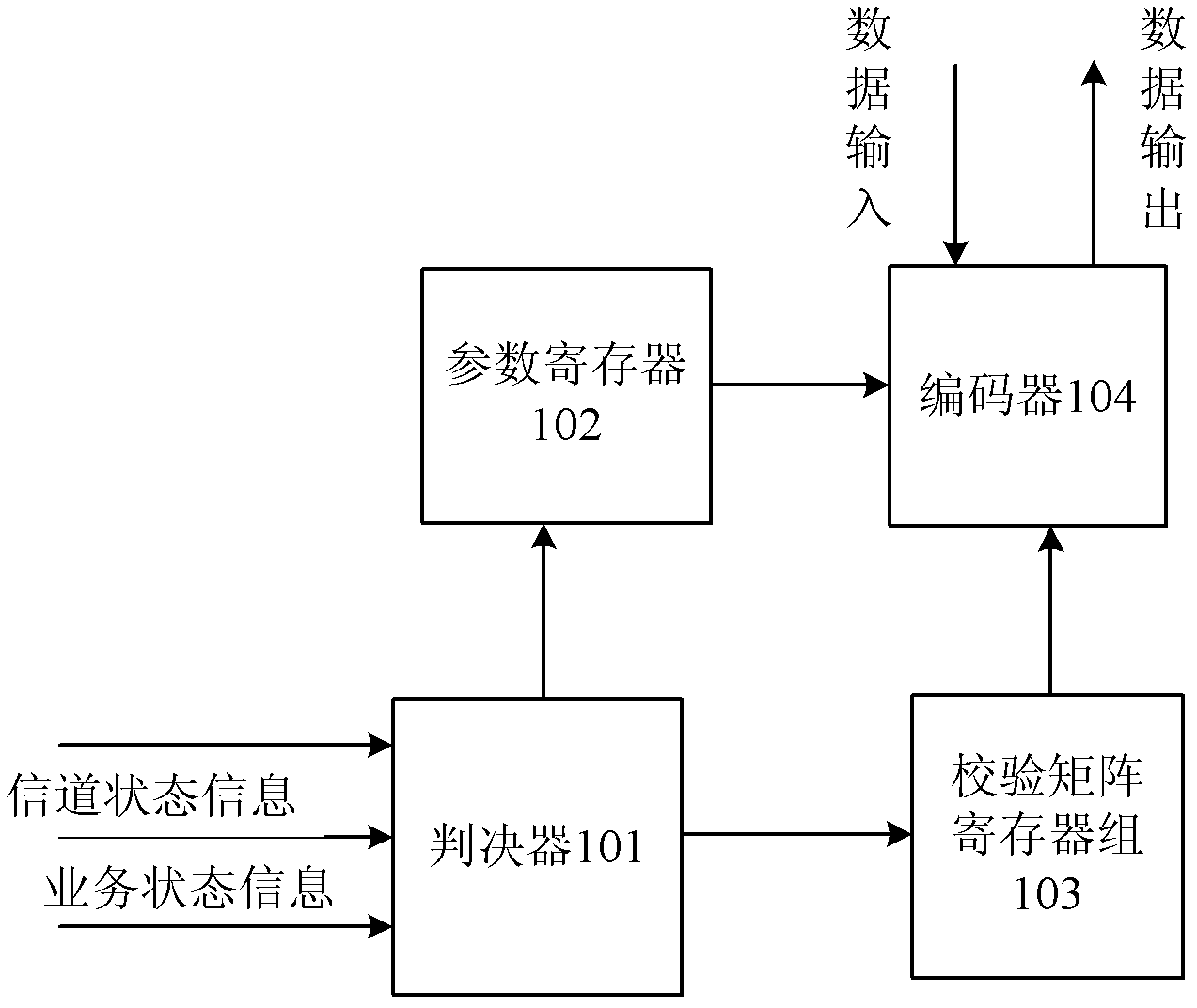

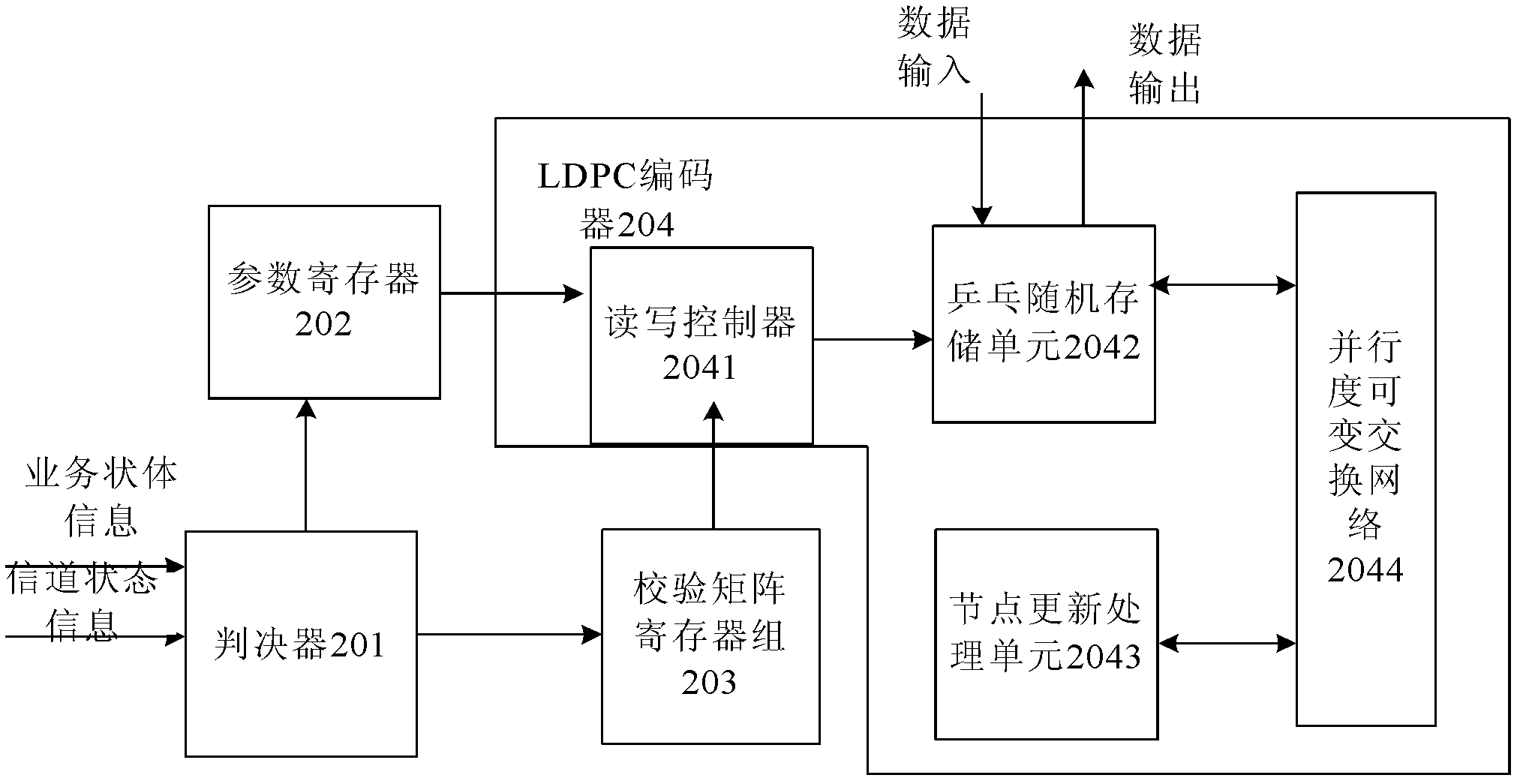

Encoding device and method

ActiveCN102801431AMeet the delay requirementLow complexity costError preventionError correction/detection using multiple parity bitsChannel state informationRegister bank

The invention discloses an encoding device and an encoding method. The device comprises a decision device, a parameter register, a check matrix register bank and an encoder, wherein the decision device is used for obtaining parameter information required by the encoding of data according to the service state information and channel state information of the received data; the parameter register is used for storing the parameter information required by the encoding of a service; the check matrix register bank is used for obtaining a check matrix required by the encoding of the service according to the parameter information; and the encoder is used for encoding the received data according to the parameter information and the check matrix, and outputting the encoded data.

Owner:HUAWEI TECH CO LTD

Superspeed wireless local area network frame polymerization device and control method thereof

InactiveCN101969665BImprove throughput performanceMeet the delay requirementsNetwork traffic/resource managementNetwork topologiesTime errorTime delays

The invention discloses a superspeed wireless local area network frame polymerization device and a control method thereof. The device comprises a transmitting end and a receiving end, wherein the transmitting end comprises a frame format control unit and a transmitting unit; the receiving end comprises a receiving unit and a control command unit, and the control command unit controls a frame polymerization / segmentation mode and an access mode under different services and comprises an optimal frame format control module and a frame polymerization control command generation module; the optimal frame format control module receives real-time error rate information from the receiving unit, and compares the real-time error rate information with an error rate interval comparison table to select an optimal frame polymerization / segmentation mode and access mode; and according to the optimal frame polymerization / segmentation mode and access mode, the frame polymerization control command generation module generates a frame polymerization / segmentation control command for carrying out frame polymerization / segmentation control on the frame format control unit of the transmitting end. The method and the device provided by the invention can select proper polymerization modes and polymerization frame numbers in real time according to the service type and the error rate situation, and the wireless local area network is enabled to improve the throughput performance while satisfying time delay.

Owner:SOUTHEAST UNIV

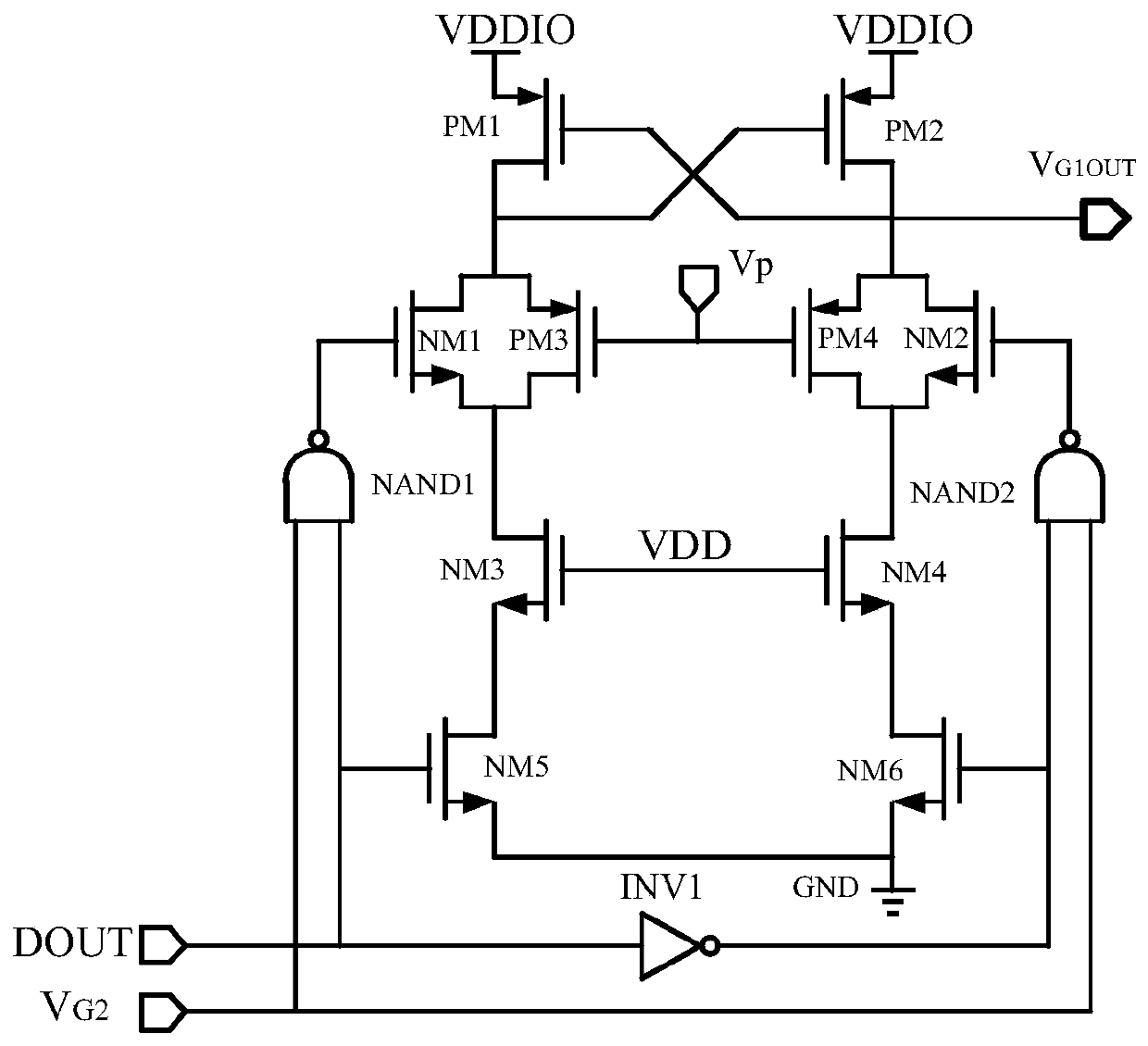

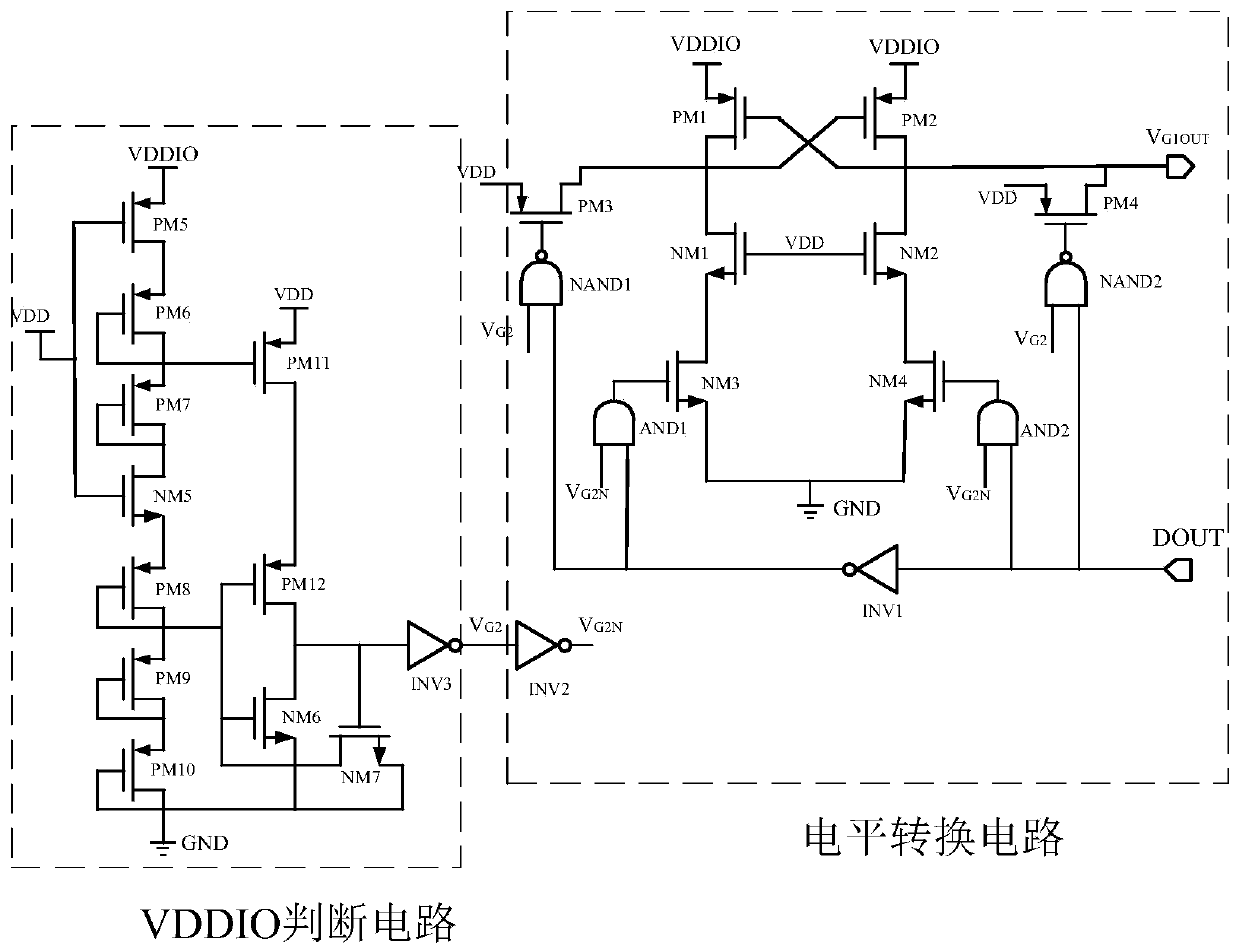

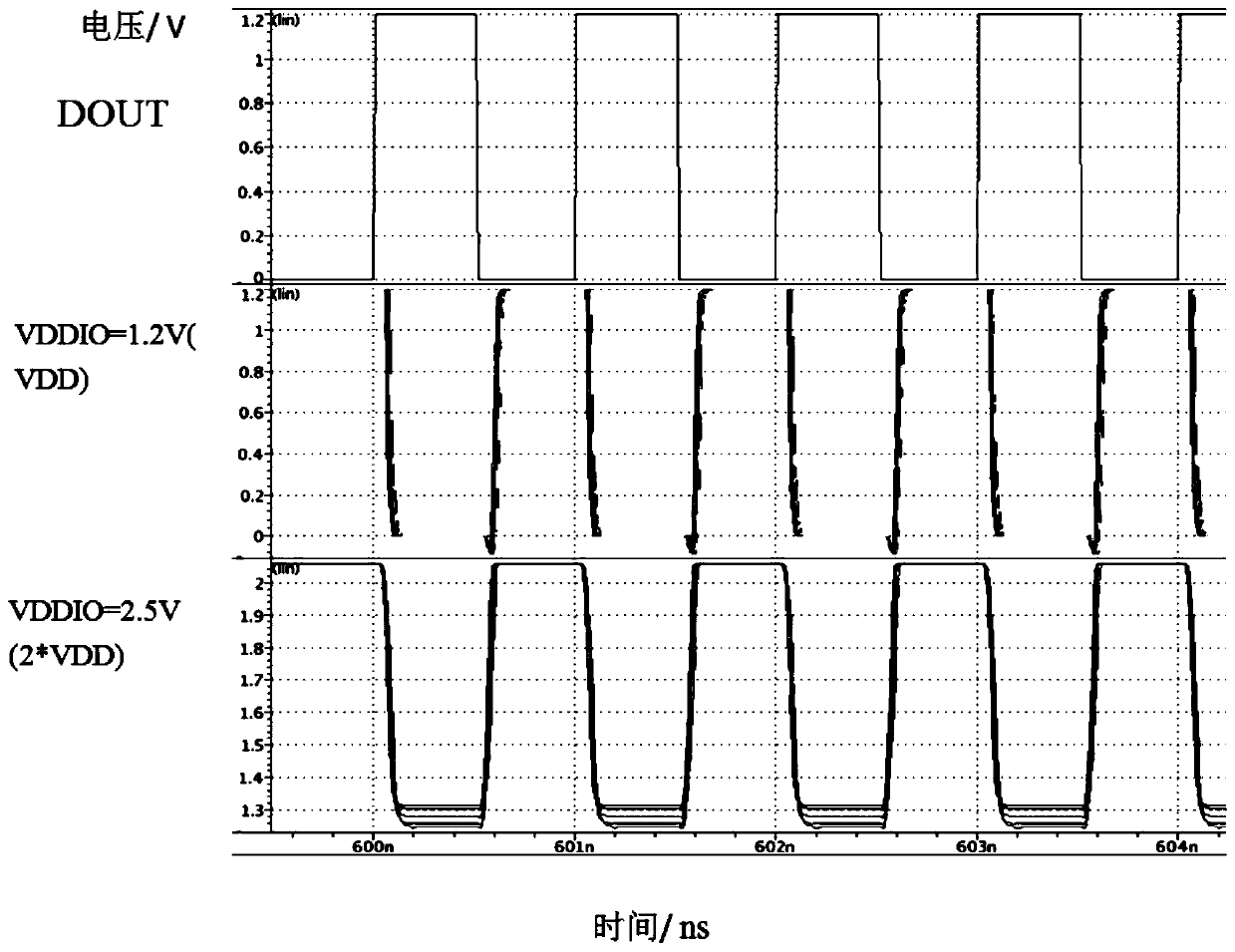

High-speed level conversion circuit applied to mixed voltage output buffer

PendingCN110890885AAvoid gate overvoltageAccurate outputLogic circuits coupling/interface using field-effect transistorsLogic circuit interface arrangementsLevel shiftingControl signal

The invention provides high-speed level conversion circuit applied to a mixed voltage output buffer. The circuit comprises a level conversion circuit and a VDDIO judgment circuit, and corresponding correct bias signals are provided for an output stage of the output buffer to drive a PMOS transistor in different voltage modes. VDDIO is the working mode voltage of the output buffer and can be VDD and 2 * VDD, DOUT is a pulse signal needing to be transmitted, and the VDDIO judgment circuit provides a control signal VG2 for the level conversion circuit according to the VDDIO voltage. In the VDD mode of the output buffer, VG2 is logic '0', PM3 and PM4 are closed, NM3 and NM4 are respectively conducted or closed according to the level state of DOUT, and 0-VDD pulse signals are output. In the 2 *VDD mode, VG2 is logic '1', PM3 and PM4 are switched on, NM3 and NM4 are switched off, and VDD-2 * VDD pulse signals are output. Voltage generation paths of different working modes of VDDIO are controlled through the logic gate so as to improve the speed of level conversion, and therefore the transmission frequency of the output buffer is improved.

Owner:重庆中易智芯科技有限责任公司

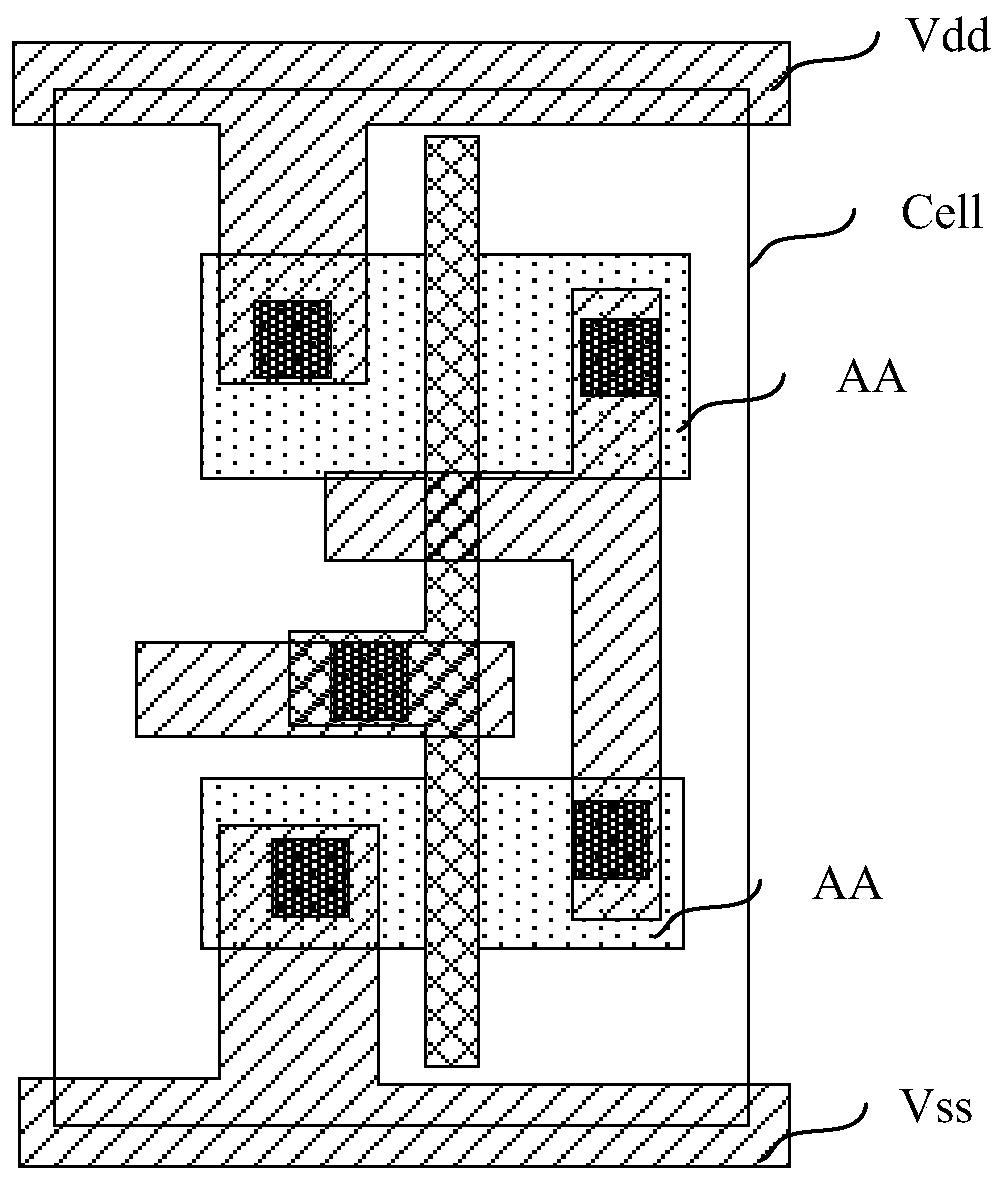

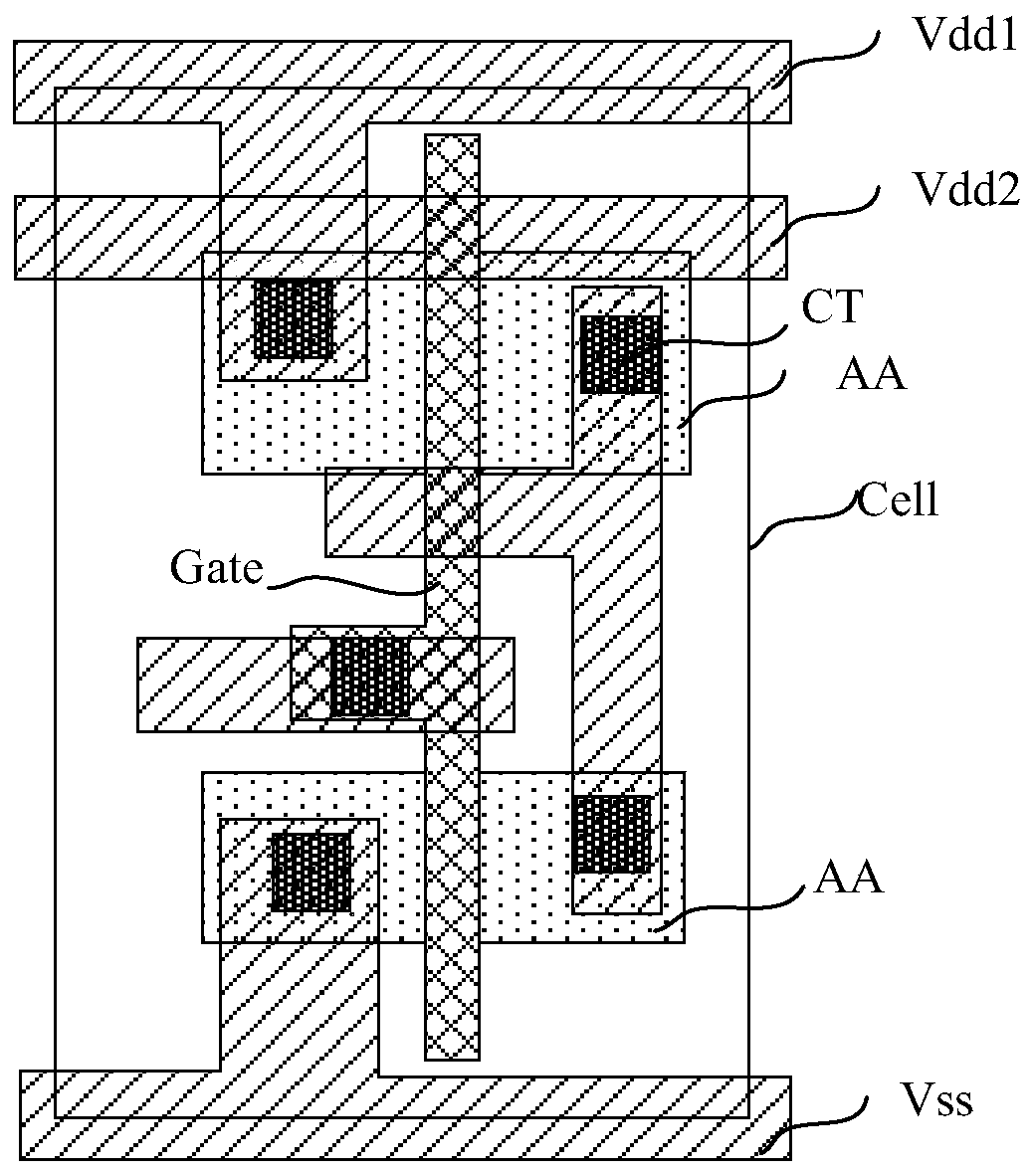

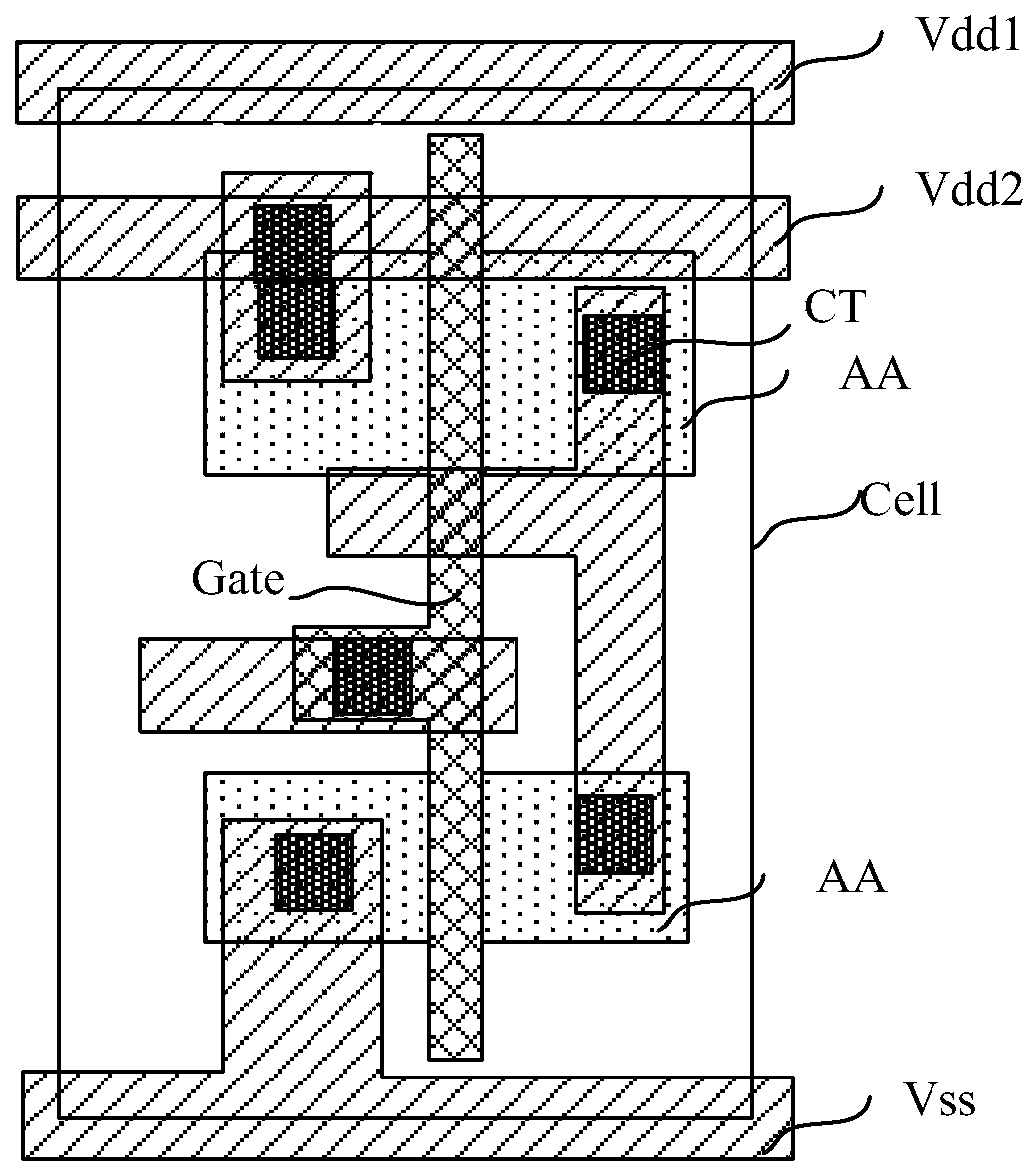

Dual-power standard cell, dual-power standard cell library and integrated circuit design method

PendingCN111079371ADoes not change the areaDoes not change functionalityVolume/mass flow measurementPower supply for data processingCell regionLow voltage

The invention provides a dual-power standard cell, a dual-power standard cell library and an integrated circuit design method. The dual-power standard cell is provided with a conventional power line and a low-voltage power line; the conventional power line and the low-voltage power line are configured to alternatively provide power voltage for the dual-power standard cell; after the conventional power line and the low-voltage power line are respectively selected, conventional power supply voltage and low-voltage power supply voltage can be correspondingly provided for the dual-power standard cell; during integrated circuit design, a dual-power standard cell connected with conventional power voltage on a non-critical path of an integrated circuit can be replaced with a dual-power standard cell connected with low-voltage power voltage according to needs; therefore, the non-critical path is optimized, and the time delay of the non-critical path is still faster than that of the critical path, so that the purpose of reducing switching power consumption and electric leakage power consumption is achieved, and an additional mask plate is not added to a manufacturing process corresponding to an integrated circuit due to layout change of a cell region.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

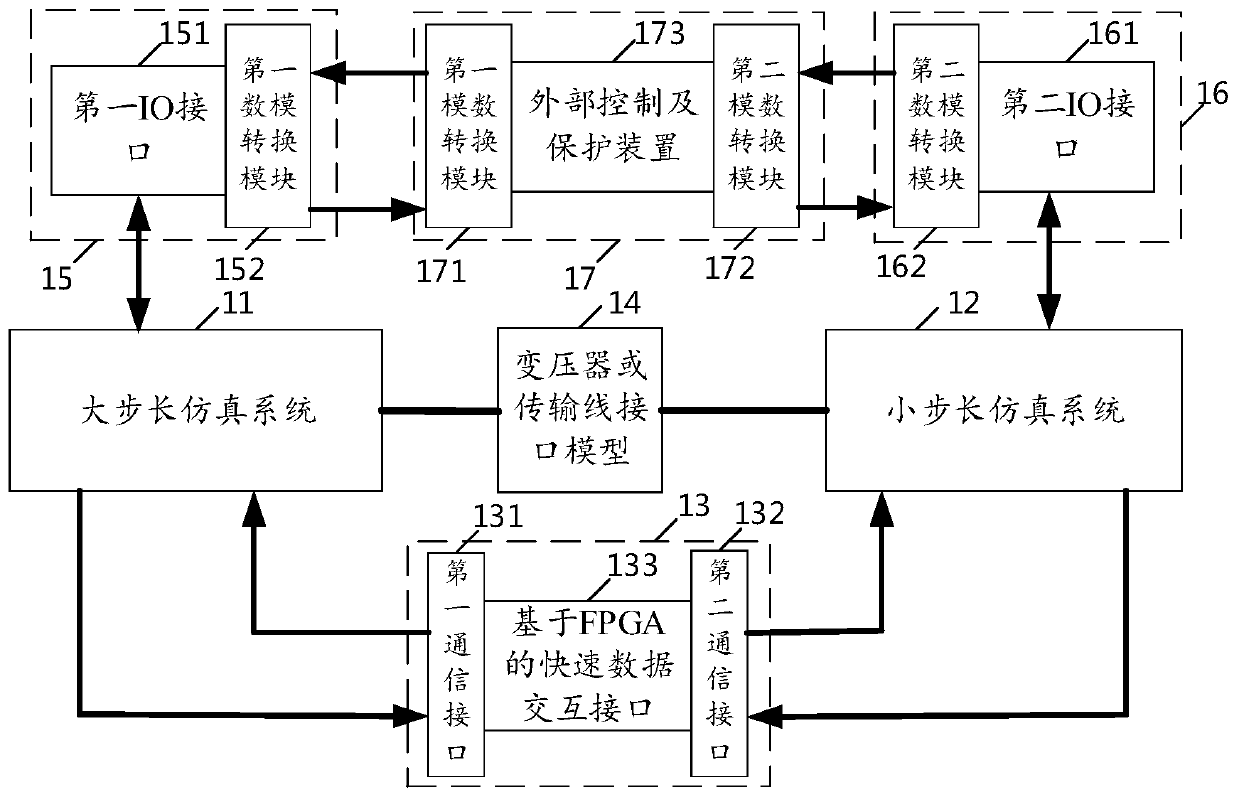

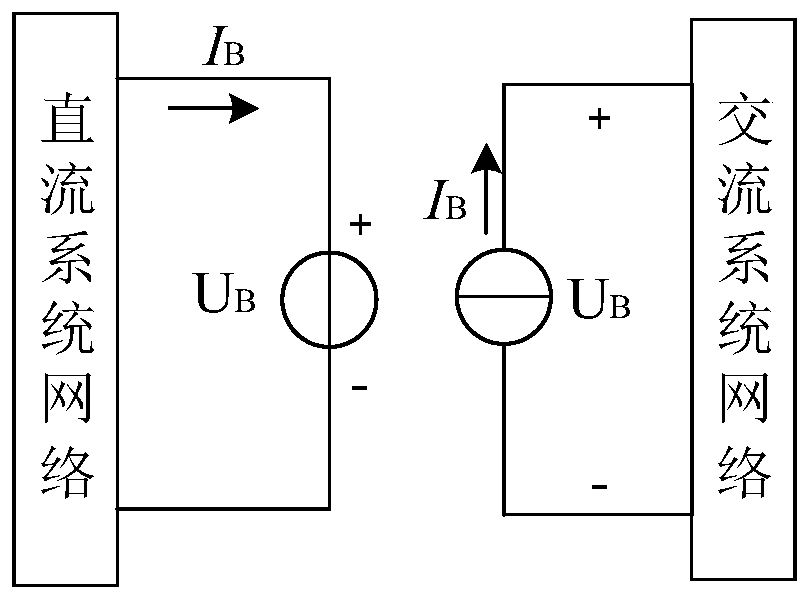

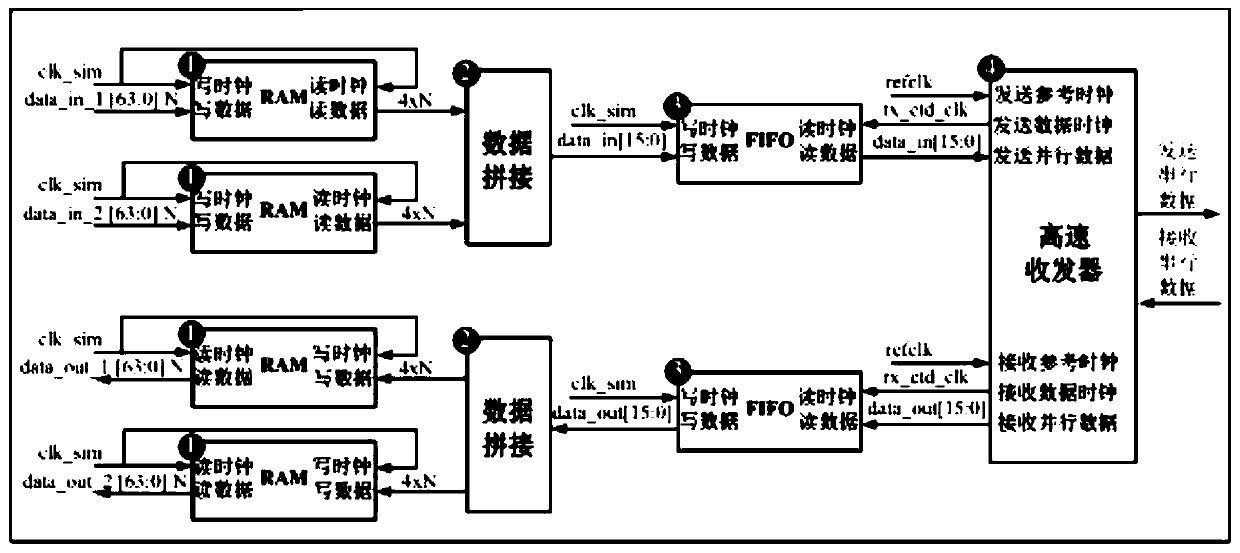

Electromagnetic transient simulation device for alternating-current and direct-current power system

ActiveCN111596567AMeet the delay requirementGuaranteed calculation accuracySimulator controlTransformerElectronic switch

The invention discloses an electromagnetic transient simulation device for an alternating-current and direct-current power system. The electromagnetic transient simulation device comprises a large-step simulation system, a small-step simulation system, a rapid data interaction module, a connection module, and a rapid data interaction module. The large-step simulation system is used for simulatingan alternating current simulation system according to the first simulation step length by adopting a preset electromagnetic transient simulation model; the small-step simulation system is used for simulating a direct-current system composed of the high-frequency power electronic switching device according to the second simulation step length by adopting a pre-established FPGA high-frequency simulation model; the connection module is used for connecting a direct-current system with an alternating-current system; the connection module is a transformer or transmission line interface model; and the rapid data interaction module is connected with the large-step simulation system and the small-step simulation system, and is used for carrying out simulation data interaction on the large-step simulation system and the small-step simulation system. Therefore, the electromagnetic transient simulation speed of the alternating-current and direct-current large power grid can be effectively improved, and the rapid simulation requirement and the precision requirement of a large-scale power system are met.

Owner:ELECTRIC POWER RESEARCH INSTITUTE, CHINA SOUTHERN POWER GRID CO LTD +1

A Decoding Method of Polar Code bp List

ActiveCN111010196BLower latencyMeet the needs of engineering applicationsError correction/detection using multiple parity bitsCode conversionTheoretical computer scienceDependability

The invention discloses a polar code BP List decoding method. Step 1: select a factor graph set according to the method of factor graph error probability; Step 2: select a factor graph from the factor graph set Z in order to perform BP decoding; Step 3: If the decoding is correct, end the decoding; otherwise, execute step 4; Step 4: If it is the last factor graph, then the decoding fails, and end the decoding; otherwise, execute Step 5; Step 5: According to the current factor graph For the decoding result in the figure, select the two positions with the lowest reliability in the x terminal, that is, select the unreliable position; Step 6: Select the symbol of the unreliable position; Step 7: Update the initial information of the channel, and then go to Step 2 for execution. The method of the invention can not only realize the performance of BP decoding close to that of CASCL8 and meet the requirements of engineering applications, but also the parallel implementation of the invention can effectively reduce the delay of the algorithm and meet the requirement of delay.

Owner:BEIHANG UNIV

A digital signal optical fiber transmission trigger system

ActiveCN105790746BAcquisition stableAvoid false triggersElectronic switchingFibre transmissionCapacitanceTransformer

The present invention discloses a digital signal fiber transmission triggering system. The system comprises an electric signal-optical signal conversion module and an optical signal-electric signal conversion module which are connected through a fiber connection line; the electric signal-optical signal conversion module has an input end which is taken as the signal input interface of a digital signal fiber transmission triggering system and is configured to receive external digital triggering signals; and the optical signal-electric signal conversion module is configured to convert the digital signals through external input to optical signals, and the optical signal-electric signal conversion module is configured to convert the optical signals to high low-level digital triggering signals and realize opto-couplers isolation and power amplification of the digital triggering signals. The digital signal fiber transmission triggering system is able to overcome the defect of the inductor (or transformer) type isolation anti-interference capability and solve the problem of the common transmission channel of capacitive coupling noise and signals, is low in cost, extensive in applicability, high in reliability and high in carrying load ability and has long-distance fiber transmission signals, etc.

Owner:HUAZHONG UNIV OF SCI & TECH

Encoding device and method

ActiveCN102801431BMeet the delay requirementsLow complexity costError preventionError correction/detection using multiple parity bitsChannel state informationRegister bank

Owner:HUAWEI TECH CO LTD

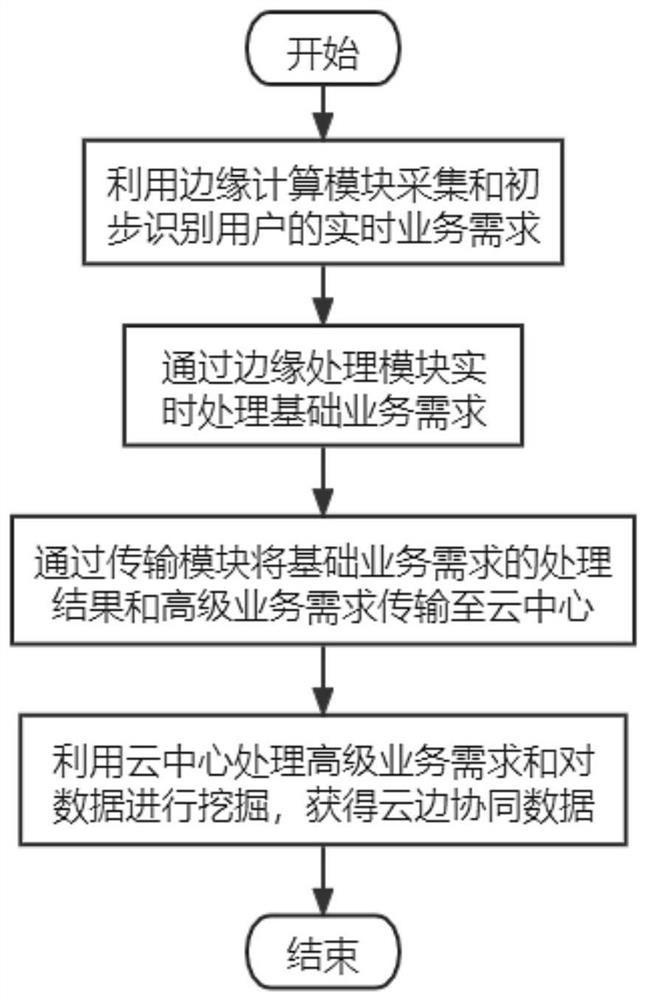

Cloud edge collaborative data acquisition method and system suitable for power industry

PendingCN114390055AMeet the delay requirementMeet the delay requirementsDatabase distribution/replicationTransmissionData acquisitionRapid processing

The invention discloses a cloud-side collaborative data acquisition method and system suitable for the power industry, and the method comprises the steps: carrying out the collection and preliminary recognition of the real-time business demands of a user through an edge calculation module, and carrying out the collection and preliminary recognition of the real-time business demands; the types of the real-time service requirements comprise basic service requirements and advanced service requirements; the basic service demand is processed in real time through the edge processing module, and the processing result of the basic service demand and the advanced service demand are transmitted to the cloud center through the transmission module; processing advanced service requirements and mining the data by using a cloud center to obtain cloud edge collaborative data; according to the invention, the independent database is arranged on the edge processing module, part of functions of the cloud center are transferred to the user side, the edge processing module is utilized to quickly process the real-time service demand of the user side, and the response time and the processing time of the edge processing module for processing the service are continuously tracked and recorded, so that the delay requirement of the real-time service is met.

Owner:GUANGDONG POWER GRID CO LTD

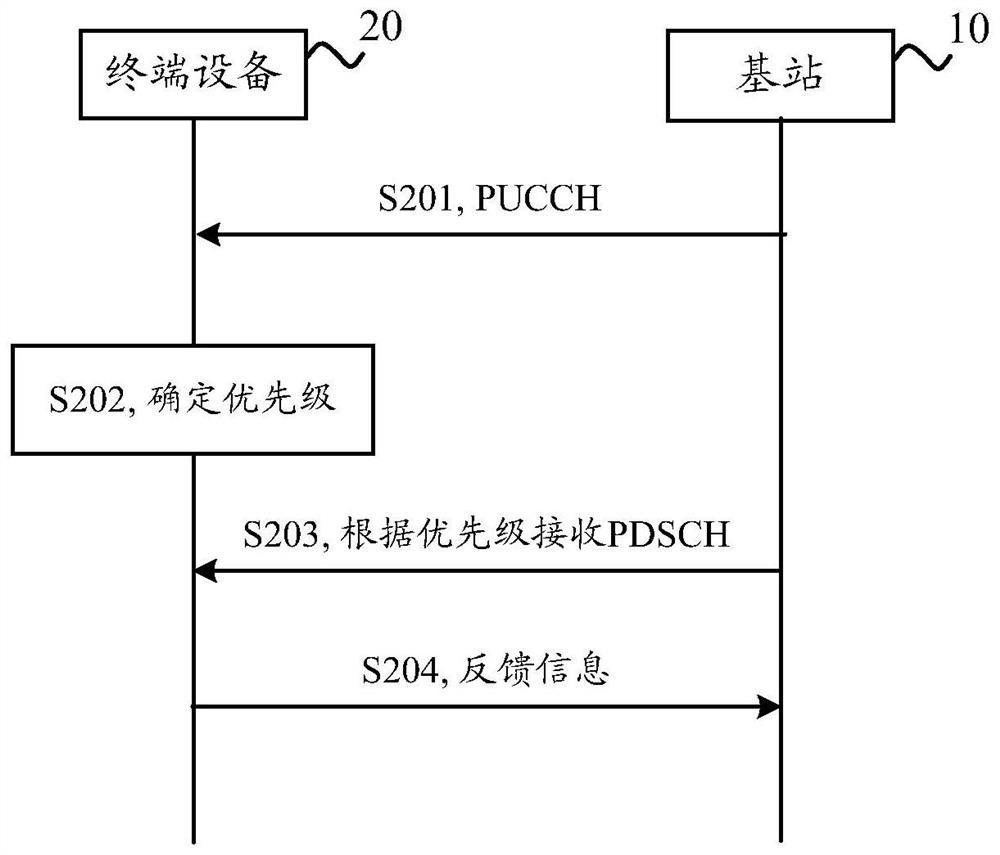

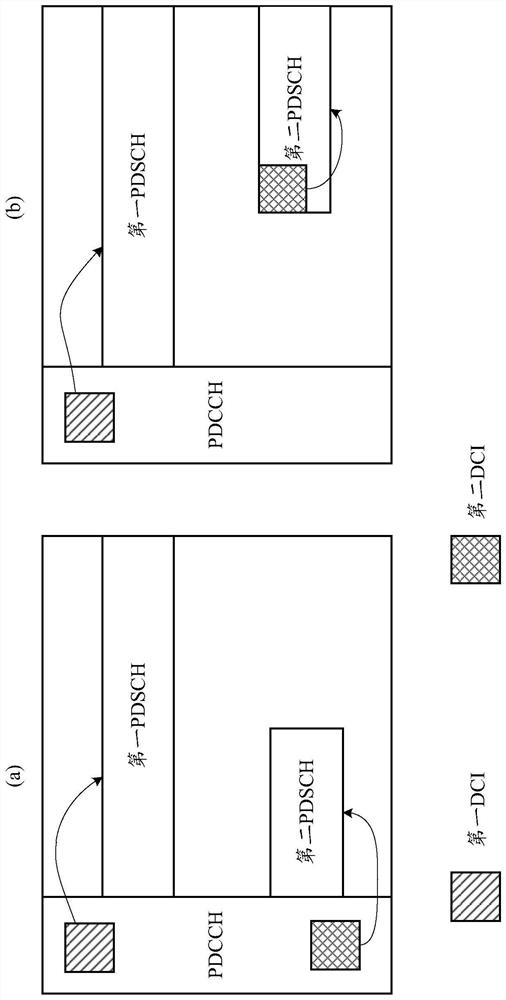

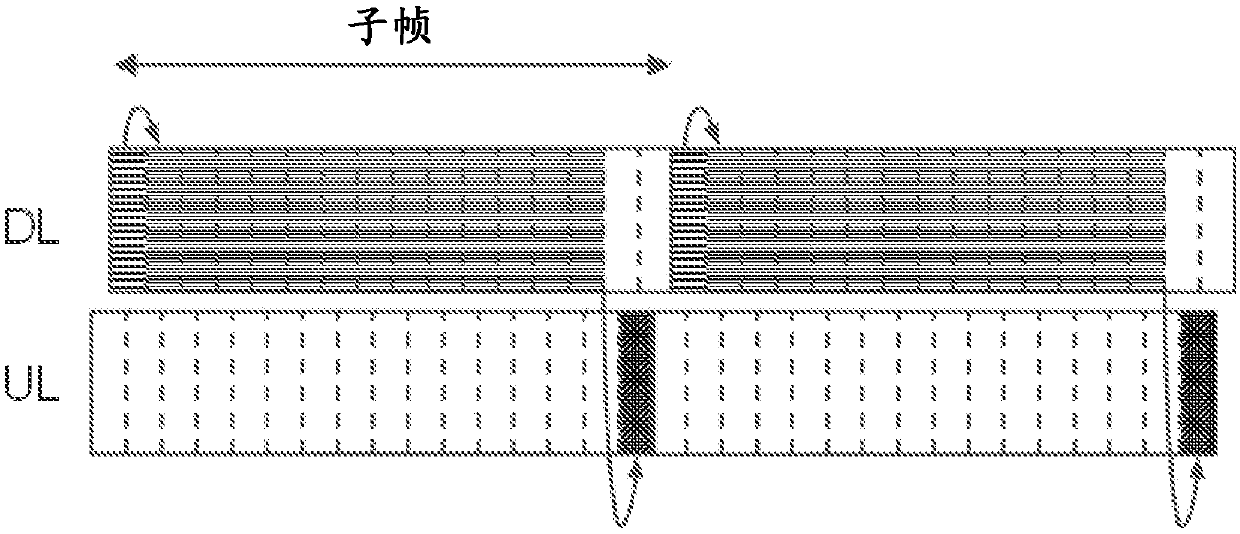

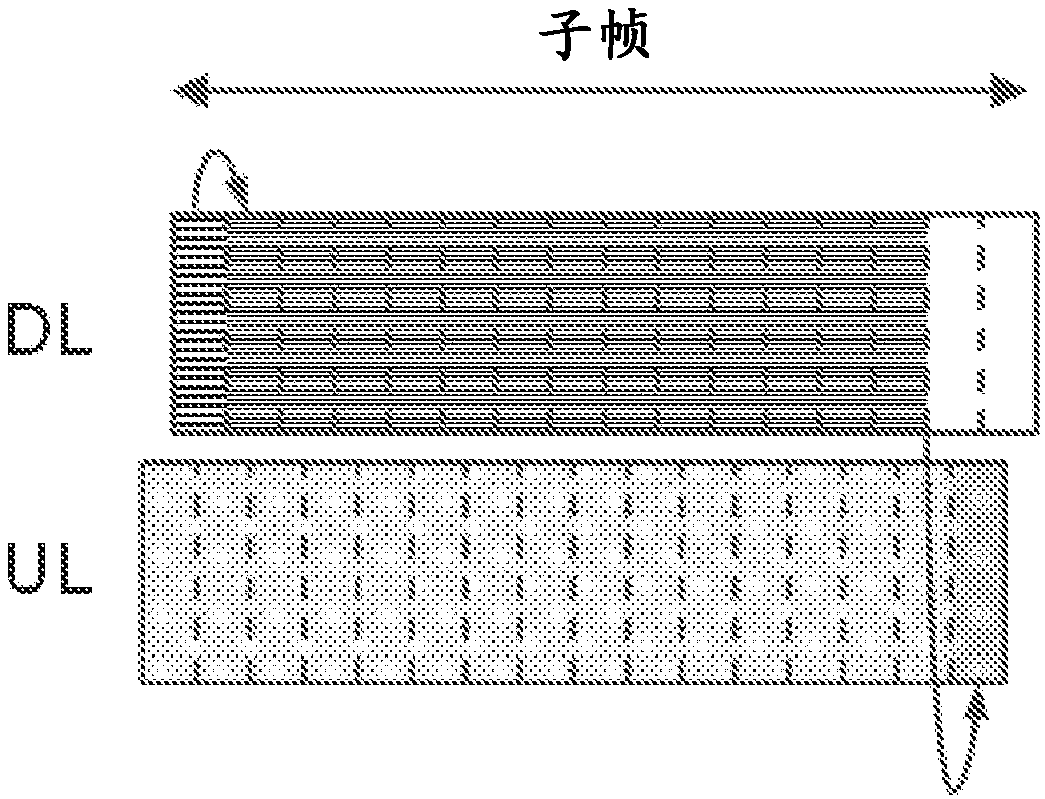

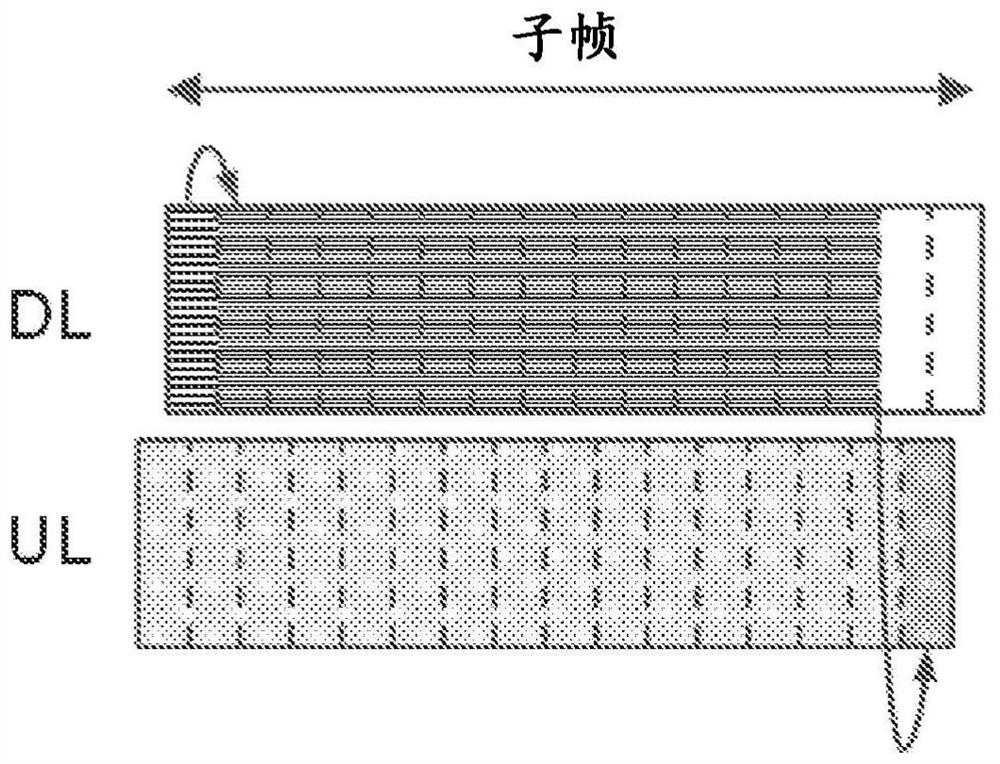

Data transmission method, terminal equipment and network equipment

ActiveCN108292969BMeet the delay requirementsCompatibilityError preventionSignal allocationData transmissionCarrier signal

A data transmission method is provided, including: a terminal device receives a first DCI and a second DCI, wherein the first DCI is used to schedule the terminal device to receive a first PDSCH transmitted using a first TTI in a target carrier, the first The second DCI is used to schedule the terminal device to receive the second PDSCH transmitted using the second TTI in the target carrier, and the first TTI is smaller than the second TTI, the first PDSCH and the second PDSCH at least partially overlapping on time resources; determining a priority relationship between the first DCI and the second DCI; according to the priority relationship, receiving the first PDSCH or the second PDSCH in the target carrier . The method provided by the embodiment of the present invention can dynamically support multiple TTIs for data transmission in the same carrier, and the terminal device can determine the priority of the transmission channel in a carrier. This method can not only meet the delay requirement, but also take into account Compatibility with existing systems.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

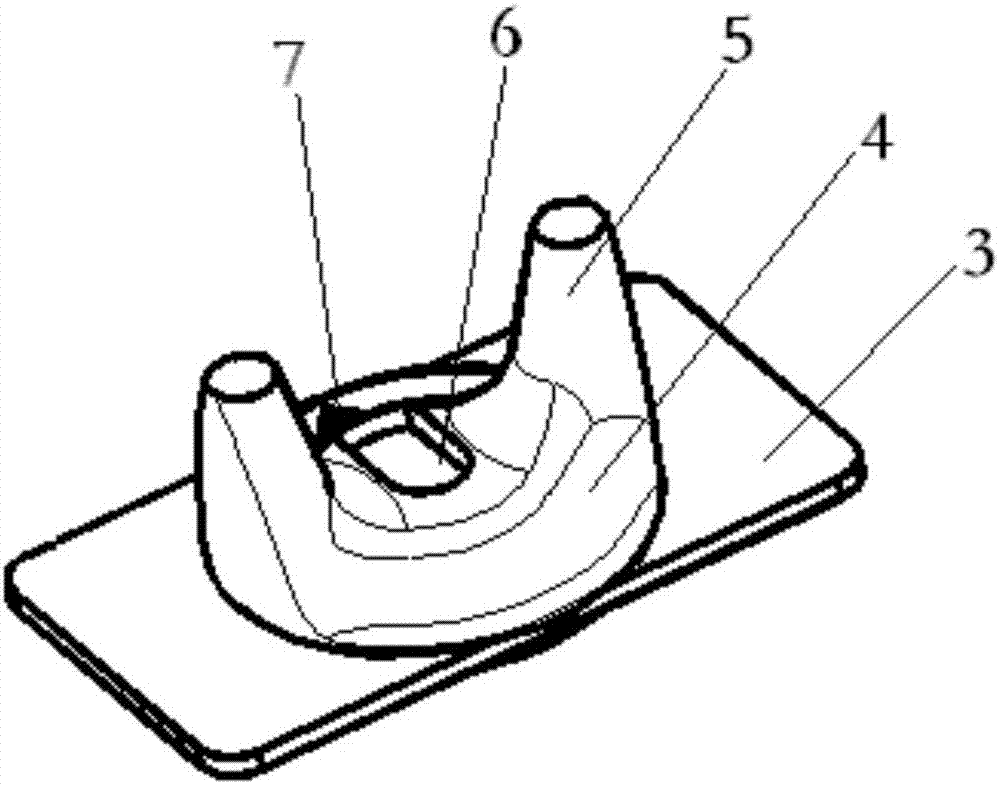

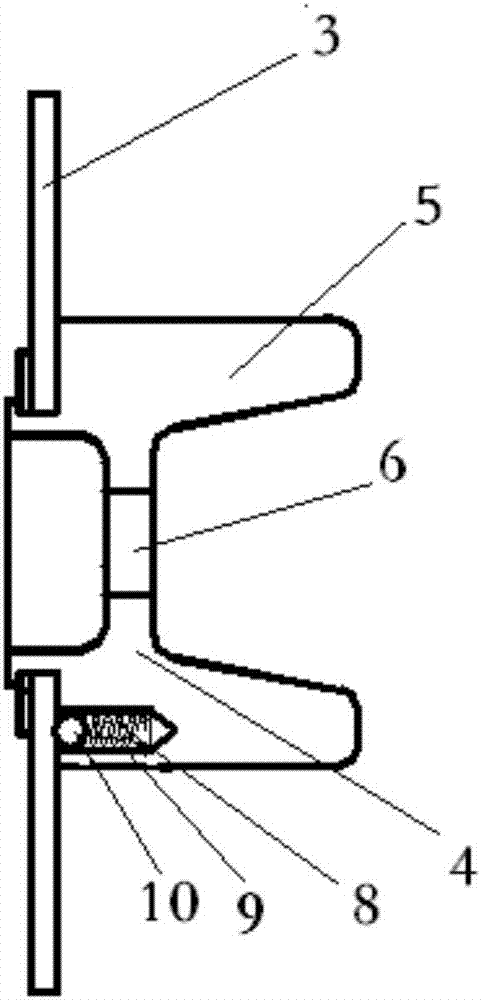

An error-proof limit method for aircraft three-position switch

The invention relates to an error-prevention limitation method for a three-position switch of an aircraft. A switch limitation structure comprises a limitation knob and a base, wherein a constraint hole is formed at the middle of the limitation knob and is biased towards one side, constraint on a state switching path of the three-position switch is formed due to the position and the shape of the constraint hole, a positioning steel ball of the limitation knob is matched with a round guide rail groove and a ball-socket shaped stop point of the base, the positioning steel ball moves along the guide rail groove on the surface of the base to be stopped at a required stop point by rotating the limitation knob, a state handle only can act in the constraint hole along a constraint direction, and thus, the function of error-prevention limitation is achieved.

Owner:XI'AN AIRCRAFT INTERNATIONAL

Echo elimination device for microphone and method thereof

InactiveCN100524466CMeet the delay requirementsGuaranteed to workAdaptive networkSpeech analysisComputer moduleSelf adaptive

This invention discloses a microphone echo elimination device and method, which eliminates echo between microphone and sound circuit, wherein, the device comprises long frame adjust module to combine one self adaptive filter parameter data frame for self adapting filter.

Owner:VIMICRO CORP

Training method of voice bandwidth expansion model and voice bandwidth expansion method

ActiveCN107705801BImprove sound qualityImprove naturalnessSpeech analysisMirror imageNarrowband speech

The invention discloses a training method of a voice bandwidth expansion model and a voice bandwidth expansion method, wherein the voice bandwidth expansion method comprises the following steps: acquiring to-be-expanded narrowband voice; calculating an amplitude spectrum and a phase spectrum of the to-be-expanded narrowband voice, and extracting auxiliary characteristics of the to-be-expanded narrowband voice ; processing the amplitude spectrum and the auxiliary characteristics of the to-be-expanded narrowband voice by virtue of the voice bandwidth expansion model which is obtained from training, so that the amplitude spectrum of a reconstructed bandwidth voice high-frequency band can be obtained; conducting mirror image reversing on the phase spectrum of the to-be-expanded narrowband voice in a frequency domain, and determining the phase spectrum of the bandwidth voice high-frequency band; and on the basis of the amplitude spectrum and the phase spectrum of the narrowband voice, and in combination with the amplitude spectrum and the phase spectrum of the reconstructed bandwidth voice high-frequency band, determining a bandwidth voice signal. With the application of the voice bandwidth expansion method provided by the invention, an effect of improving the tone quality and naturalness of the narrowband voice can be achieved.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

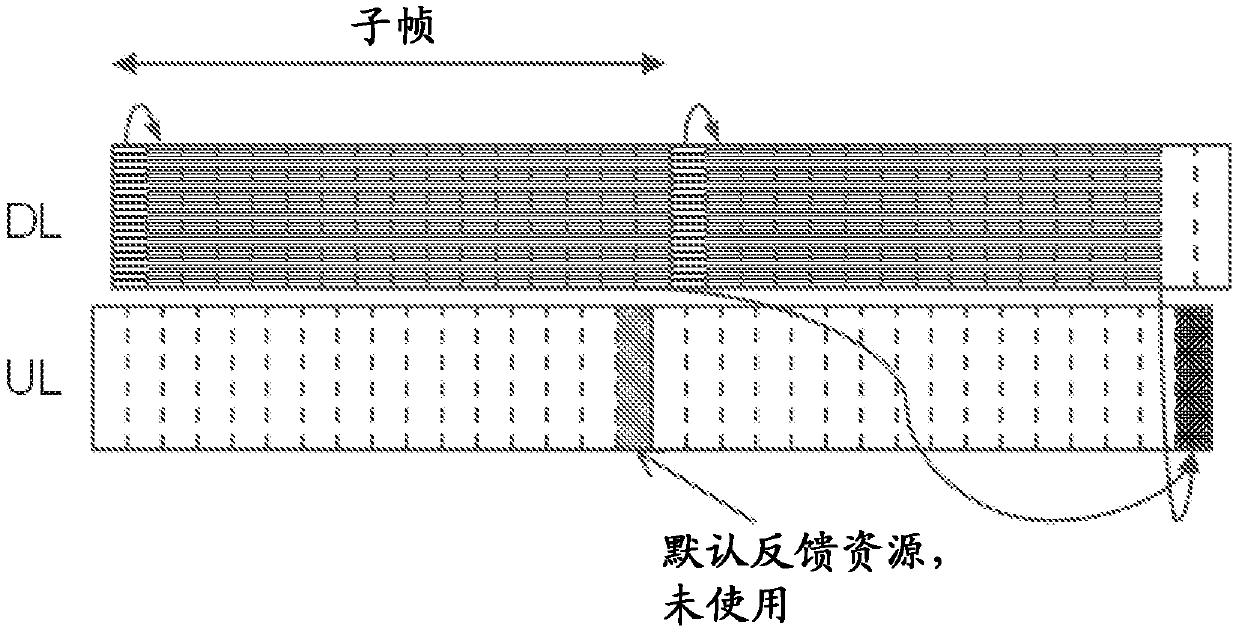

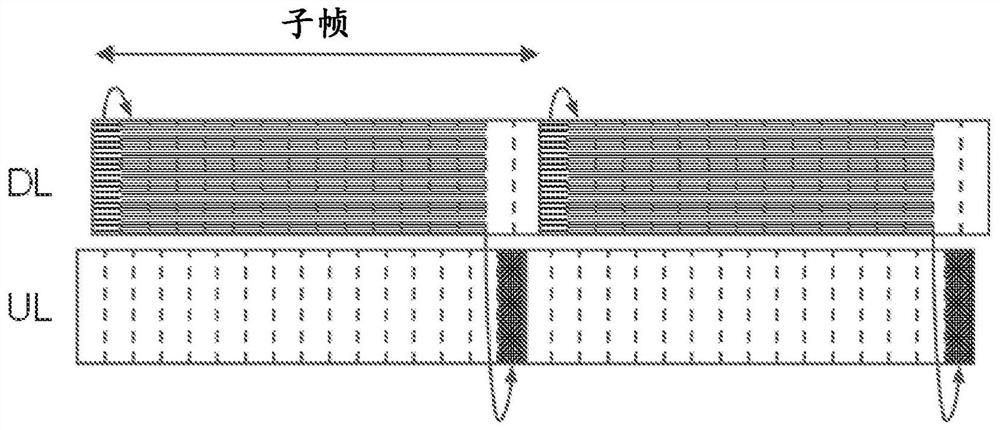

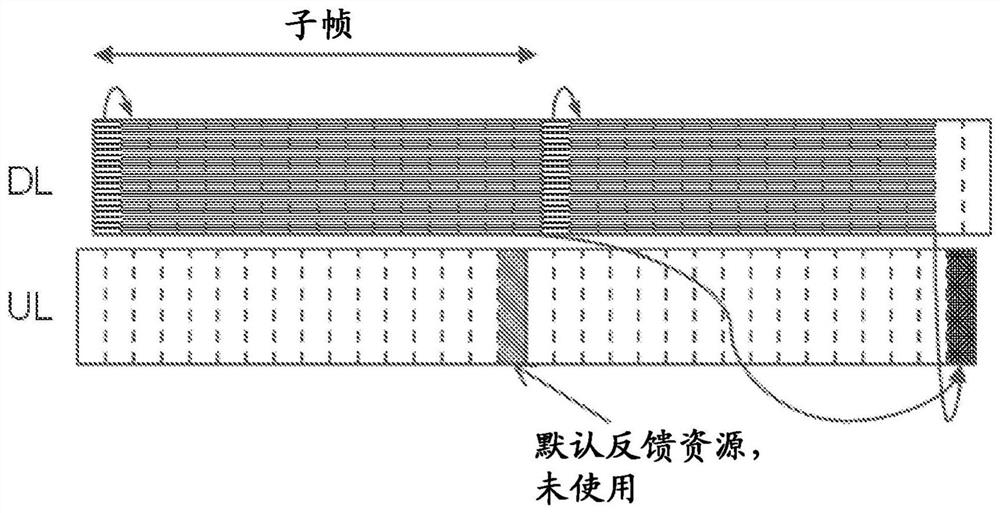

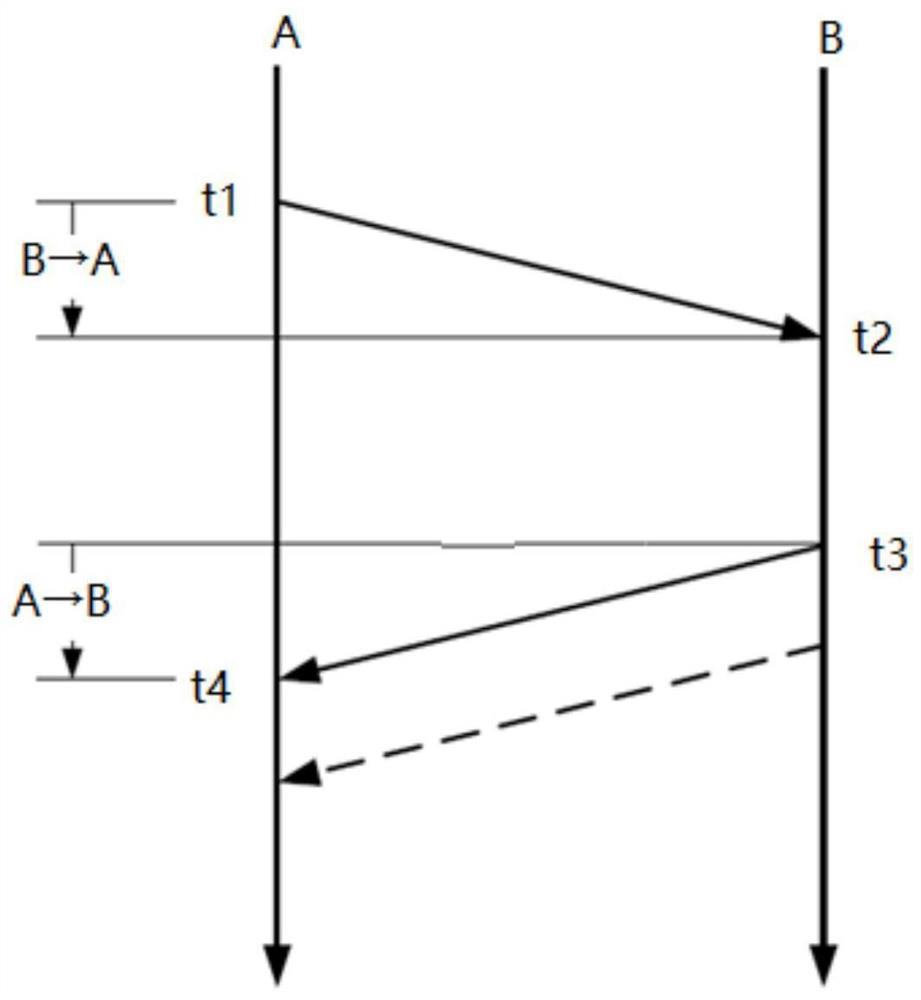

Methods and apparatuses for controlling timing of feedback transmissions

ActiveCN108028729AMeet the delay requirementSave electricityError prevention/detection by using return channelTelecommunications linkEngineering

There is disclosed a method for controlling the timing of feedback transmissions by a communication device (80) communicating over a communication link (70), wherein the communication link supports aretransmission scheme. The method comprises transmitting (42) a feedback timing indicator, FTI, wherein the indicator is selected from a set of indicators.

Owner:TELEFON AB LM ERICSSON (PUBL)

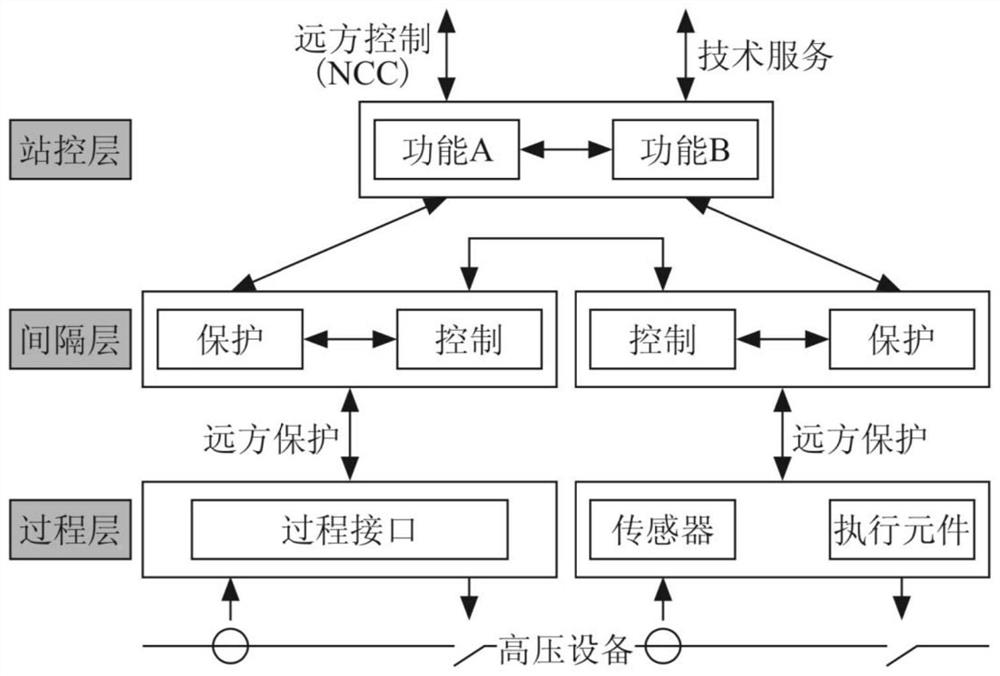

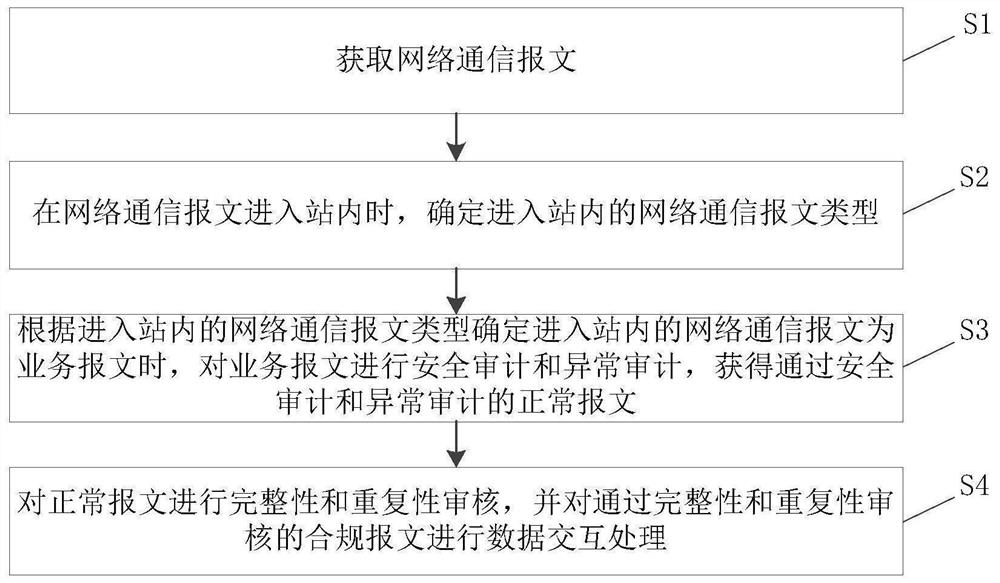

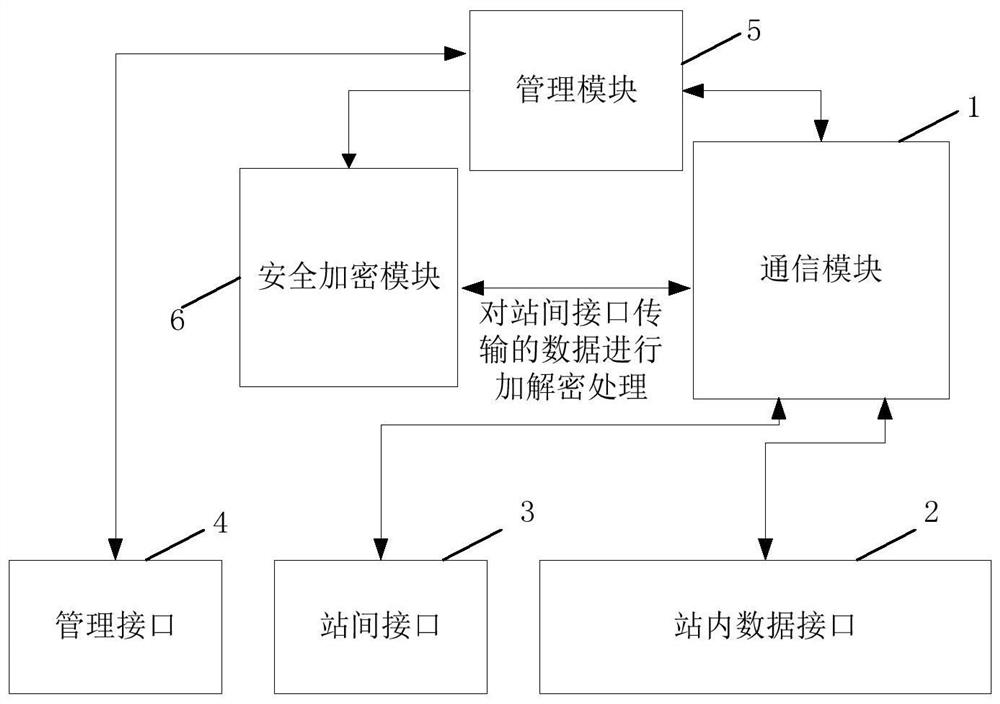

Intelligent substation and network communication security control method and device thereof

PendingCN114301621AMeet the delay requirementAvoid the problem of excessive delayCircuit arrangementsSecuring communicationNetwork communicationMessage passing

The invention discloses an intelligent substation and a network communication security control method and device thereof. The control method comprises the following steps: acquiring a network communication message; when the network communication message enters the station, determining the type of the network communication message entering the station; when the network communication message entering the station is determined to be a service message according to the type of the network communication message entering the station, performing security auditing and abnormal auditing on the service message to obtain a normal message passing the security auditing and abnormal auditing; and performing integrity and repeatability auditing on the normal message, and performing data interaction processing on the compliance message passing the integrity and repeatability auditing. Therefore, according to the control method, data security processing is carried out on the data entering and exiting the intelligent substation, network data transmission security is guaranteed, meanwhile, the problem that data message delay exceeds the standard due to the fact that security strategies of external authentication equipment and security equipment are used is avoided, and it is guaranteed that data transmission meets the requirements of specifications and standards for data delay.

Owner:BEIJING SMARTCHIP MICROELECTRONICS TECH COMPANY +1

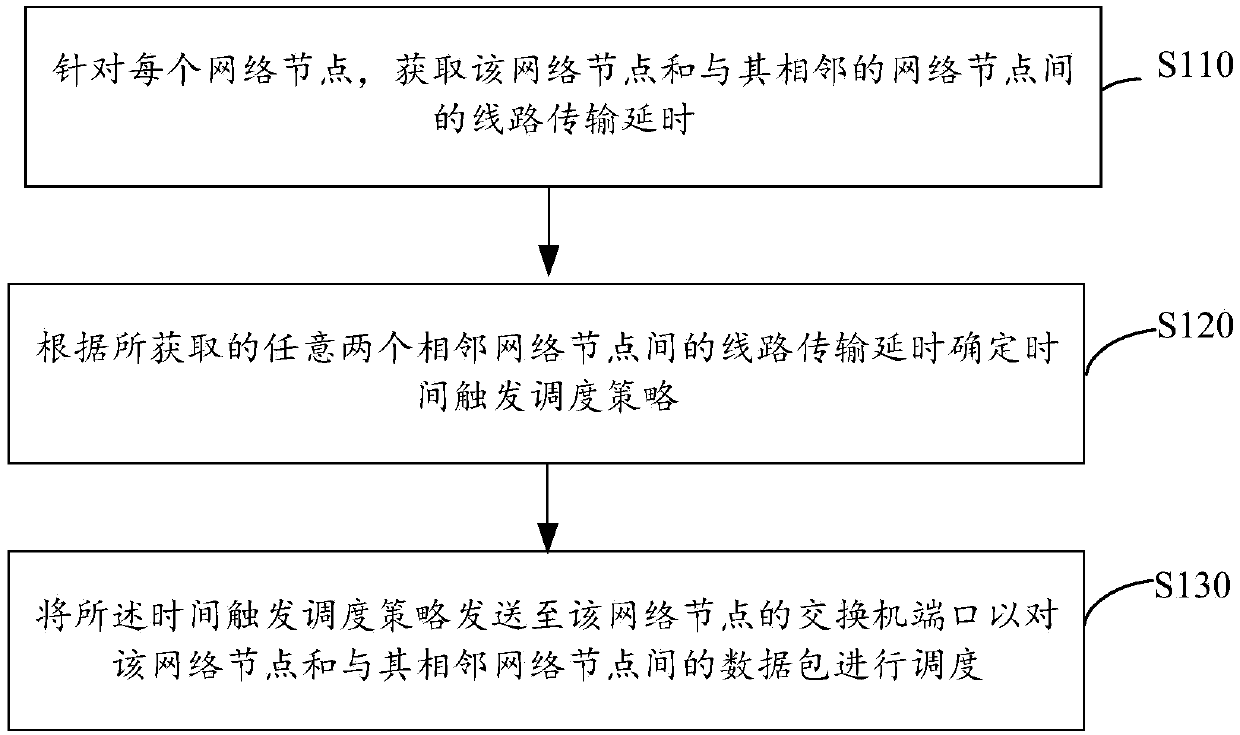

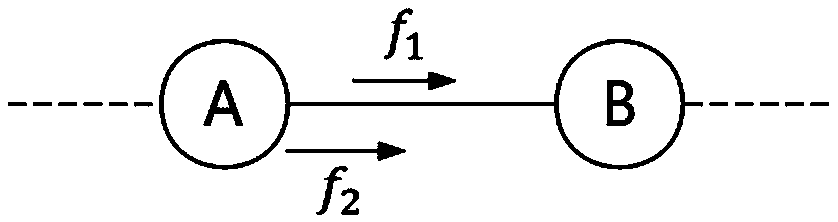

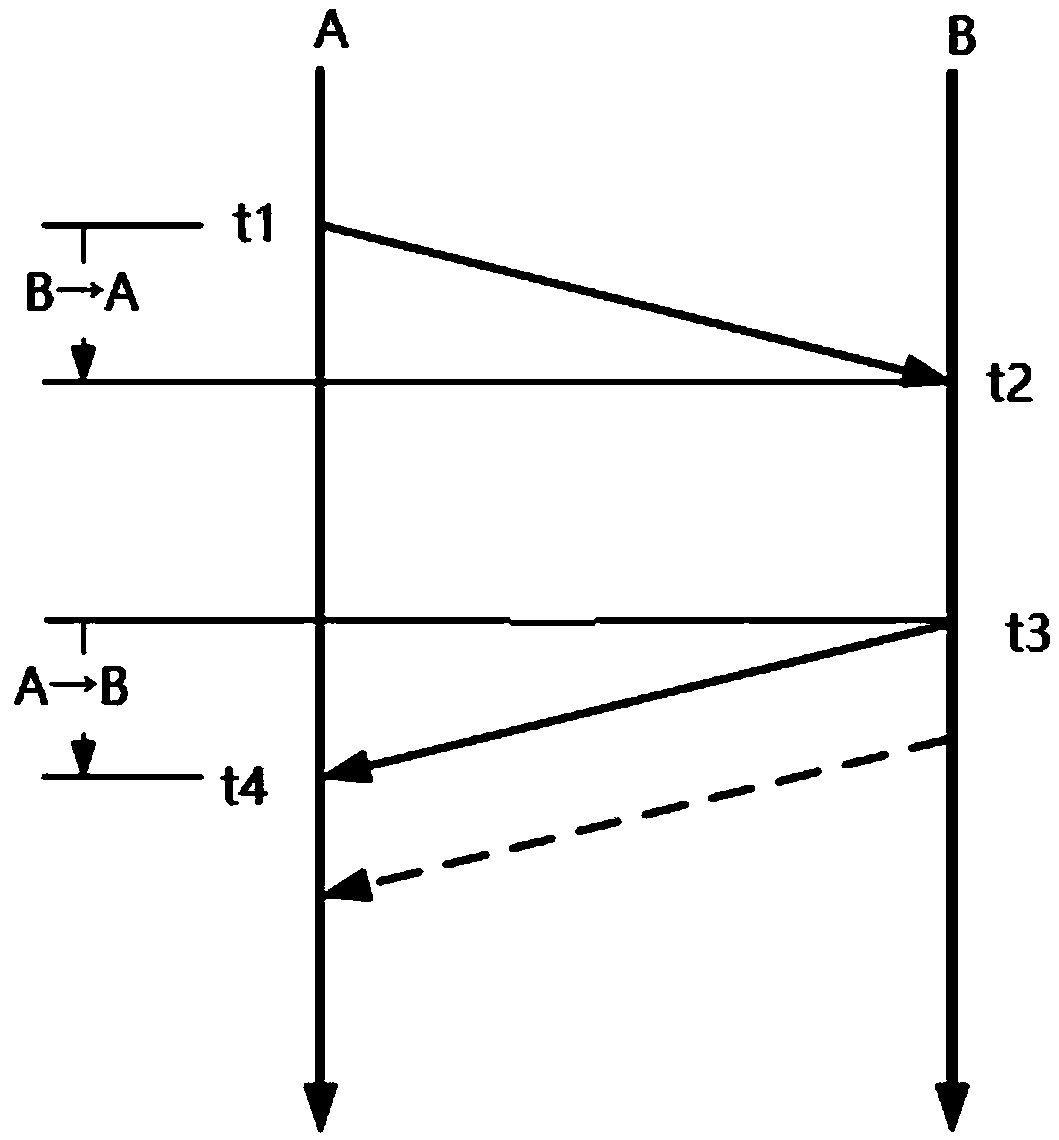

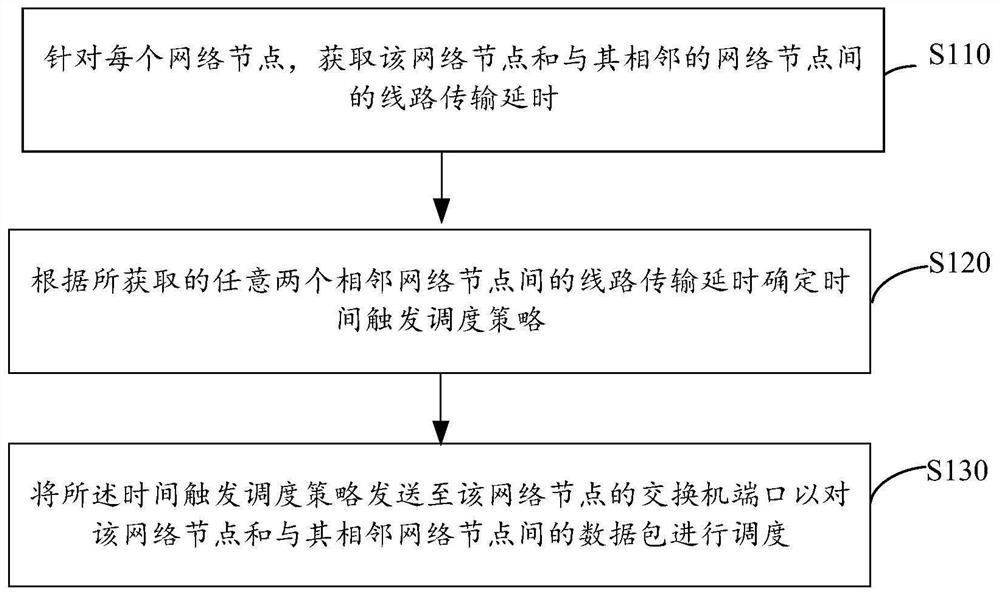

Line length adaptive time trigger scheduling method and device thereof

ActiveCN111464420AMeet the delay requirementsMeet real-time network needsData switching networksComputer networkEngineering

The invention discloses a line length self-adaptive time trigger scheduling method and a device thereof. The method comprises the steps that for each network node, line transmission delay between thenetwork node and the adjacent network node is obtained, and the total line delay between any two adjacent network nodes in a deployed network is smaller than a preset line transmission delay thresholdvalue; a time triggering scheduling strategy is determined according to the acquired line transmission delay between any two adjacent network nodes; and the time-triggered scheduling strategy is sentto a switch port of the network node so as to schedule data packets between the network node and the adjacent network node.

Owner:TSINGHUA UNIV

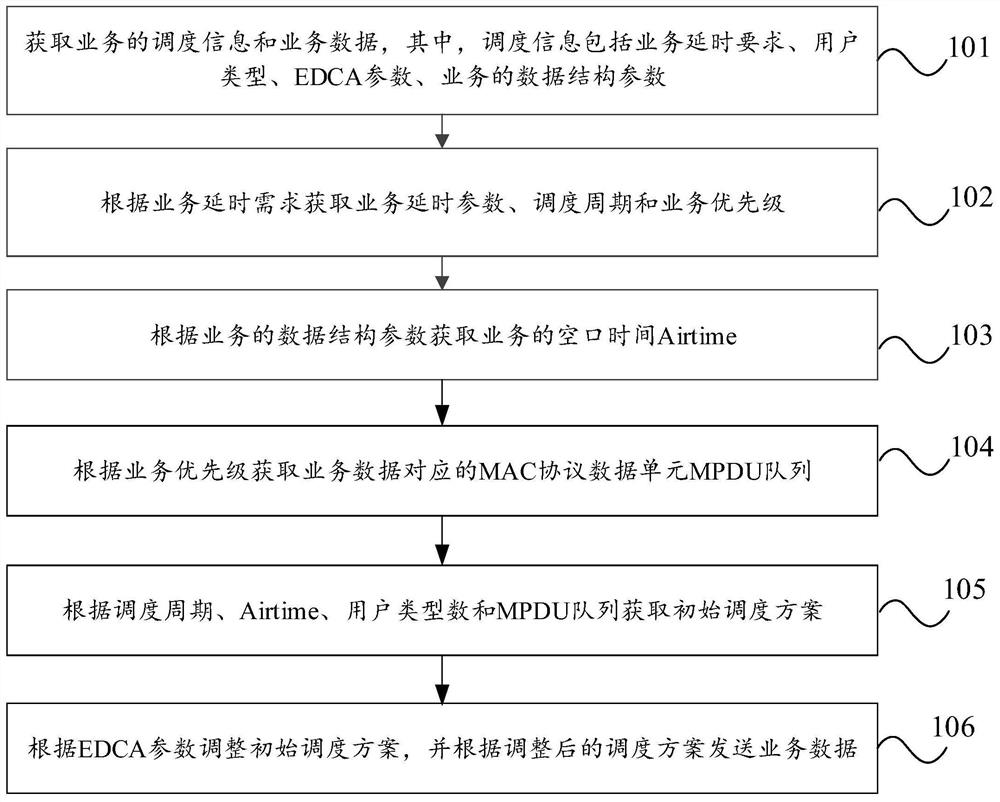

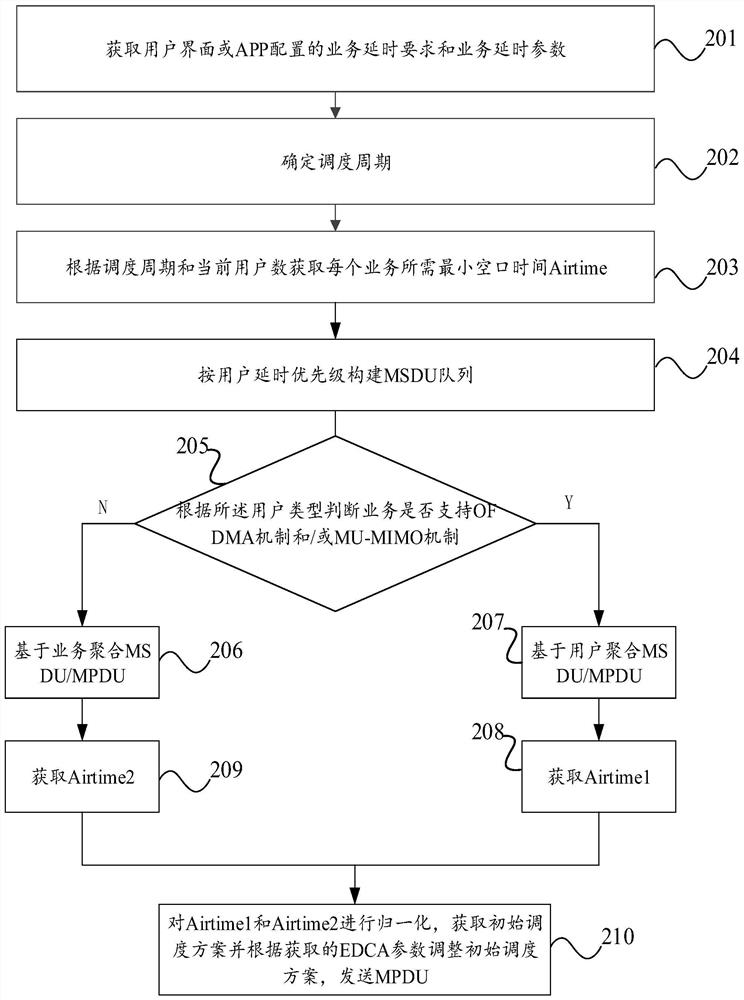

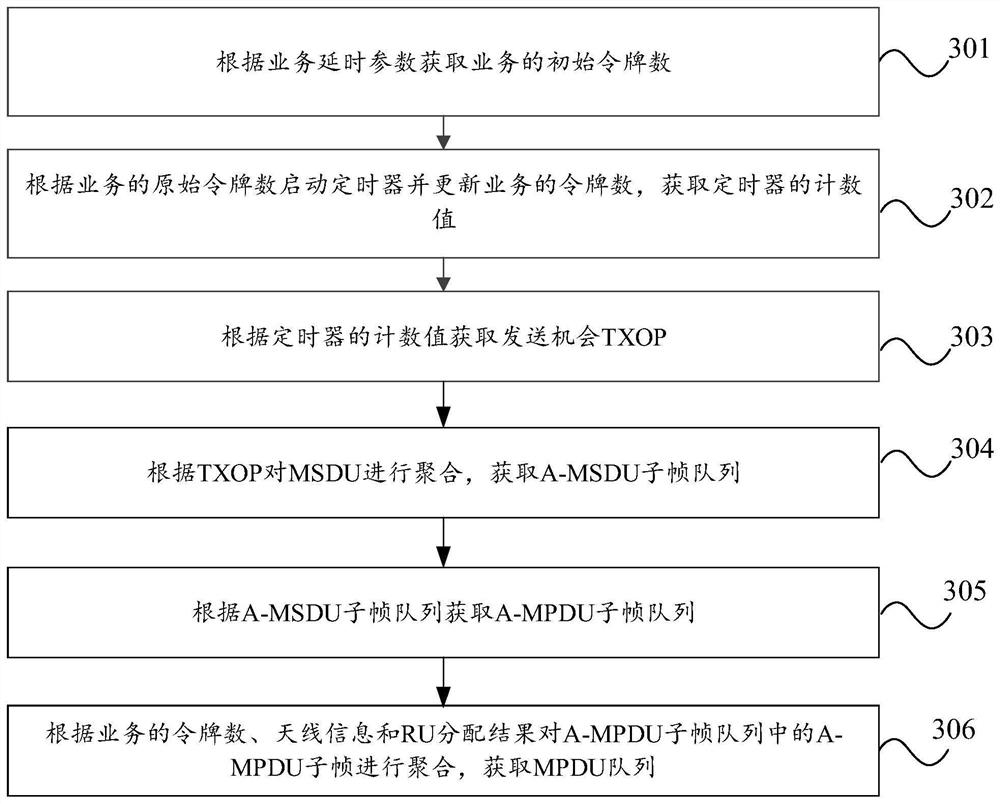

Scheduling method and device and electronic equipment

PendingCN114338558AMeet the delay requirementLow latency requirementTransmissionWireless communicationAir interfaceEngineering

The embodiment of the invention relates to the field of communication, in particular to a scheduling method and device and electronic equipment. The scheduling method comprises: obtaining scheduling information and service data of a service, the scheduling information comprising a service delay requirement, a user type, an EDCA parameter, and a data structure parameter of the service; obtaining a service delay parameter, a scheduling period and a service priority according to the service delay demand; according to the data structure parameter of the service, acquiring air interface time of the service; obtaining an MAC protocol data unit MPDU queue corresponding to the service data according to the service priority; obtaining an initial scheduling scheme according to the scheduling period, the Airtime, the number of user types and the MPDU queue; and adjusting the initial scheduling scheme according to the EDCA parameter, and sending the service data according to the adjusted scheduling scheme. The method is applied to a wireless local area network, and the purpose of meeting the low-delay requirement of a user is achieved.

Owner:ZTE CORP

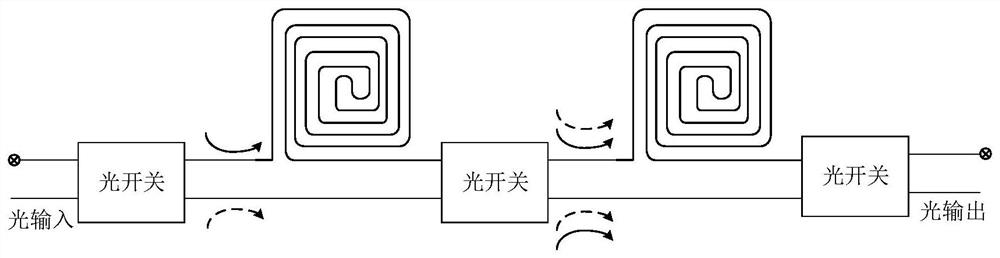

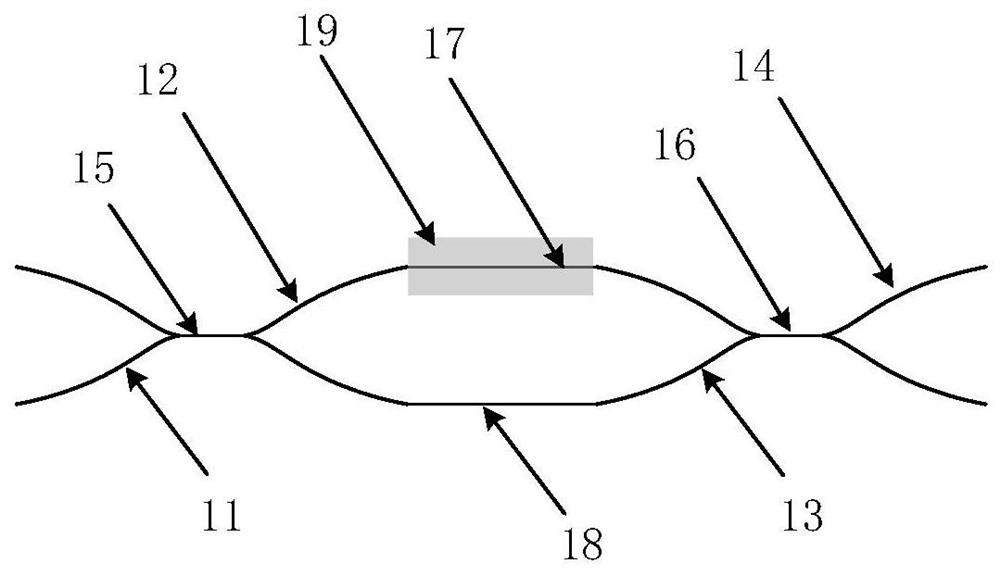

High extinction ratio light delay regulation and control structure and device

PendingCN111913330ARealize regulationEffective filteringNon-linear opticsSignal lightLight extinction

The invention discloses a high extinction ratio optical delay regulation and control structure, which comprises an input optical switch, a first optical waveguide delay line, a first optical waveguidestraight line, a high extinction ratio optical switch, a second optical waveguide delay line, a second optical waveguide straight line and an output optical switch; the high extinction ratio opticalswitch comprises two mach-zehnder optical switches; and one output end of the first Mach-Zehnder optical switch is connected with one input end of the second Mach-Zehnder optical switch. According tothe invention, the optical waveguide delay line and the optical waveguide straight-through line are connected in series by adopting the double Mach-Zehnder optical switches, the first Mach-Zehnder optical switch enables signal light and leakage light in an optical path to be transmitted separately, then the leakage light in the optical path is effectively filtered, and the second Mach-Zehnder optical switch controls the transmission path selection of the optical path. Regulation and control of an optical path are achieved, so that the extinction ratio in an optical link is improved, and the noise in the optical link is reduced.

Owner:THE 44TH INST OF CHINA ELECTRONICS TECH GROUP CORP

Method and apparatus for controlling timing of feedback transmission

ActiveCN108028729BFlexible Retransmission Feedback TimingAchieve short latencyError prevention/detection by using return channelTelecommunications linkEngineering

A method is disclosed for controlling the timing of feedback transmissions by a communications device (80) communicating over a communications link (70), wherein the communications link supports a retransmission mechanism. The method comprises sending (42) a Feedback Timing Indicator FTI, wherein the indicator is selected from a group of indicators.

Owner:TELEFON AB LM ERICSSON (PUBL)

Line length adaptive time trigger scheduling method and device

ActiveCN111464420BMeet the delay requirementsMeet real-time network needsData switching networksComputer networkEngineering

The present invention discloses a line length adaptive time-triggered scheduling method and device, wherein the method includes: for each network node, acquiring the line transmission delay between the network node and its adjacent network nodes, wherein the deployed The total line delay between any two adjacent network nodes in the network is less than the preset line transmission delay threshold; determine the time-triggered scheduling strategy according to the obtained line transmission delay between any two adjacent network nodes; The time-triggered scheduling policy is sent to the switch port of the network node to schedule data packets between the network node and its adjacent network nodes.

Owner:TSINGHUA UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com