Patents

Literature

163results about How to "Satisfy latency requirements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

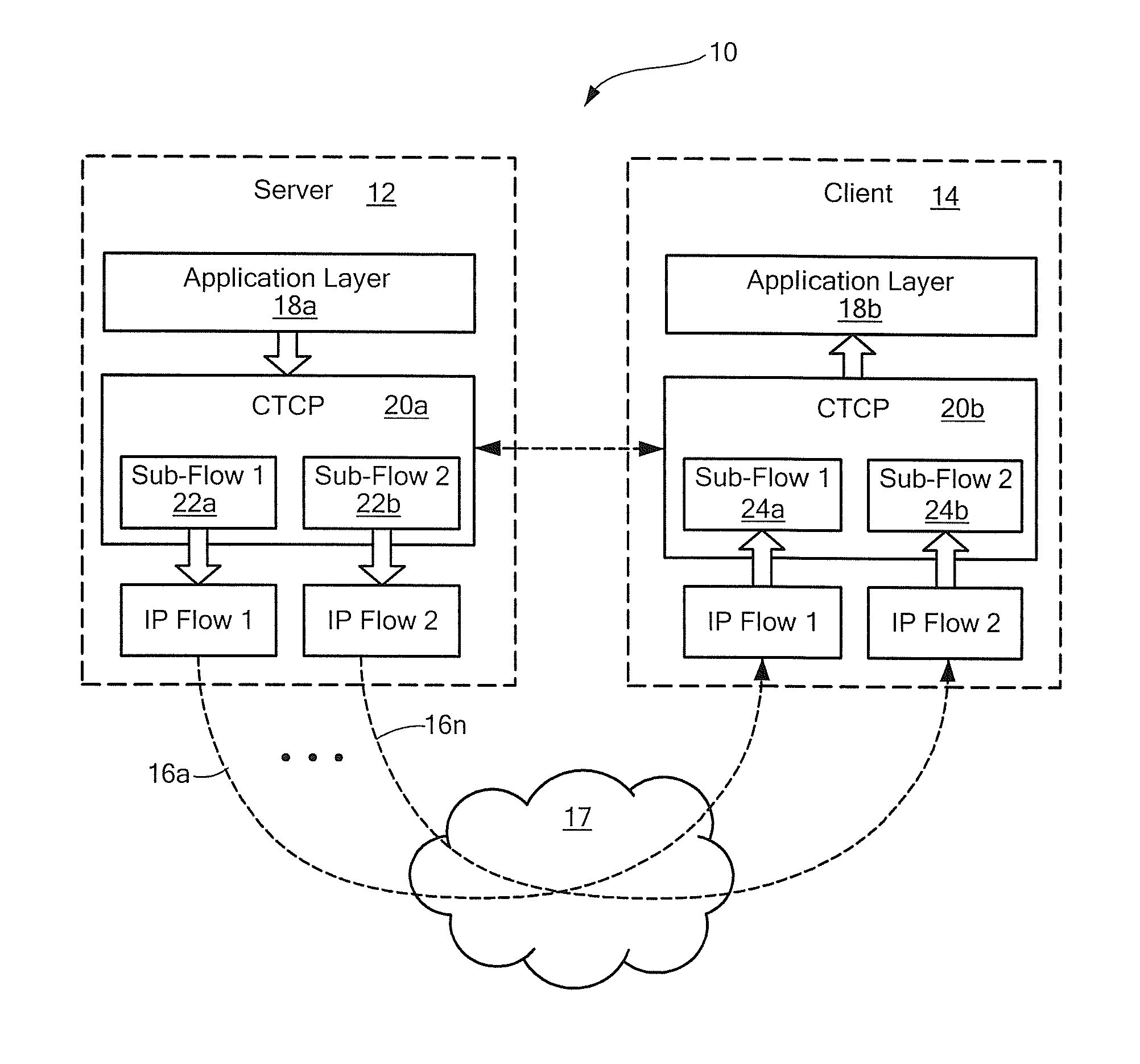

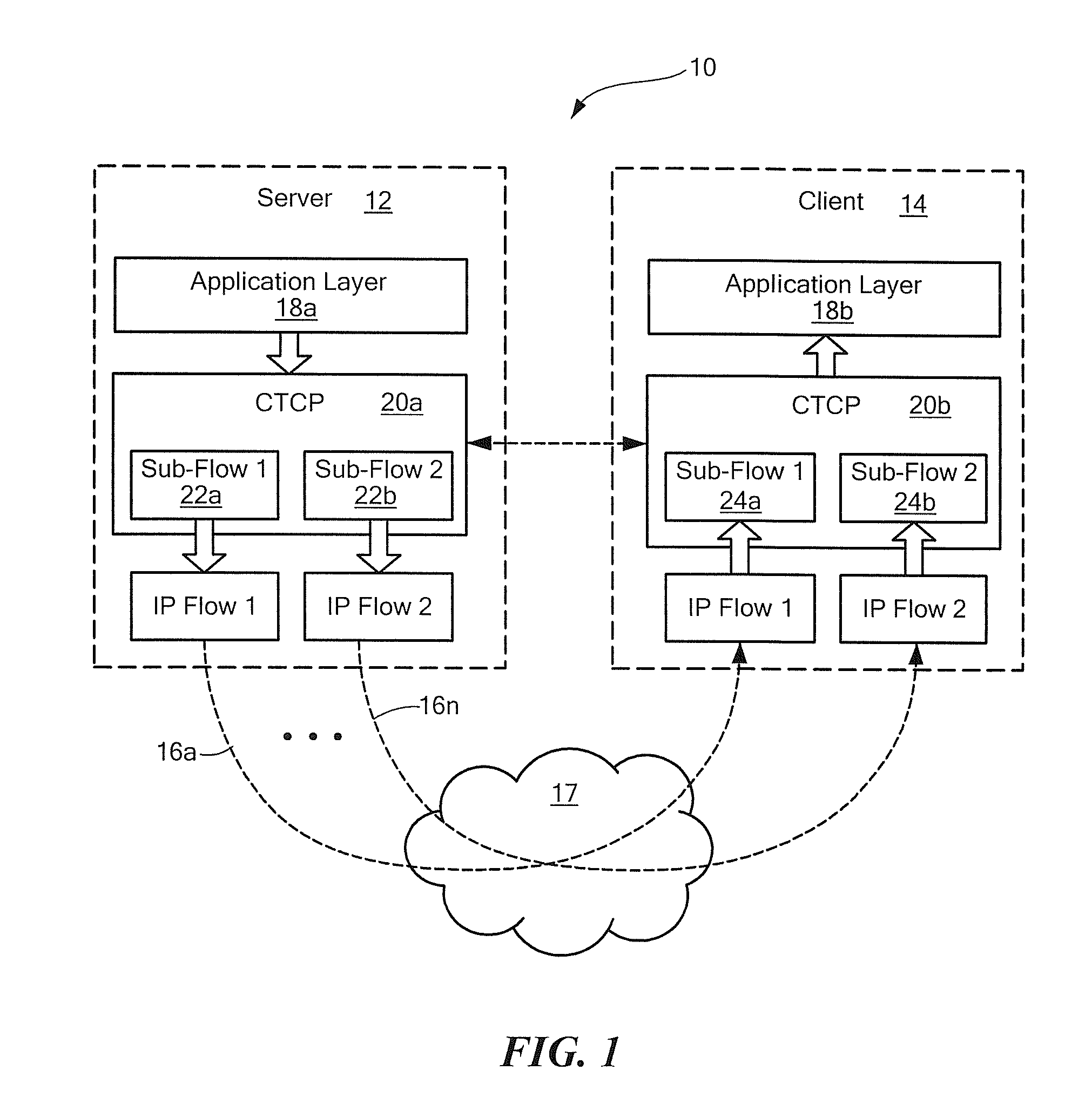

Coding Approach For A Robust And Flexible Communication Protocol

ActiveUS20130114481A1Easy to implementEffective serviceNetwork traffic/resource managementAssess restrictionTransmission protocolNetwork Communication Protocols

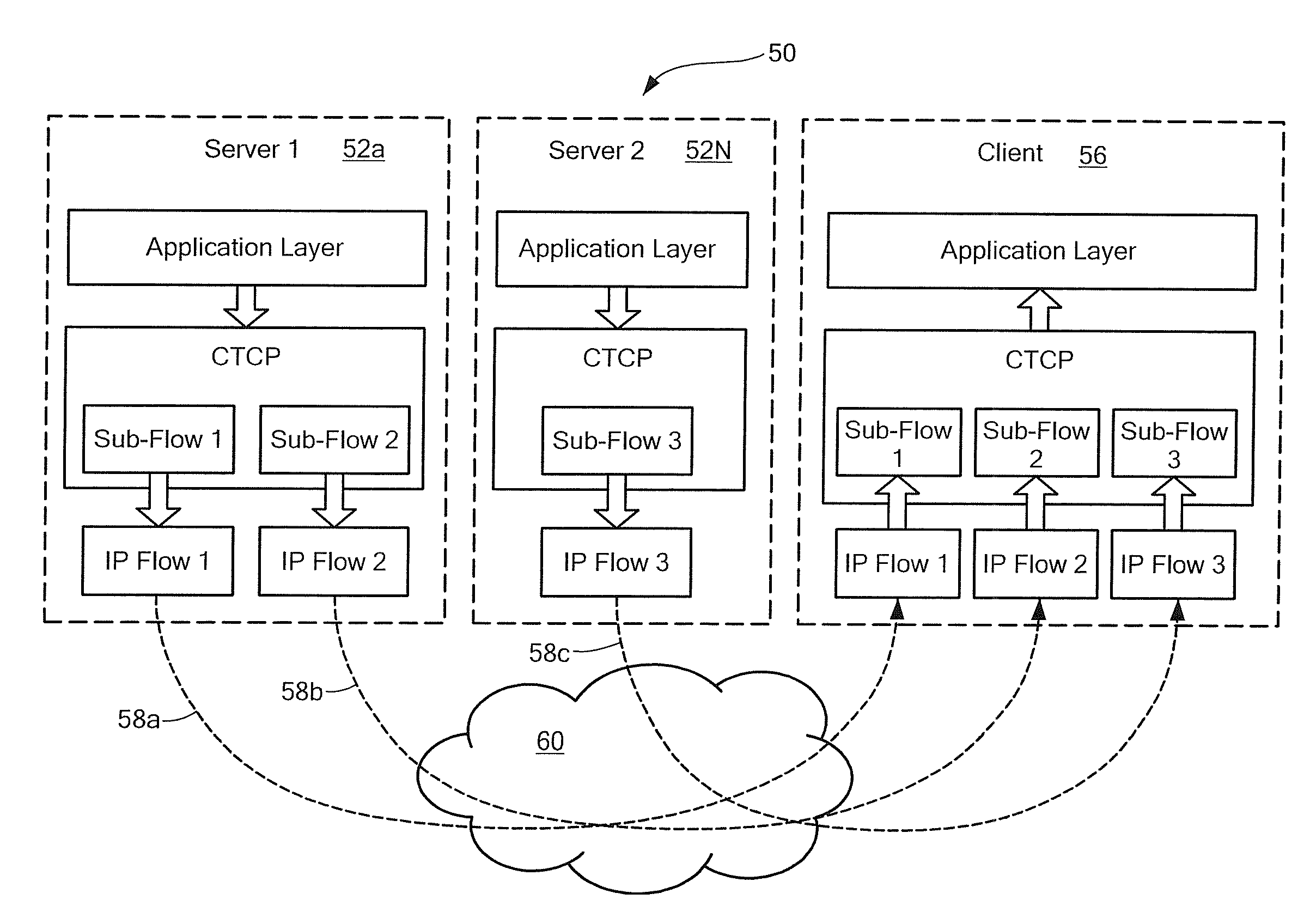

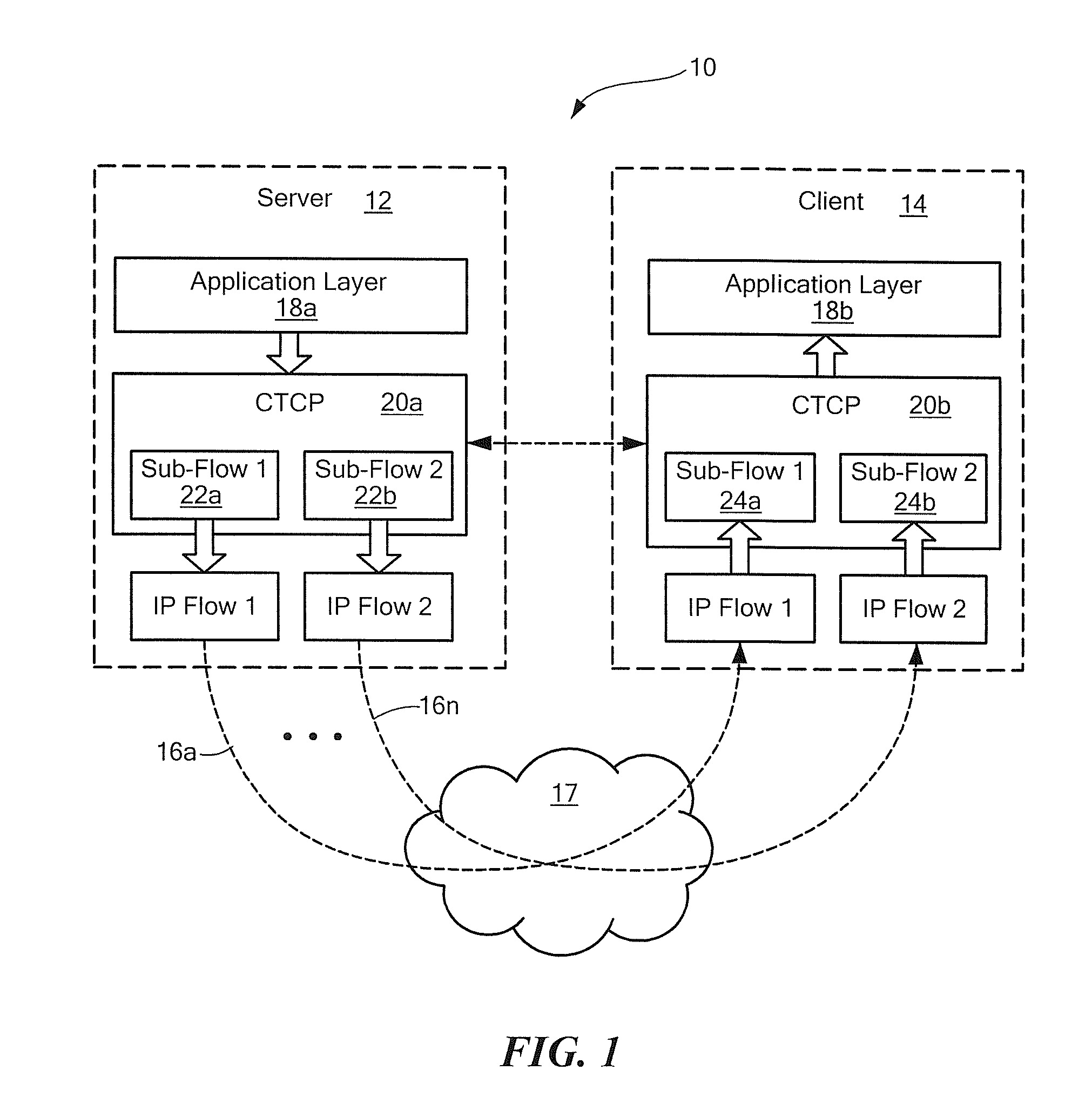

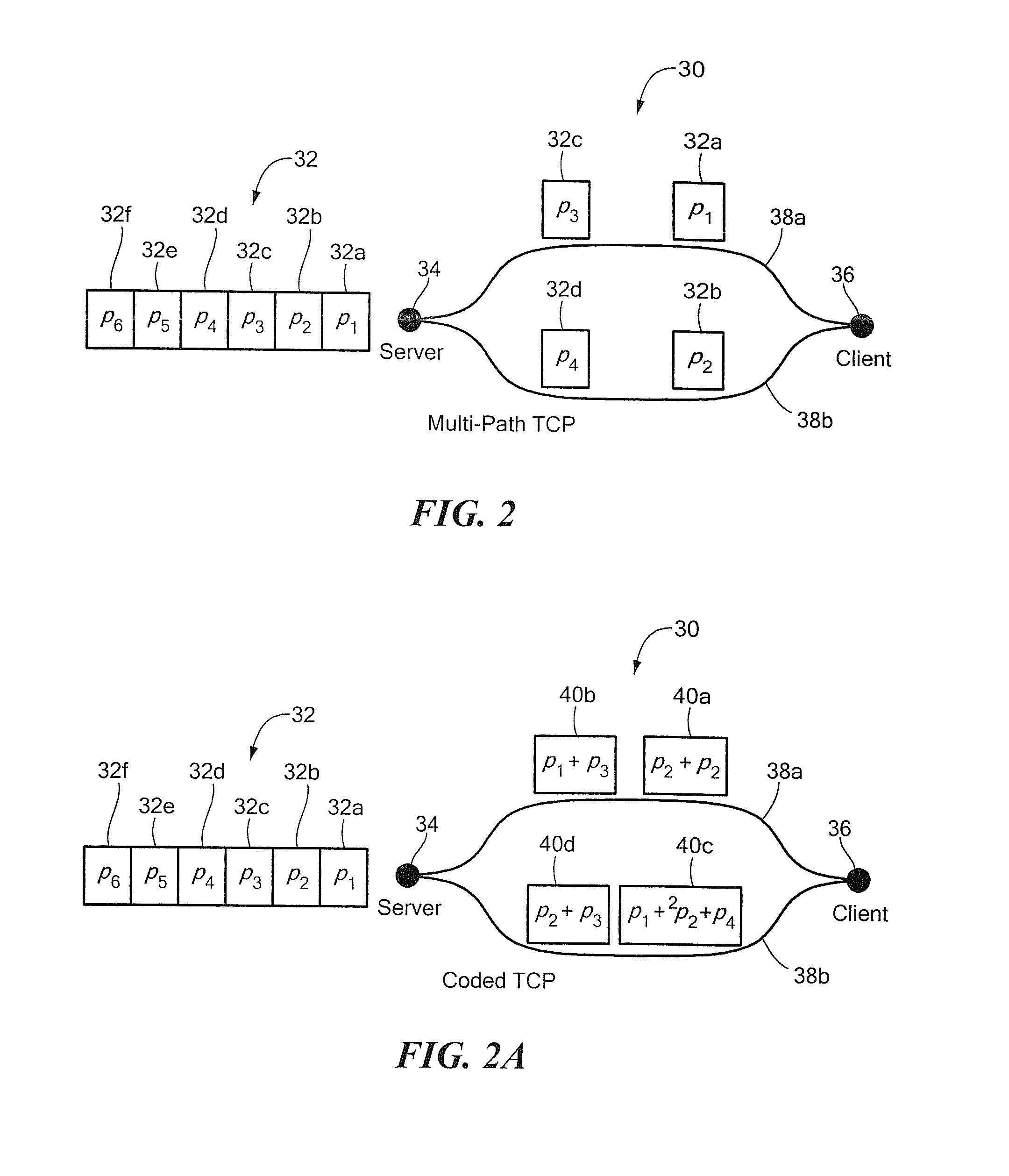

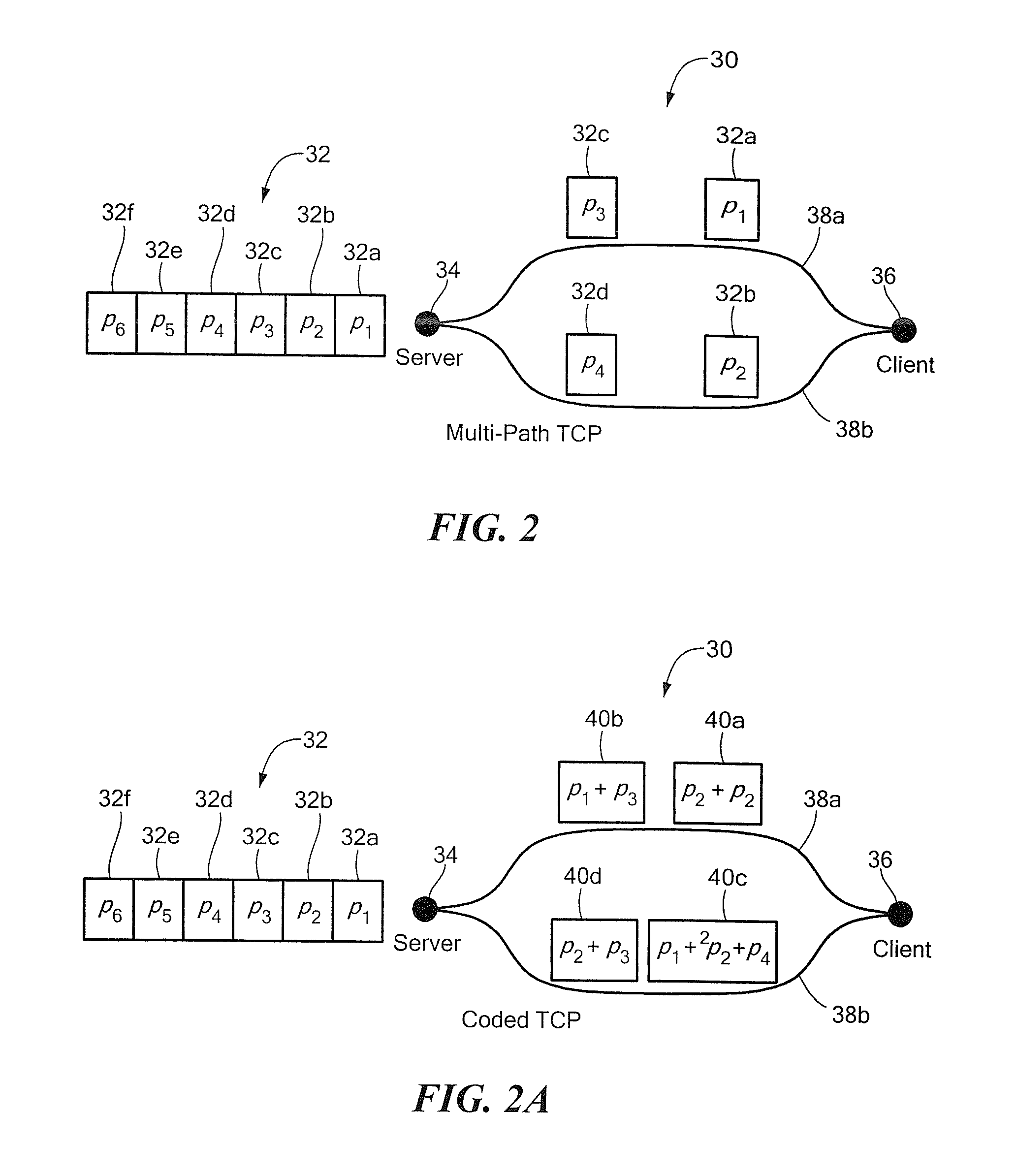

A coding approach for a robust and flexible network communication protocol is described. By using coding, it is possible to eliminate the need to track packet identities, and hence, it is possible to reduce coordination overhead associated with many conventional protocols. The method and system described herein takes advantage of multiple paths, interfaces, mediums, servers, and storage locations available in a network. The proposed protocol allows quick response to congestion by load balancing over different network resources. The method also enables soft vertical hand-overs across heterogeneous networks. In one embodiment, a media file is divided into chunks and transmitted using a transport protocol tailored to meet delay requirements of media streaming applications. Also described are different coding strategies for chunk delivery based upon an urgency level of each chunk.

Owner:MASSACHUSETTS INST OF TECH

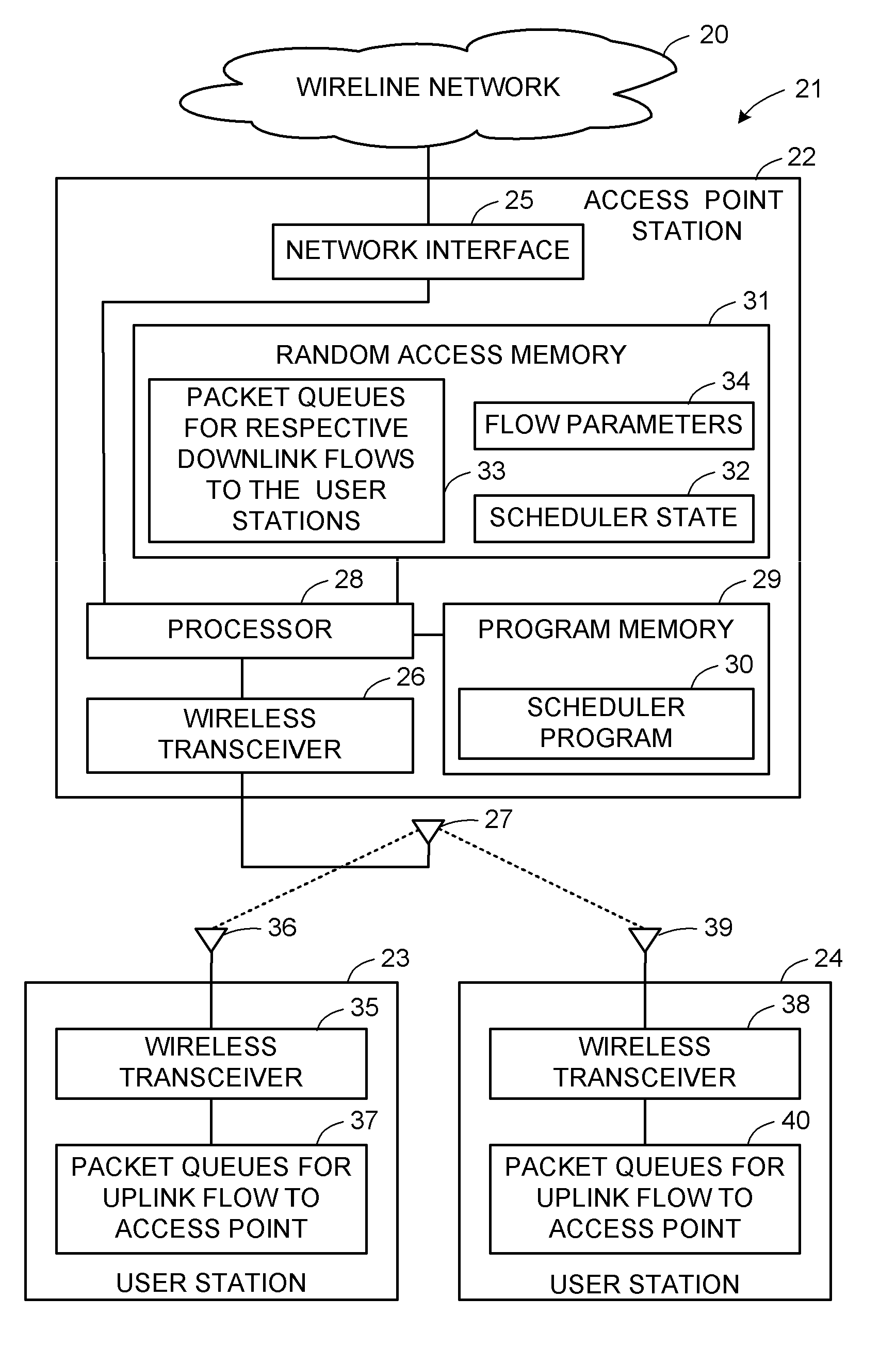

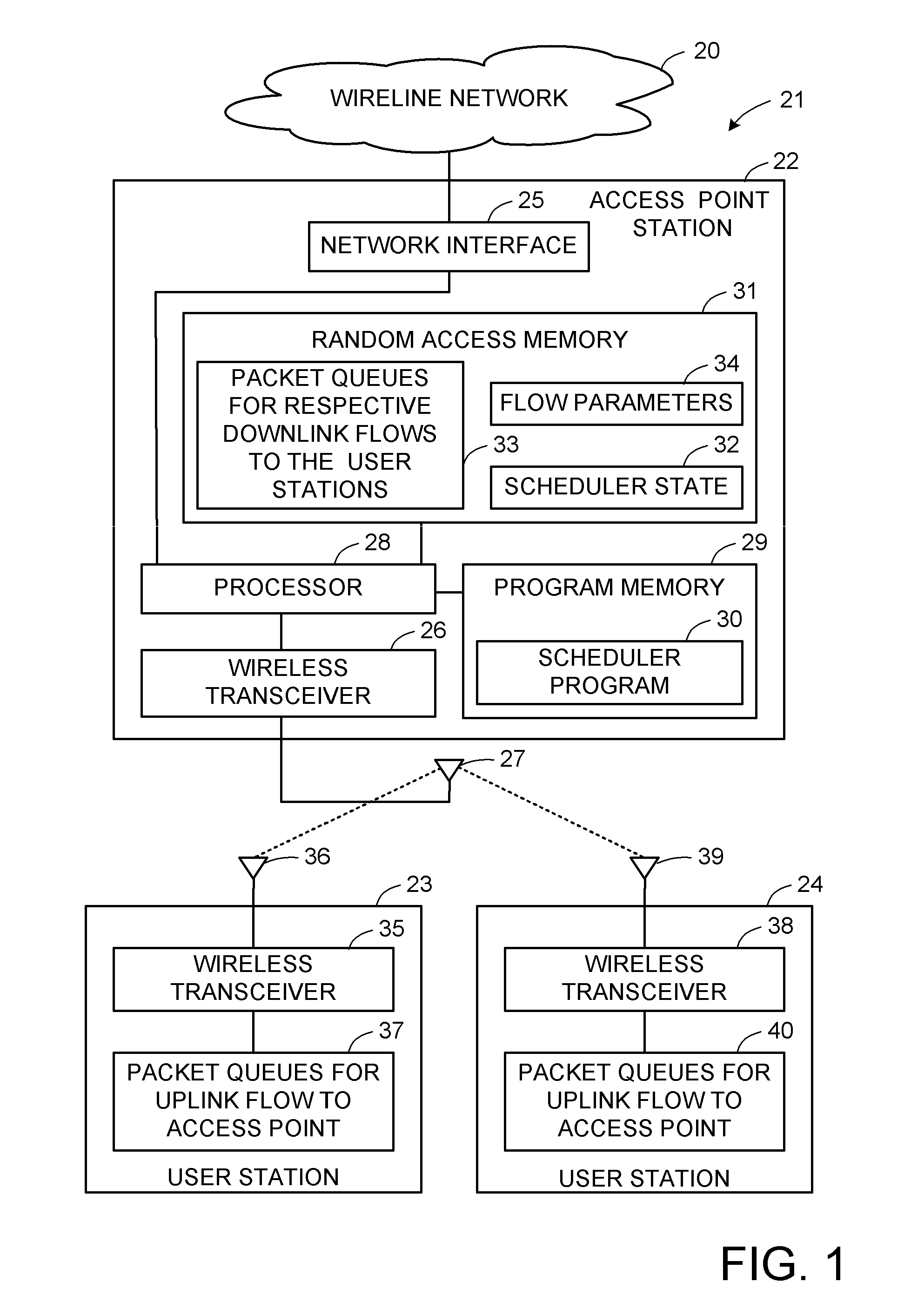

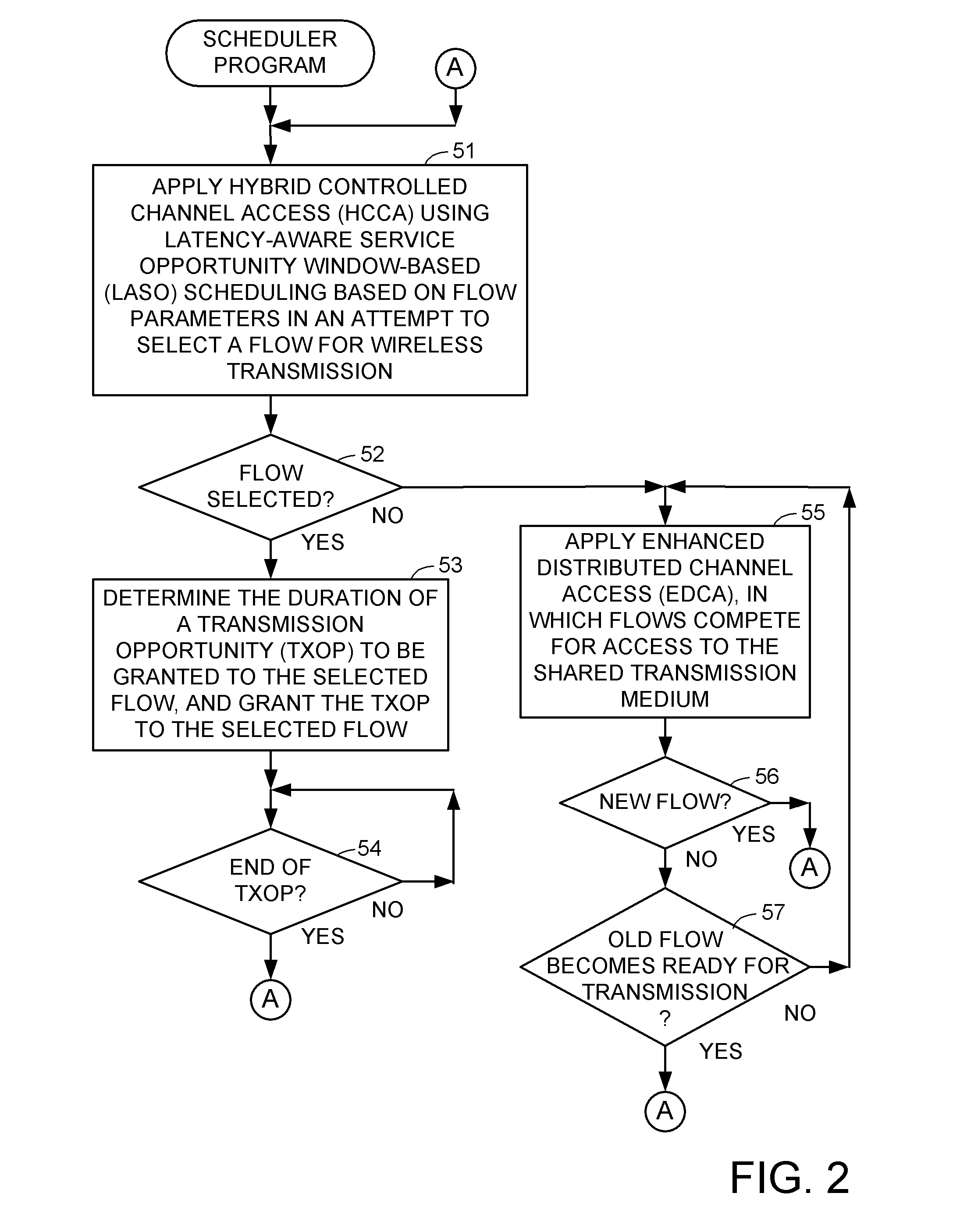

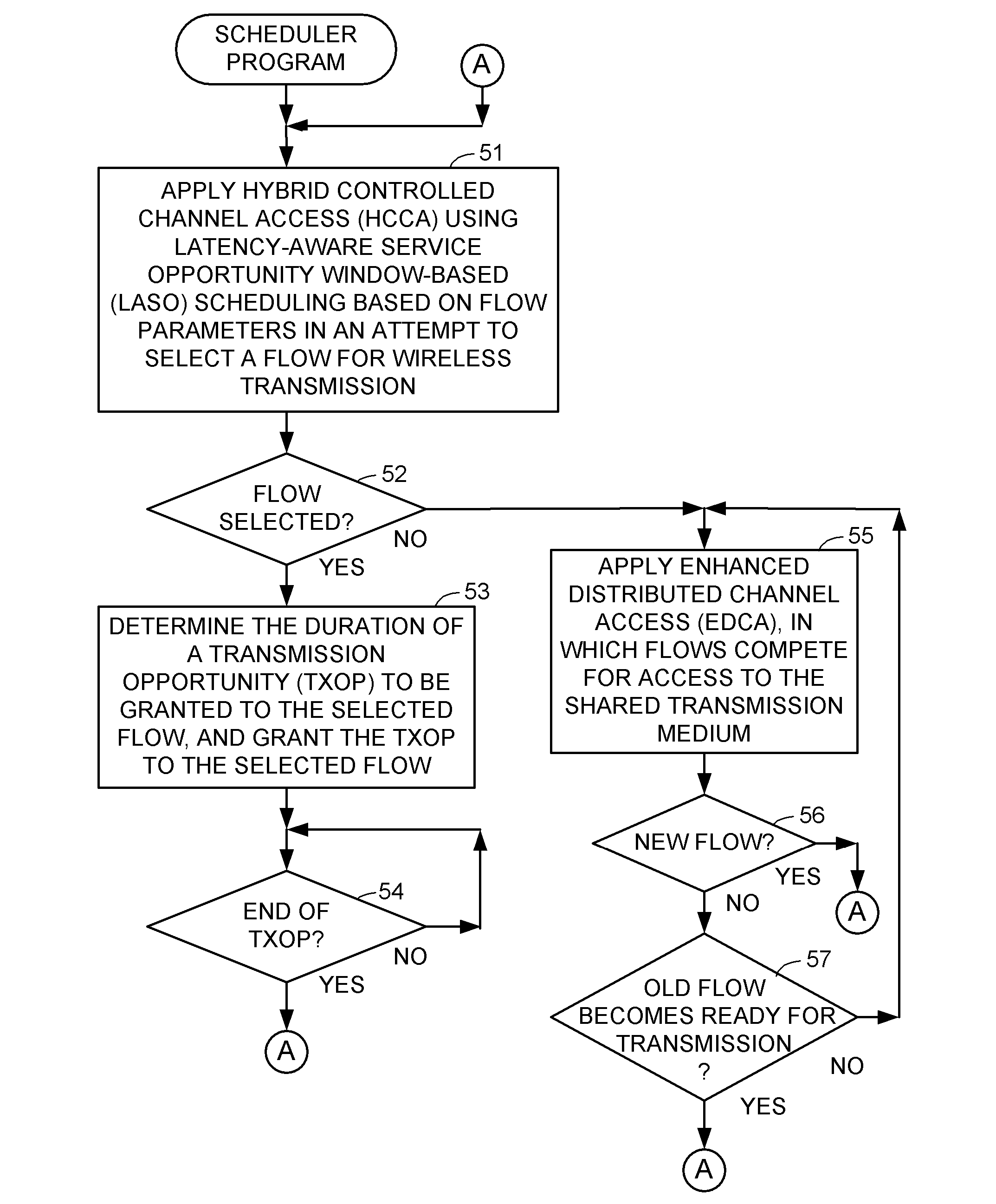

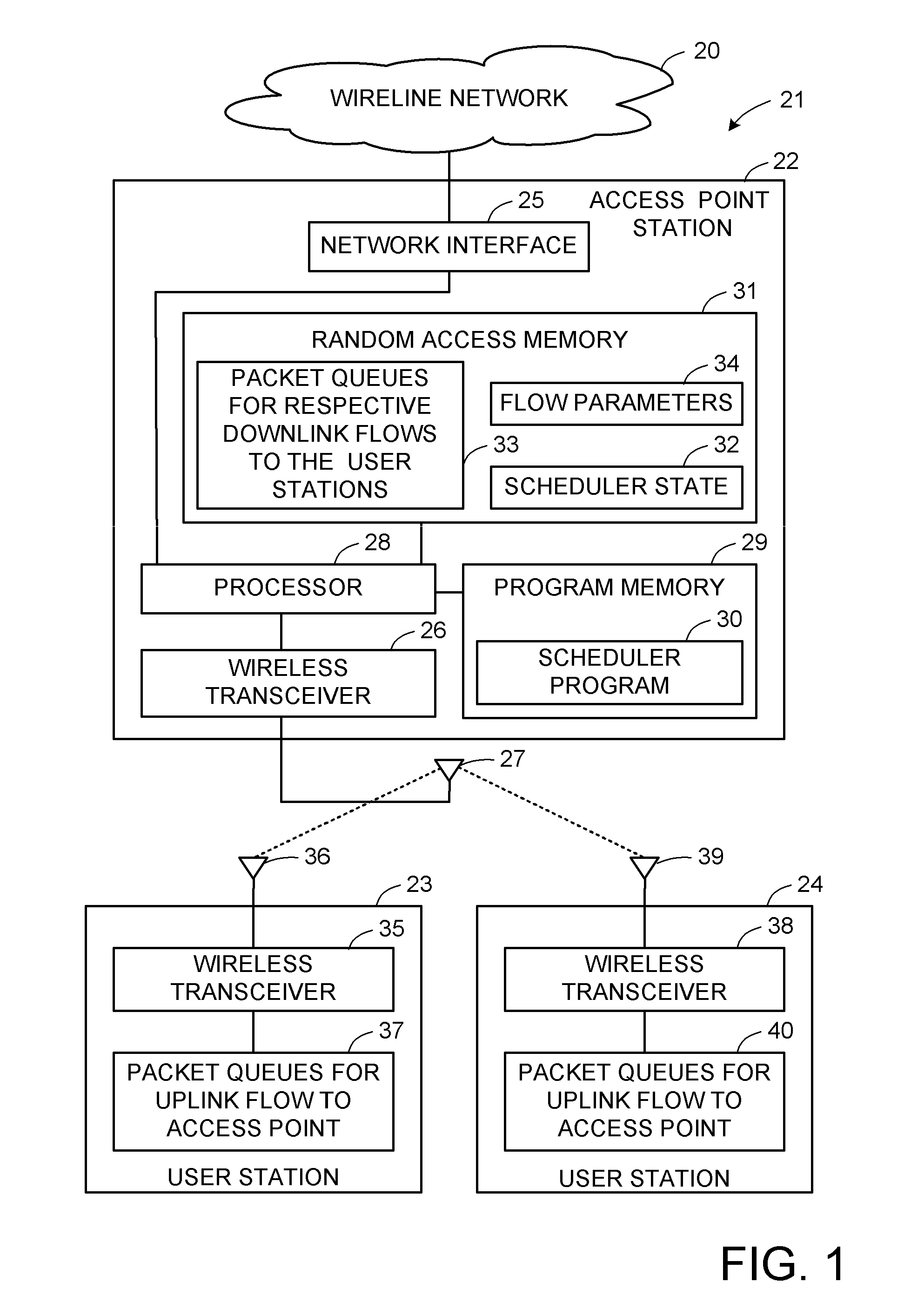

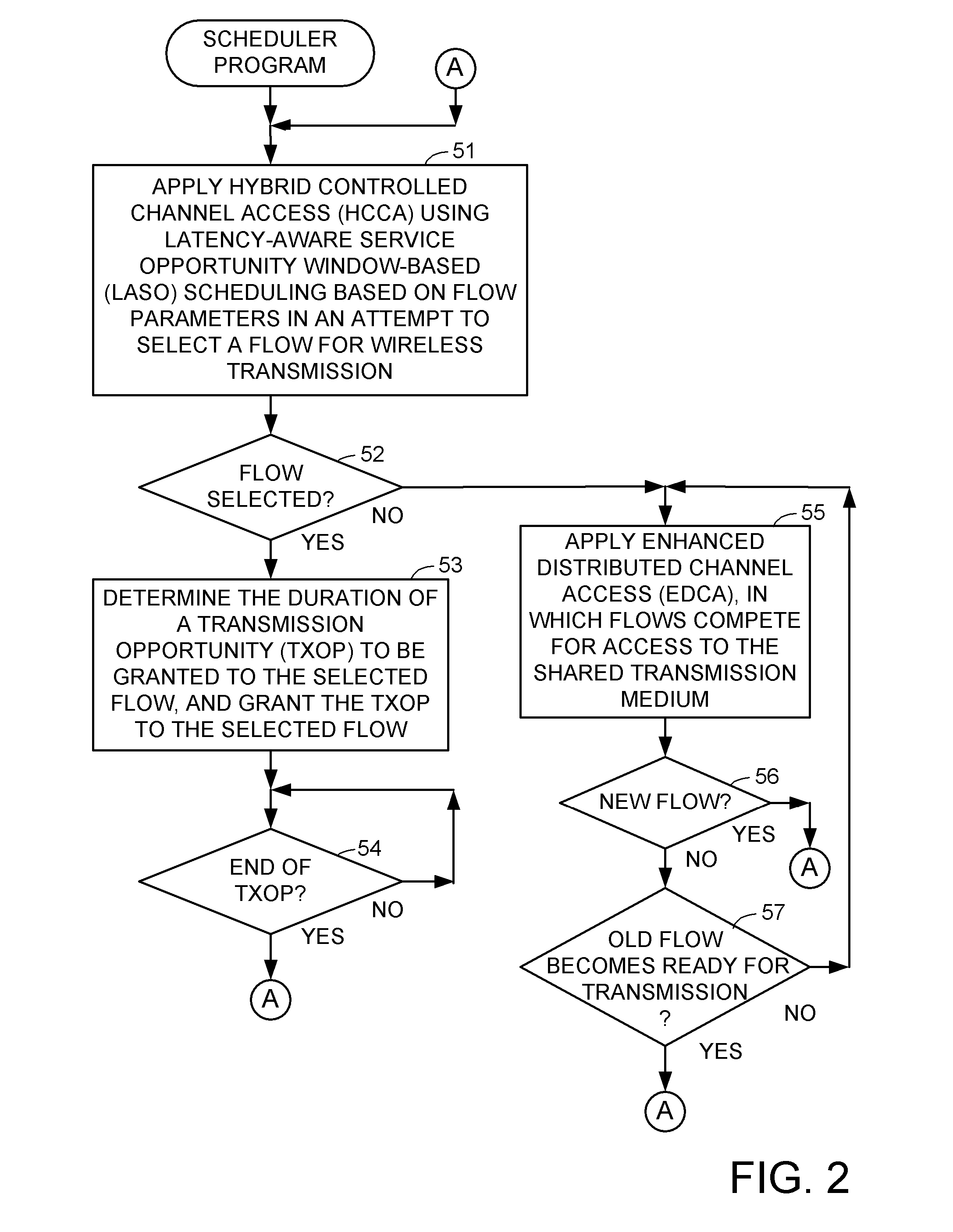

Latency-aware service opportunity window-based (LASO) scheduling

ActiveUS20070036116A1Maximize amount of time providedMeet the delay requirementsNetwork traffic/resource managementRadio/inductive link selection arrangementsData packControl channel

Traffic flows of data packets from respective packet queues in wireless stations to a shared transmission medium of a wireless network are scheduled in accordance with Hybrid Controlled Channel Access (HCCA) and Enhanced Distributed Channel Access (EDCA). HCCA is applied by eliminating from consideration for HCCA access flows for which the sum of a desired minimum age of an oldest data packet in the respective packet queue and the time of creation of the oldest data packet is greater than the present time. For flows that are not eliminated from consideration, HCCA access is granted to the flow having a smallest sum of the desired maximum age of the oldest data packet and the time of creation of the oldest data packet. When all traffic flows are eliminated from consideration for HCCA access, EDCA is applied so that traffic flows compete for access to the medium.

Owner:TELCORDIA TECHNOLOGIES INC +2

Coding approach for a robust and flexible communication protocol

ActiveUS8780693B2Reduce overheadEliminate needError preventionFrequency-division multiplex detailsNetwork Communication ProtocolsVertical handover

A coding approach for a robust and flexible network communication protocol is described. By using coding, it is possible to eliminate the need to track packet identities, and hence, it is possible to reduce coordination overhead associated with many conventional protocols. The method and system described herein takes advantage of multiple paths, interfaces, mediums, servers, and storage locations available in a network. The proposed protocol allows quick response to congestion by load balancing over different network resources. The method also enables soft vertical hand-overs across heterogeneous networks. In one embodiment, a media file is divided into chunks and transmitted using a transport protocol tailored to meet delay requirements of media streaming applications. Also described are different coding strategies for chunk delivery based upon an urgency level of each chunk.

Owner:MASSACHUSETTS INST OF TECH

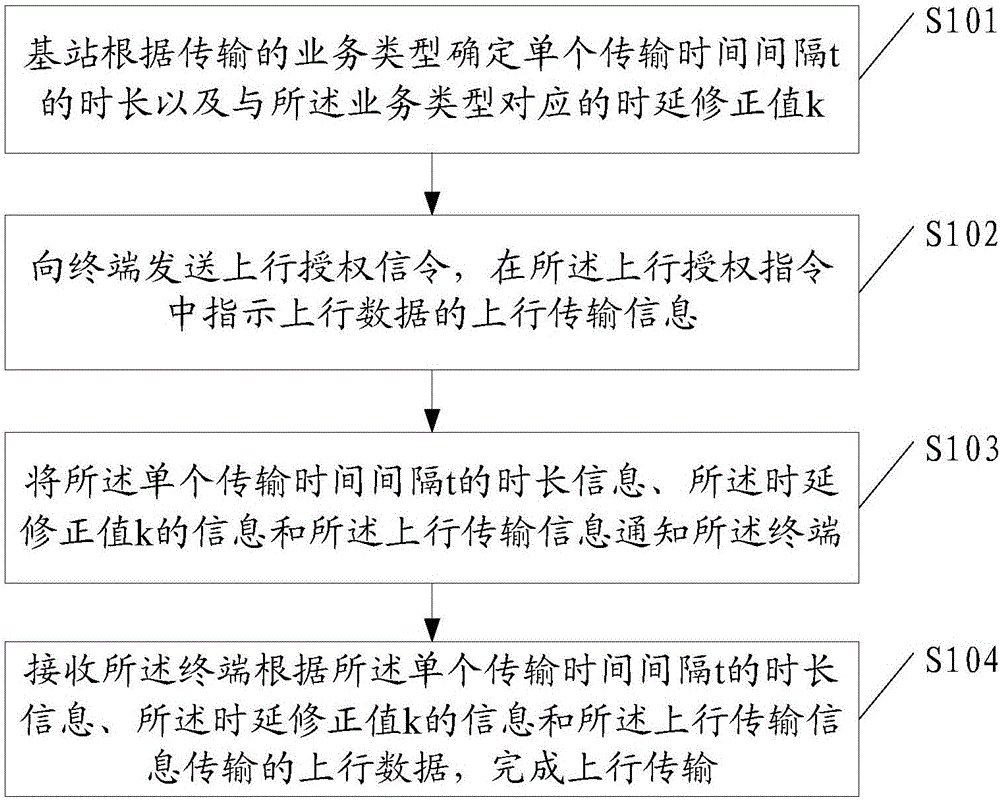

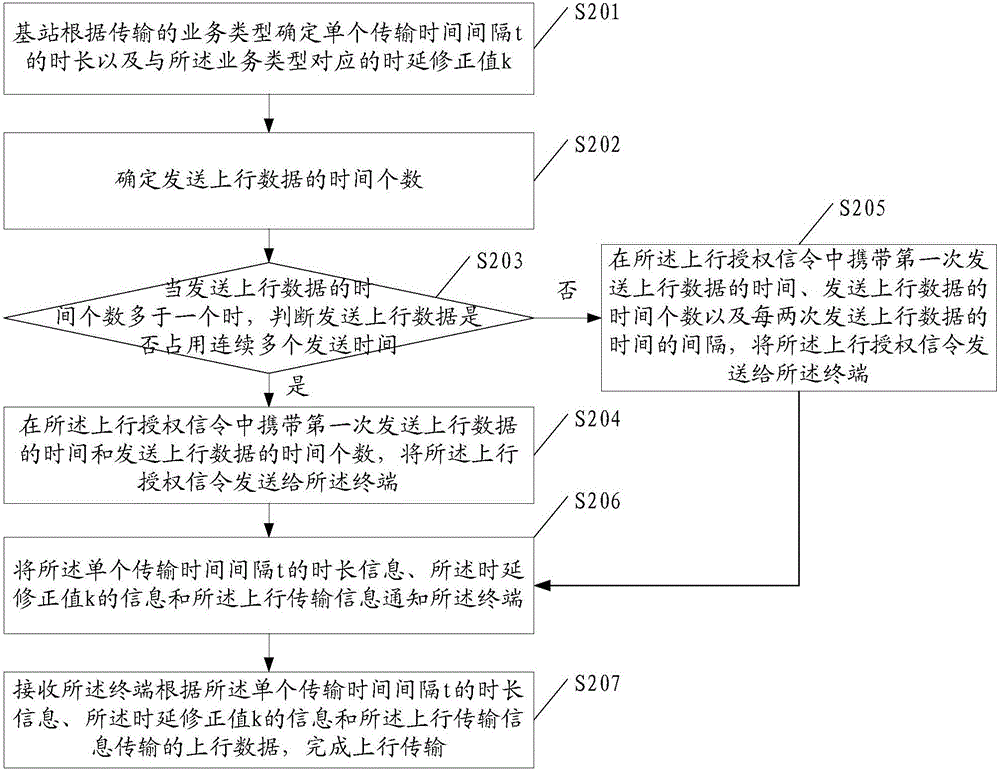

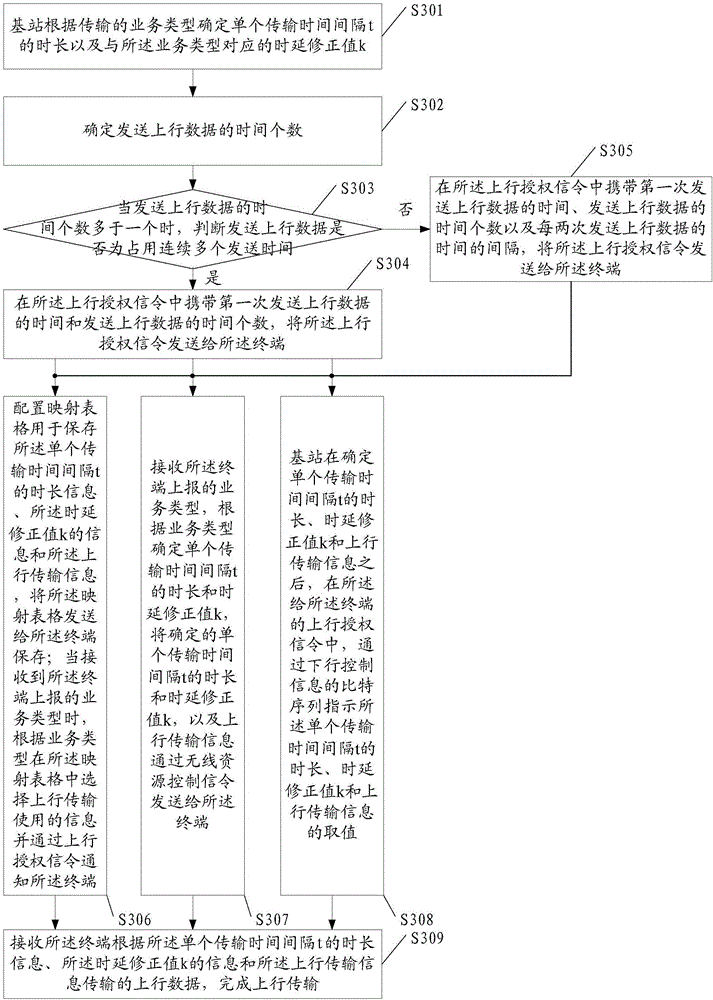

Uplink transmission method and base station

ActiveCN106102180ASatisfy latency requirementsImprove data transmission experienceSynchronisation arrangementTime delaysAuthorization

The embodiment of the invention discloses an uplink transmission method and a base station. The method comprises the steps of determining a time length of a single transmission time interval t and a time delay correction value k corresponding to a business type by the base station according to the transmitted business type; transmitting an uplink authorization signaling to a terminal, and indicating uplink transmission information of uplink data in the uplink authorization signaling, wherein the uplink transmission information comprises the time of transmitting the uplink data for the first time and the number of times of transmitting the uplink data, or the uplink transmission information comprises the time of transmitting the uplink data for the first time, the number of times of transmitting the uplink data, and a time interval of transmitting the uplink data every two times; notifying the terminal of time length information of t, information of k and the uplink transmission information; and receiving the uplink data transmitted by the terminal according to the time length information of t, the information of k and the uplink transmission information, and finishing uplink transmission. By adopting the uplink transmission method and the base station provided by the invention, the base station is facilitated to adjust an uplink scheduling time delay according to the business type, and the diversified demands of 5G business in the future can be satisfied.

Owner:YULONG COMPUTER TELECOMM SCI (SHENZHEN) CO LTD

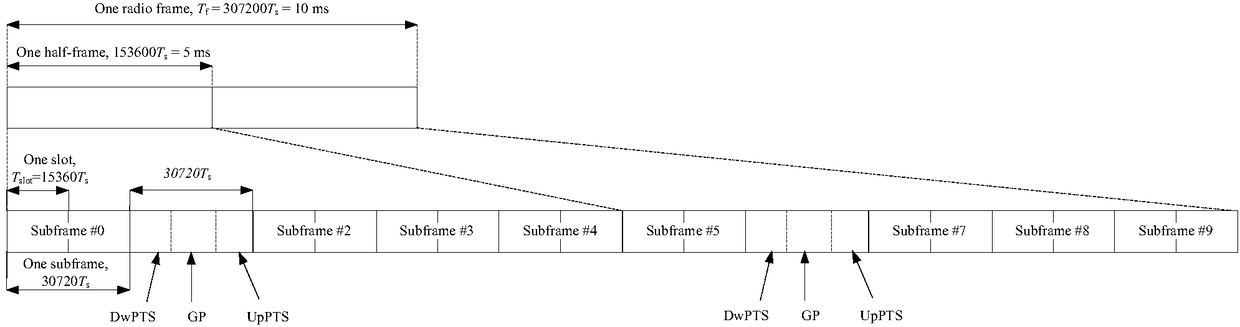

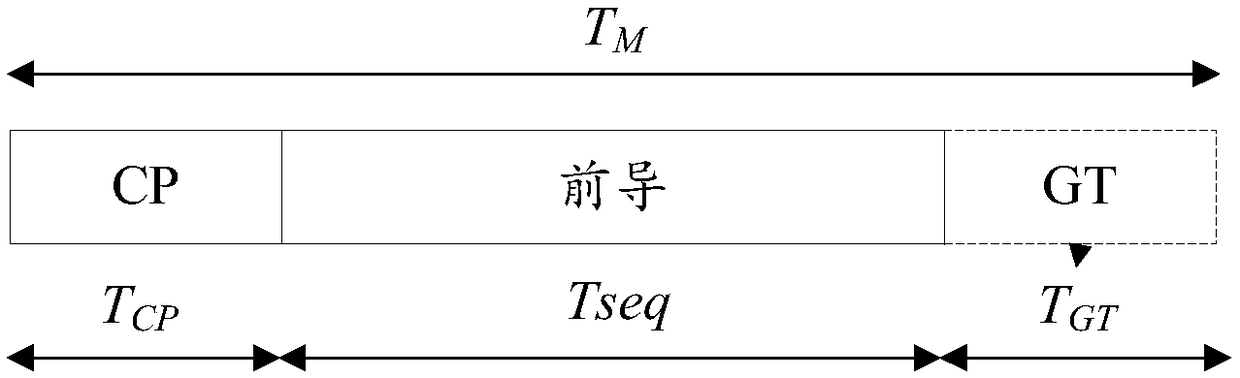

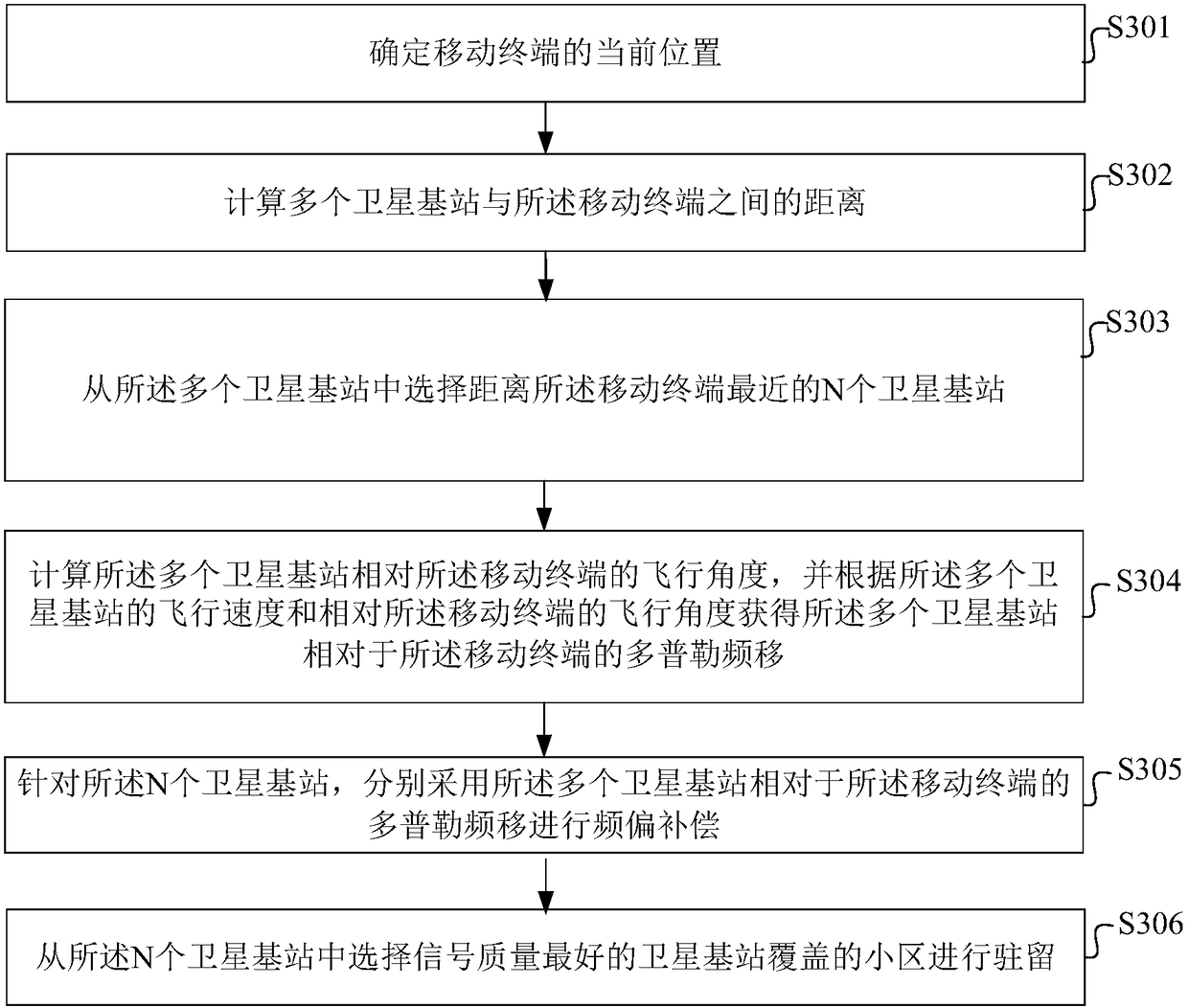

Cell search, cell access method and device in satellite communication

ActiveCN108243391ASatisfy latency requirementsSynchronisation arrangementModulated-carrier systemsPropagation delayAccess method

An embodiment disclosed by the invention relates to a cell search method, a cell access method, a cell search device and a cell access device in satellite communication. The cell search method comprises the steps of calculating distances between a mobile terminal and a plurality of satellite base stations, and calculating Doppler frequency shifts of the plurality of satellite base stations relative to the mobile terminal; selecting, from the plurality of satellite base stations, N satellite base stations which are closest to the mobile terminal; for the N satellite base stations , adopting theDoppler frequency shifts of the plurality of satellite base stations relative to the mobile terminal to perform frequency offset compensation; and selecting cells covered by the satellite base stations with the best signal quality from the N satellite base stations for resident. Correspondingly, the cell access method comprises the steps of: calculating a distance between the mobile terminal anda satellite base station to which a target is accessed; calculating propagation delay according to the distance between the mobile terminal and the satellite base station to which the target is accessed; and bringing forward PRACH according to the propagation delay and the frequency shifts, and performing cell access on the satellite base station to which the target is accessed. According to the cell search method, the cell access method, the cell search device and the cell access device, the application of LTE in satellite communication is realized by adopting an in-advance compensation method.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

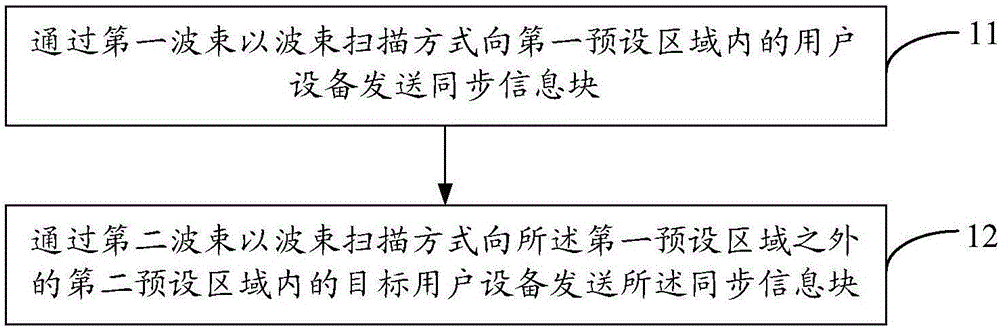

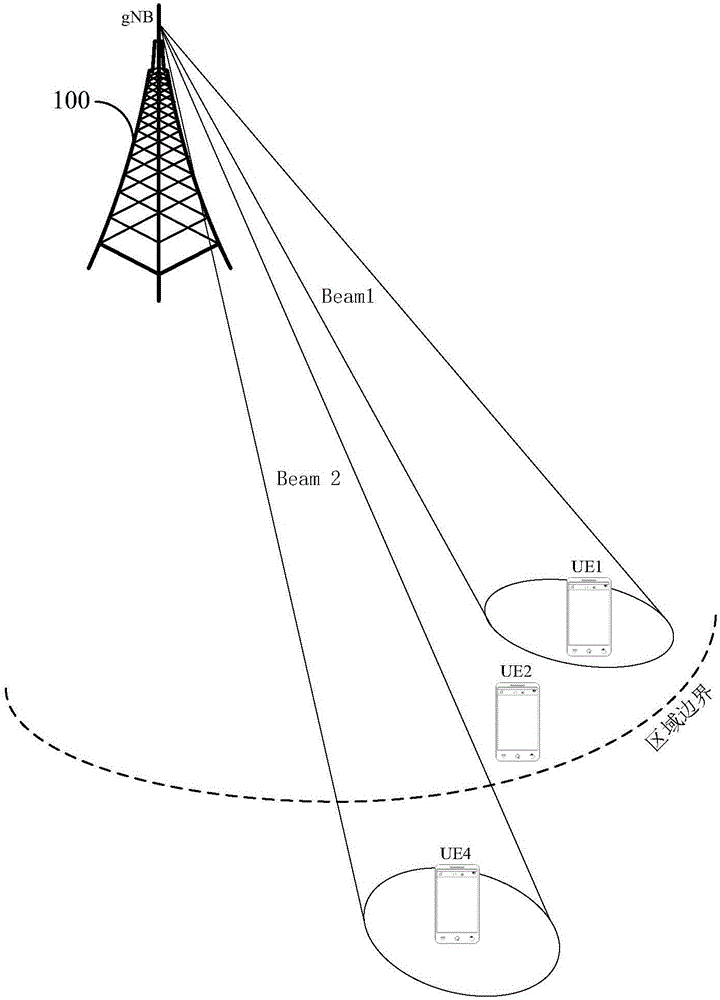

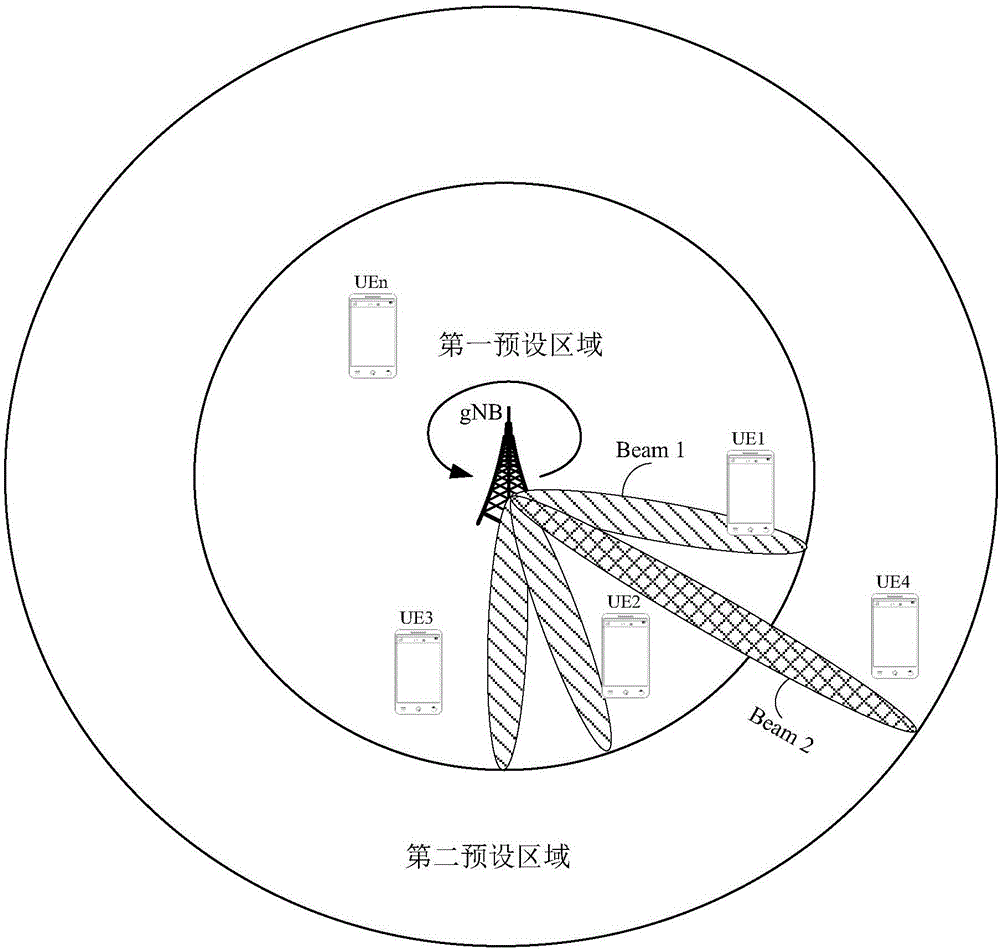

Method and device for sending and acquiring synchronization information block

ActiveCN106793059AImprove terminal coverage performanceSave system power and wireless resourcesSynchronisation arrangementHigh level techniquesSystem informationReal-time computing

This invention provides a method and a device for sending and acquiring synchronization information block. The method for sending the synchronization information block comprises the steps that a synchronization information block is sent to the user equipment within a first preset region through a first beam in the beam scanning mode, the synchronization information block comprises a main auxiliary synchronization signal, and necessary system information; the synchronization information block is sent to the target user equipment within a second preset region outside the first preset region through a second beam in the beam scanning mode; wherein the transmitted power of the second beam is greater than the transmitted power of the first beam; the interval of the second beam scanning cycle is greater than the interval of the first beam scanning cycle. Through the adoption of the method for sending the synchronization information block, under the condition that less time resources are taken up, the performance of the terminal coverage of a system can be improved, and the system power consumption and wireless resources are saved.

Owner:BEIJING XIAOMI MOBILE SOFTWARE CO LTD

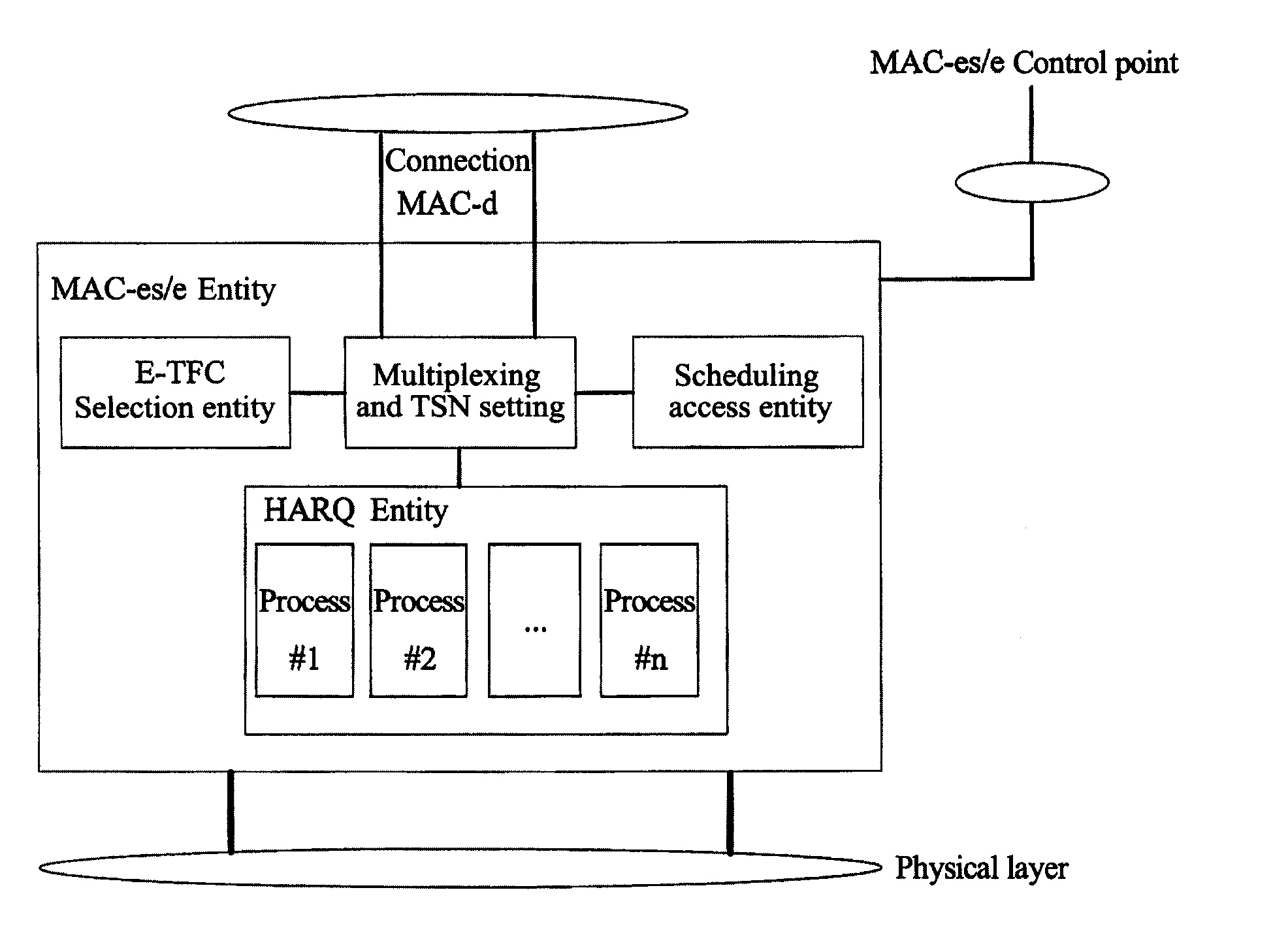

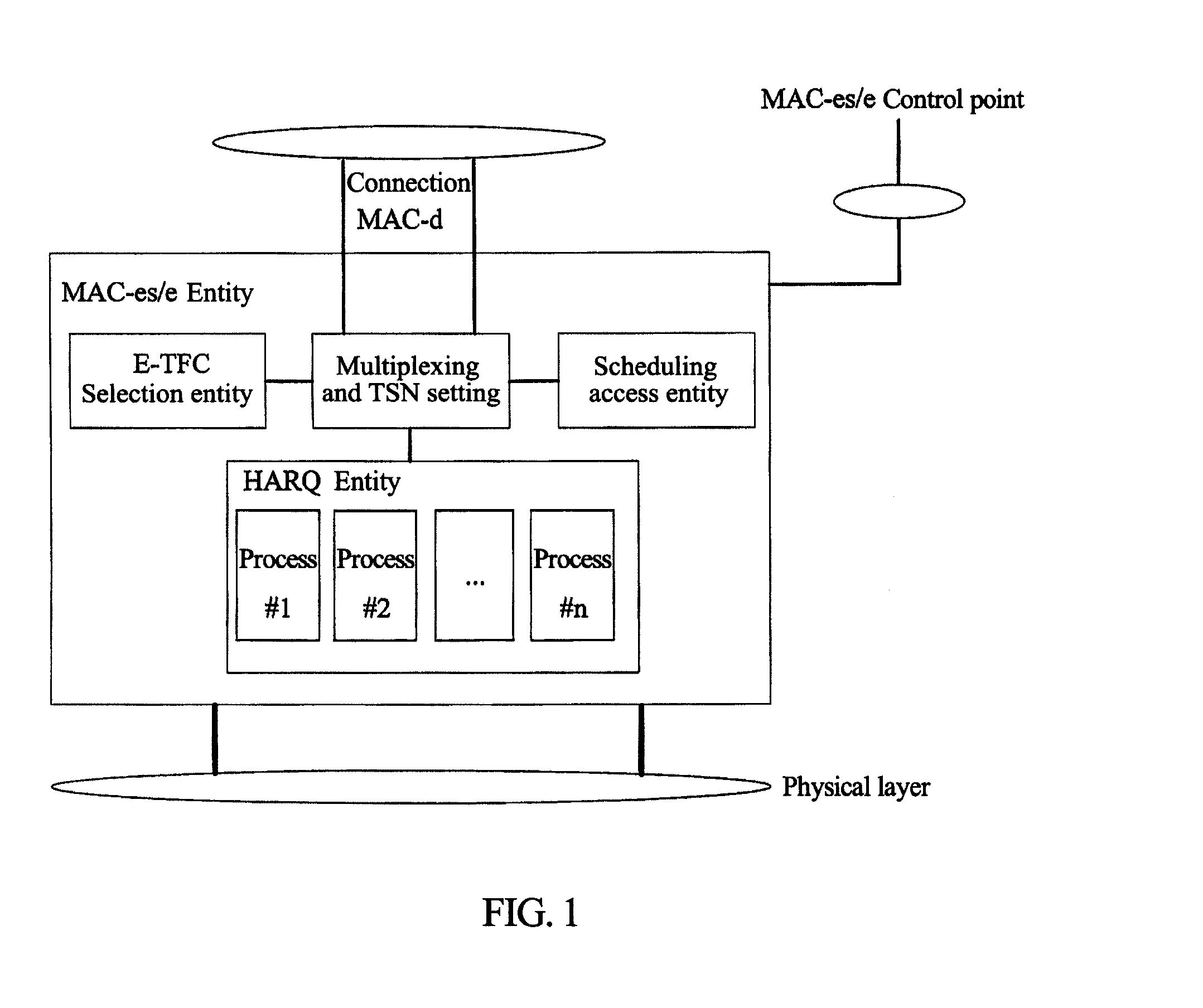

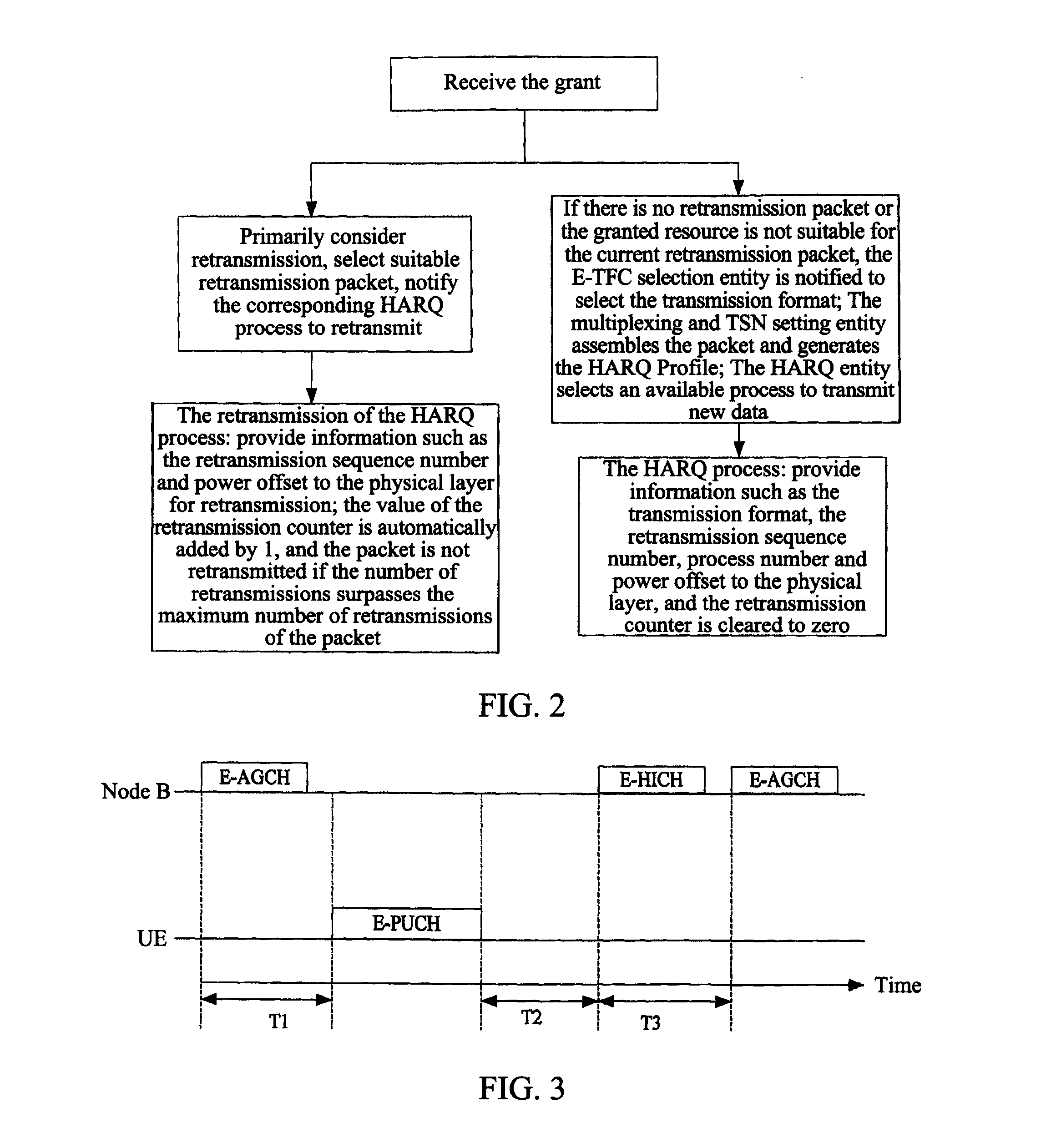

Repeat control method in enhanced uplink asynchronous hybrid automatic repeat request

ActiveUS20110134829A1Satisfy latency requirementsAvoid retransmissionError prevention/detection by using return channelFrequency-division multiplex detailsTelecommunicationsMediaFLO

A repeat control method in the enhanced uplink asynchronous hybrid automatic repeat request (HARQ) includes the following steps: (1) the network side adding a parameter of retransmission timer in the HARQ Profile of each dedicated media access control (MAC-d) entity flow in the user equipment, and the user equipment configures the value of the retransmission timer of the enhanced media access control entity (MAC-e) protocol data unit (PDU) according to the parameter of the retransmission timer; (2) the user equipment uses the value of the retransmission timer and the maximum number of retransmissions to control the retransmission. The radio bearer QoS delay requirement and the cooperation work between the sender and the receiver are implemented.

Owner:ZTE CORP

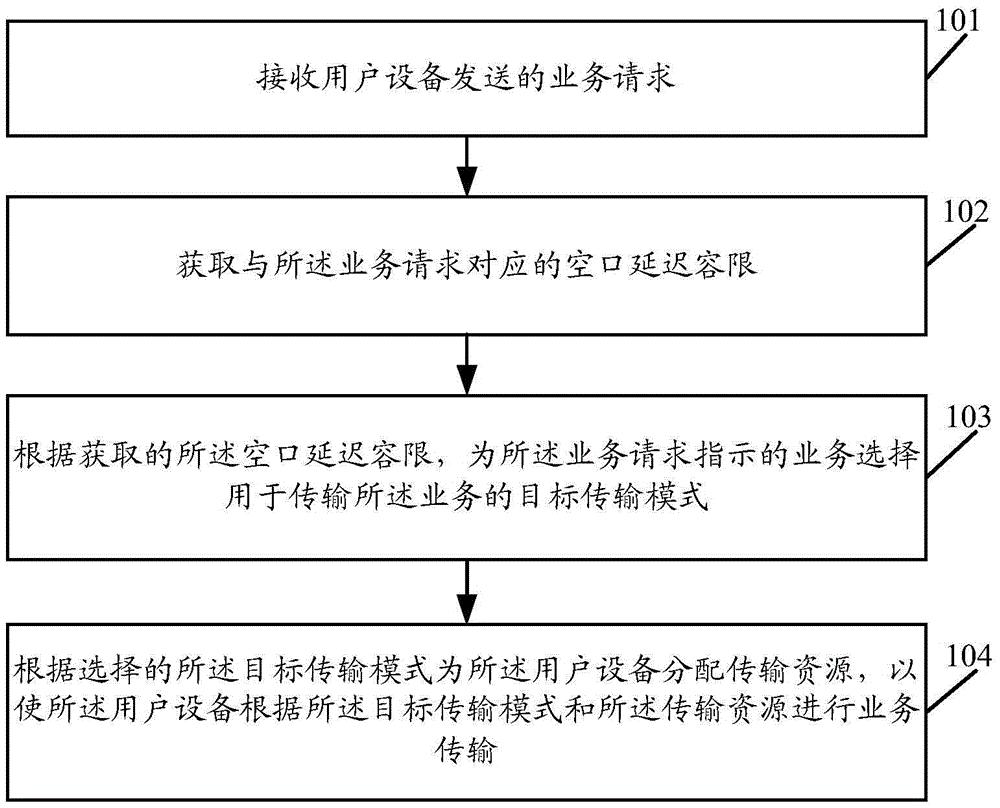

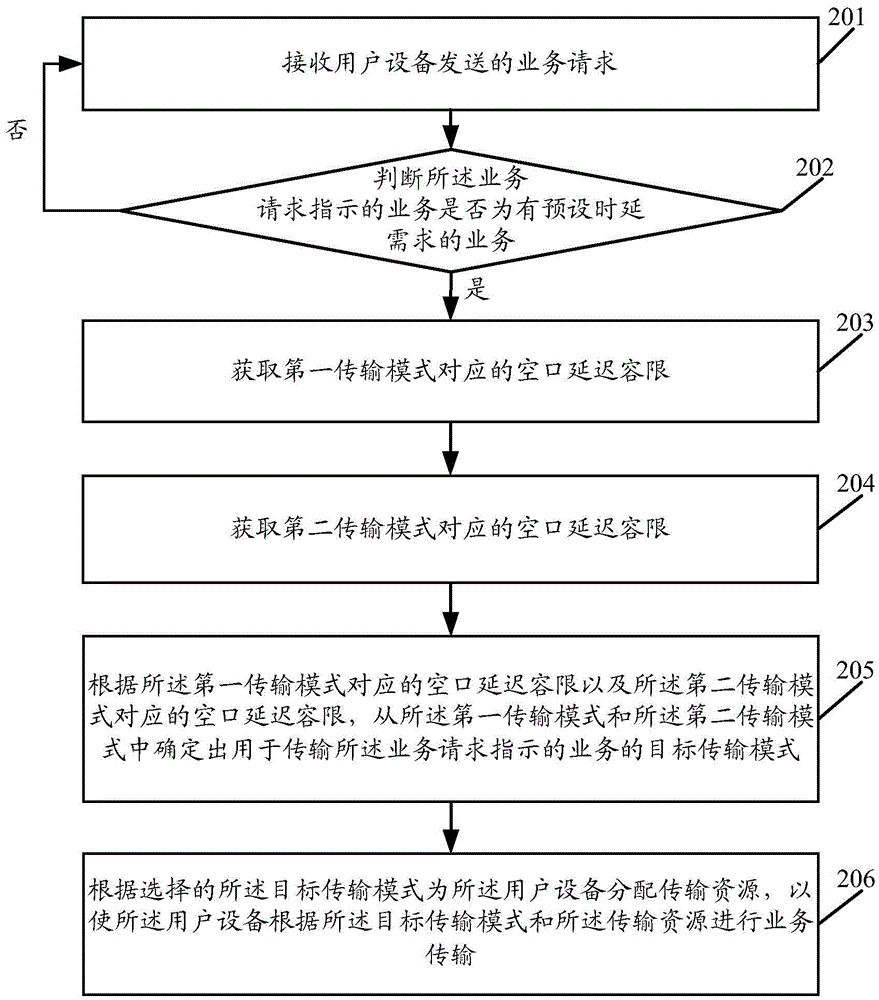

Service transmission method and device

ActiveCN105554689AMeet business latency requirementsSatisfy latency requirementsWireless commuication servicesMachine-to-machine/machine-type communication serviceTime delaysTelecommunications

The embodiment of the present invention discloses a service transmission method which comprises a step of receiving the service request sent by user equipment, a step of obtaining the air interface delay tolerance corresponding to the service request, a step of selecting a target transmission mode of transmitting service for the service indicated by the service request according to the air interface delay tolerance, a step of distributing a transmission resource for the user equipment according to the selected target transmission mode such that the user equipment carries out service transmission according to the target transmission mode and the transmission resource. The embodiment of the present invention also discloses a service transmission device. By employing the embodiment of the invention, the service transmission mode can be selected according to the air interface delay tolerance, and thus the time delay requirement of a short time delay service can be satisfied.

Owner:DONGGUAN COOLPAD SOFTWARE TECH

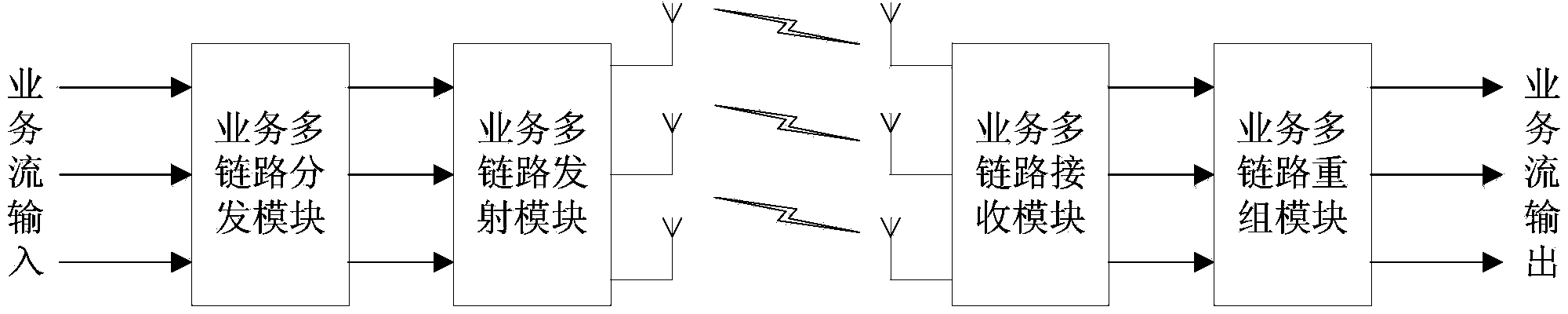

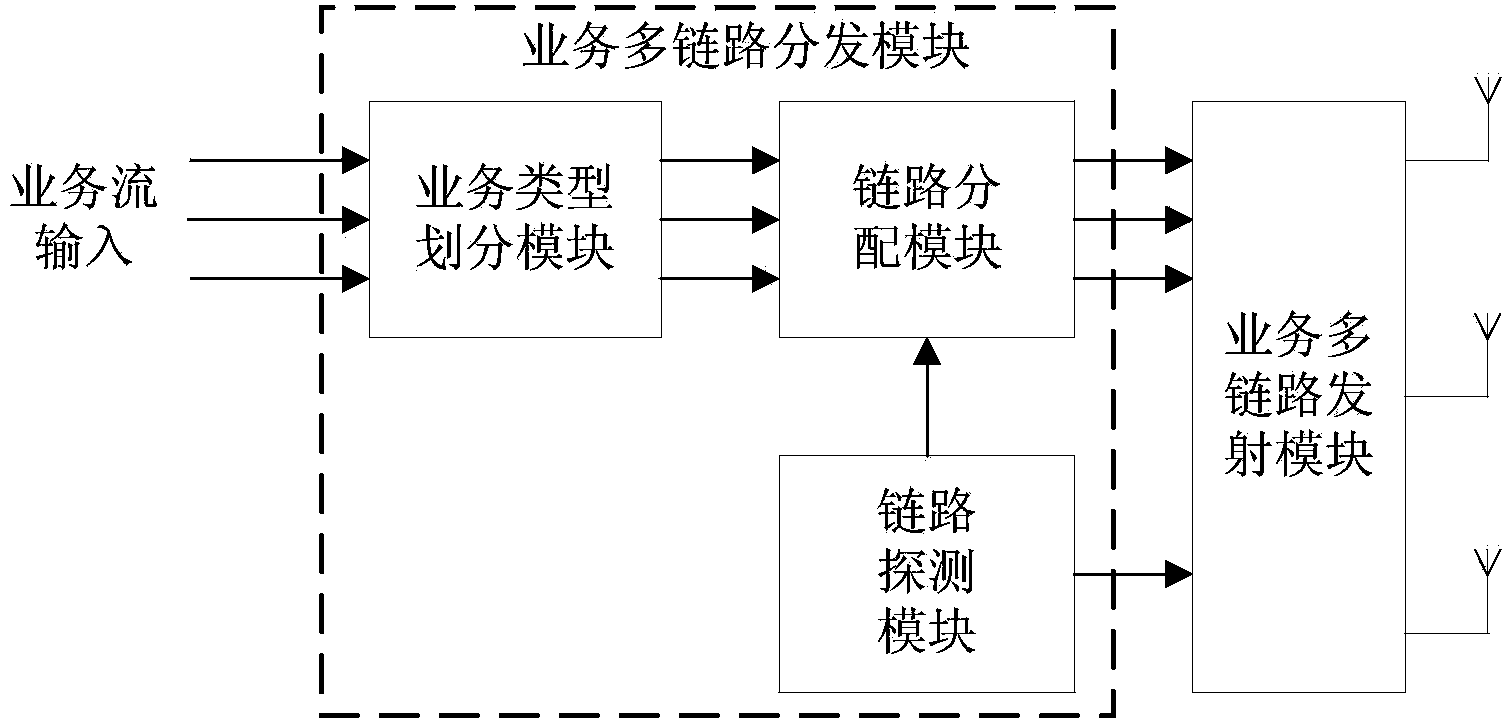

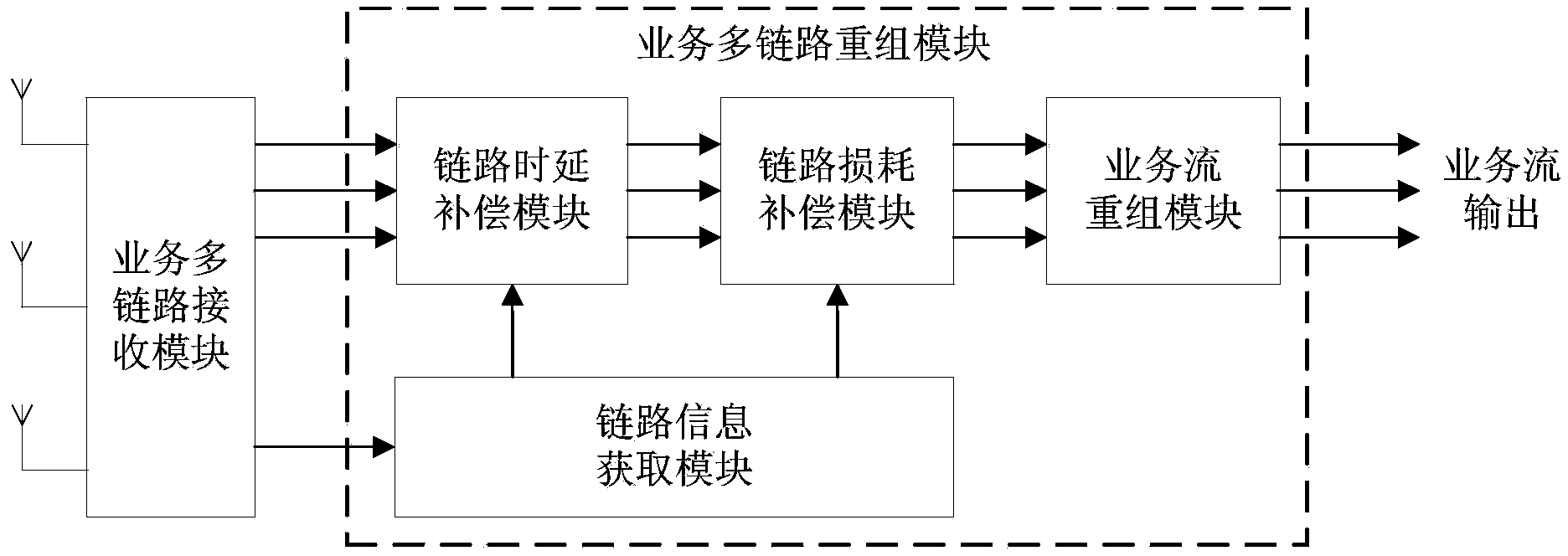

Multi-service link distribution and reorganization device and method

ActiveCN103561472AMeet needsImprove channel utilizationError preventionWireless communicationQuality of serviceTime delays

The invention provides a multi-service link distribution and reorganization device and method. The device comprises a service multi-link distribution module and a service multi-link reorganization module, wherein the service multi-link distribution module can classify services of different input service streams according to service quality requirements, detect available links, and then distribute the classified service streams to different links, and the classified service streams are sent out through a service multi-link transmission module; the service multi-link reorganization module is used for compensating for the time delay of the different links of the services which are received by a service multi-link receiving module so as to balance link loss, reorganize the service streams and restore original service streams. According to the scheme of the multi-service link distribution and reorganization device and method, link resources are distributed to the different services at the sending end according to link states and the service quality requirements, as a result, service transmission demands are met, and the utilization rate of system channel resources also can be increased; time delay and loss compensation can be conducted on data at the receiving end, and meanwhile, the out-of-order problem in parallel transmission is solved due to the fact that the same service is reorganized according to the type and package number of the service.

Owner:PLA UNIV OF SCI & TECH

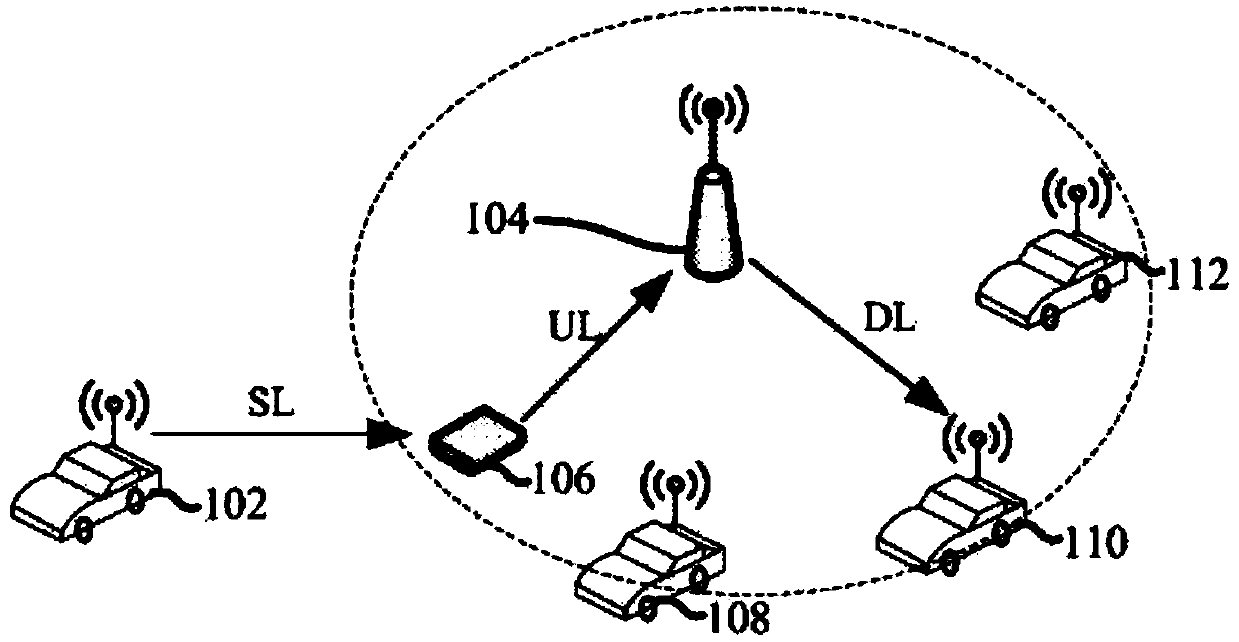

V2X business transmission method

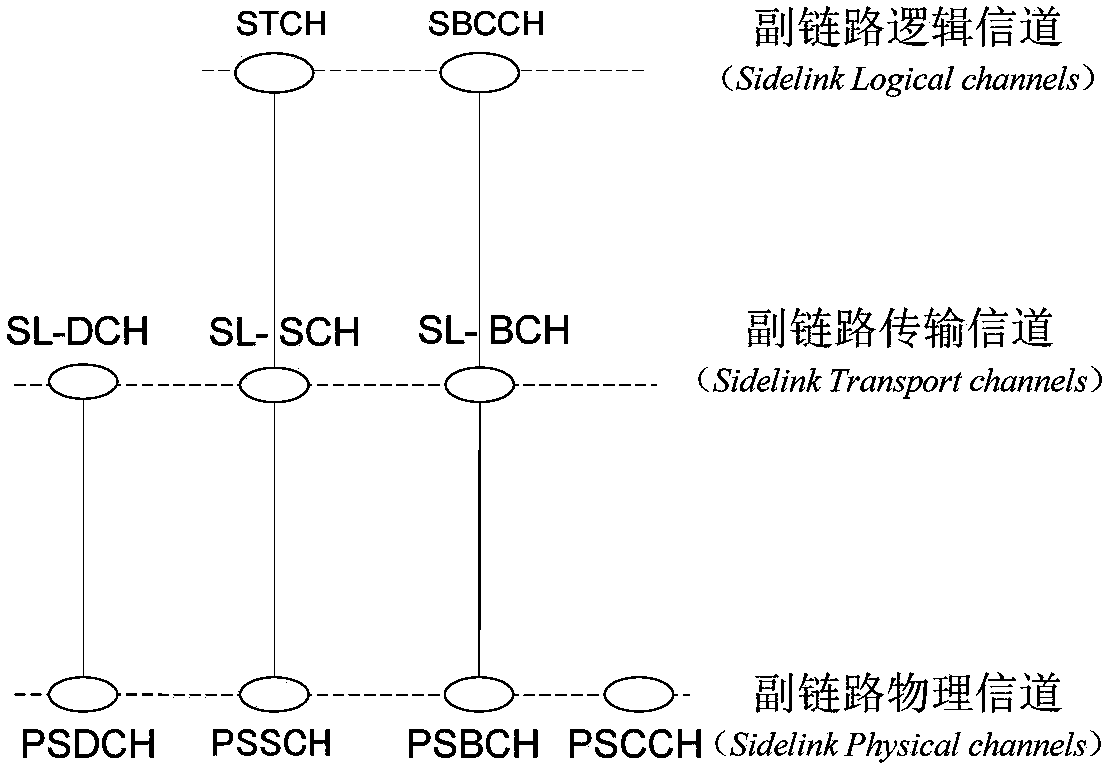

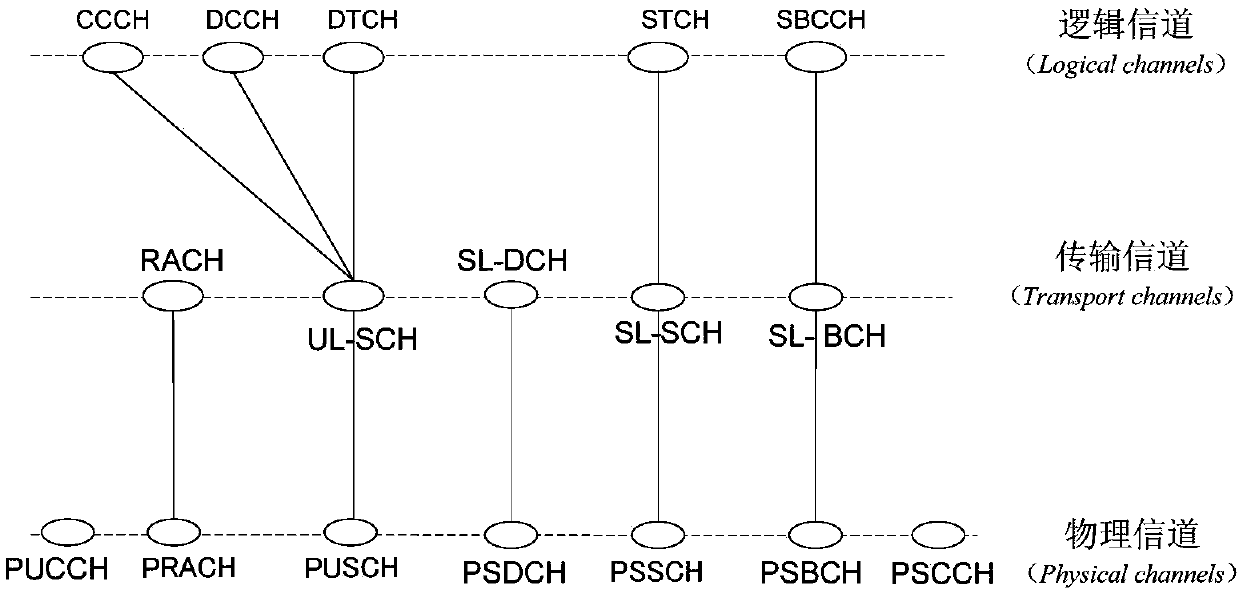

InactiveCN107645710ARealize transmissionSatisfy latency requirementsBroadcast service distributionTransmission channelBusiness data

The invention discloses a V2X business transmission method. A logical channel of a MAC (media access control) layer is added. A vehicle business channel VTCH is used for transmitting the V2X businessdata. As a Sidelink logical channel, the VTCH and the Sidelink business channel STCH both map to a Sidelink transmission channel. A Sidelink shared channel SLSCH is provided. As an uplink logical channel, the VTCH maps to the transmission channel. An uplink shared channel ULSCH is provided. The method comprises the steps that a vehicle terminal transmits the V2X business data through the VTCH; thevehicle terminal transmits communication D2D business data between devices through the Sidelink business channel STCH. The invention is advantageous in that with the new logical channel, and with thegiven mapping relationship among the new logical channel, the transmission channel and the physical channel, the transmission of the V2X business can be realized.

Owner:POTEVIO INFORMATION TECH

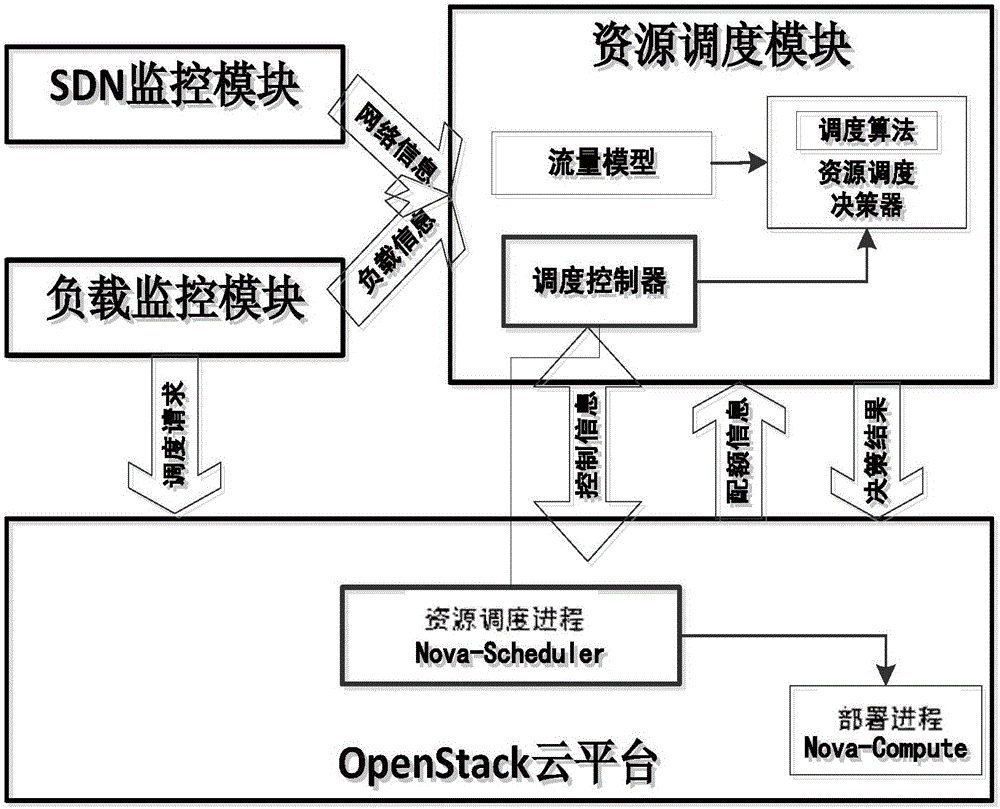

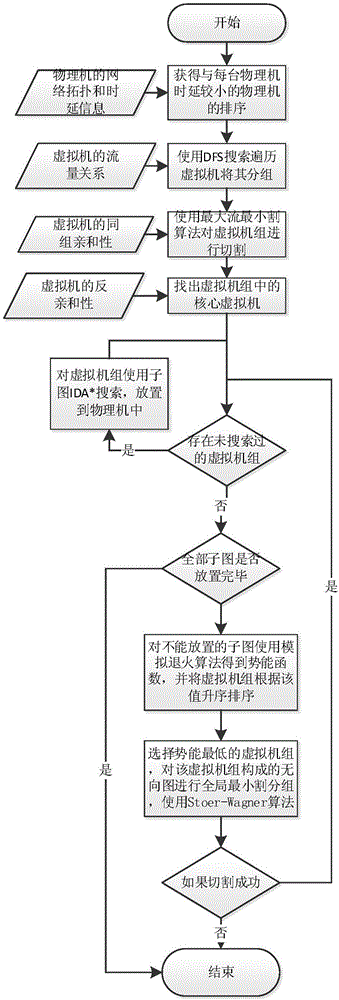

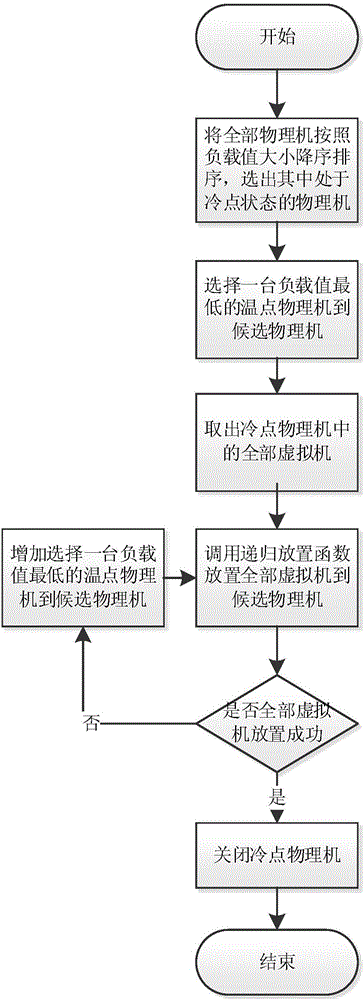

OpenStack cloud platform resource dynamic scheduling system and method based on flow affinity

ActiveCN106534318AReduce energy consumptionLoad balancingProgram controlTransmissionTime delaysClient-side

The invention discloses an OpenStack cloud platform resource dynamic scheduling system and method based on flow affinity. The system includes an OpenStack cloud platform performing a resource scheduling process, a system load monitoring module monitoring and collecting the load information of a physical host in the OpenStack cloud platform cluster and providing the load information to a resource scheduling module, determining the existence of cold spots and hot spots in the cluster and sending a cold spot integration or hot spot elimination request to the resource scheduling process, an SDN monitoring module monitoring and collecting the network topological structure information in the OpenStack cloud platform cluster, the flow information between the physical hosts and the flow information between the virtual machine instances, and providing the information to the resource scheduling module, and the resource scheduling module processing the virtual machine instance initial setup request from the client of the OpenStack cloud platform and the cold spot integration request and hotspot cancellation request from the system load monitoring module. The scheduling system meets the time delay requirements of specific business, realizes load balancing of a cloud platform physical machine cluster and reduces the energy consumption of the cloud platform.

Owner:ZHEJIANG UNIV

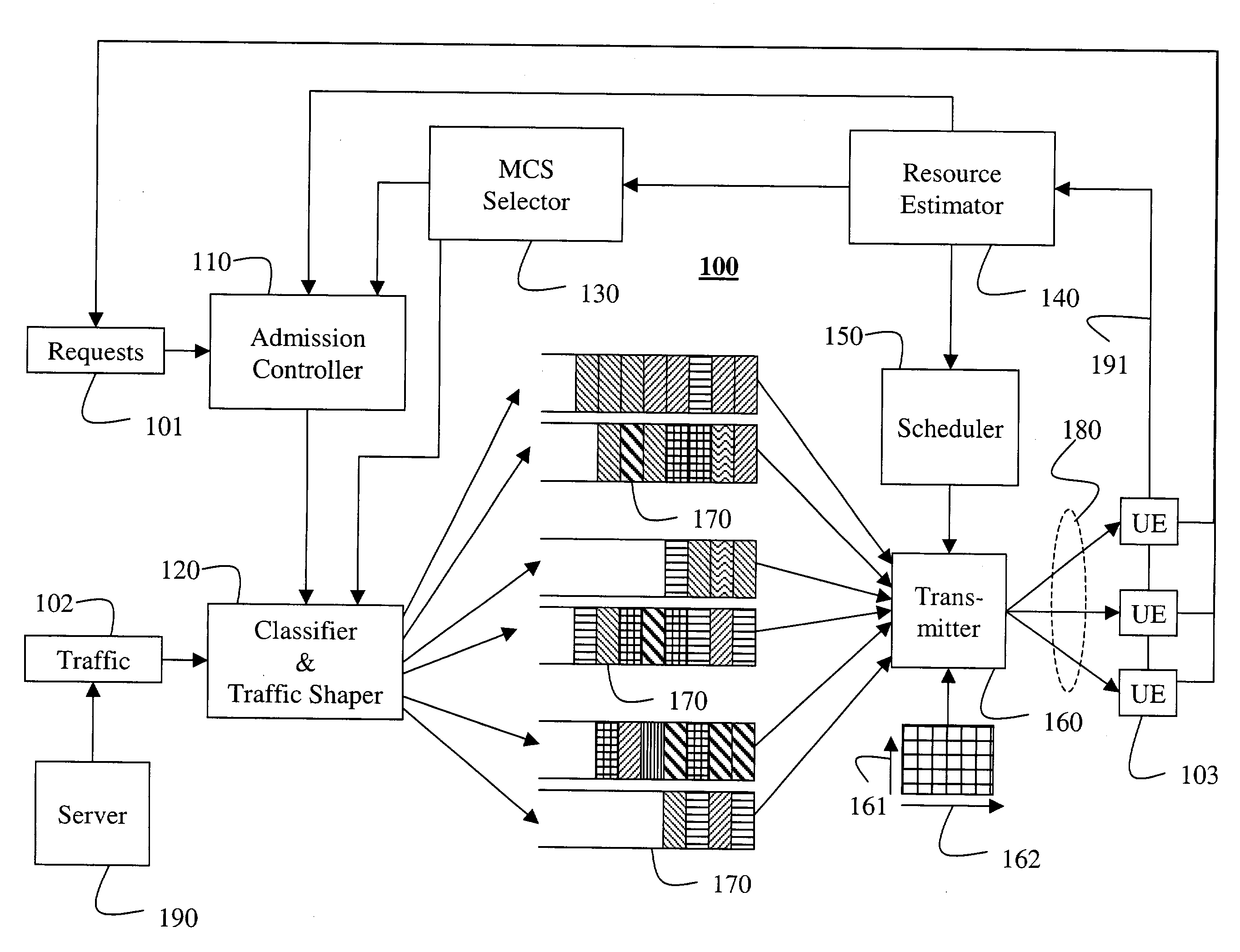

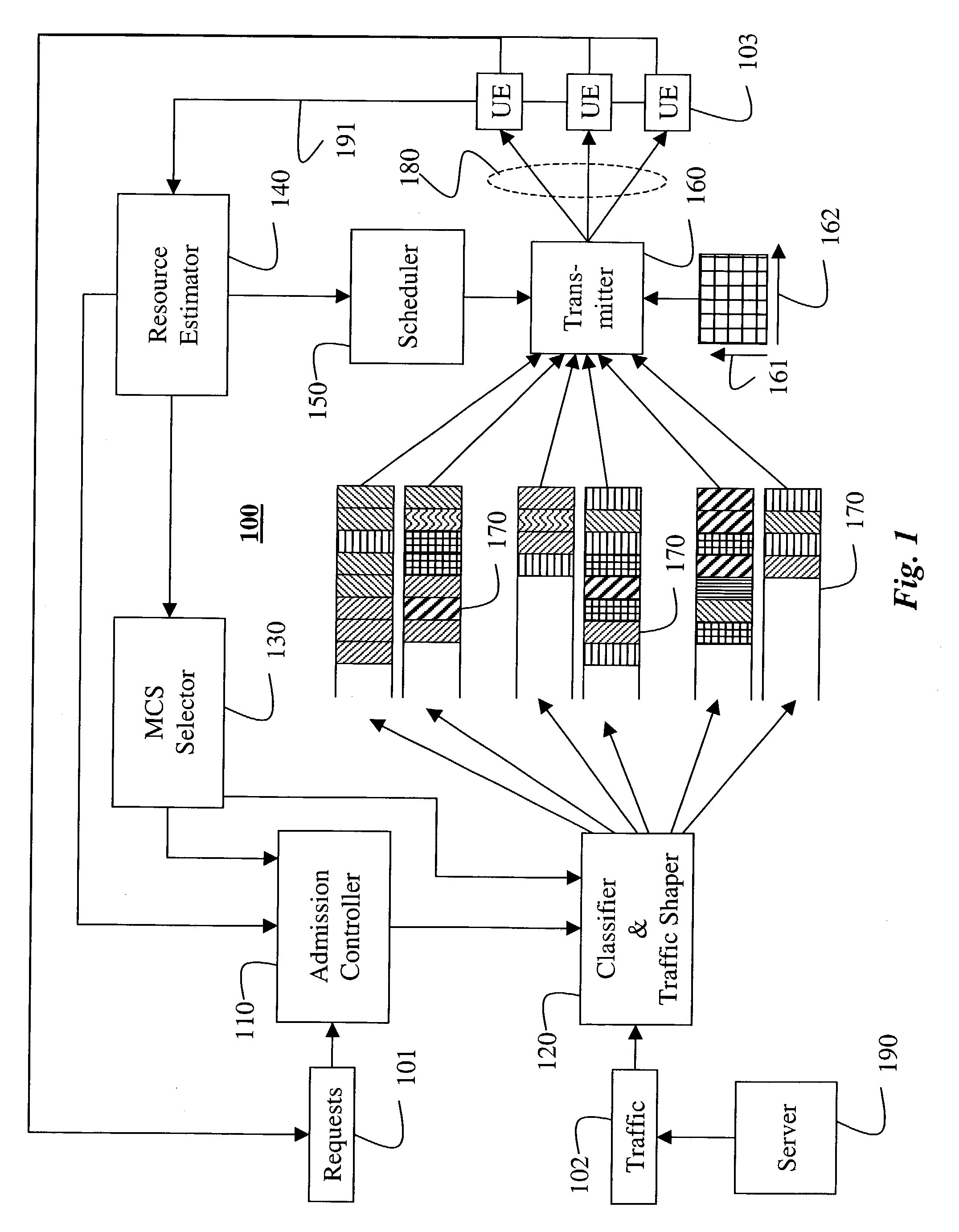

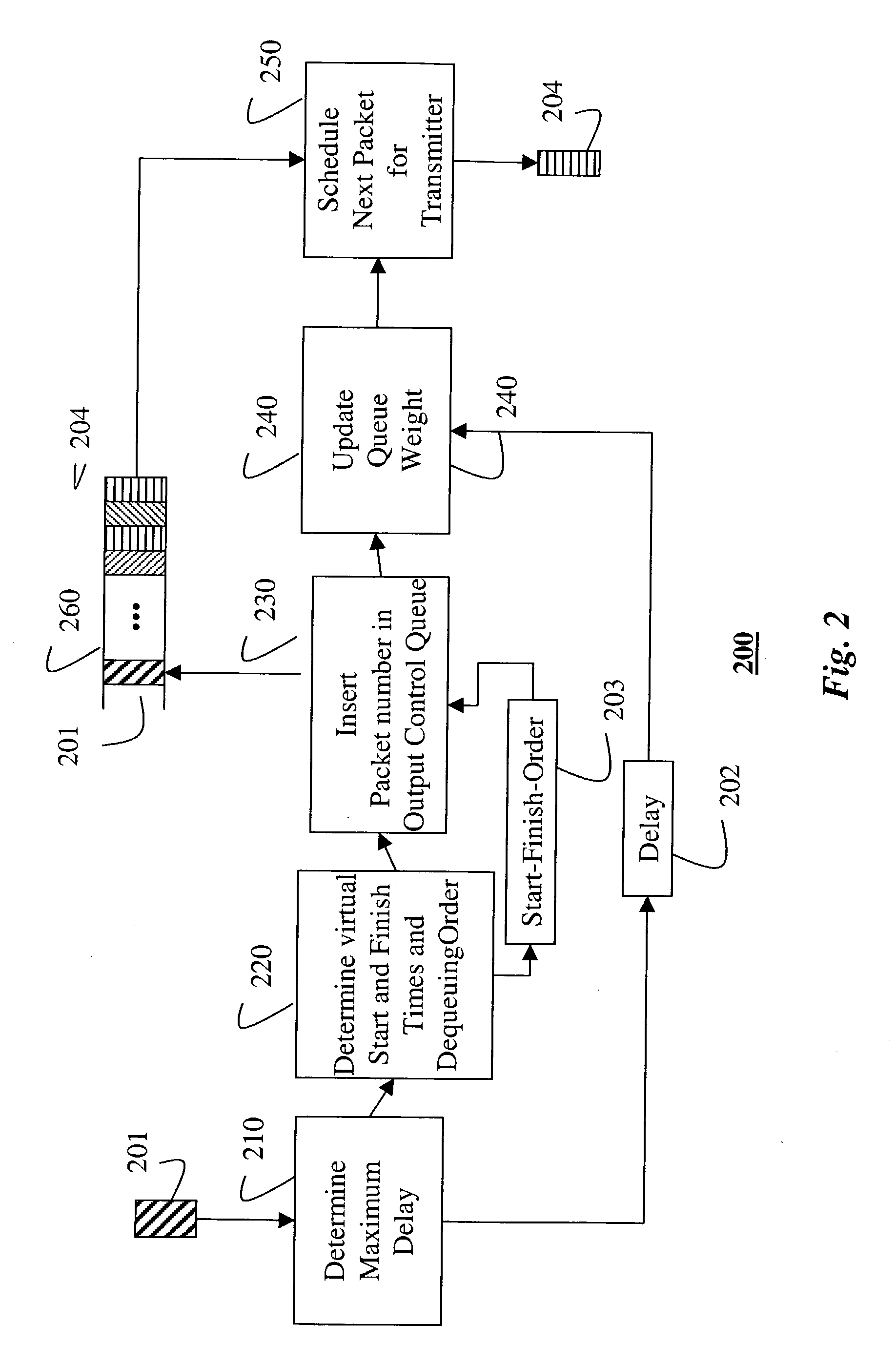

Dynamic resource control for high-speed downlink packet access wireless channels

InactiveUS7330433B2Improve network efficiencyMeet the delay requirementsError preventionNetwork traffic/resource managementStart timeDynamic resource

A method allocates resources of a wireless communications network to traffic transmitted to user equipment over a channel of the network. A packet of the traffic to be stored in a selected queue is received. A maximum delay of the selected queue is determined, along with a start time, a finish time, and a queuing order. The packet is inserted in the selected queue according to the start time, the finish time and the queuing order, and then a weight of the selected queue is updated. Then, a next packet to be dequeued from the selected queue is scheduled, and the next packet is transmitted to the user equipment over the channel.

Owner:MITSUBISHI ELECTRIC RES LAB INC

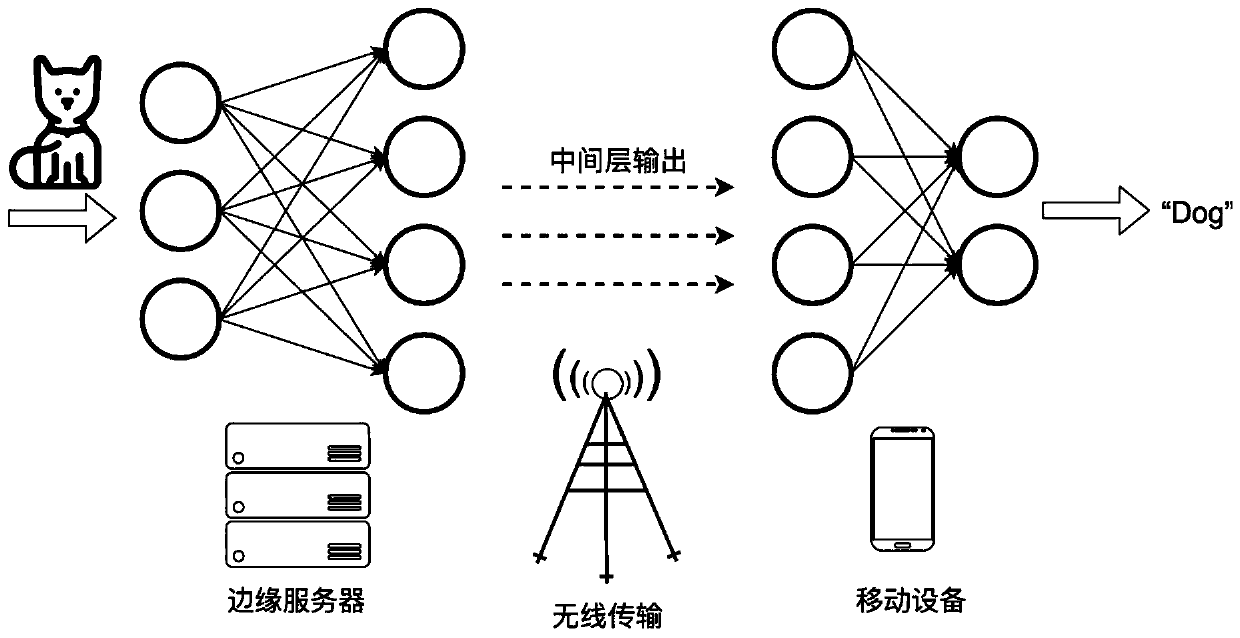

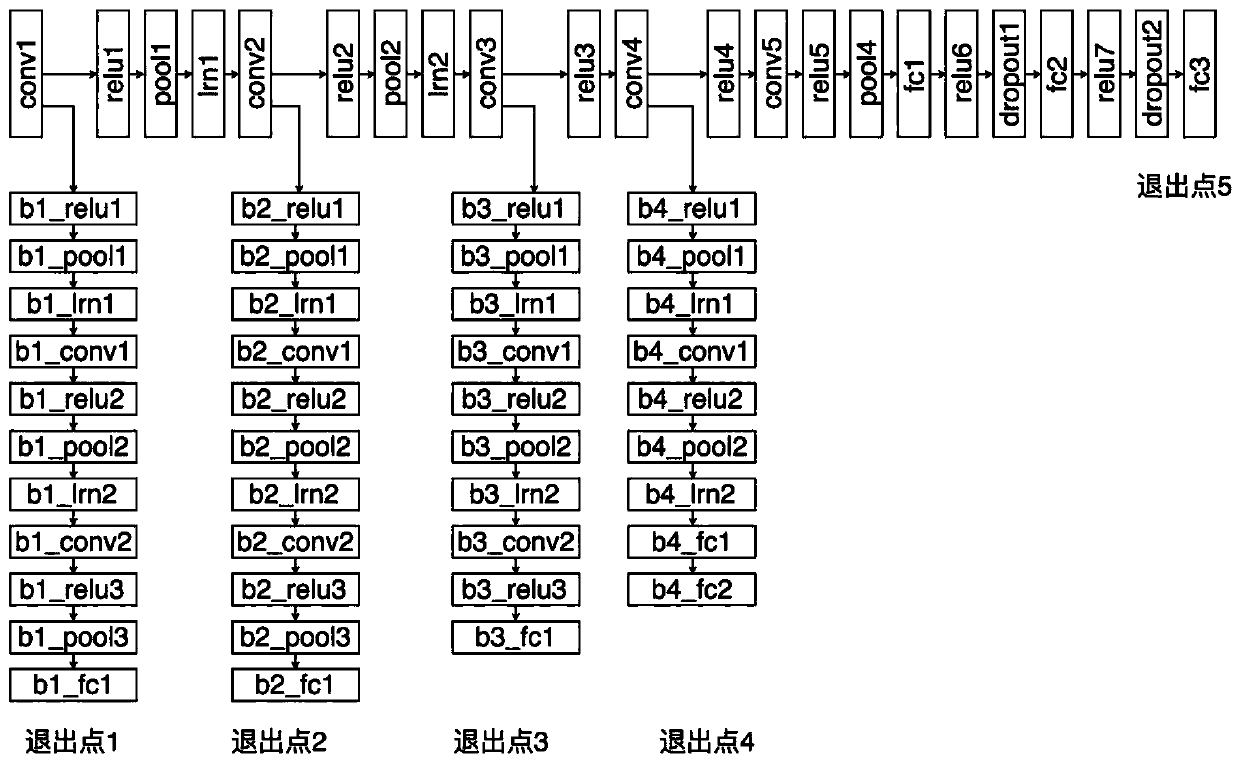

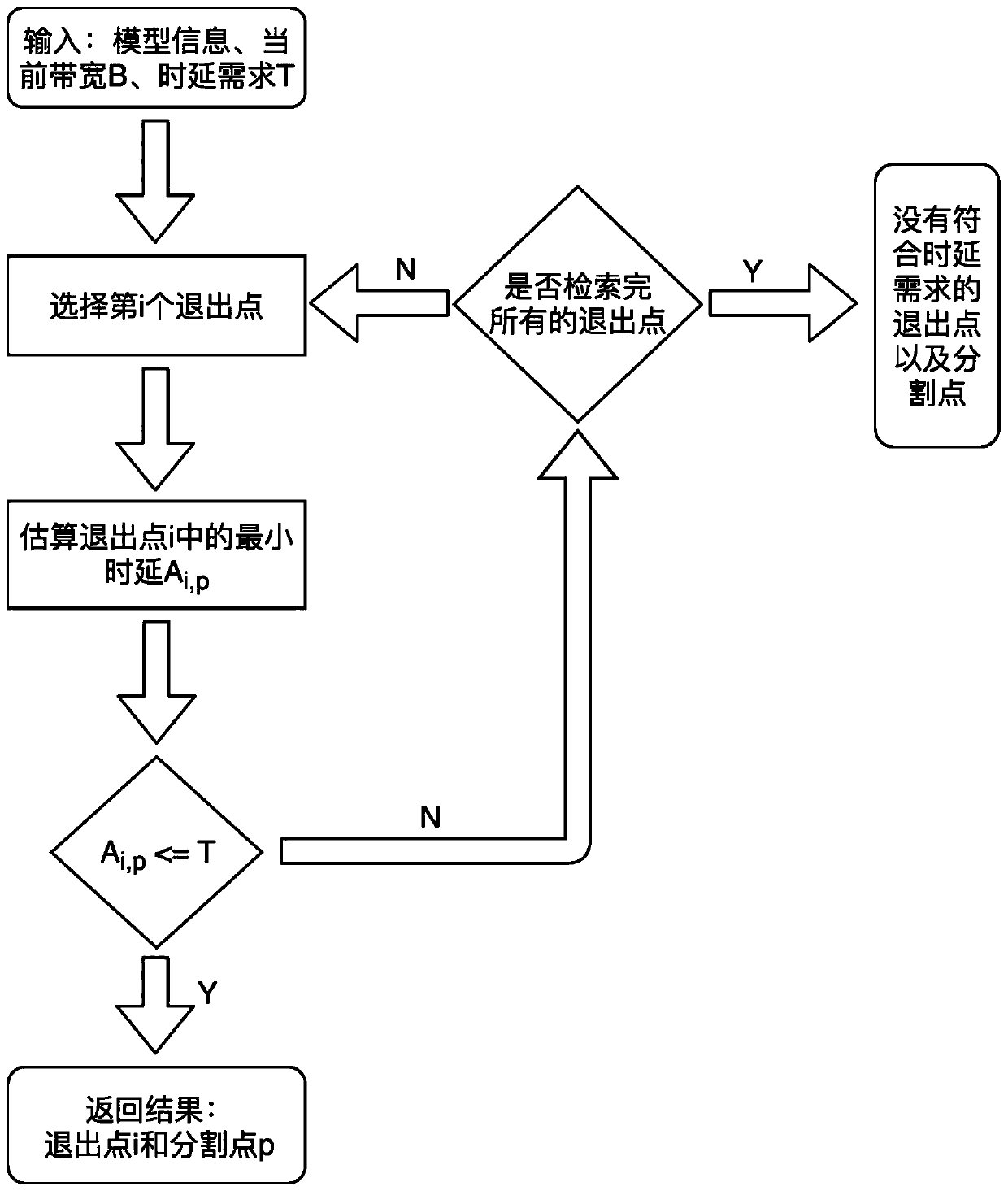

Deep learning model reasoning acceleration method based on cooperation of edge server and mobile terminal equipment

PendingCN110309914AReduce inference latencyTroubleshooting Deploying Deep Learning ModelsNeural architecturesPhysical realisationEdge serverAlgorithm

The invention discloses a deep learning model reasoning acceleration method based on cooperation of an edge server and mobile terminal equipment. Model segmentation and model simplification are combined. Through training and using the regression model, an operation delay of the network layer of a deep learning model on the edge server and on a mobile terminal device is accurately estimated. Therefore, an exit point and the segmentation point which meet the time delay requirement are searched out. Compared with a traditional method based on a cloud data center and a method directly deployed onequipment, the method not only can realize efficient and low-time-delay reasoning of the deep learning model on the mobile terminal equipment, but also can provide a deep learning model reasoning scheme meeting the time delay requirement for trade-off between the time delay and the accuracy.

Owner:SUN YAT SEN UNIV

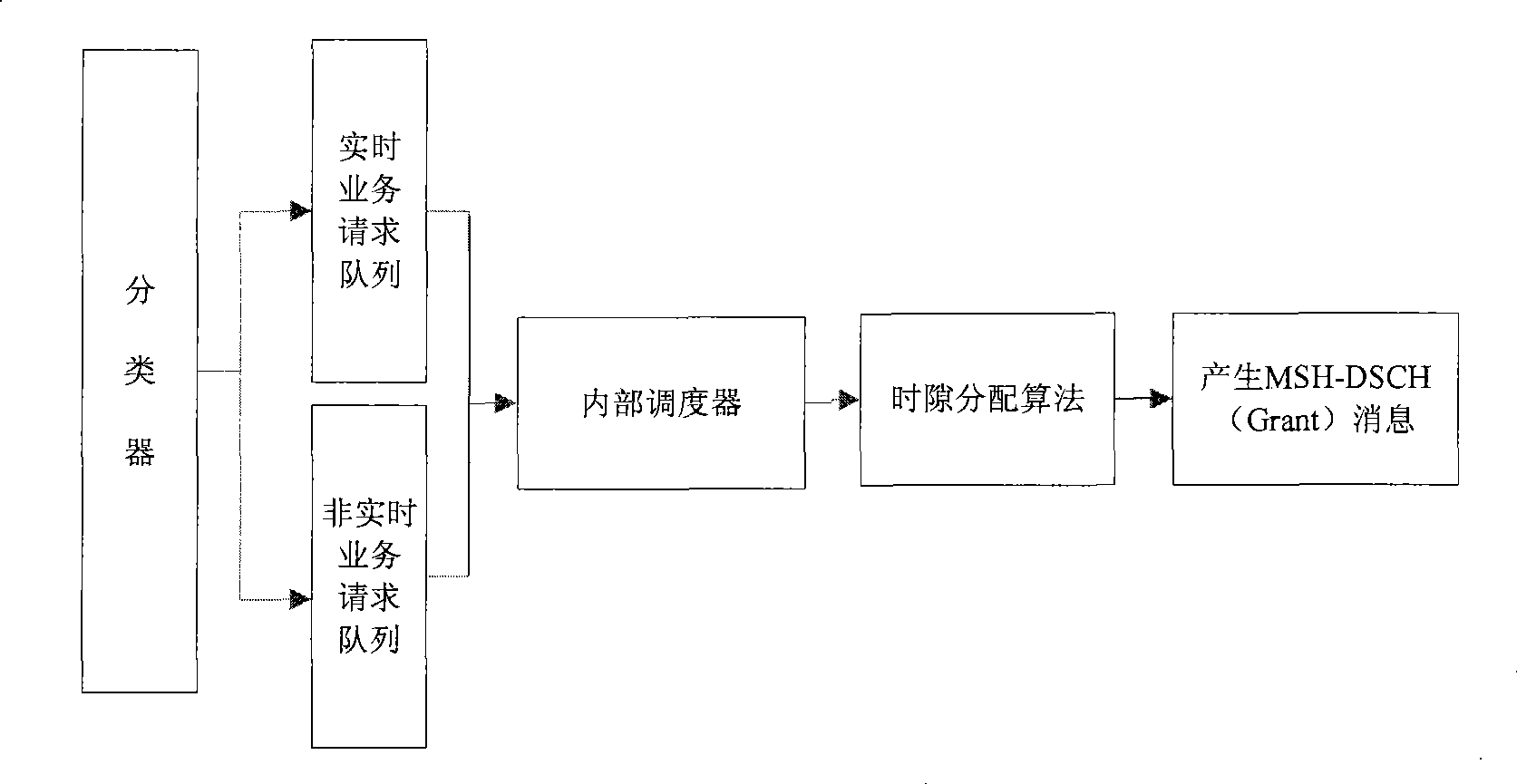

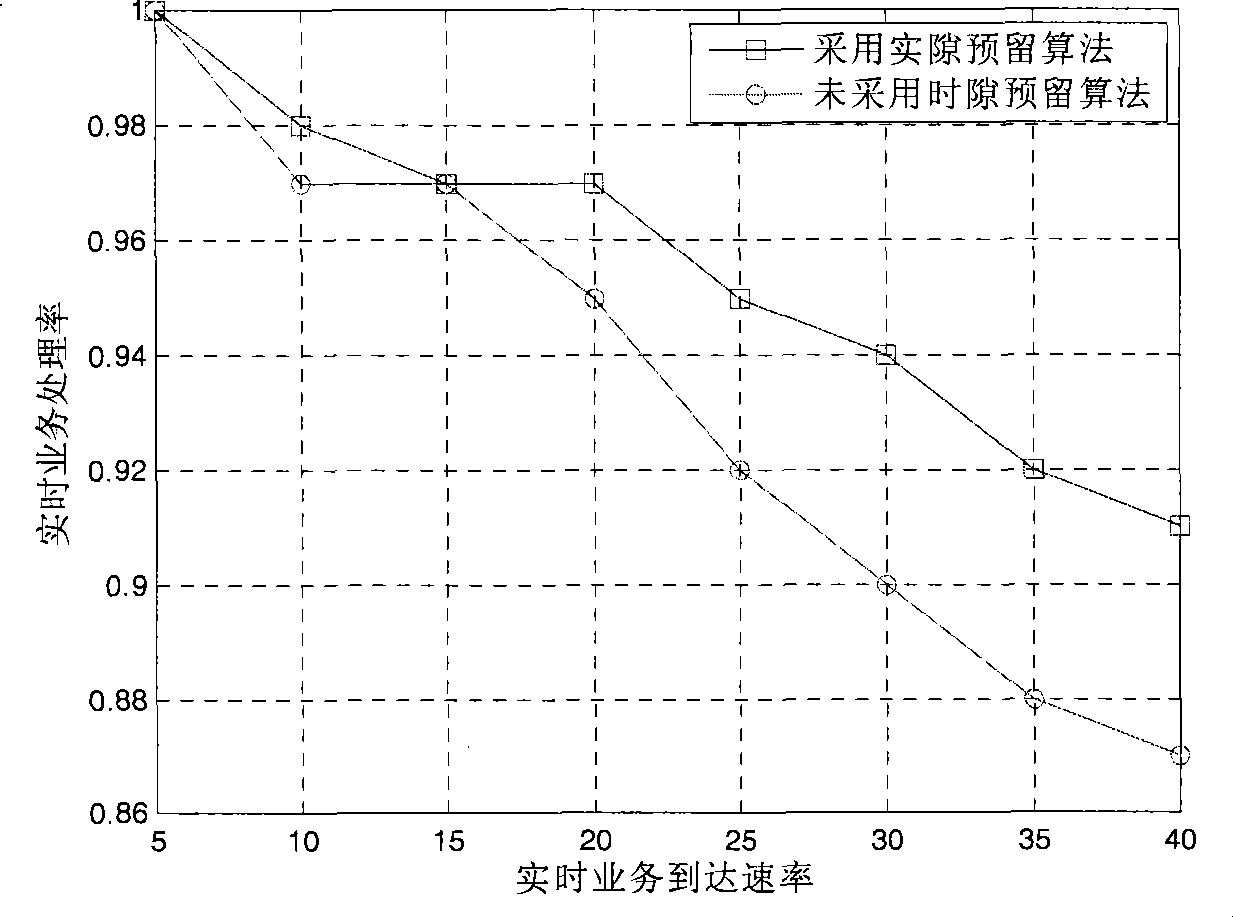

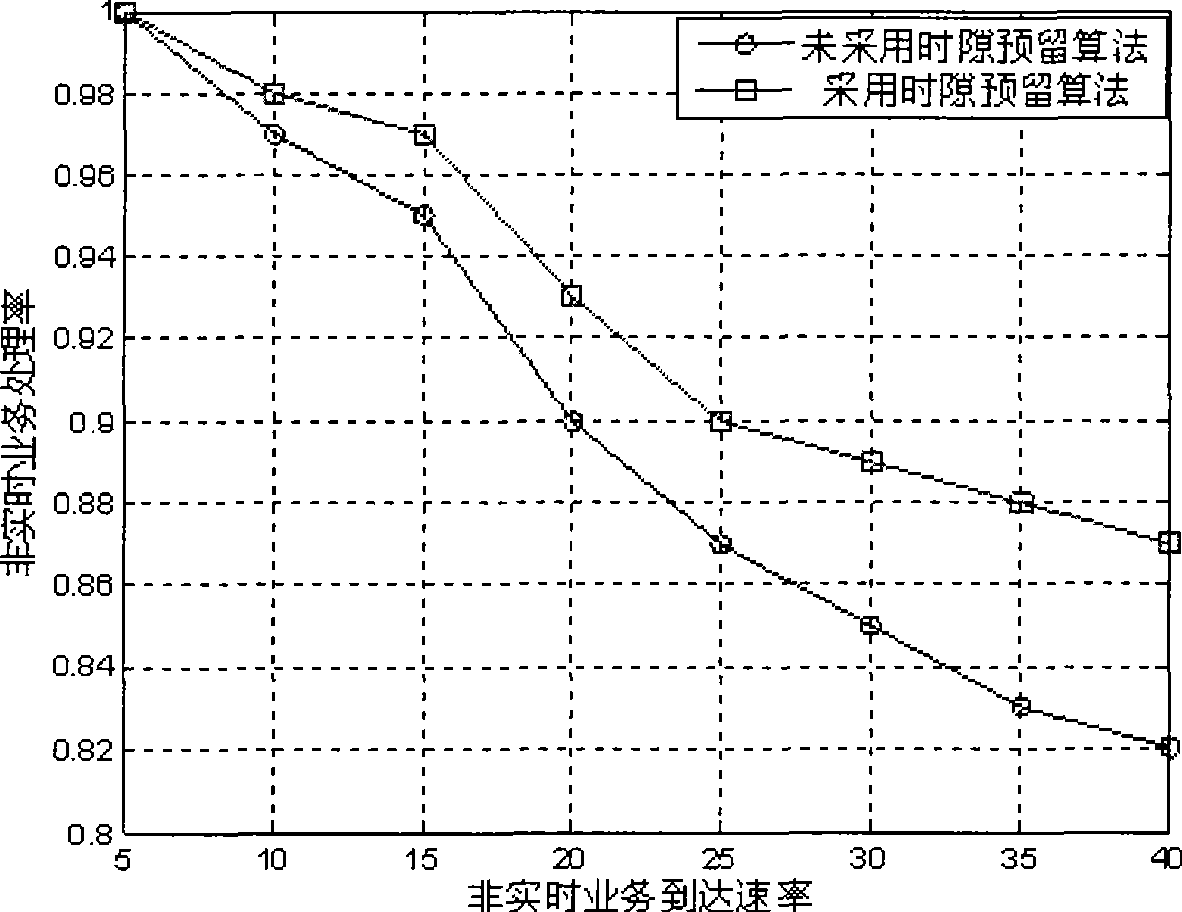

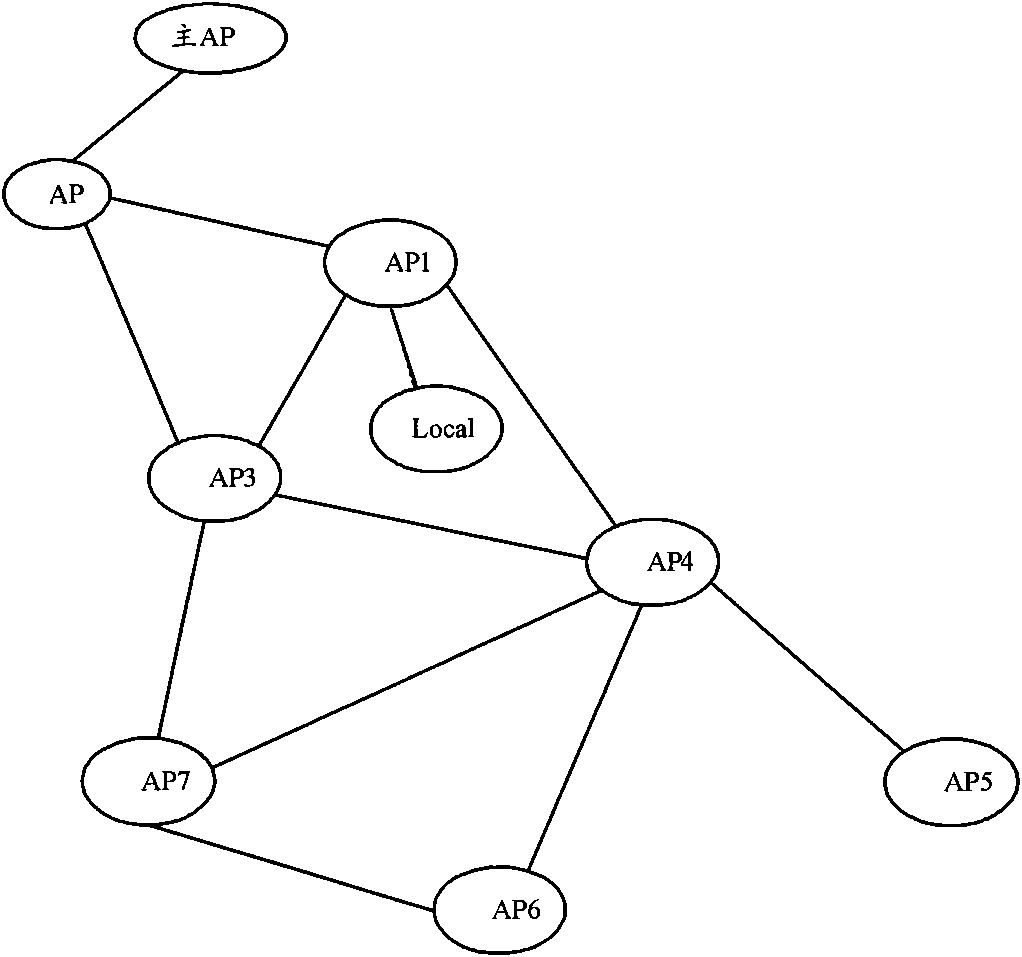

Wireless Mesh network MAC layer bandwidth request and allocation method based on IEEE802.16d standard

InactiveCN101459932AGuaranteed priorityAvoid hunger and thirstNetwork traffic/resource managementNon real timeHigh bandwidth

The invention relates to a request and distribution method of MAC bandwidth of wireless Mesh network based on standard of IEEE802.16d. Based on MAC standard, the invention is combined with some queue scheduling algorithms to make bandwidth request and distribution strategy with QoS guarantee under the mode of Mesh. The strategy preferentially treats real-time business request, reserves bandwidth, and guarantees time delay of the real-time business. Simultaneously, size and step-length of the reserved bandwidth are dynamically adjusted according to non-real time business request queue length, and equity of service is enhanced. Simultaneously, the request and distribution method of the invention realizes that different applications are provided with different levels of QoS guarantee to a certain extent, and higher bandwidth availability ratio can still be achieved.

Owner:BEIJING JIAOTONG UNIV

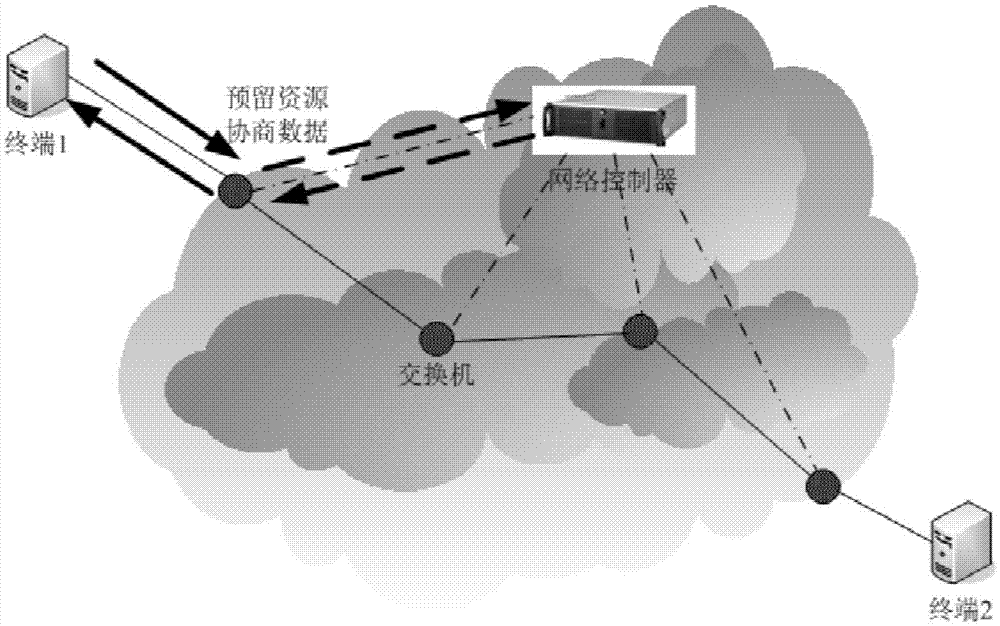

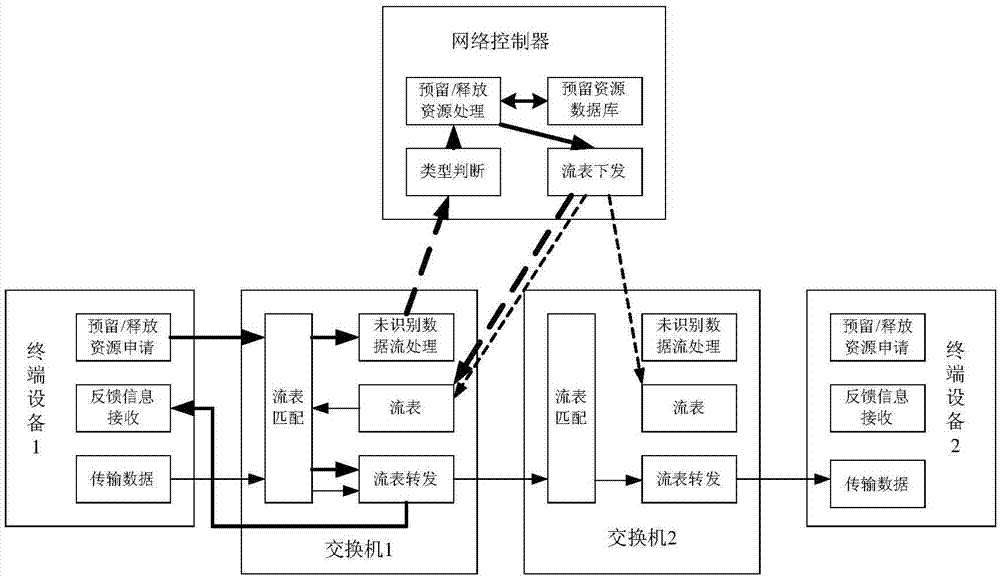

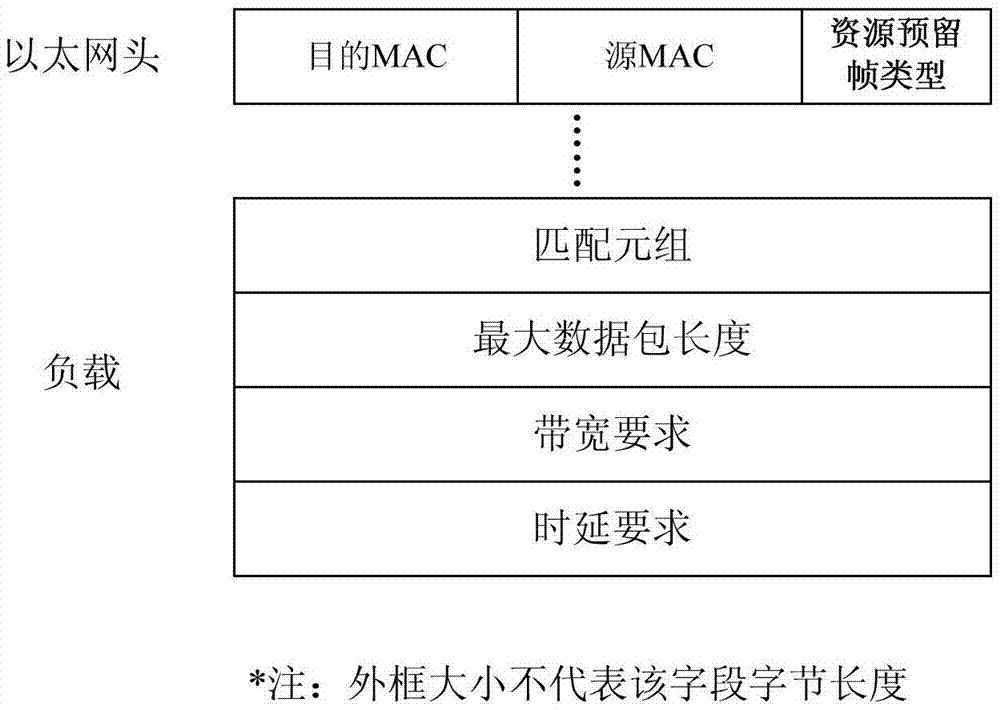

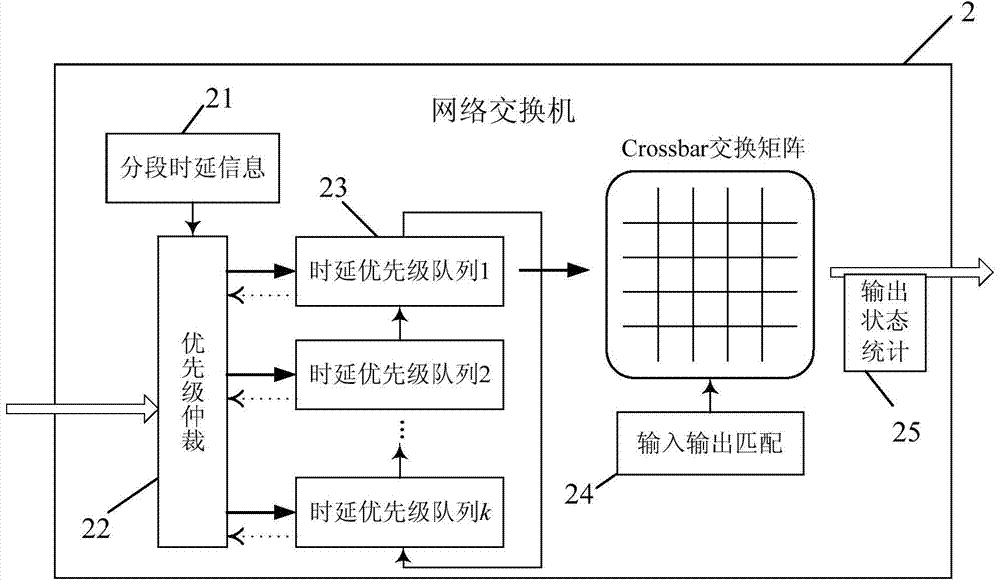

Dynamic network resource reservation QoS guaranteeing method oriented to industrial SDN

ActiveCN106921594AMeet bandwidth requirementsSatisfy latency requirementsData switching networksData streamTerminal equipment

The invention discloses a dynamic network resource reservation QoS guaranteeing method oriented to an industrial SDN. The method comprises a reserved resource application process, a reserved resource forwarding process and a reserved resource releasing process. A data packet with a designated Ethernet type is used for performing the negotiation of the resource reservation between a terminal device and a network, a network switch connected with the terminal intercepts the data packet of this type and sends the same to a controller; the controller reserves a bandwidth resource for the data flow according to the bandwidth and delay requirement of the data flow and the actual application condition of the network bandwidth, or releases the reserved bandwidth resource, and delivers the reserved resource result to the switch in a flow table sending way to be executed. The resource reservation / releasing process is flexibly controlled through a negotiation mechanism, and the supportability on the service data flow especially the period service data flow and the adaptability on the complicated communication state by the network can be improved.

Owner:SHENYANG INST OF AUTOMATION - CHINESE ACAD OF SCI

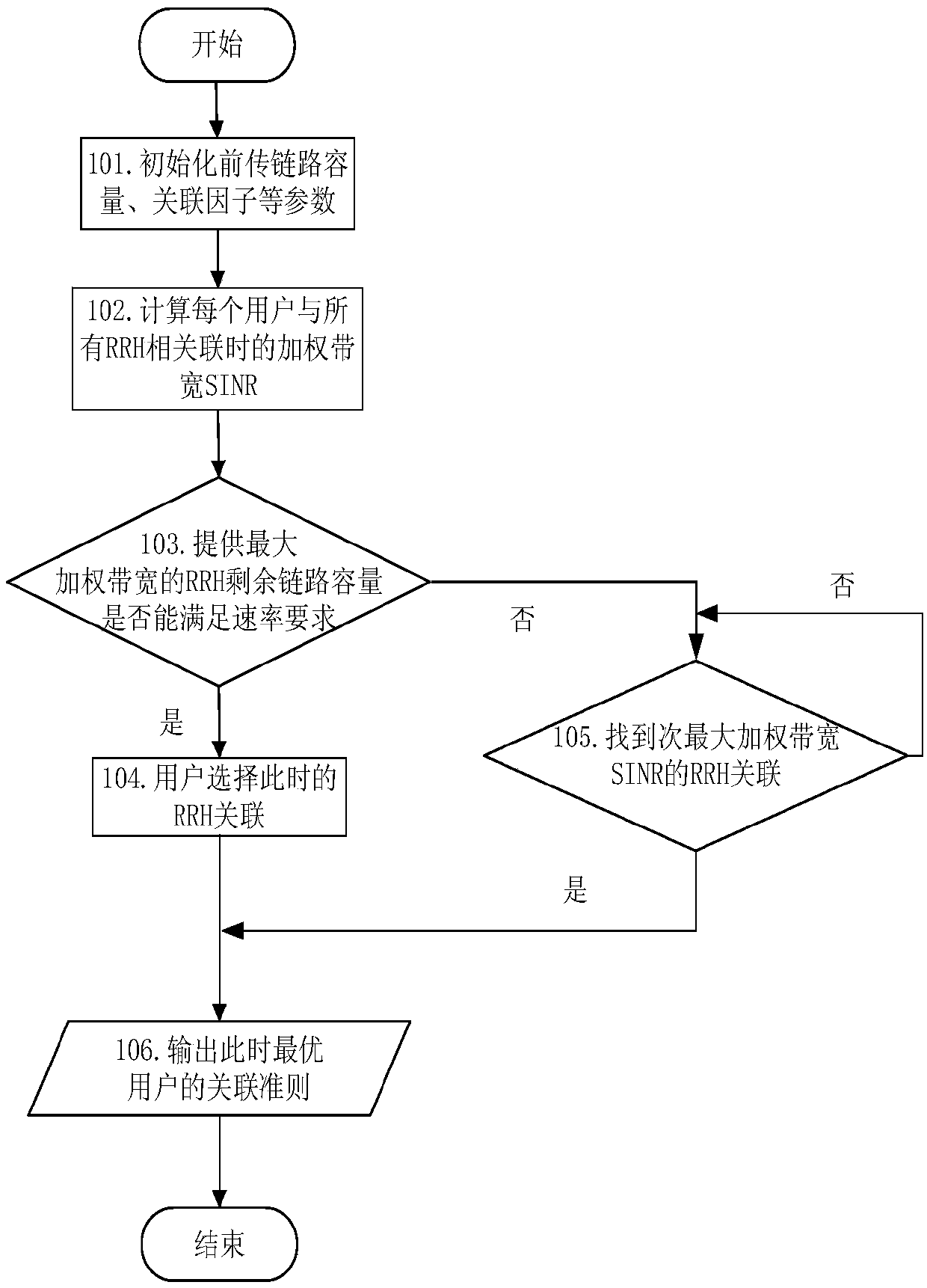

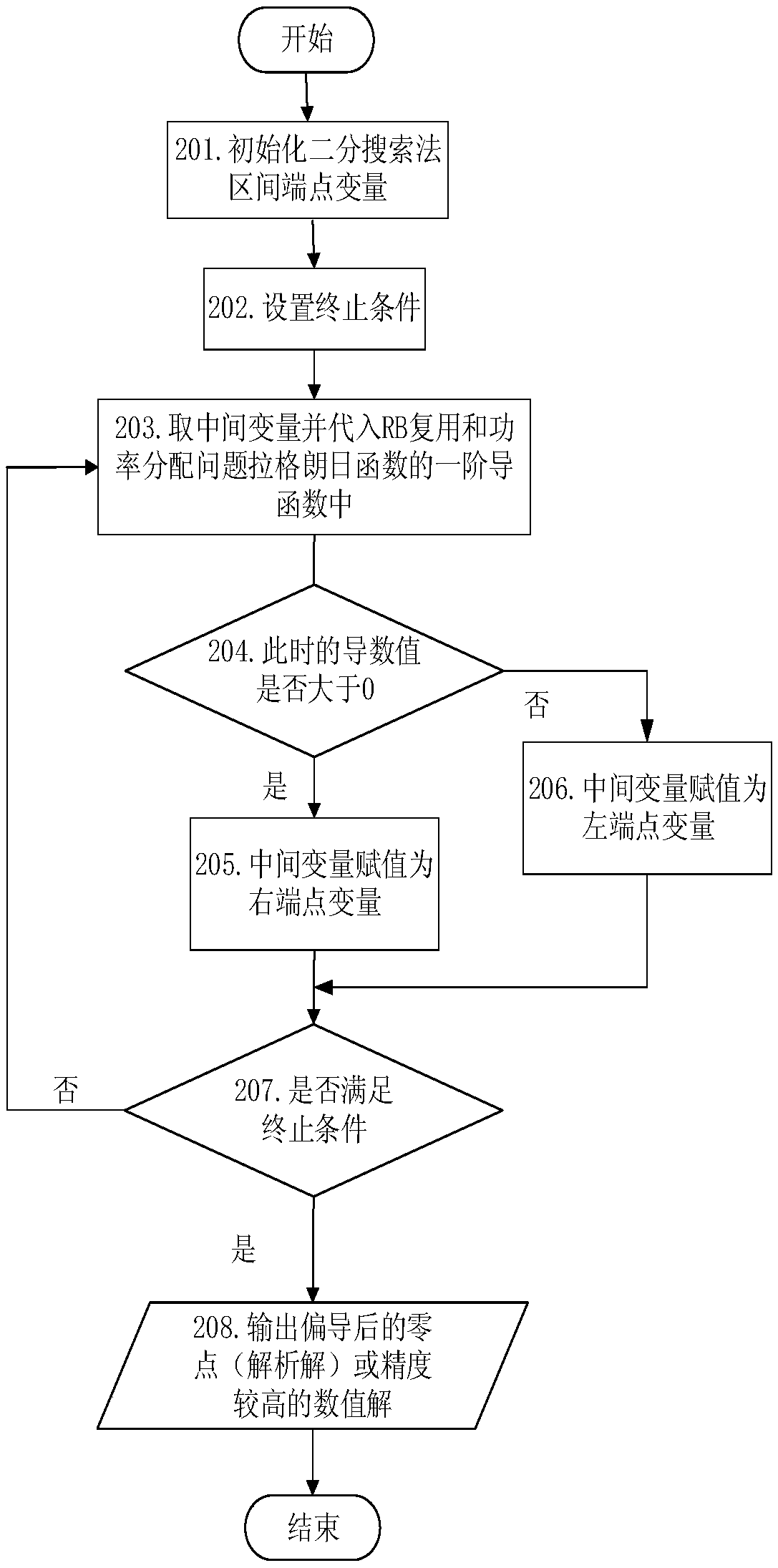

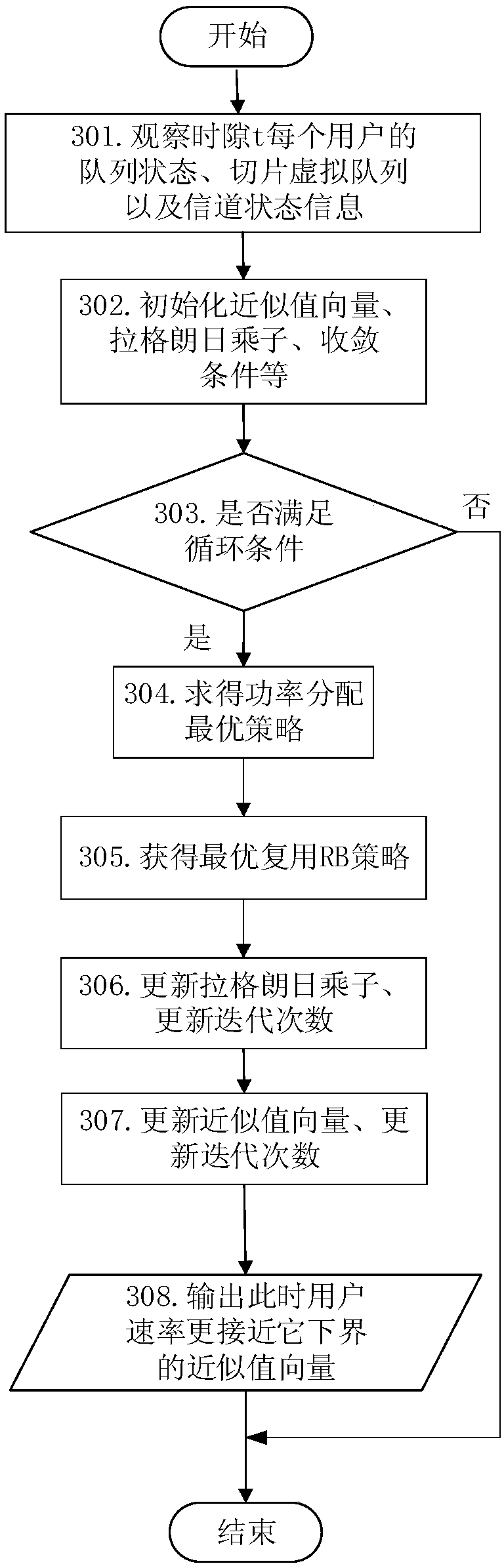

A network slicing dynamic joint user association and power allocation method based on NOMA

ActiveCN109041193AMaximize network throughputImprove throughputPower managementBroadbandResource utilization

The invention relates to a network slice dynamic joint user association and power distribution method based on NOMA, belonging to the mobile communication field. Under the condition of imperfect downlink channel of NOMA system, the wideband SINR between slice user and RRH is obtained according to the channel state information, and judges the strategy of user and RRH association. According to the user queue state information and the channel state information, the power of a plurality of users in the network slice is multiplexed on the same RB within the maximum number of multiplexed users of the resource block RB, and the optimal power resources are allocated to each user under the premise of satisfying the minimum rate requirements of each slice and user, user delay requirements, system outage probability constraints and forward link capacity constraints. The invention not only improves the utilization rate of spectrum resources and the throughput of the network, but also satisfies thelowest speed requirement of the slice and the user and the time delay requirement of the user.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

Latency-aware service opportunity window-based (LASO) scheduling

ActiveUS7463892B2Maximize amount of time providedSatisfy latency requirementsNetwork traffic/resource managementTime-division multiplexControl channelTraffic flow

Traffic flows of data packets from respective packet queues in wireless stations to a shared transmission medium of a wireless network are scheduled in accordance with Hybrid Controlled Channel Access (HCCA) and Enhanced Distributed Channel Access (EDCA). HCCA is applied by eliminating from consideration for HCCA access flows for which the sum of a desired minimum age of an oldest data packet in the respective packet queue and the time of creation of the oldest data packet is greater than the present time. For flows that are not eliminated from consideration, HCCA access is granted to the flow having a smallest sum of the desired maximum age of the oldest data packet and the time of creation of the oldest data packet. When all traffic flows are eliminated from consideration for HCCA access, EDCA is applied so that traffic flows compete for access to the medium.

Owner:TELCORDIA TECHNOLOGIES INC +2

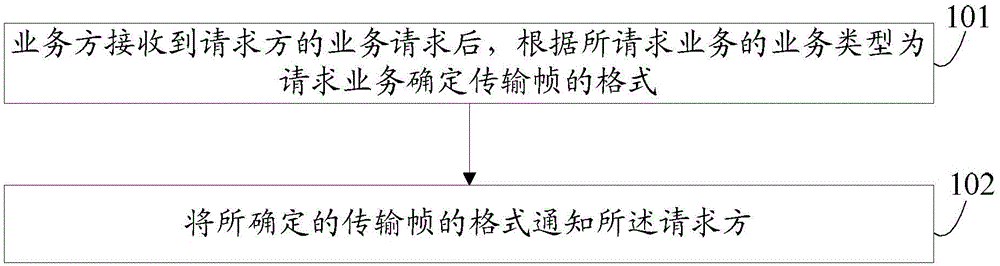

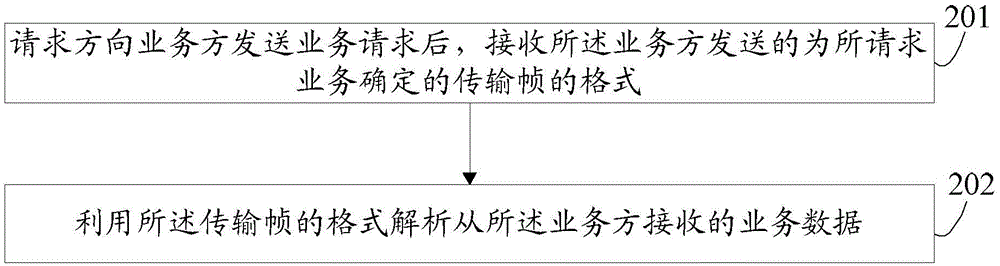

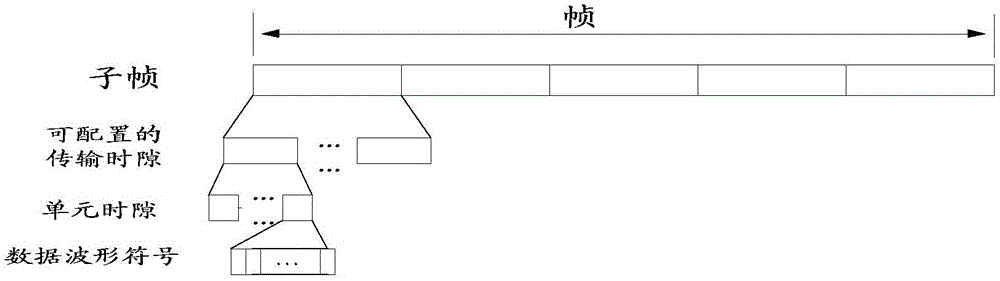

Terminal, network cell equipment, device and method for service transmission on basis of configurable structural frames

ActiveCN106358297AImprove transmission efficiencyReduce overheadPilot signal allocationWireless communicationMinimum timeComputer terminal

An embodiment of the invention discloses a terminal, network cell equipment, a device and a method for service transmission on the basis of configurable structural frames. The method includes that after receiving a service request from a requester, a service side determines a format of a transmission frame for a request service according to a service type of the request service and informs the requester of the determined format of the transmission frame. The transmission frame comprises a plurality of subframes, each subframe comprises one or more transmission time slots, and each transmission time slot comprises one or more unit time slot, wherein each unit time slot is a minimum time unit in the transmission frame and comprises one or more data symbols, and the unit time slots are identical in fixed duration. The unit time slots in each format of the transmission frame are different in pilot frequency patterns, the pilot frequency patterns of the unit time slots can be adjusted according to lengths of the transmission time slots, and the unit time slot pilot frequency patterns in each transmission time slot can be identical or not.

Owner:CHINA MOBILE COMM GRP CO LTD

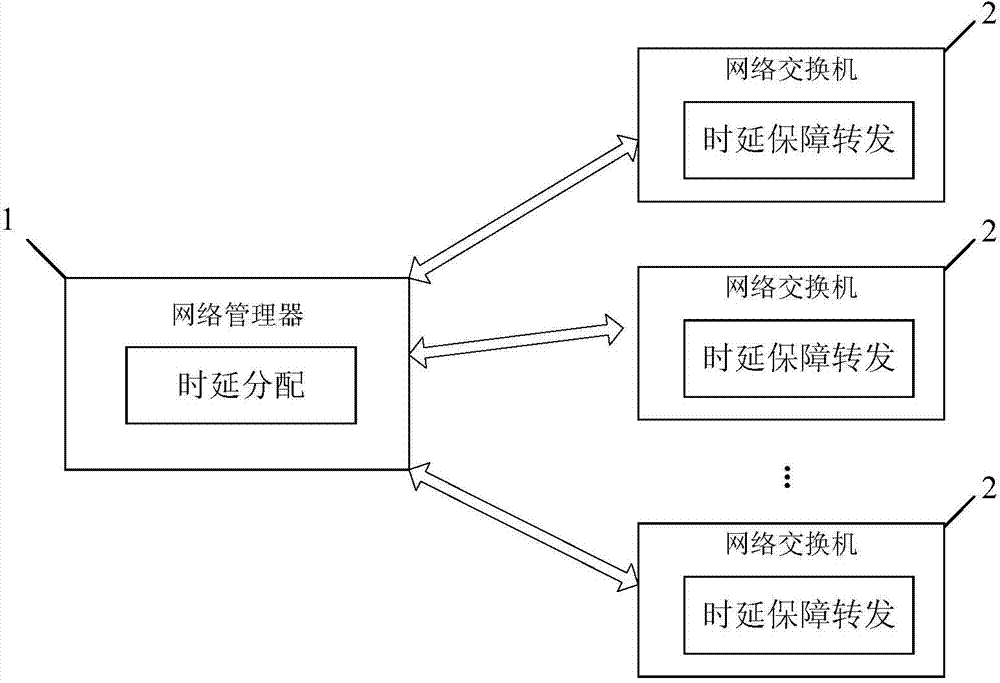

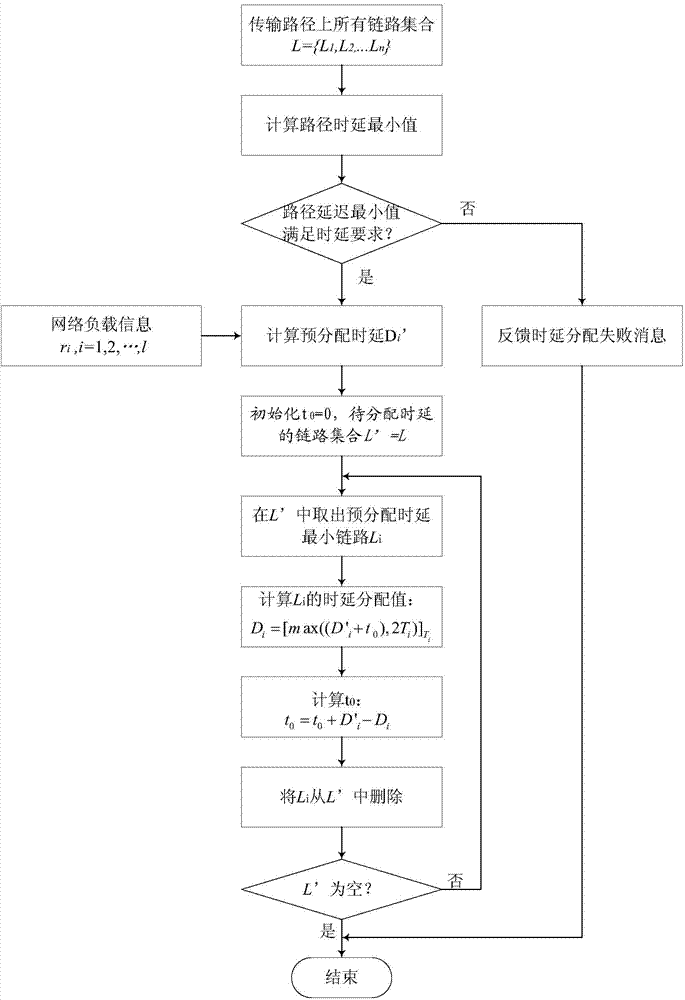

End-to-end time delay guarantee transmission scheduling method oriented to industrial backhaul network

ActiveCN104734991ARealize end-to-end latency guaranteeAchieve separationData switching networksDistribution methodBusiness data

Owner:SHENYANG INST OF AUTOMATION - CHINESE ACAD OF SCI

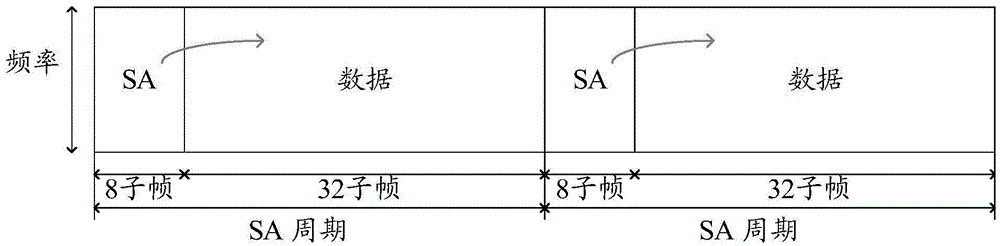

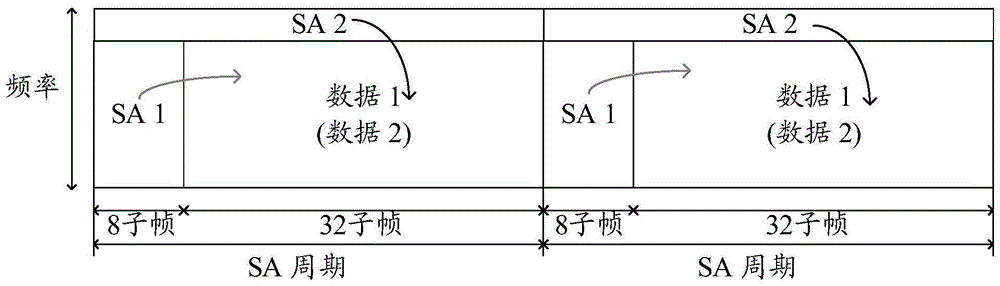

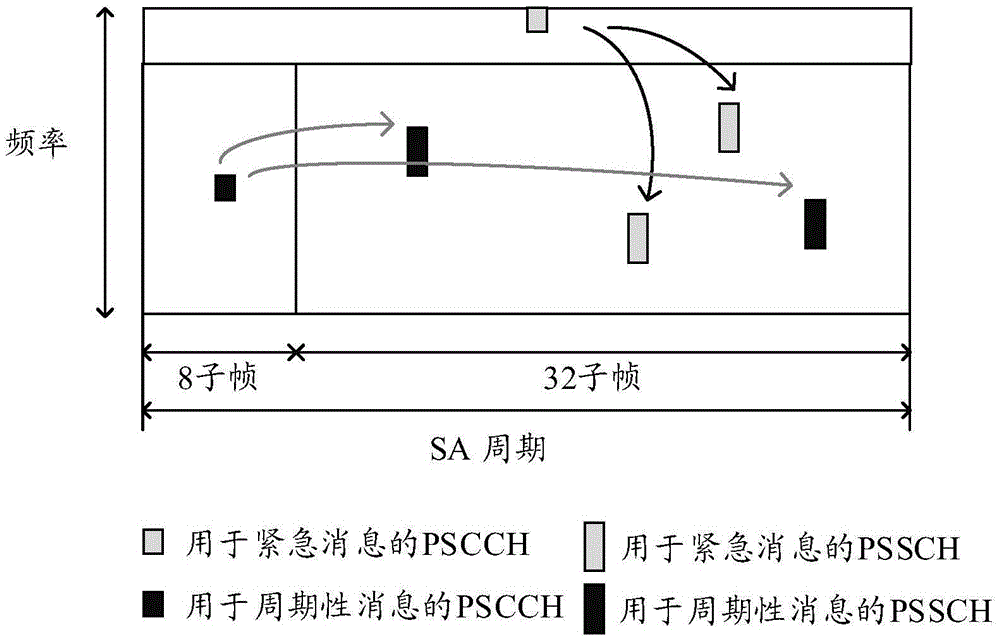

Method and apparatus for reducing delay in vehicle-to-vehicle communication

InactiveCN106658716AReduce transmission delaySatisfy latency requirementsNetwork traffic/resource managementResource poolIn vehicle

An embodiment of the disclosure provides a method and apparatus for reducing the delay in vehicle-to-vehicle communication. The method comprises the steps of allocating separate scheduling allocation resource pools for messages with different delay requirements; and performing frequency division multiplexing of a scheduling allocation resource pool for a first message requiring a lower delay and a corresponding data resource pool, to reduce the transmission delay of the first message. Compared with the prior art, the embodiment of the disclosure are effective in reducing the transmission delay of the emergency message, thus satisfying the delay requirements for vehicle safety message communication.

Owner:ALCATEL LUCENT SHANGHAI BELL CO LTD

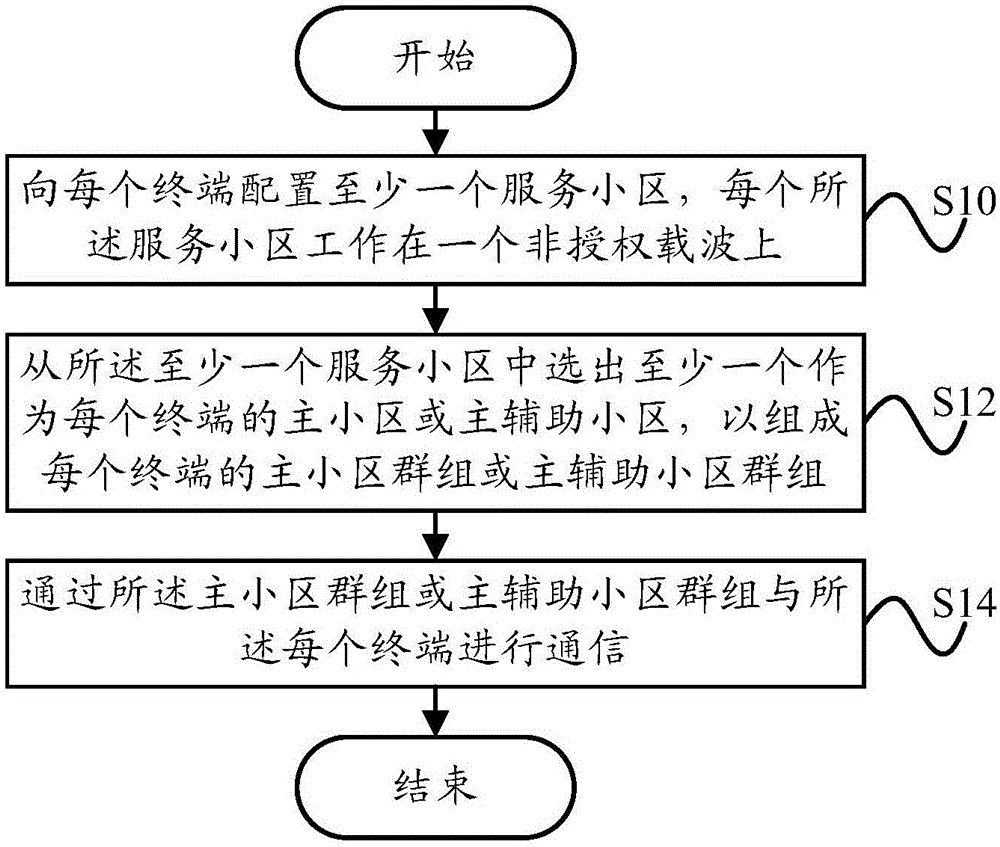

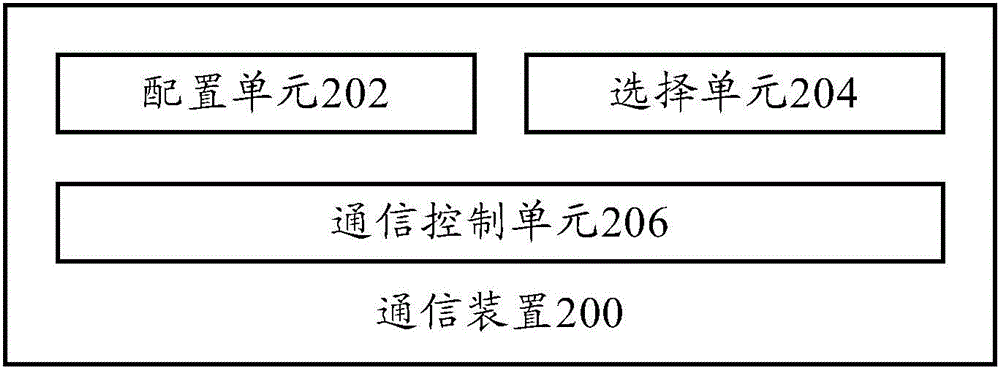

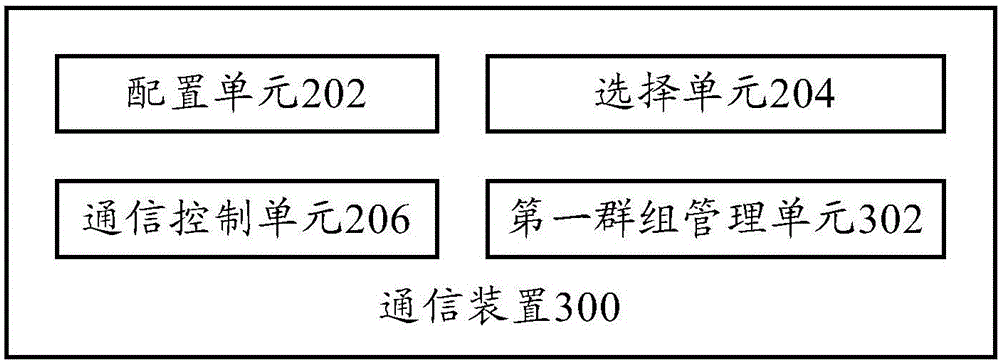

Communication method and communication device

ActiveCN106255122ASatisfy latency requirementsMeet efficiency requirementsNetwork planningTime delaysCarrier signal

The invention provides a communication method and a communication device. the communication method comprises steps: at least one service cell is configured to each terminal, and each service cell works on an unauthorized carrier; at least one is selected from the at least one service cell as a main cell or a main auxiliary cell for each terminal to form a main cell cluster or a main auxiliary cell cluster for each terminal; and according to the main cell cluster or the main auxiliary cell cluster, communication with each terminal is carried out. The technical scheme of the invention can improve the signal transmission probability in the main cell cluster or the main auxiliary cell cluster on the unauthorized carrier, the main cell cluster or the main auxiliary cell cluster can thus be ensured to transmit and receive necessary information and data timely and effectively, and communication time delay and efficiency requirements can be met.

Owner:YULONG COMPUTER TELECOMM SCI (SHENZHEN) CO LTD

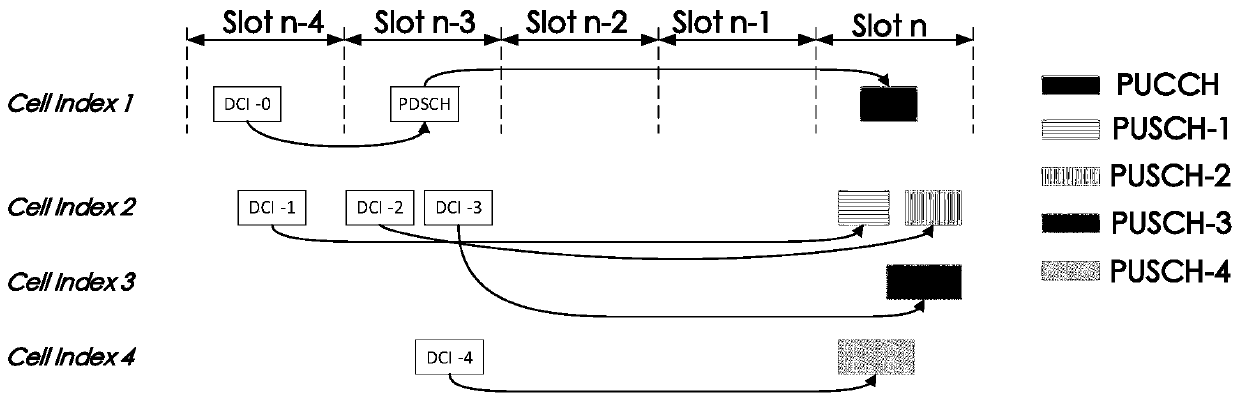

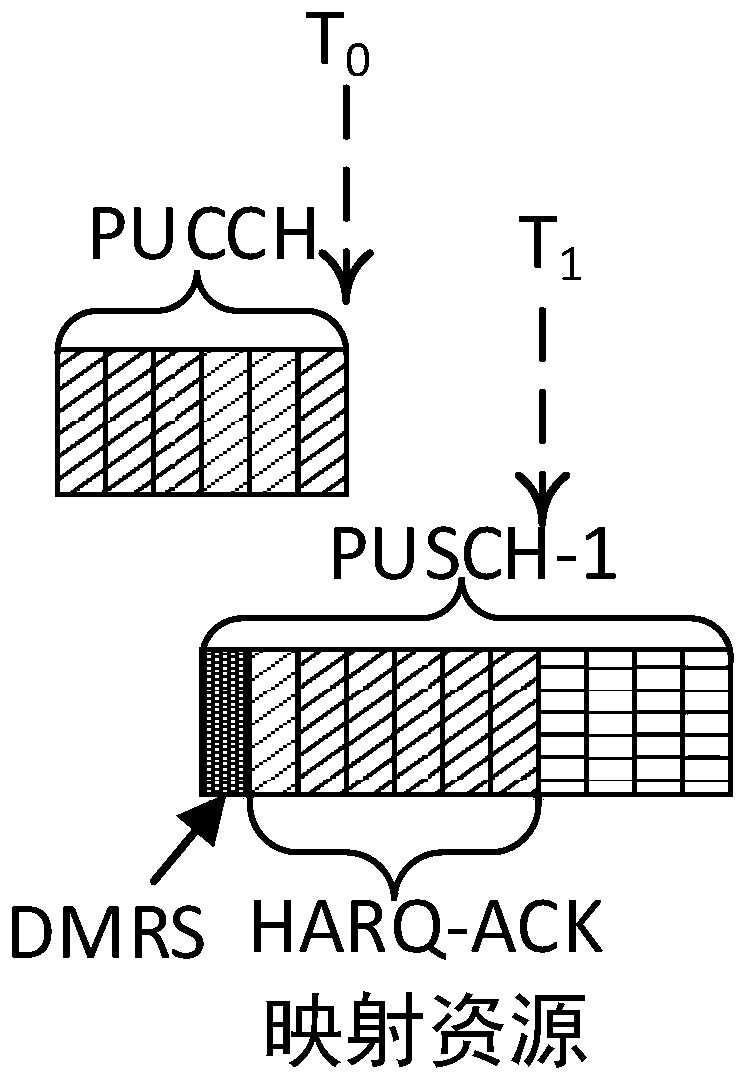

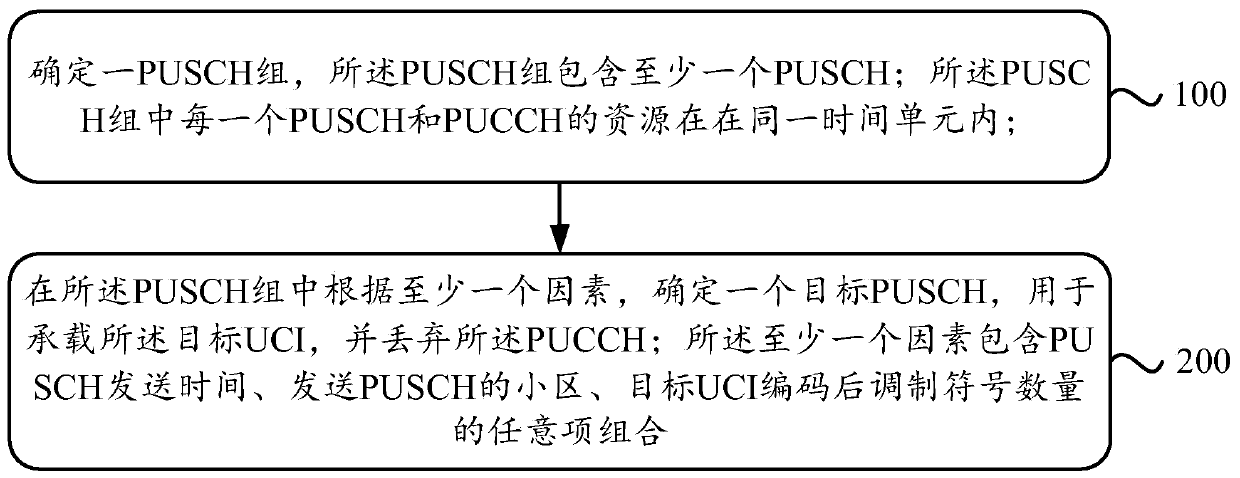

Uplink information multiplexing method and equipment

ActiveCN110768773AMeet reliability requirementsSatisfy latency requirementsSignal allocationWireless communicationMultiplexingComputer network

The invention discloses an uplink information multiplexing method. A PUSCH group comprises at least one PUSCH, and each PUSCH in the PUSCH group and the resources of a PUCCH are in the same time unit;the PUCCH comprises a target UCI (Uplink Control Information); a target PUSCH is determined in the PUSCH group according to at least one factor, the target PUSCH being used for bearing the target UCIand discarding the PUCCH; the at least one factor comprises any combination of the PUSCH sending time, a cell sending the PUSCH and the number of modulation symbols after target UCI coding. The invention further provides equipment applying the method. According to the method and the equipment, the problem of how to realize multiplexing of the UCI on the PUSCH by the service with high reliabilityrequirement and low time delay requirement is solved.

Owner:CHINA ACADEMY OF INFORMATION & COMM

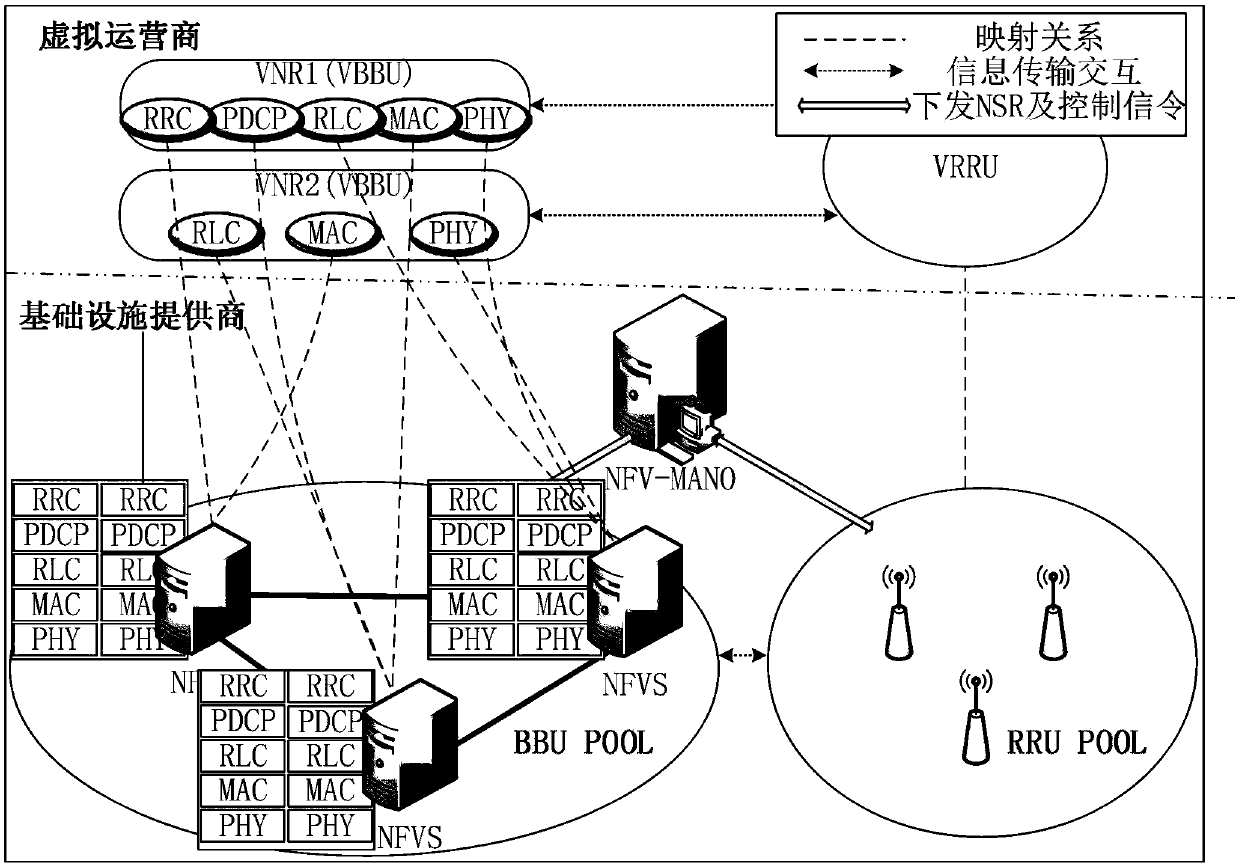

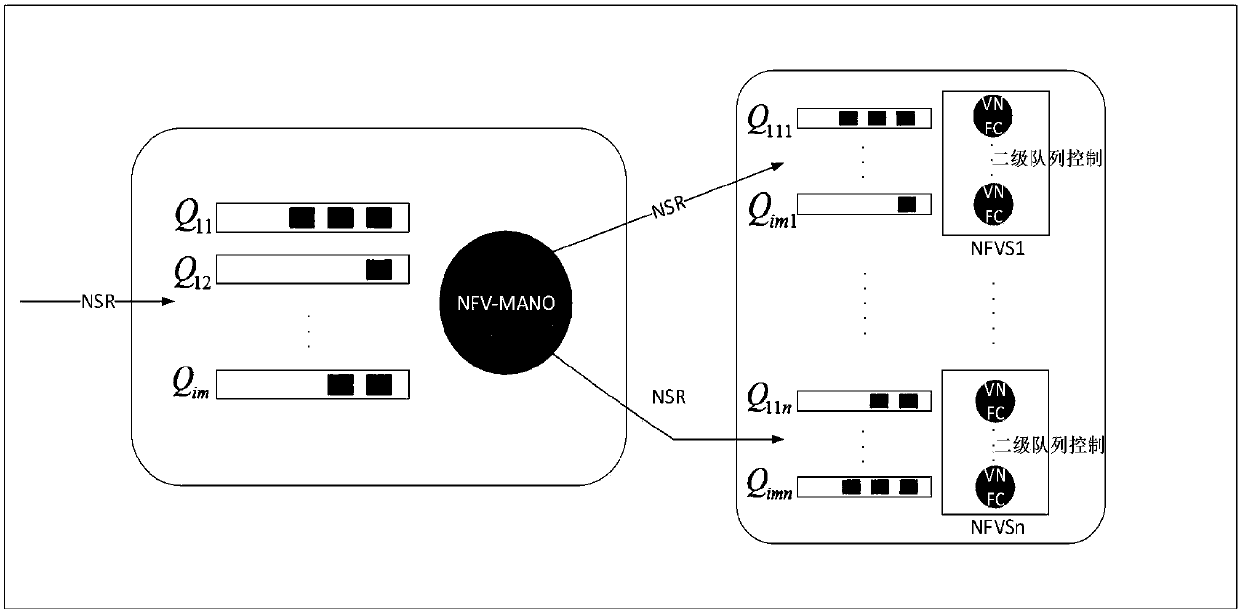

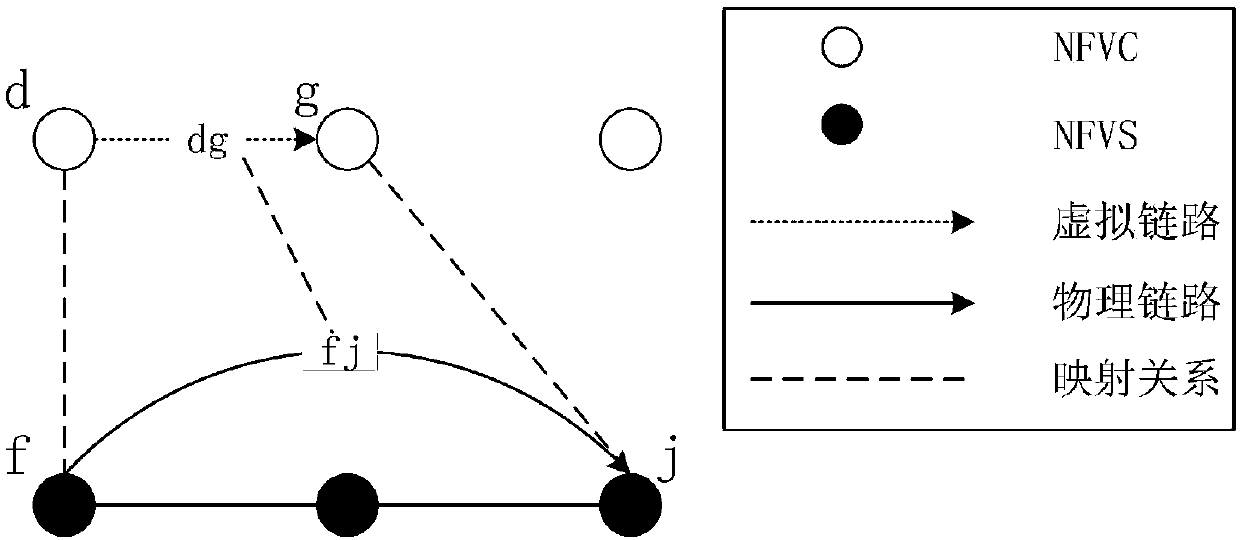

5G virtual access network mapping method in time delay sensing condition

The invention relates to a 5G virtual access network mapping method in the time delay sensing condition and belongs to the technical field of mobile communication. According to the method, the difference between the arrivals of virtual network requests, the dynamic occupation and release of limited physical resources, and the difference between the service capabilities of network function virtualization servers are combined, and then a queue state transfer equation is established at a network functional virtualization choreographer and each network function virtualization server. Meanwhile, atwo-stage queue dynamic scheduling method is provided. Furthermore, the queue states of all queues in the system are sensed, so that the queue dynamic scheduling is carried out to meet the time delayrequirement. Moreover, the mapping is completed by taking a minimum mapping cost as a target. According to the 5G virtual access network mapping method, the mapping cost can be minimized, and the timedelay requirement of the system can be met.

Owner:杭州余杭华数科技有限公司

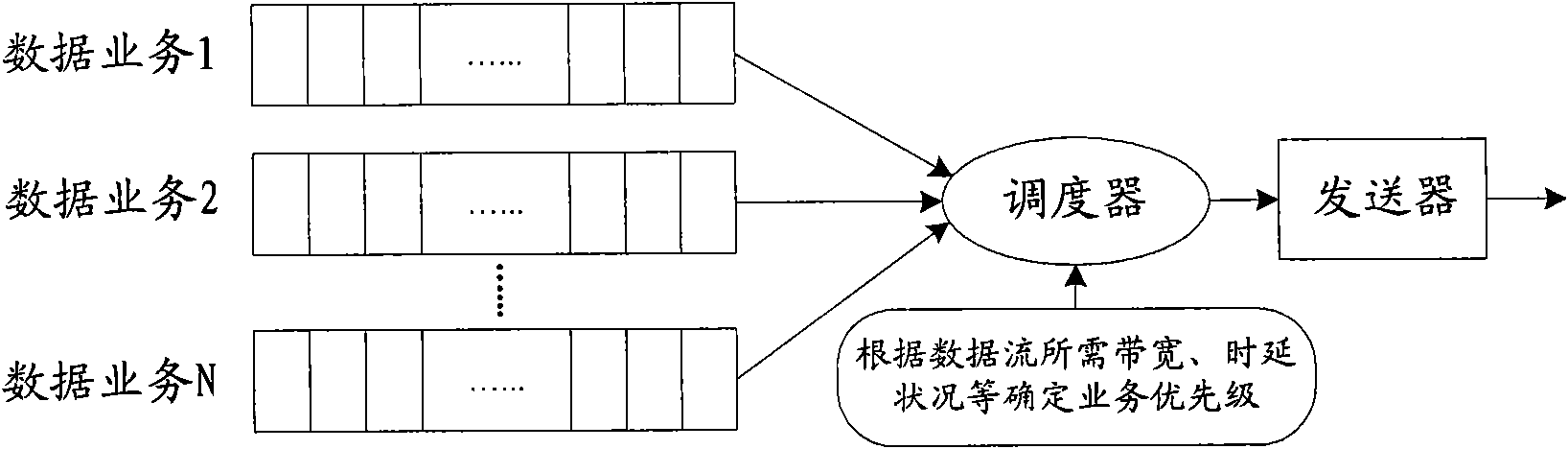

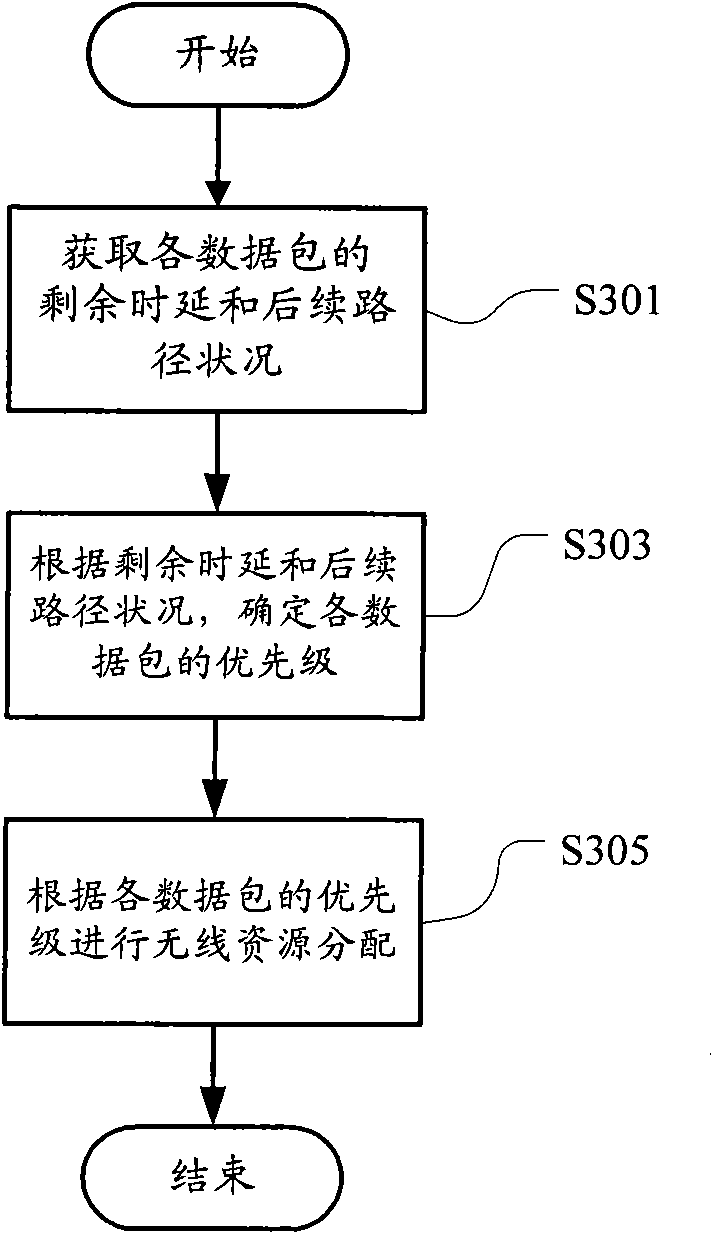

Method for packet scheduling of multi-hop network and node device

InactiveCN101645830AReduce the probability of being discardedEnsure fairnessData switching by path configurationWireless communicationTime delaysLarge capacity

The invention discloses a method for packet scheduling of a multi-hop network and a node device, wherein the method comprises the following steps of: acquiring residual time delay and follow-up routeconditions of all data packets; according to the residual time delay and following route conditions, determining the priority of the data packets; and according to the priority, allocating wireless resources to the data packets. The method has the advantages of effectively ensuring the packet scheduling of the high-capacity wireless multi-hop network meets the requirements of the data service on time delay, lowering the probability of discarding of the data packet with more residual hop counts, ensuring the fairness of the packet data services undergoing different hop counts, and avoiding waste of network resources.

Owner:CHINA MOBILE COMM GRP CO LTD

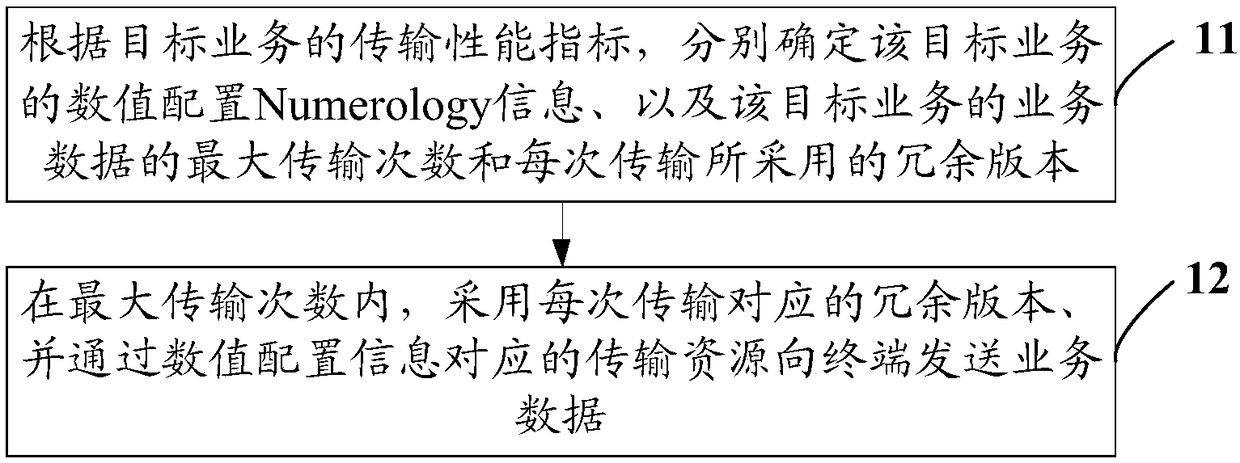

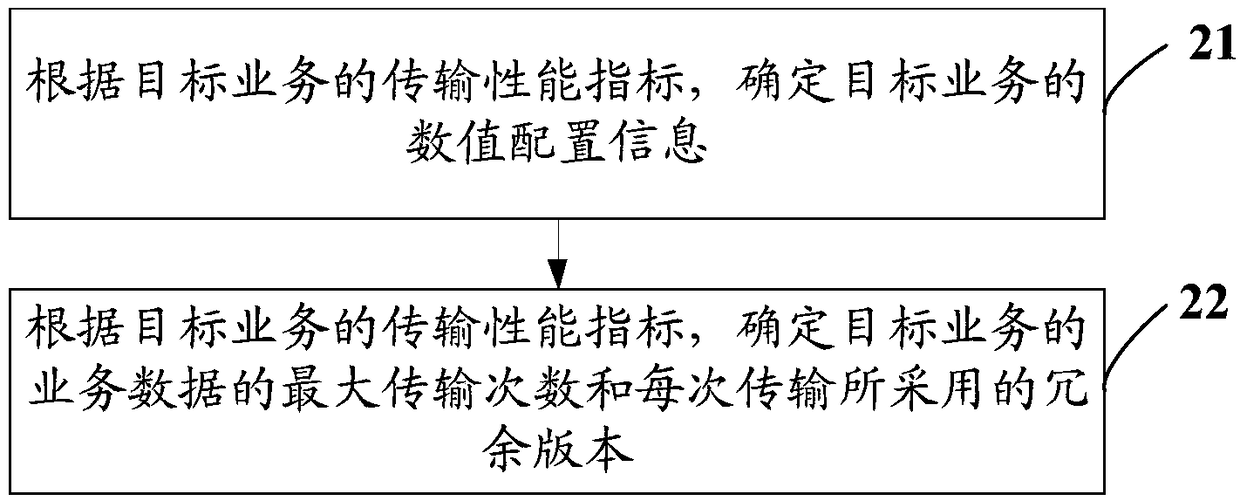

Service data transmission method, base station and terminal

InactiveCN108667572AGuaranteed Latency RequirementsGuaranteed transmission reliabilityError prevention/detection by using return channelComputer terminalNumerology

The invention discloses a service data transmission method, a base station and a terminal. The method comprises the following steps: determining numerical value configuration Numerology information oftarget service, the maximum transmission times of the service data of the target service and a redundancy version adopted in every transmission according to a transmission performance indicator of the target service; and within the maximum transmission times, sending the service data to the terminal through a transmission resource corresponding to the numerical value configuration information byadopting the redundancy version corresponding to every transmission. The base station disclosed by the invention determines the numerical value configuration information according to the transmissionperformance indicator of the generated service to ensure the delay requirements of the service transmission, and further determines the maximum transmission times and the redundancy version adopted in every transmission according to the transmission performance indicator of the generated service to ensure the transmission reliability of the service data. If the transmission performance indicatorsof the service are different, various parameters configured to the service are different so as to meet different reliability and delay requirements.

Owner:维沃软件技术有限公司

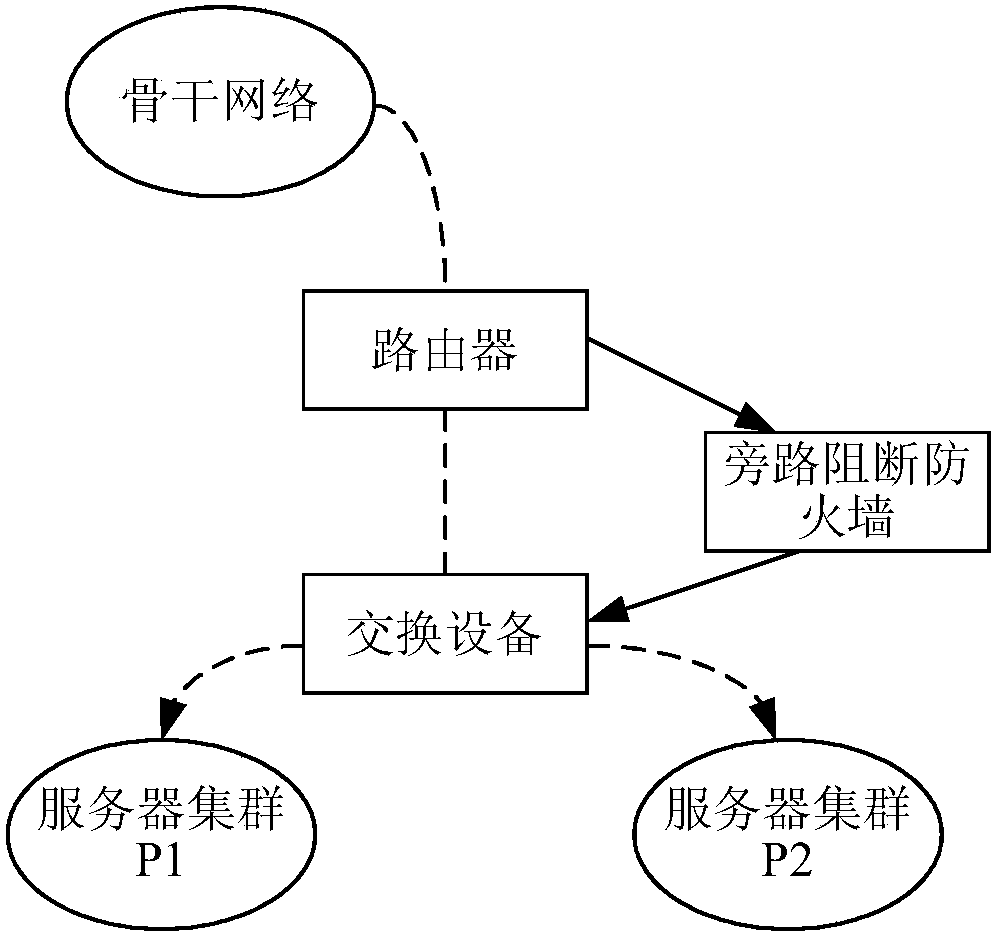

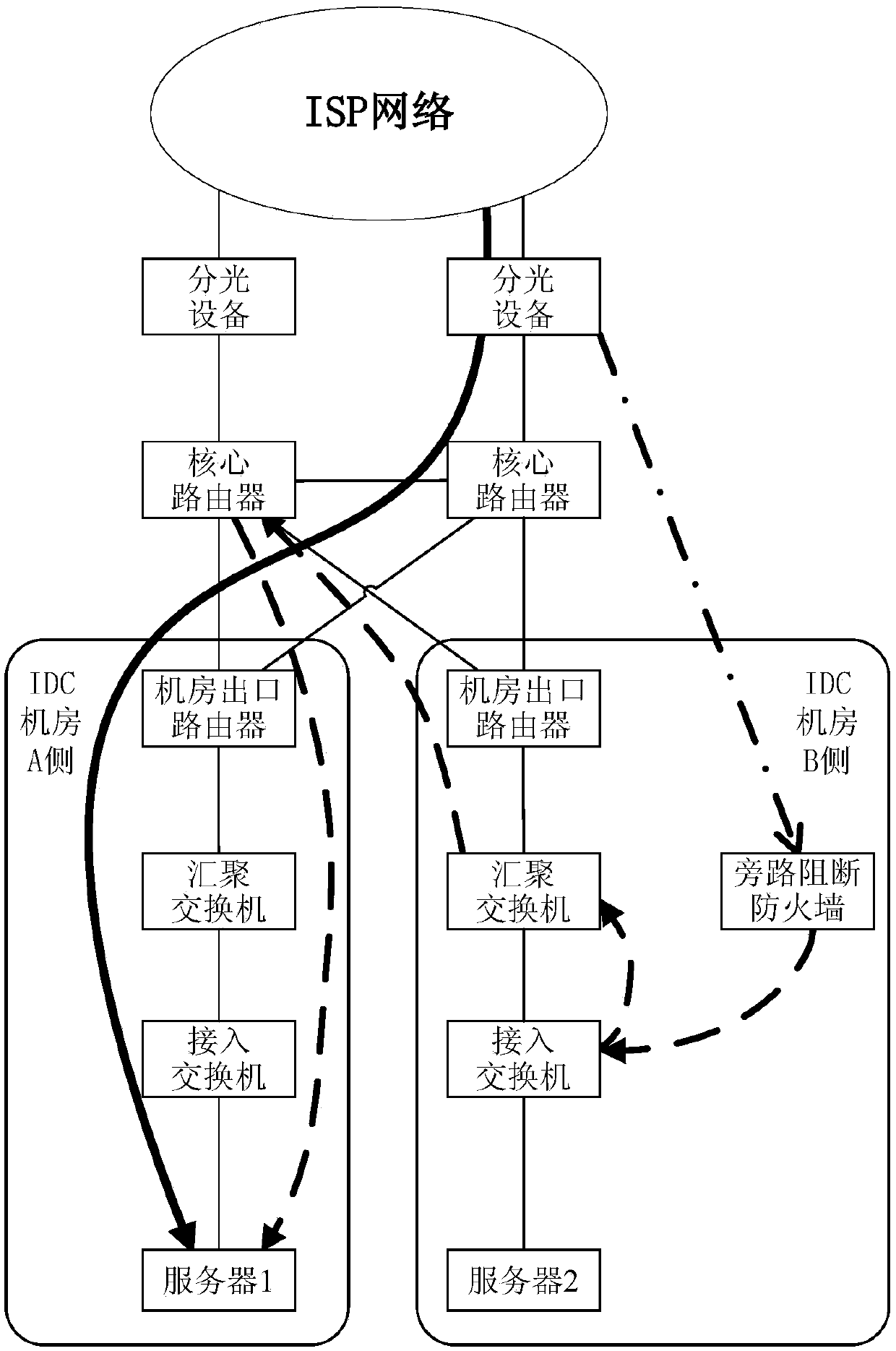

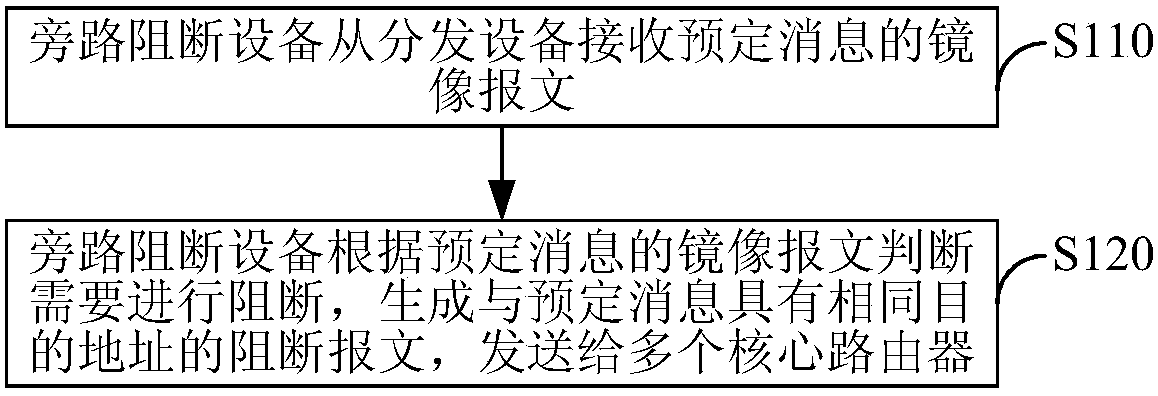

Bypass blocking method, device, system, and electronic device

ActiveCN107645470AReduce deployment dependenciesReduce the difficulty of deploymentNetworks interconnectionTTEthernetTelecommunications

The invention provides a bypass blocking method, device, system, and electronic device. The bypass blocking method comprises the steps that a bypass blocking device receives a mirror image report of predetermined message from a distributing device, wherein the distributing device is used for distributing the downstream data of an Internet service provider (ISP network); the bypass blocking devicedetermines whether blocking is required or not based on the mirror image report of the predetermined message, and generates a blocking report having the same destination address as the predetermined message, and sends the blocking report to a plurality of core routers. The invention is advantageous in that the disposition difficulty and cost of bypass blocking can be reduced, and the time-delay demand of the bypass blocking can be guaranteed to a certain degree.

Owner:ALIBABA GRP HLDG LTD

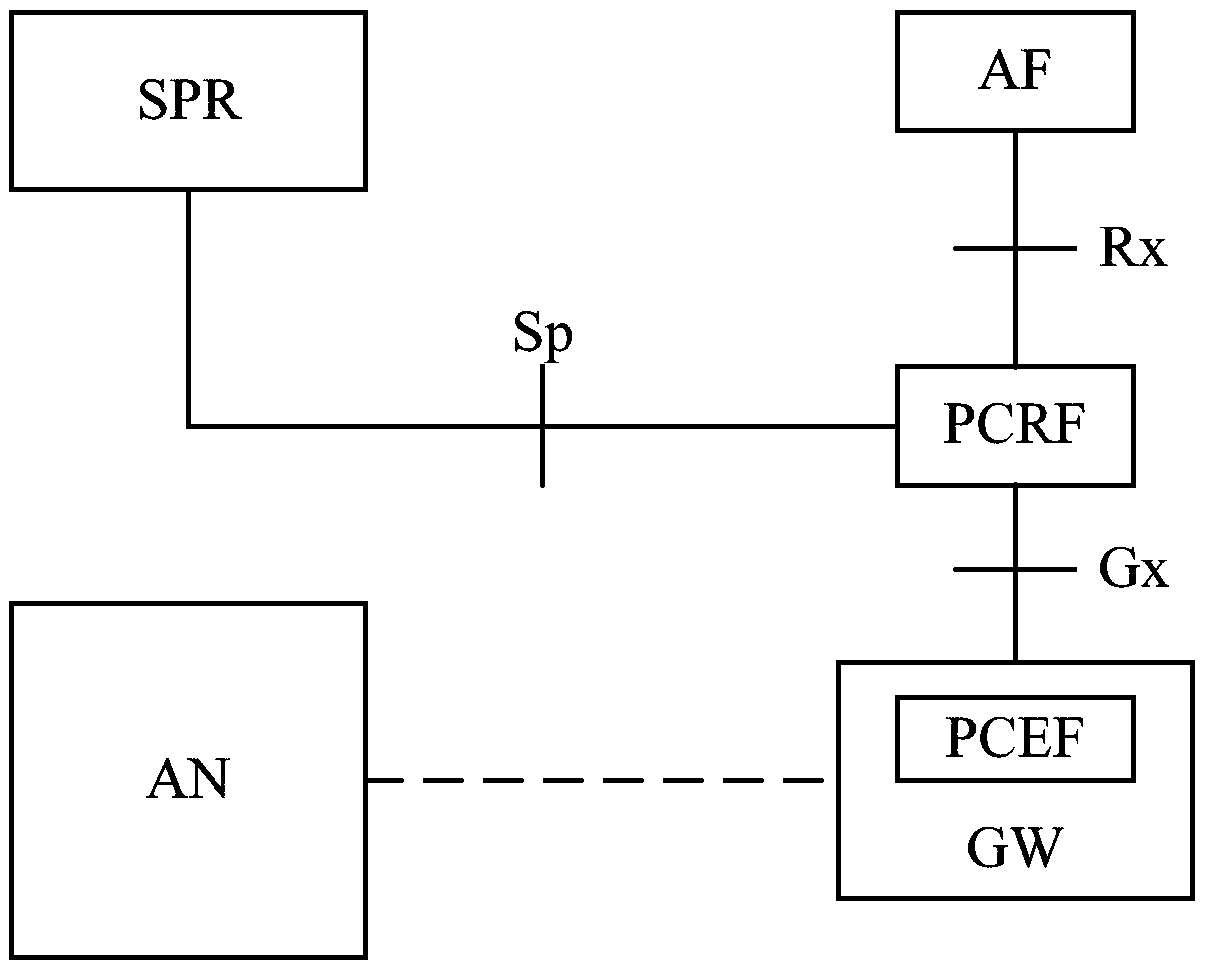

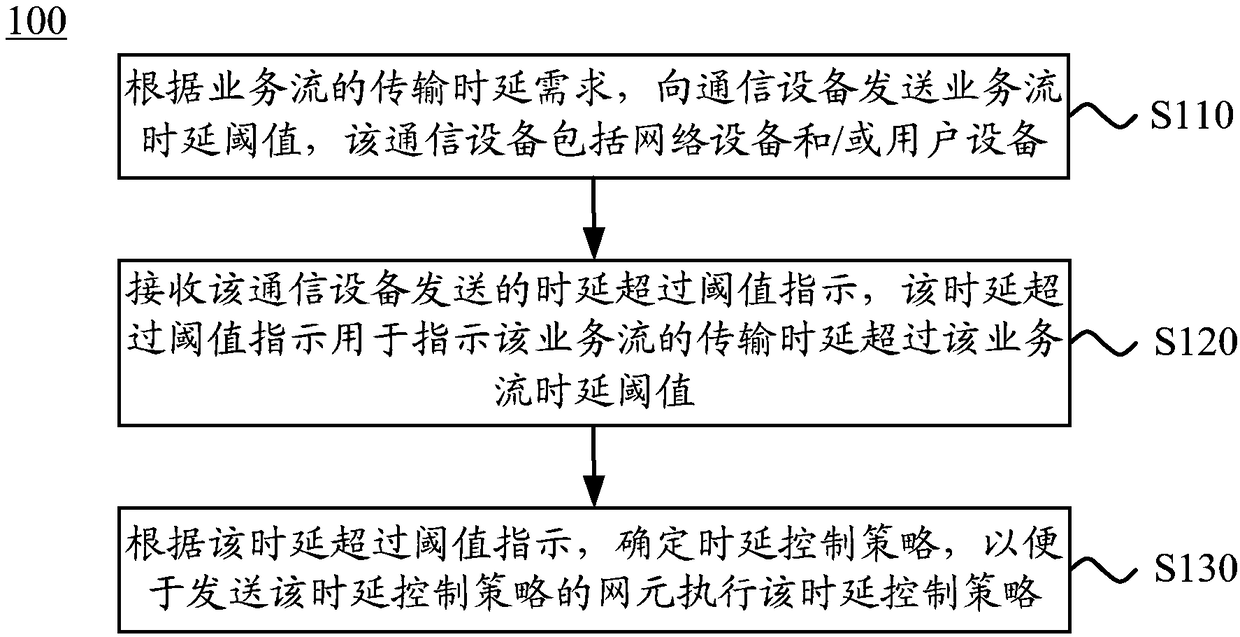

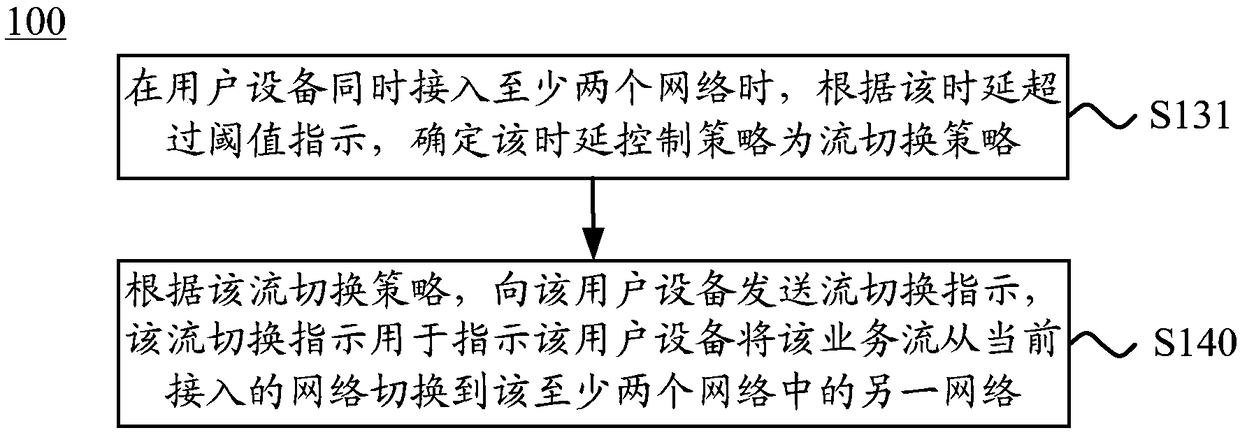

Method for controlling network transmission time delay, service quality control entity, and communication device

InactiveCN109245936AMeet end-to-end latency requirementsSatisfy latency requirementsNetwork traffic/resource managementData switching networksQuality of serviceService flow

The invention discloses a method for controlling network transmission time delay, a service quality control entity, and a communication device. The method includes the steps: sending a traffic flow delay threshold to a communication device according to a transmission delay requirement of a service flow, wherein the communication device includes a network device and / or user equipment; receiving a time-delay-exceeding-threshold indication send by the communication device, wherein the time-delay-exceeding-threshold indication is used to indicate that the transmission delay of the service flow exceeds the service flow delay threshold; and determining a delay control strategy according to the time-delay-exceeding-threshold indication, so that the communication device that sends the delay control strategy performs the delay control strategy. According to the invention, the method monitors the network transmission delay by setting a service flow delay threshold, and when determining that thetransmission delay of the service flow cannot be satisfied, sets a time delay control strategy to dynamically adjust the network transmission delay, and improves the user experience.

Owner:HUAWEI TECH CO LTD

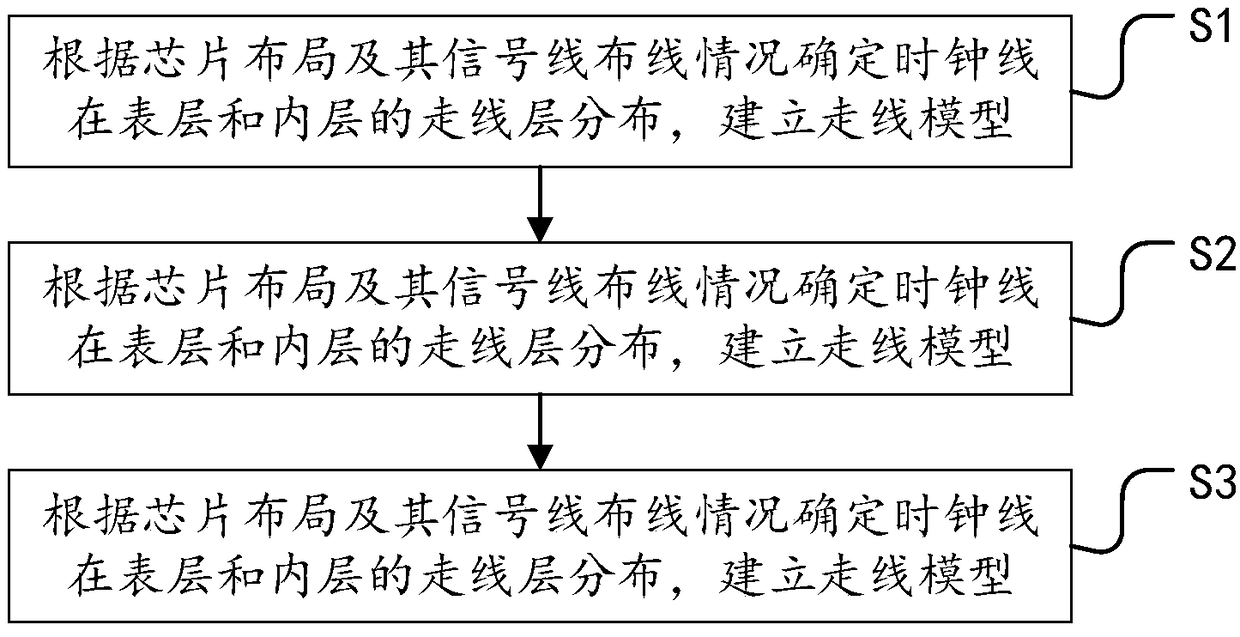

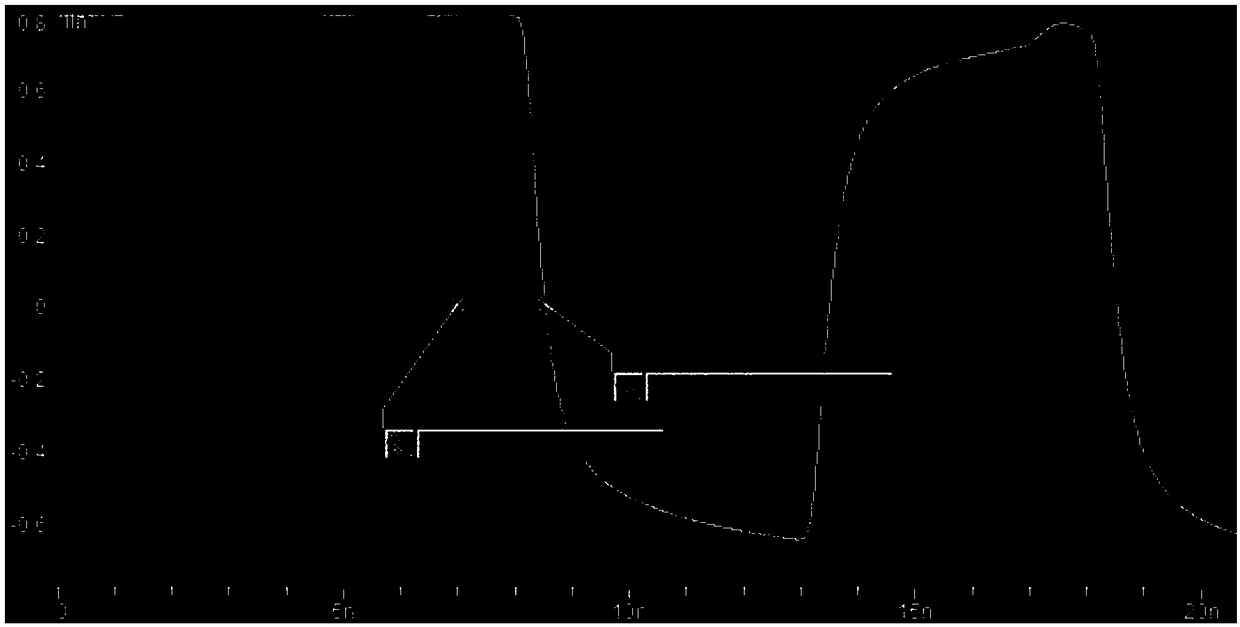

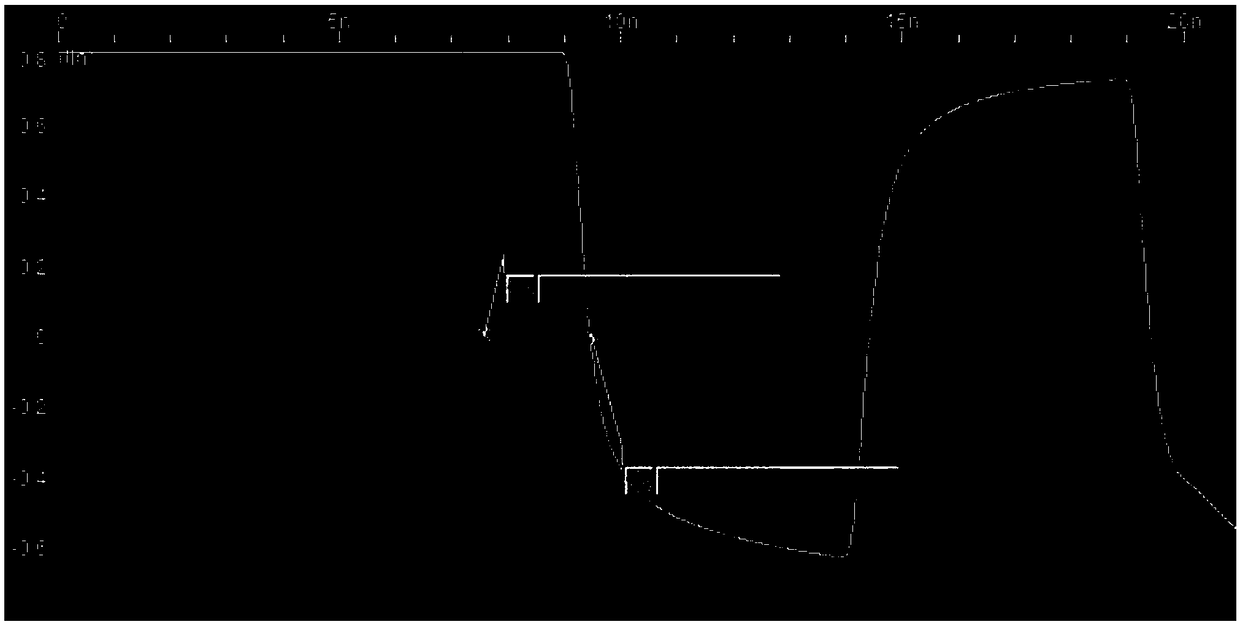

High-speed signal optimization method and system for reference clock lines

ActiveCN108763734AOptimized designReasonable designSpecial data processing applicationsLink designVIT signals

The invention provides a high-speed signal optimization method and system for reference clock lines. The method comprises the following steps: S1, determining routing layer distributions of clock lines in a surface layer and an inner layer according to chip layout and signal line wiring condition thereof, and building a routing model; S2, obtaining lamination information of a simulation waveform based on the routing model, and evaluating propagation speeds of signals in the surface layer and the inner layer; and S3, setting routing lengths in the surface layer and the inner layer by combiningan equal length requirement and a time delay requirement and according to the signal propagation speeds. The method provided by the invention has the advantages that the routing layer distributions ofthe clock lines are determined, the signal propagation speed of each routing layer is calculated according to the laminate information of the simulation waveform, and finally the length of each routing layer is set by combining the equal length requirement and the time delay requirement, so that optimal design of a clock signal line is realized, on the basis that physical equal length is met, thetime delay requirement is also met, a link design risk is reduced, formation of unforeseeable problems is avoided, system design success rate is improved, and signal quality is enhanced.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

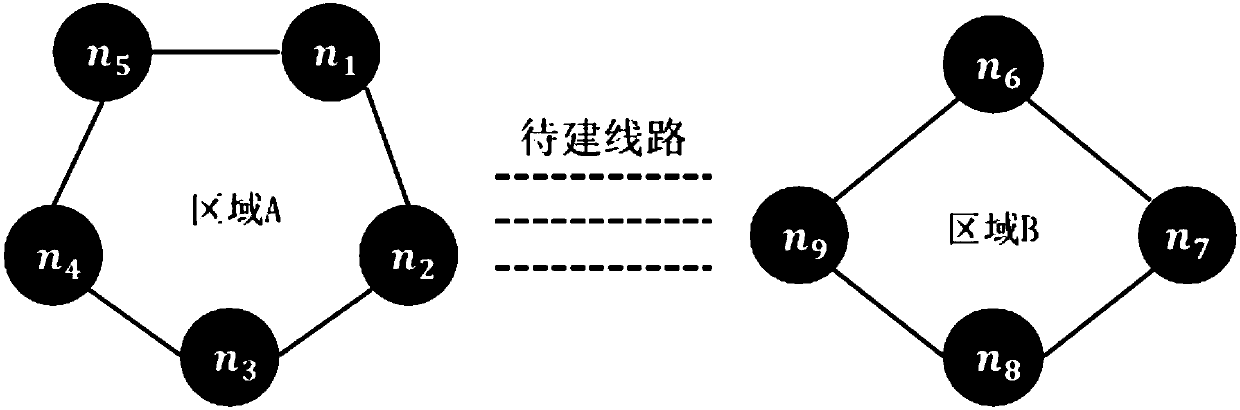

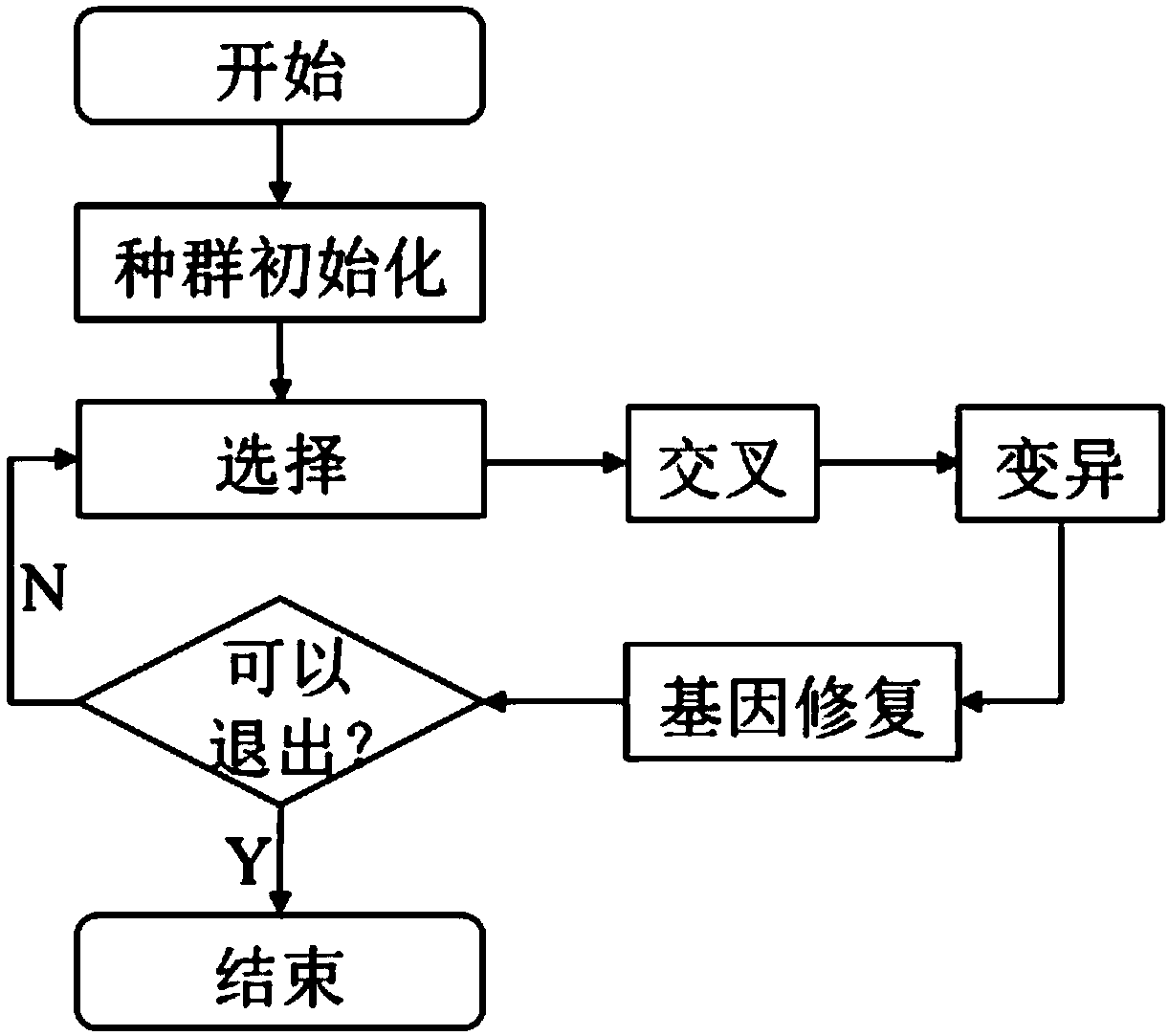

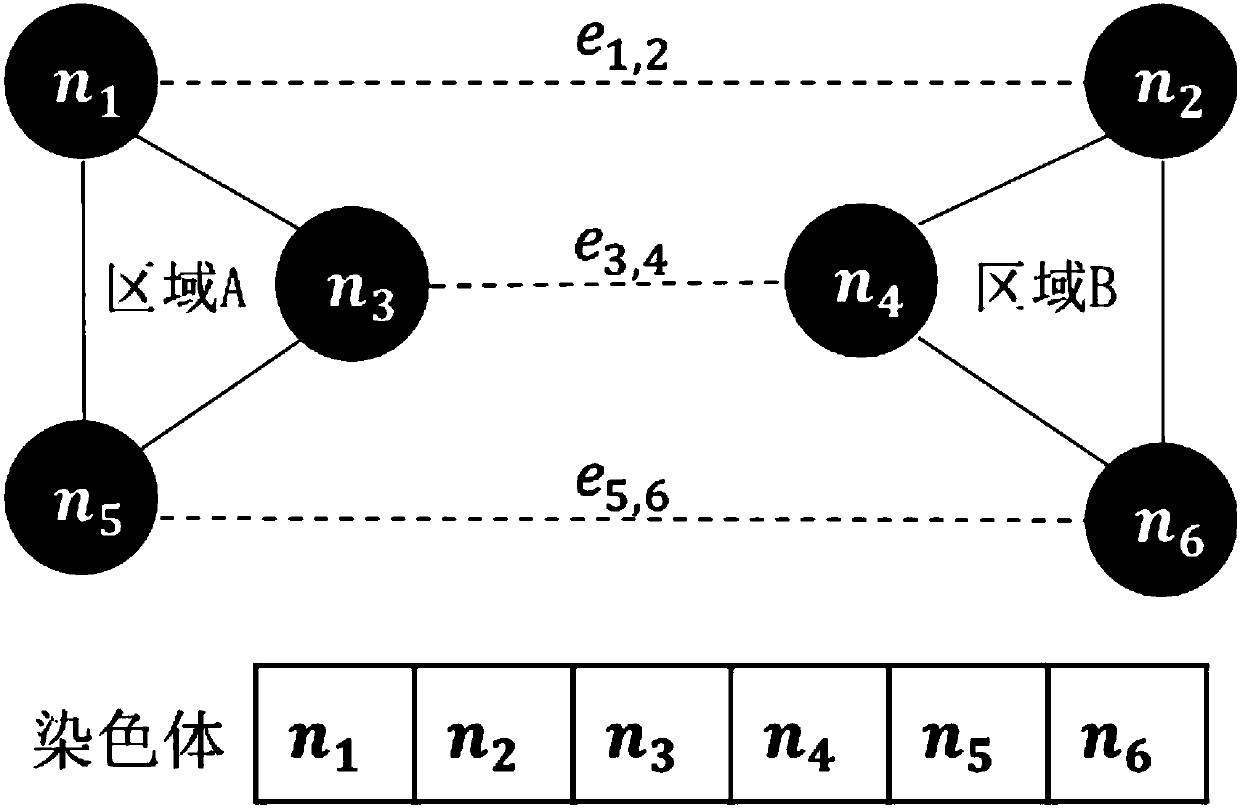

Cross-region power system protection communication network planning method

ActiveCN108880886ASatisfy latency requirementsReduce riskData switching networksGenetic algorithmsFirst generationVariable length

The invention relates to a cross-region power system protection communication network planning method, comprising the steps of initializing a first generation of populations through adoption of a variable-length chromosome coding method; setting a fitness function, and evaluating fitness of chromosomes according to features of target populations; selecting parental chromosomes according to the fitness function, specifically, selecting the parental chromosomes through adoption of a selection operator, thereby enabling the parental chromosomes to be inherited by a next generation; carrying out cross processing on the parental chromosomes, and generating new chromosomes, thereby improving diversity of species; carrying out variation processing on the parental chromosomes after the cross processing, thereby improving searching capability of the populations; and combining the parental chromosomes and the newly generated chromosomes, as descendants of a current generation of populations, carrying out a next round of evolution until the preset generation number is realized, exiting a loop, and obtaining a final planning scheme, namely the chromosomes with the highest fitness in the last generation of populations. According to the method, a demand of line protection business for delay can be satisfied.

Owner:STATE GRID INFORMATION & TELECOMM BRANCH +3

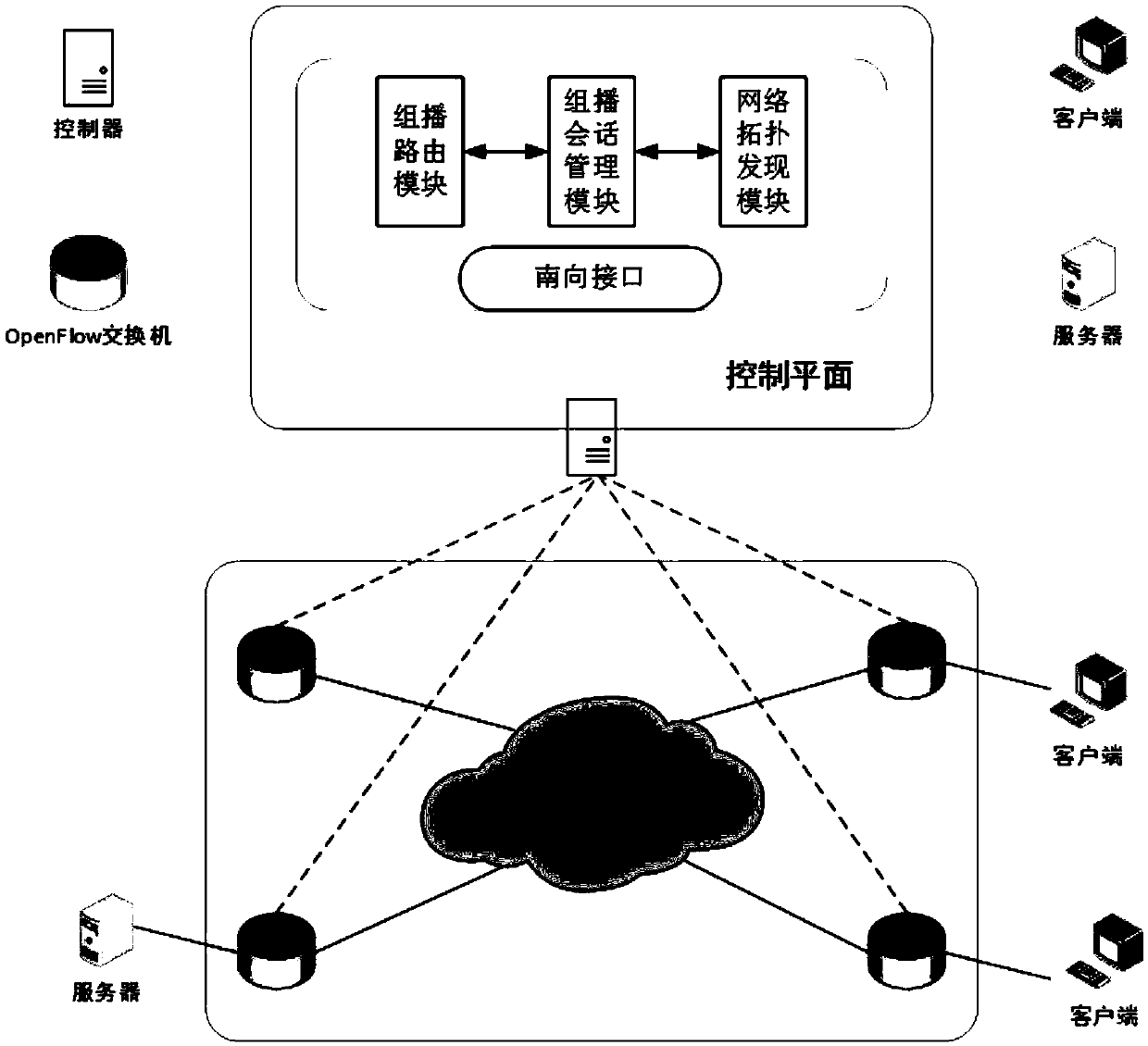

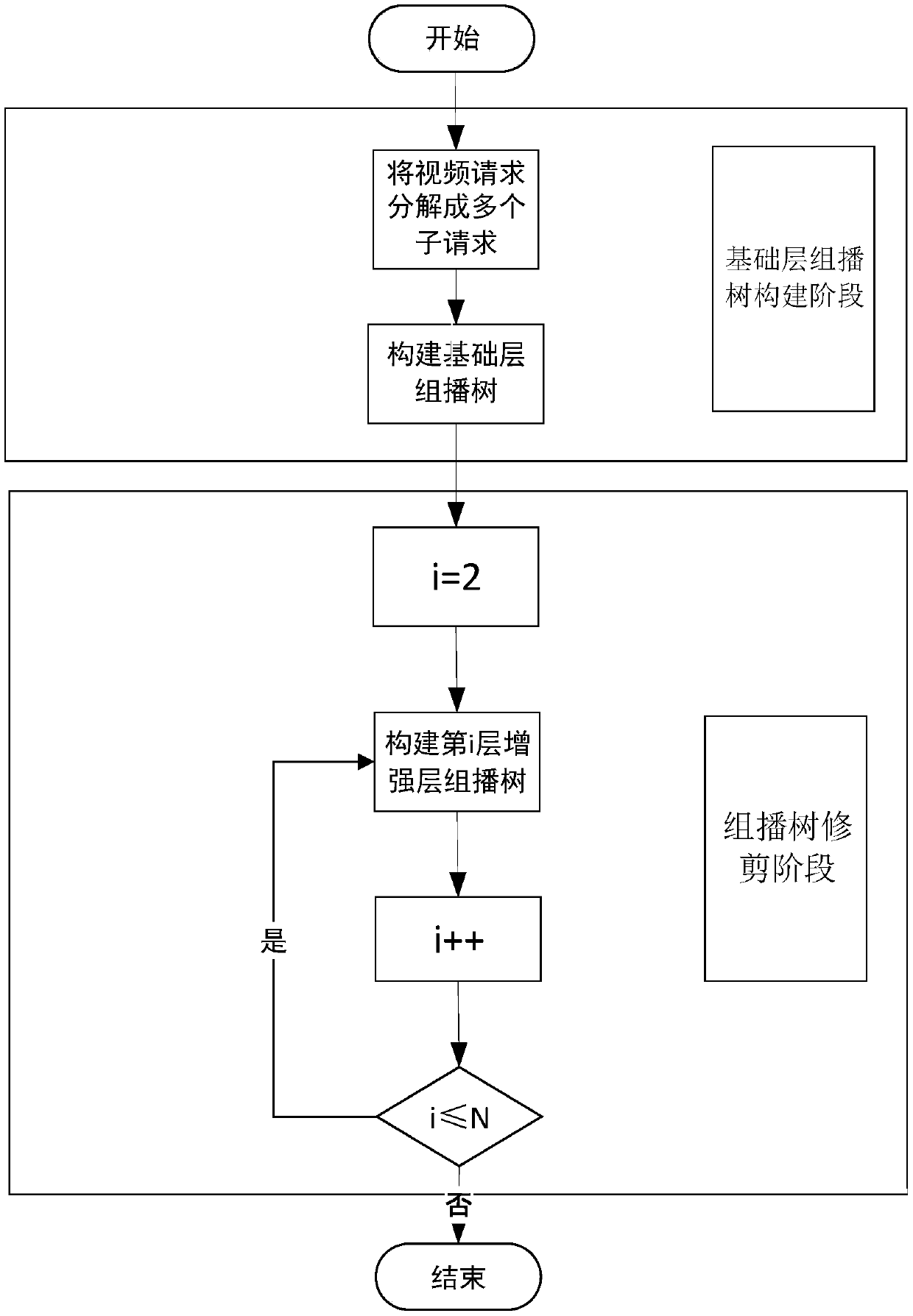

Scalable video stream multicast method based on QoS intelligent perception in SDN environment

ActiveCN109005471AGuaranteed network quality service experienceSatisfy latency requirementsSpecial service provision for substationSelective content distributionClient-sideMulti path routing

The invention discloses a scalable video stream multicast method based on QoS intelligent perception under SDN environment, which comprises: firstly decomposing a video request into a plurality of sub-requests, then searching a path conforming to network quality service requirements from a client to a server for each sub-request, and finally constructing a base layer multicast tree; and then constructing the enhancement layer multicast tree from the bottom up. When constructing the enhancement layer multicast tree, the current enhancement layer multicast tree is obtained from the upper layer multicast tree through the pruning operation, and then the congested links are rerouted in turn. Through such a bottom-up process, the invention can effectively reduce the number of links occupied by the multicast session and the number of group tables distributed, thereby improving the scalability of the video multicast session. At the same time, the invention adopts the method of multi-path routing to transmit the layered video stream, thereby effectively utilizing the link bandwidth resources in the network and improving the network quality service experience of the user.

Owner:ANHUI UNIVERSITY