Low-delay dual-mode lockstep soft error tolerance processor system

A processor system and processor technology, applied in the directions of non-redundancy-based fault handling, response error generation, etc., can solve problems such as low accuracy, large delay time of the processor system, and no consideration of soft errors.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

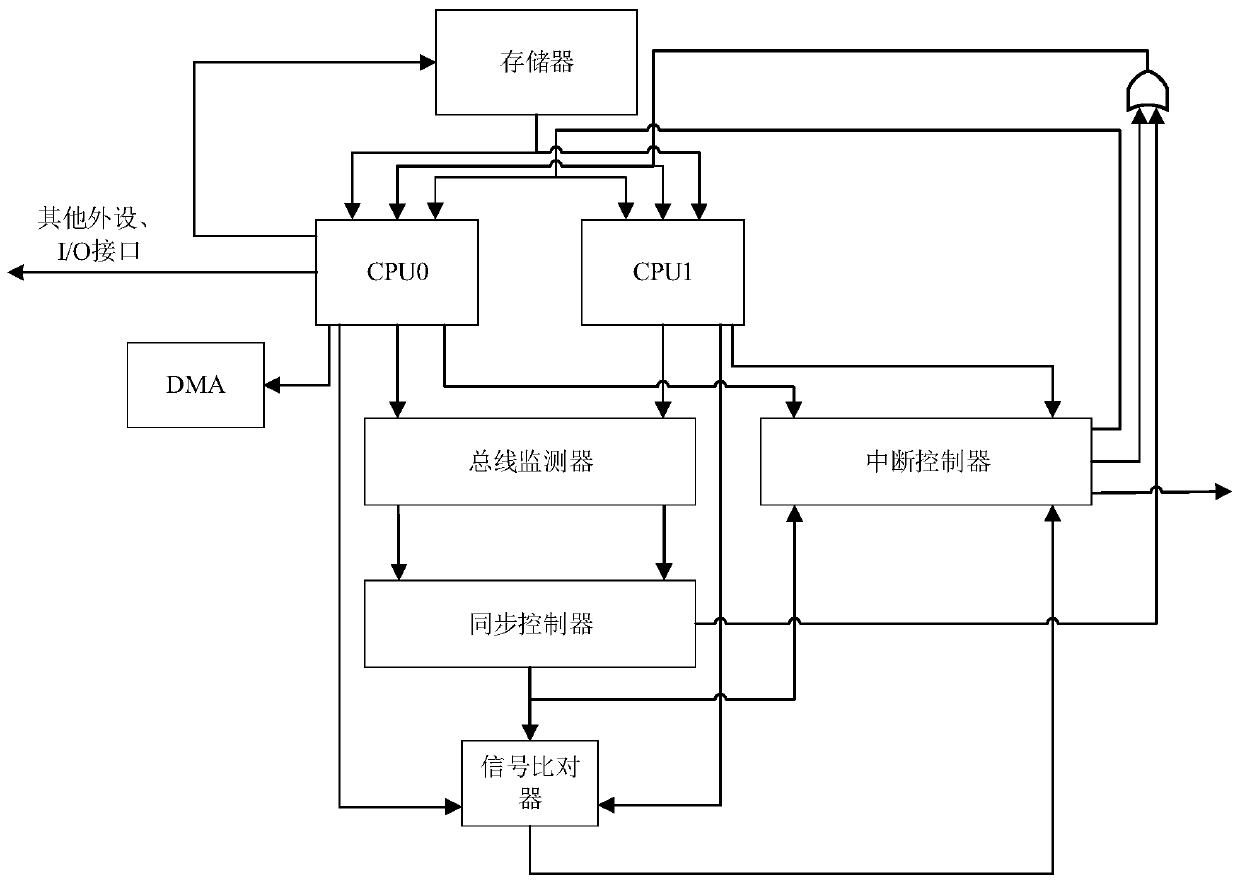

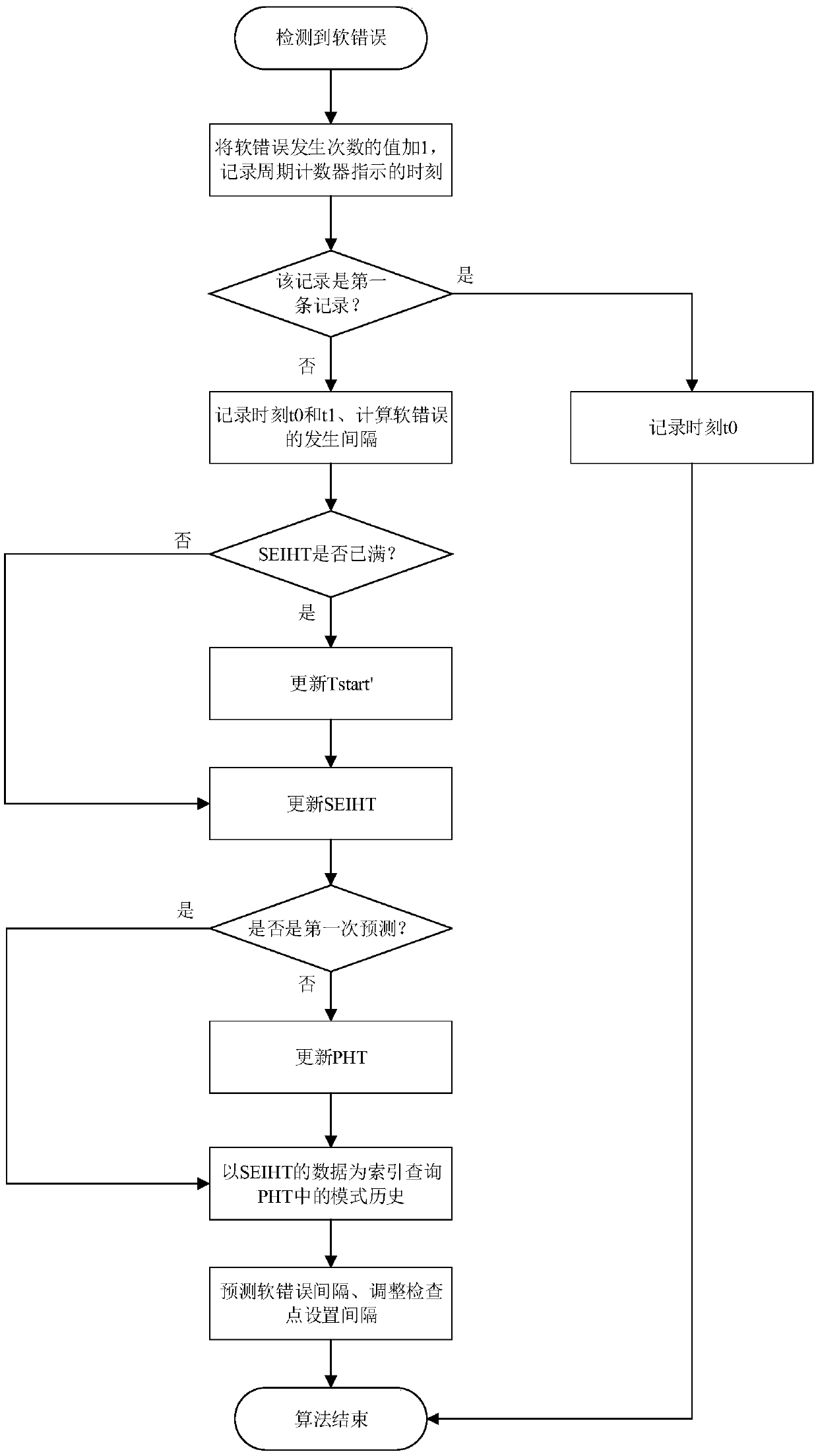

[0097] This embodiment provides a low-latency dual-mode lockstep soft error-tolerant processor system. For the hardware architecture diagram, see figure 1 , the system includes: memory, two identical processors CPU0 and CPU1, DMA, bus monitor, synchronous controller, signal comparator and interrupt controller; the system realizes the instruction level parallelism of dual processors, to The two processors CPU0 and CPU1 perform a bit-level comparison for soft error detection.

[0098] The low-latency dual-mode lockstep-tolerant soft error handler system has three sub-functions:

[0099] 1. Soft error detection function: Through the bus controller and the synchronization controller, the processors CPU0 and CPU1 realize instruction-level parallelism, and then perform bit-level comparison of the two processors CPU0 and CPU1 through the signal comparator to realize lockstep Soft error detection for processor systems;

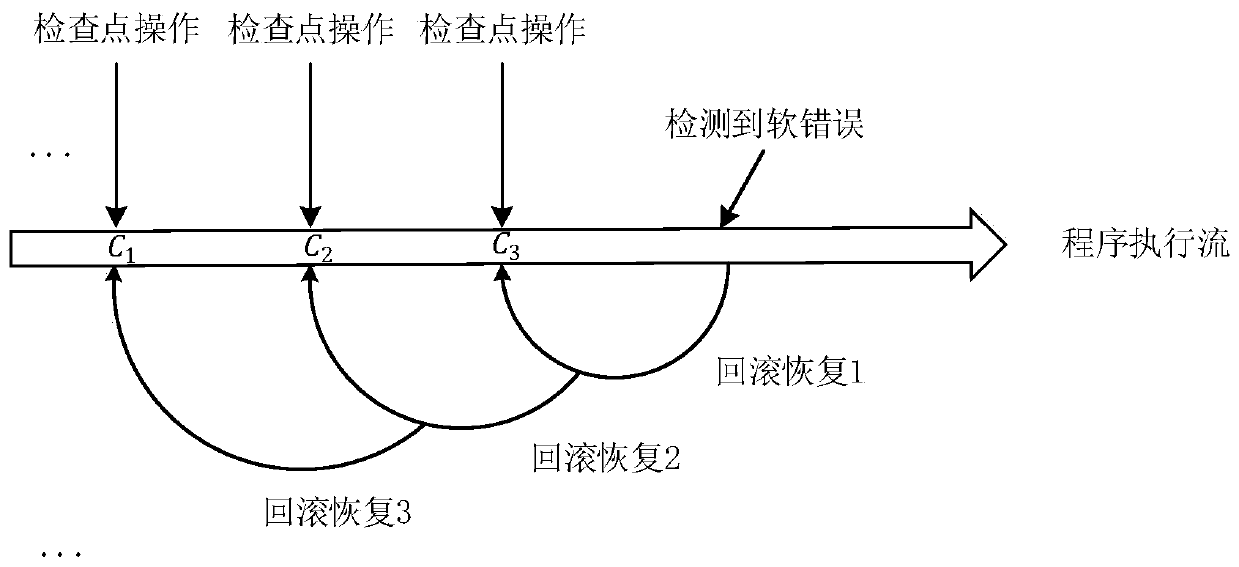

[0100] 2. Pervasive checkpoint and rollback recovery: The perv...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More