Dynamic self-adaptive SRAM type FPGA system fault tolerance method based on BRAM detection

A dynamic self-adaptation and system fault-tolerant technology, which is applied in the direction of non-redundancy-based fault handling, response error generation, and architecture with a single central processing unit, can solve problems such as high availability and low execution performance, and improve efficiency , Improve availability, solve the effect of unbalanced availability and performance resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The specific implementation method described in the present invention takes the Virtex-4 XQR4VSX55 SRAM FPGA which can realize dynamic partial reconstruction launched by Xilinx as an example, which can be dynamically reconstructed.

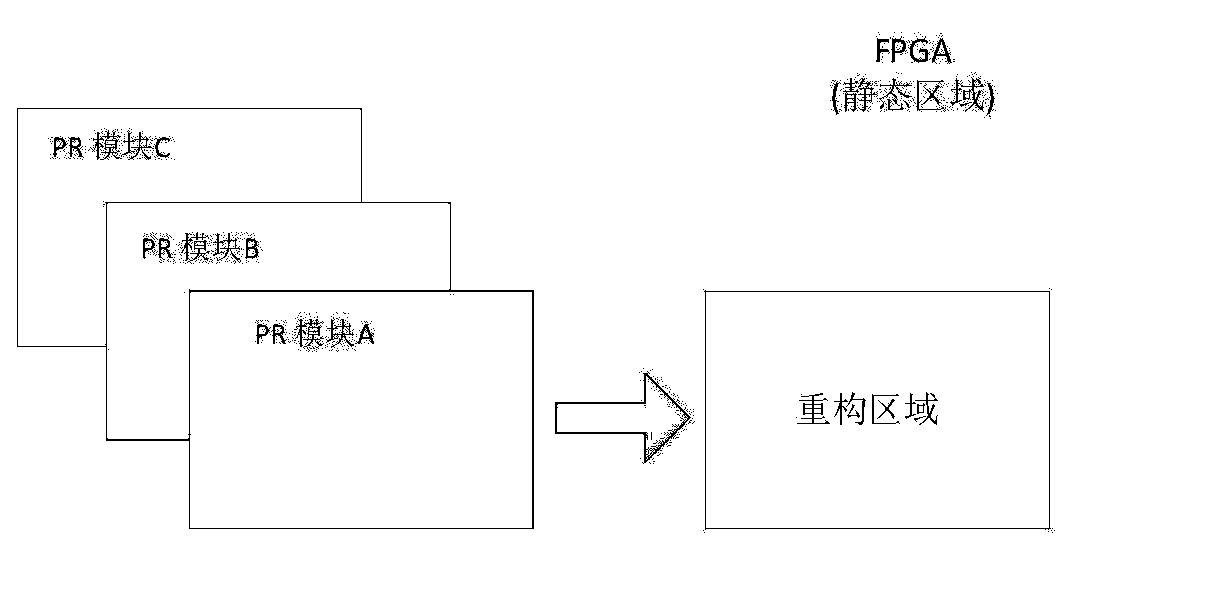

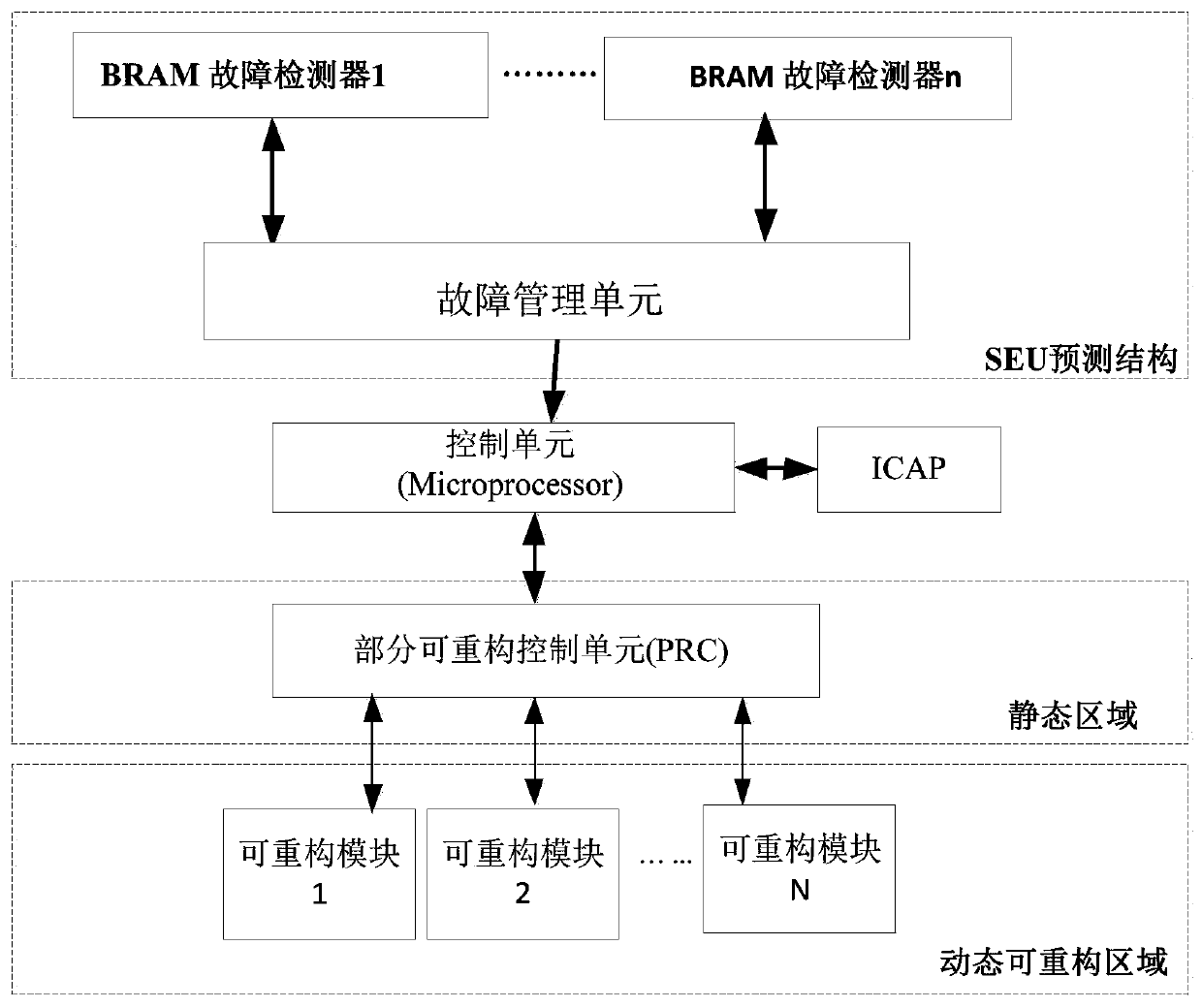

[0036] Step 1: Choose the Virtex-4 XQR4VSX55 SRAM FPGA of Xilinx Company, and divide the reconfigurable area and static area by the resources of the ISE tool on the FPGA. Configure the static area function, configure it as a partial reconfiguration controller (PRC, Partial Reconfiguration Controller), configuration interface and system internal connection line (PLB, Processor Local Bus), PLB connects all components and memory controllers to the control unit . Since the static area is configured with more critical modules, it occupies less resources and cannot be partially reconstructed. All structures in this area are protected by TMR to shield the accumulation of SEU in the static area.

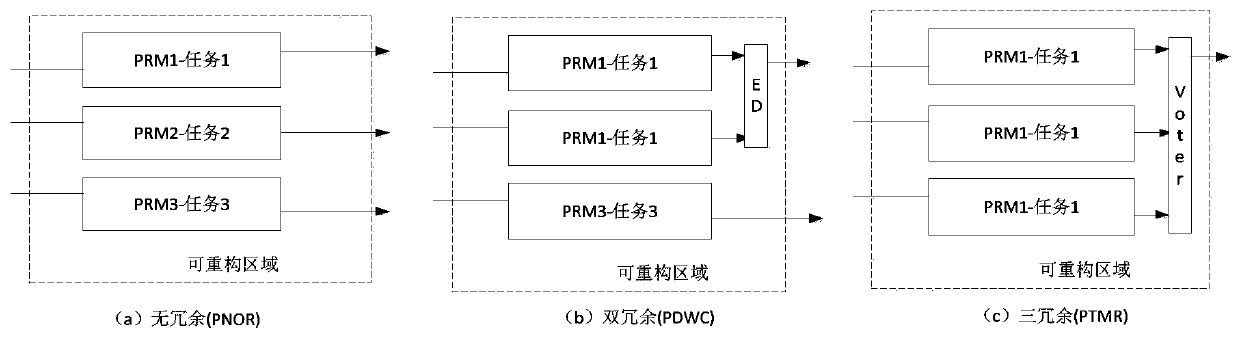

[0037] Step 2: Construct adaptive resources in the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More