Method for converting Avalon bus into Axi4 bus

A bus and data technology, applied in Avalon bus-to-Axi4 bus devices, Avalon bus-to-Axi4 bus, and computer-readable storage media, can solve the problem of large use limitations, large delays, and inability to support cross-clock domain conversions, etc. problems, to achieve efficient verification, improve development efficiency, and reduce interface debugging work

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

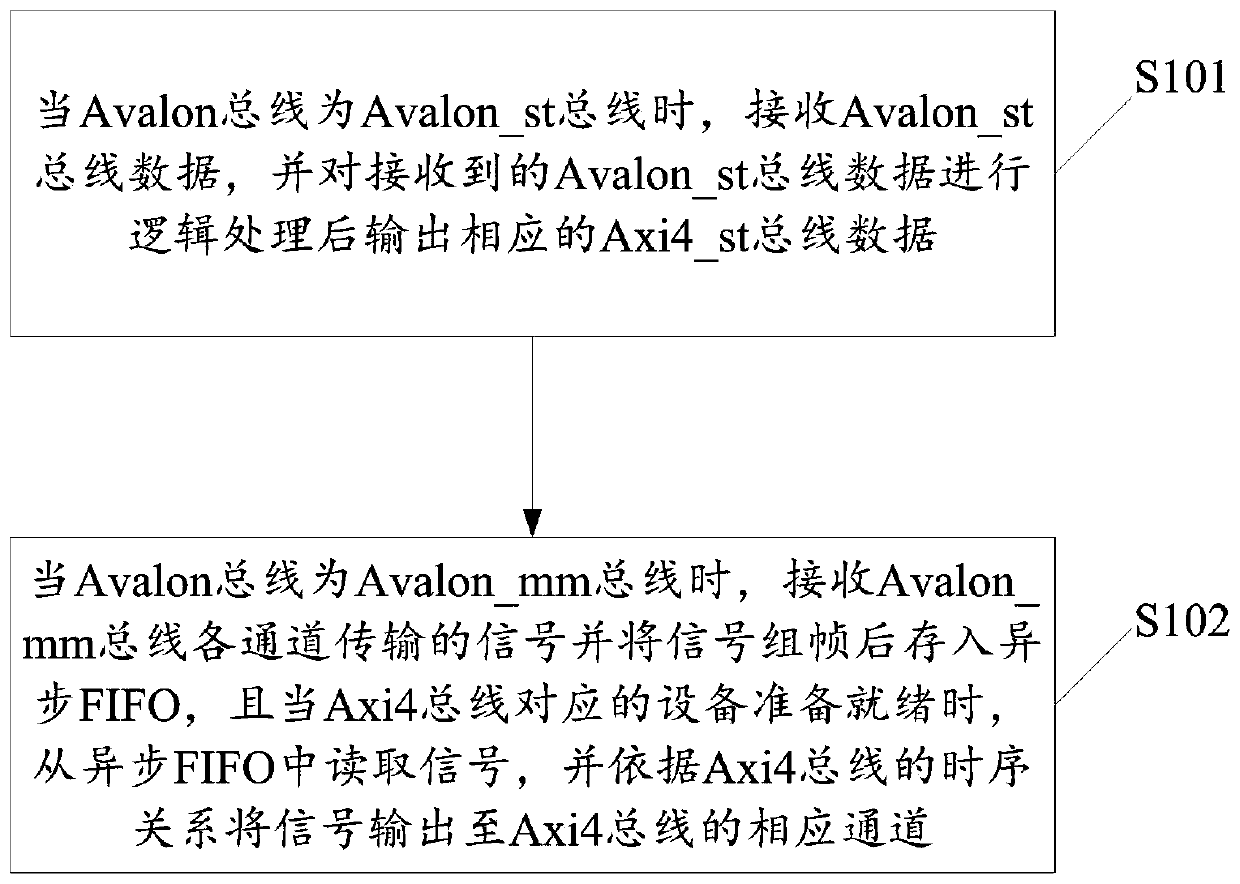

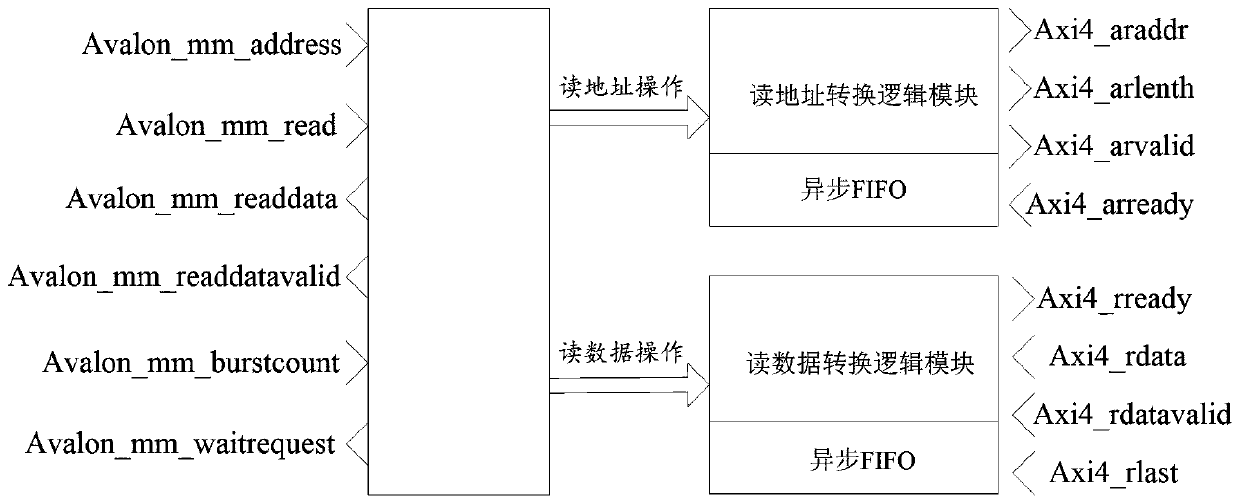

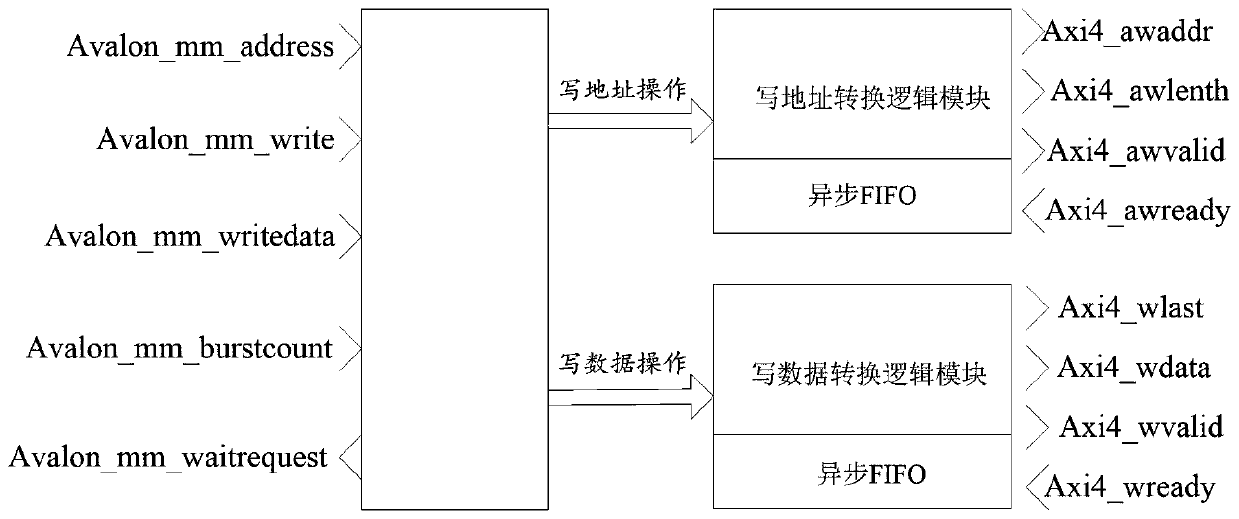

[0038] The core of this application is to provide a method for converting Avalon bus to Axi4 bus, which can realize the conversion of Avalon bus to Axi4 bus without delay and across clock domains, and realize the work of fast design and matching interface in cross-platform general design or code transplantation scheme . Another core of the present application is to provide an Avalon bus-to-Axi4 bus conversion device, equipment, and computer-readable storage medium, all of which have the above-mentioned technical effects.

[0039] In order to make the purposes, technical solutions and advantages of the embodiments of the present application clearer, the technical solutions in the embodiments of the present application will be clearly and completely described below in conjunction with the drawings in the embodiments of the present application. Obviously, the described embodiments It is a part of the embodiments of this application, not all of them. Based on the embodiments in t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More