Convolutional network accelerator, configuration method and computer readable storage medium

A convolutional network and configuration method technology, applied in data exchange networks, digital transmission systems, electrical components, etc., can solve the problems of not making full use of FPGA resources, not achieving time-division multiplexing, and not having a general implementation scheme, etc. Achieve flexible configurability, improve the balance of bandwidth, time and accelerator operation time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

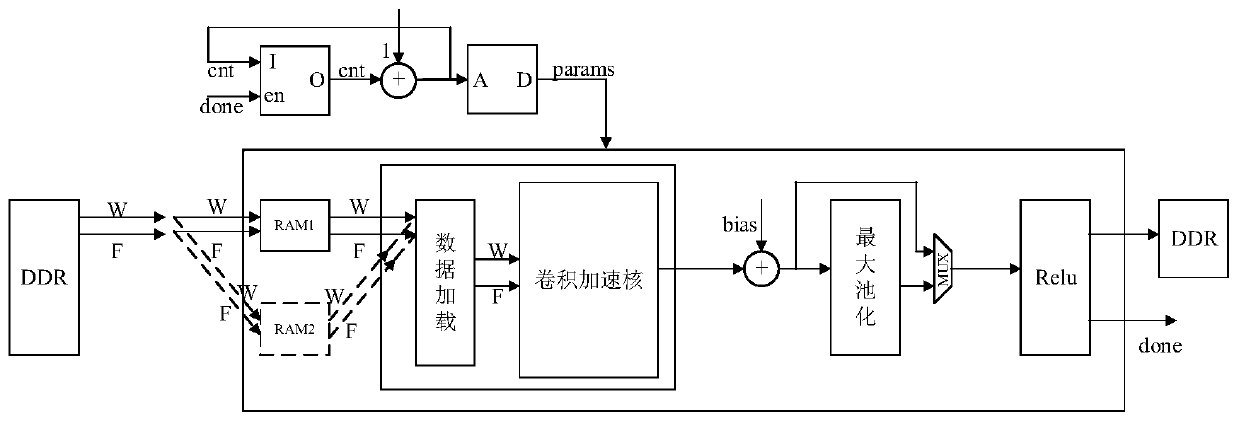

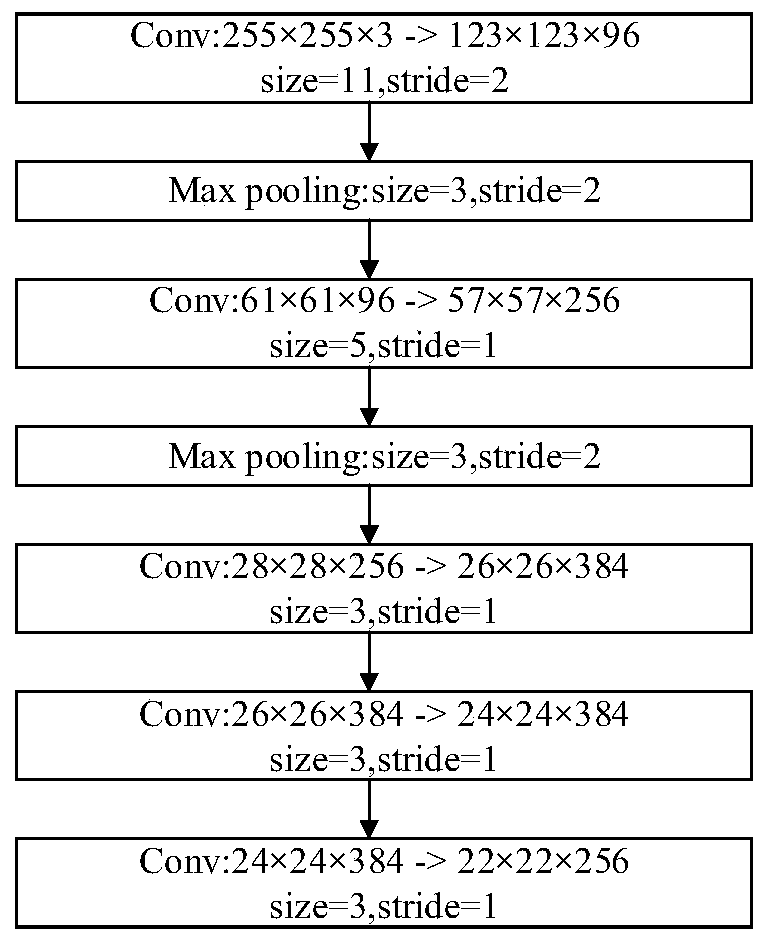

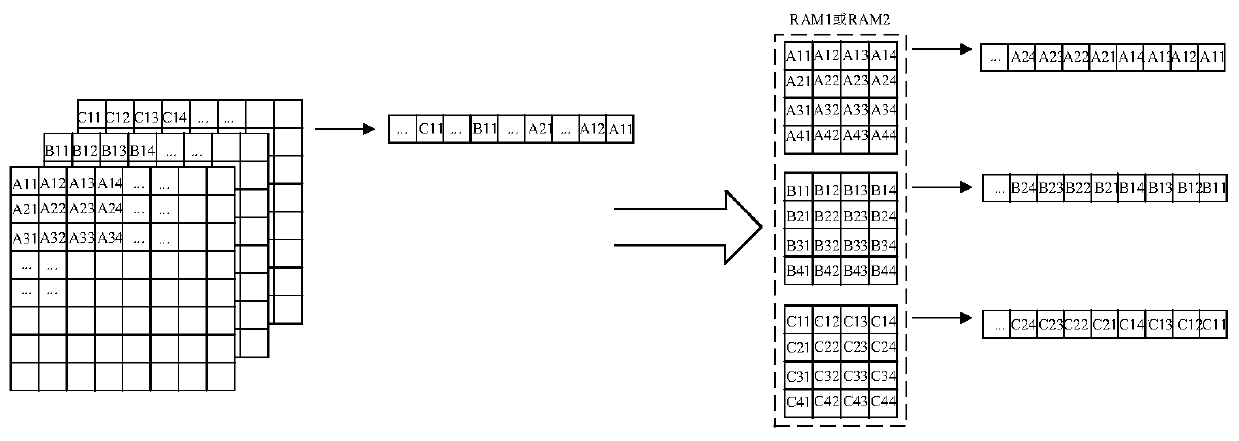

[0068] The FPGA chip-based convolutional network accelerator provided by the embodiment of the present invention is based on the basic structure of a single-layer convolutional network, that is, the structure of convolutional layer + pooling layer + activation layer + batch normalization operation layer. For the number of layers of the overall network model, the executed forward network layer obtains the configuration parameters of the current layer such as the size of the input and output feature map (length, width, number of channels), and the size of the convolution kernel (length, width, number of channels) , step size of convolution and pooling operations, etc., and load feature maps and weight parameters in batches from DDR (double data rate off-chip memory) through configuration parameters. At the same time, the acceleration kernel of the convolutional layer can also configure the degree of parallelism according to the configuration parameters.

[0069] The present inve...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More