Method and system for realizing consistency of cached data of multi-path processor based on distributed finite directory

A multi-processor, data cache technology, applied in memory systems, transaction processing, electrical digital data processing, etc., can solve the problems of starvation and blockage of request transactions, and achieve the effect of improving reliability and scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

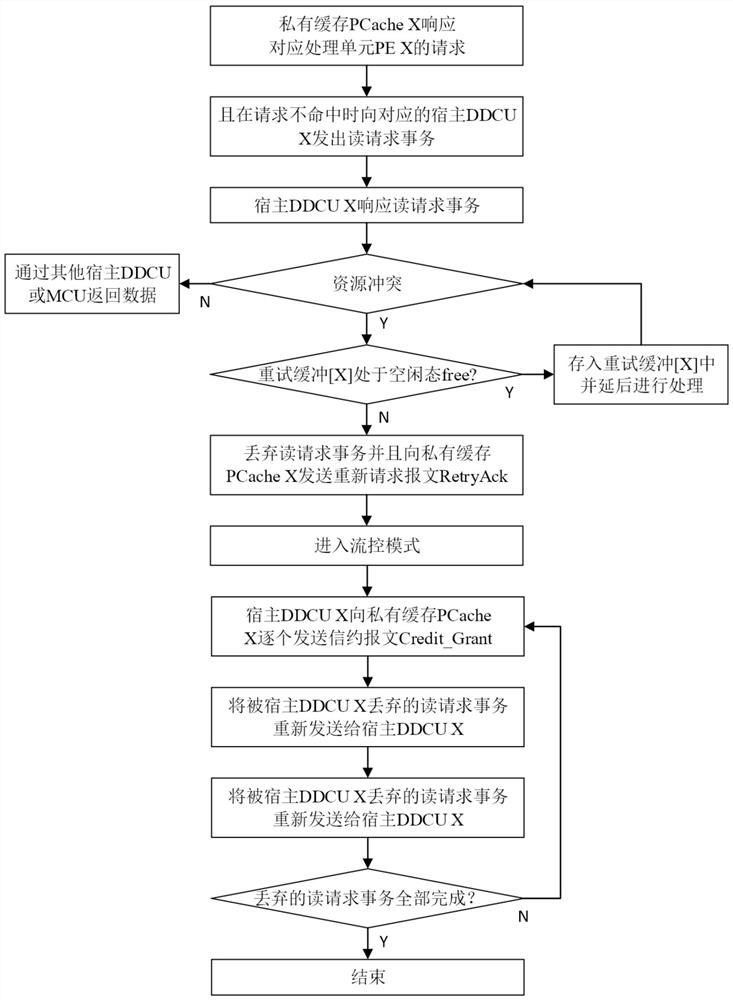

[0031] like image 3 As shown, the implementation steps of the method for implementing the consistency of multi-processor cache data based on a distributed limited directory in this embodiment include:

[0032] 1) The private cache PCache X responds to the request of the corresponding processing unit PE X, and sends a data read and write consistency request transaction to the corresponding host DDCU X when the request misses;

[0033] 2) The host DDCU X responds to the data read / write consistency request transaction and detects whether there is a resource conflict. If there is no resource conflict, it will return data through other host DDCU or MCU, end and exit; otherwise, wait for the retry buffer [X] to be idle state free, and when the retry buffer [X] is in the idle state free, the data read and write consistency request transaction is discarded, and the retry response message RetryAck is sent to the private cache PCache X, and the next step is skipped;

[0034] 3) The fl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com