Double-sided chip

A chip, double-sided technology, applied in the field of double-sided chips, can solve the problems of reducing the packaging area and increasing the area of a single chip, and achieve the effect of reducing the chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] Embodiments of the present application are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals denote the same or similar components or components having the same or similar functions throughout. The terms "first", "second", "third", etc. (if any) in the description and claims of this application and the drawings are used to distinguish similar objects and not necessarily to describe a specific order or priority. It should be understood that the items so described are interchangeable under appropriate circumstances. In the description of the present application, "plurality" means two or more, unless otherwise specifically defined. Furthermore, the terms "comprising" and "having", as well as any variations thereof, are intended to cover a non-exclusive inclusion.

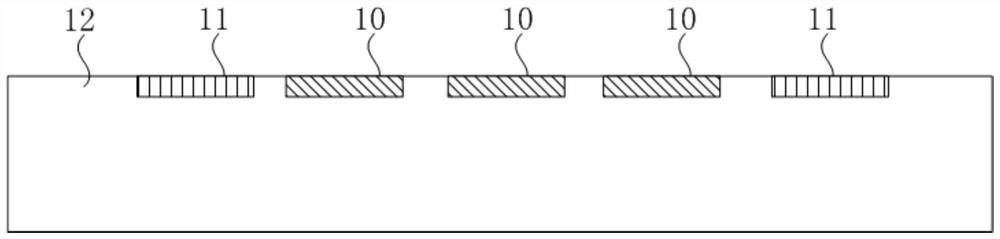

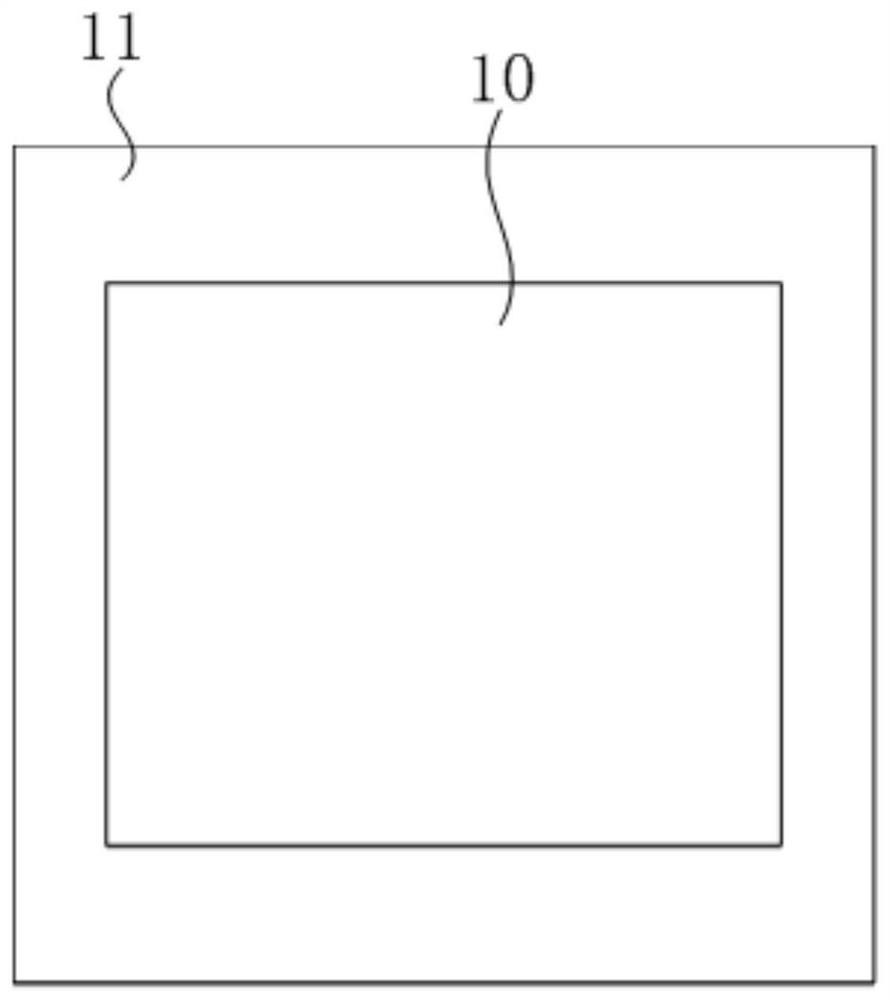

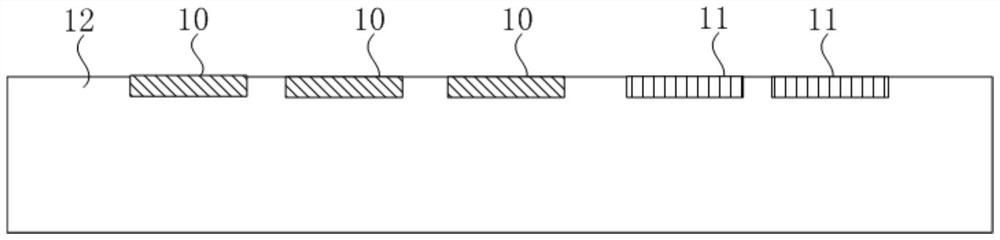

[0018] see figure 2 , in the first embodiment of the double-sided chip of the present invention, the double-sided chip includes a first la...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More