Device isolation structure used for high pressure manufacturing process and its manufacturing method

An isolation structure and device isolation technology, applied in the manufacture of the device isolation structure, shallow trench isolation mixed with local silicon oxidation isolation device structure field, can solve problems such as unfavorable process control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

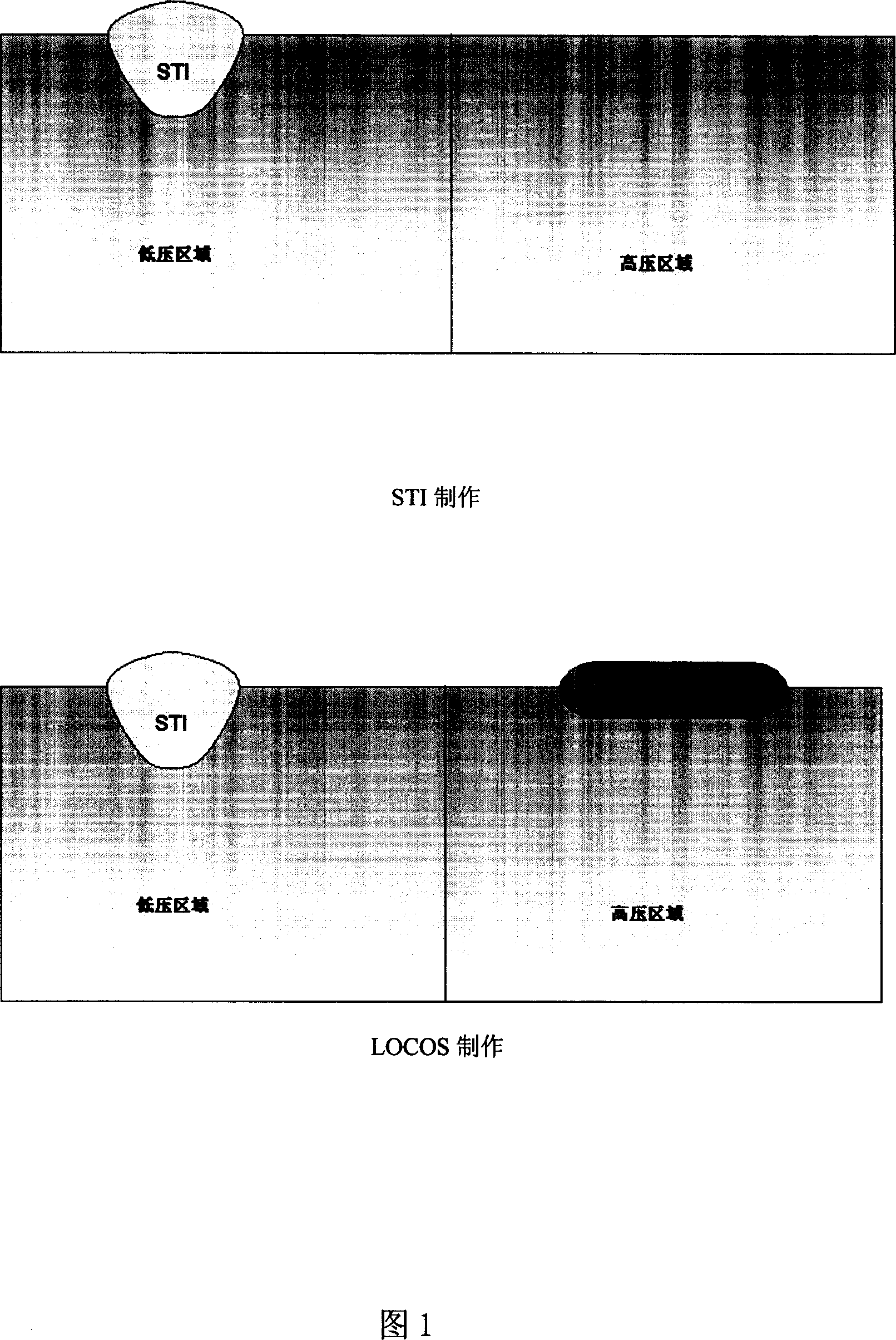

[0019] In the existing high-voltage process technology, generally only one isolation structure among STI or LOCOS is selected for device isolation. The manufacturing process of the device isolation structure is generally placed in the initial stage of silicon wafer processing. The device isolation structure is firstly prepared on the silicon wafer through the standard STI or LOCOS process, and then the device structure and other subsequent processes are gradually completed.

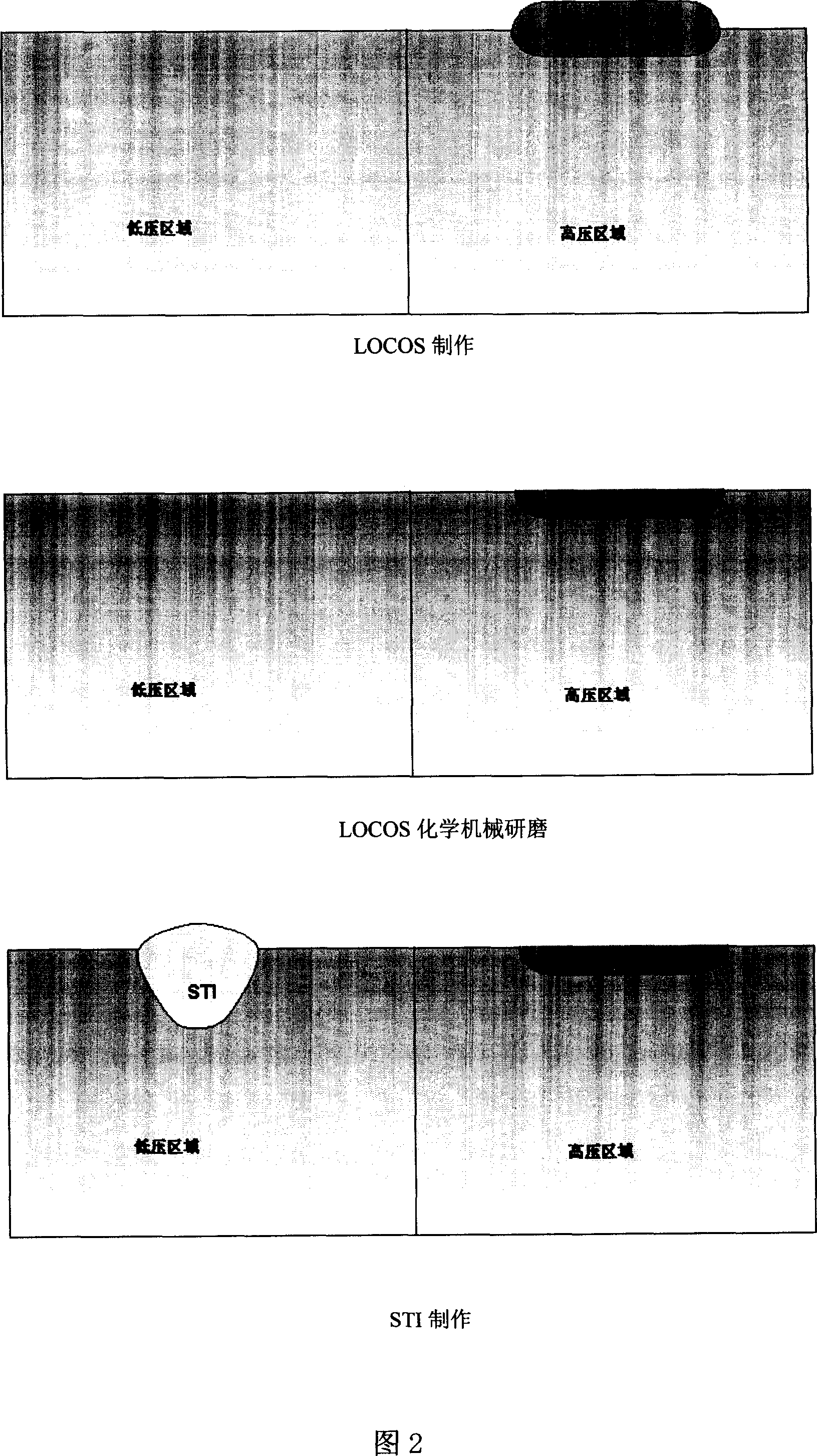

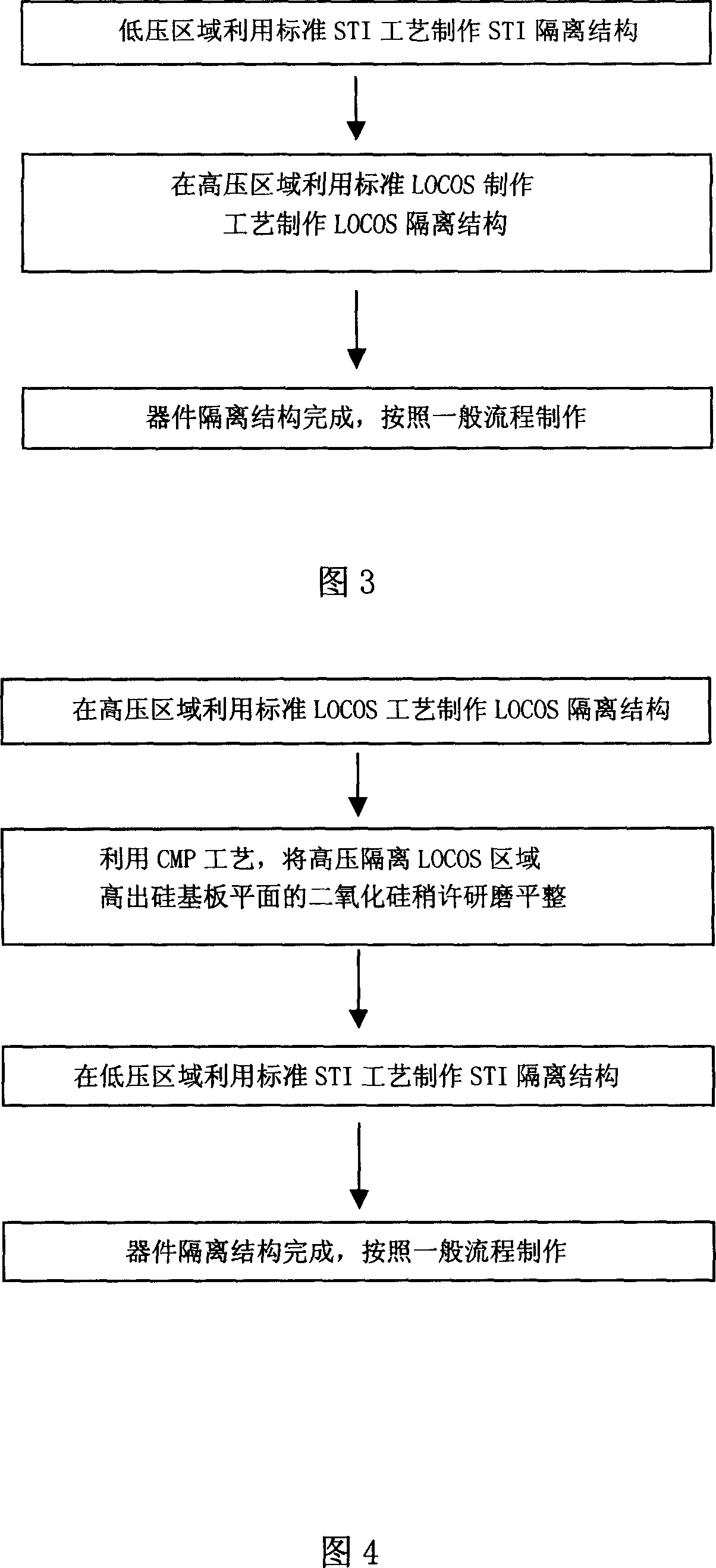

[0020] The present invention makes two isolation structures STI and LOCOS simultaneously in a high-pressure process. For device isolation in the low-voltage area, because the working voltage is not high, the isolation effect of the device is not high, so the STI isolation structure is adopted; for the device isolation in the high-voltage area, considering the high working voltage, in order to ensure good device isolation effect, Therefore, the LOCOS isolation structure is adopted. The manufacturing proce...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More