Three-dimensional memory structure and preparation method thereof

A memory, three-dimensional technology, applied in the direction of electric solid-state devices, semiconductor devices, electrical components, etc., can solve the problems of gate layer breakdown, gate layer short circuit, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

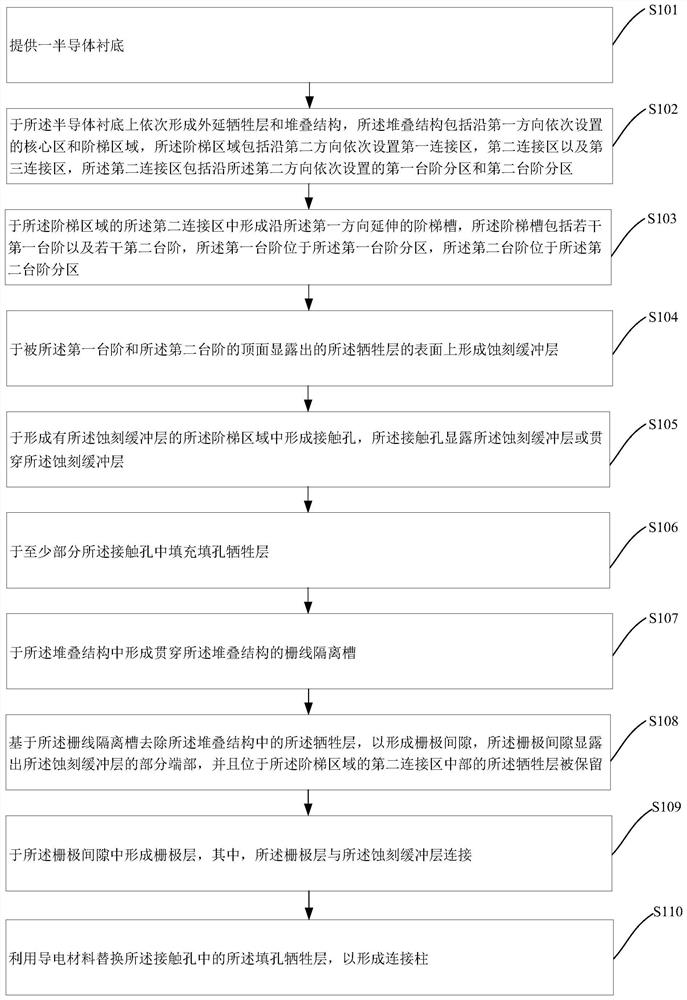

[0156] figure 1 A flow chart of preparing a three-dimensional memory structure according to an embodiment of the present invention is shown. see figure 1 , the preparation method of the three-dimensional memory structure includes:

[0157] Step S101, providing a semiconductor substrate;

[0158] Step S102, sequentially forming an epitaxial sacrificial layer and a stacked structure on the semiconductor substrate, the stacked structure includes alternately stacked interlayer dielectric layers and sacrificial layers, and the stacked structure includes core regions and A stepped area, the stepped area includes a first connection area, a second connection area and a third connection area arranged in sequence along the second direction, and the second connection area includes a first step partition and a second connection area arranged in sequence along the second direction Second step partition;

[0159] Step S103, forming a stepped groove extending along the first direction in...

Embodiment 2

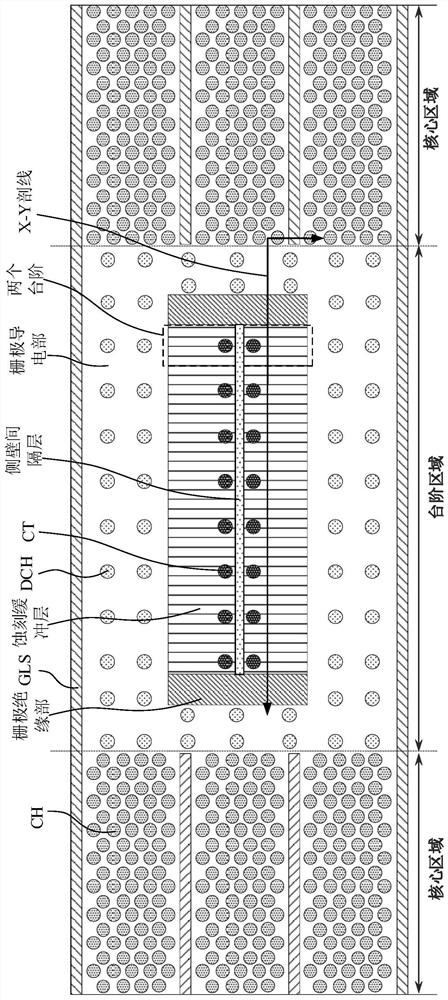

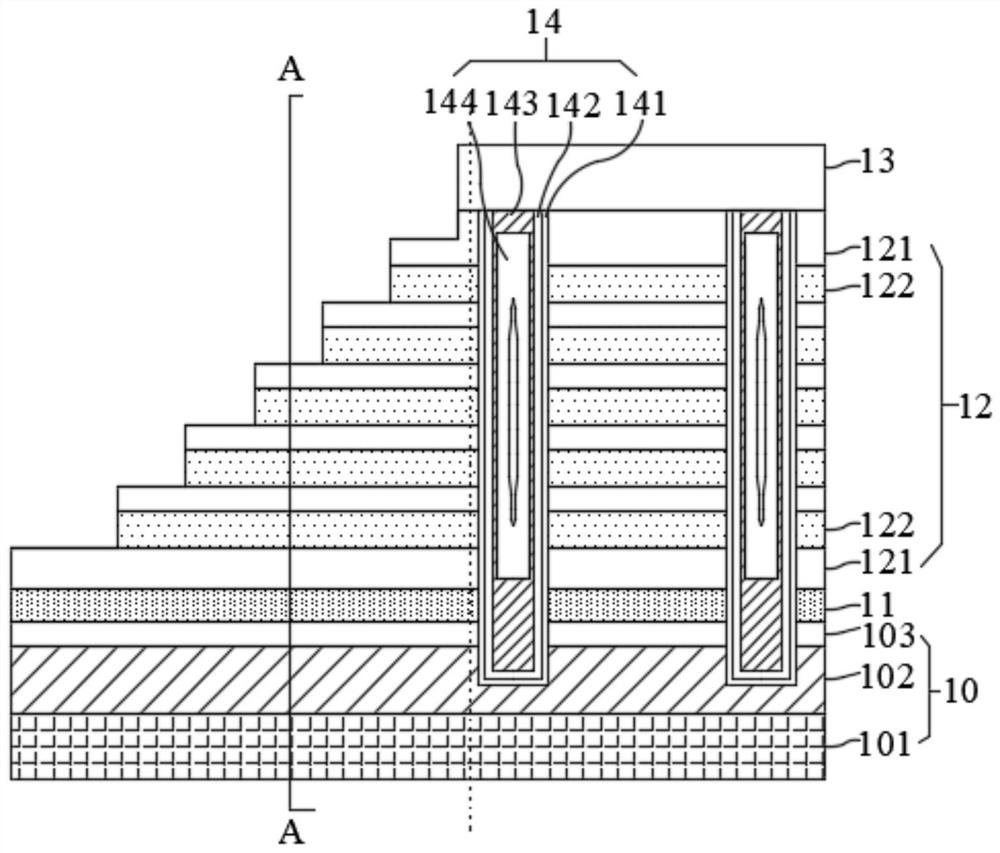

[0198] see figure 2 as well as Figure 31-33 The present invention also provides a three-dimensional memory structure prepared by the preparation method in Embodiment 1. The three-dimensional memory structure at least includes a semiconductor substrate 10, an epitaxial layer 28, a stacked gate structure 30, and several steps (several first steps and several second steps), etch buffer layer 18 and several connection pillars 32 ( figure 2 CT in ). The three-dimensional memory structure of this embodiment can reduce the process difficulty of etching the contact hole 20 in the stepped area, eliminate the word line bridge (Word Line Bridge) of different layers caused when the contact hole 20 is etched during the etching process (Punch), and improve the three-dimensional memory. performance of the piece.

[0199] see figure 2 as well as Figure 31-33 , in this embodiment, the semiconductor substrate 10 includes a substrate body 101, and a doped well is formed in the substrat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com