Patents

Literature

85results about How to "Reduce the difficulty of etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

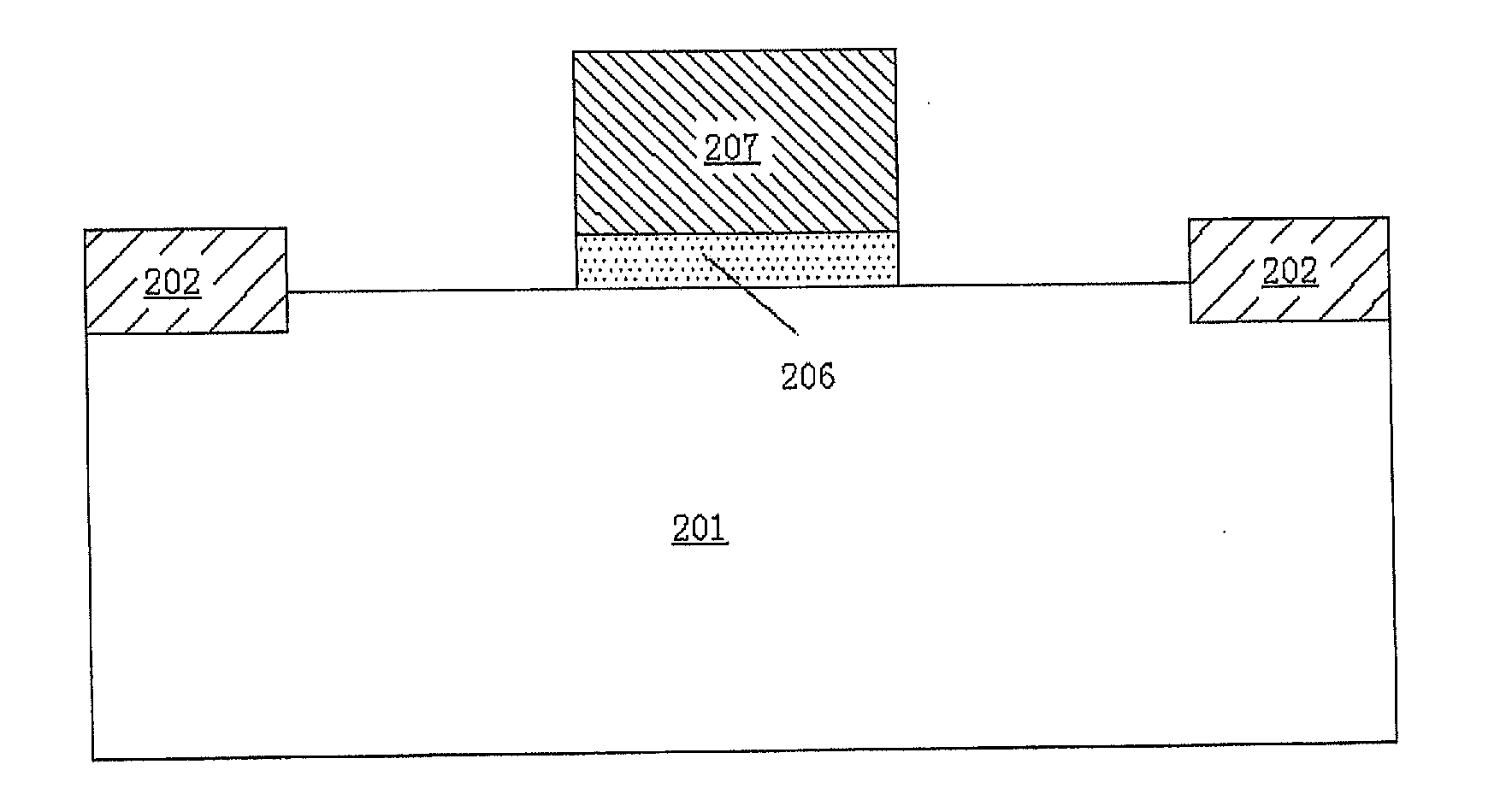

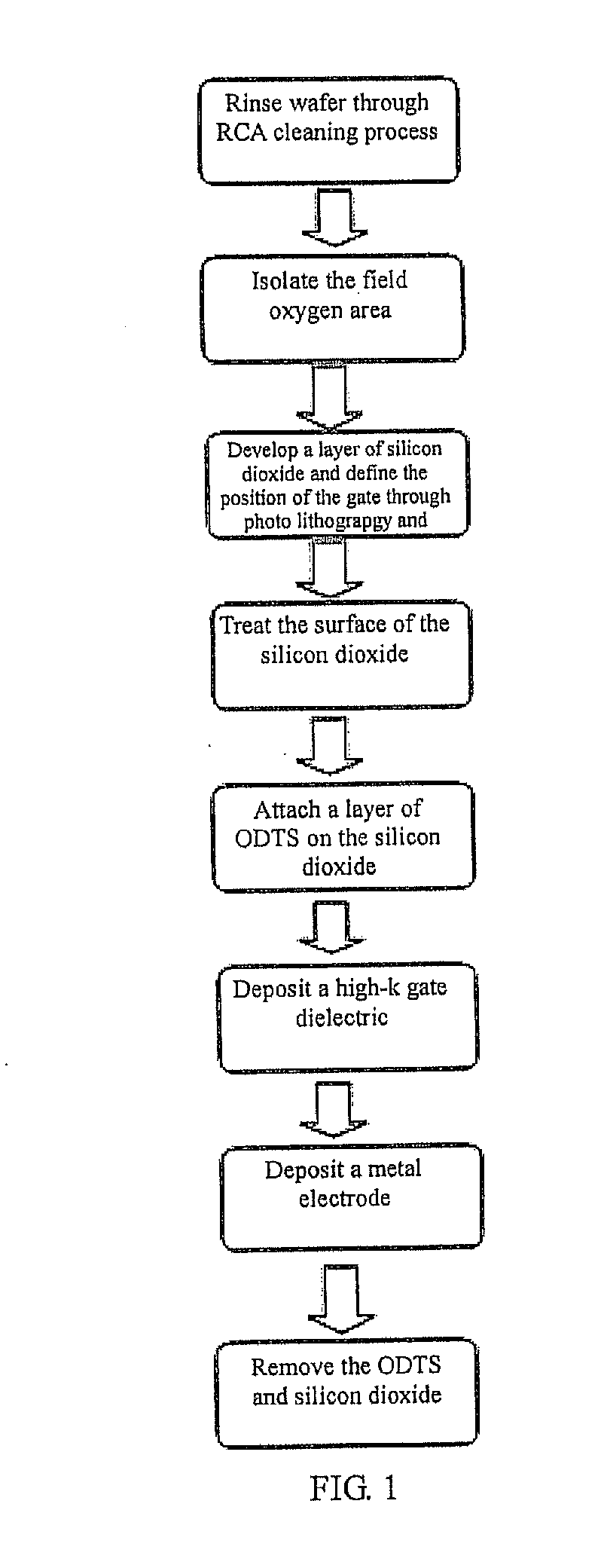

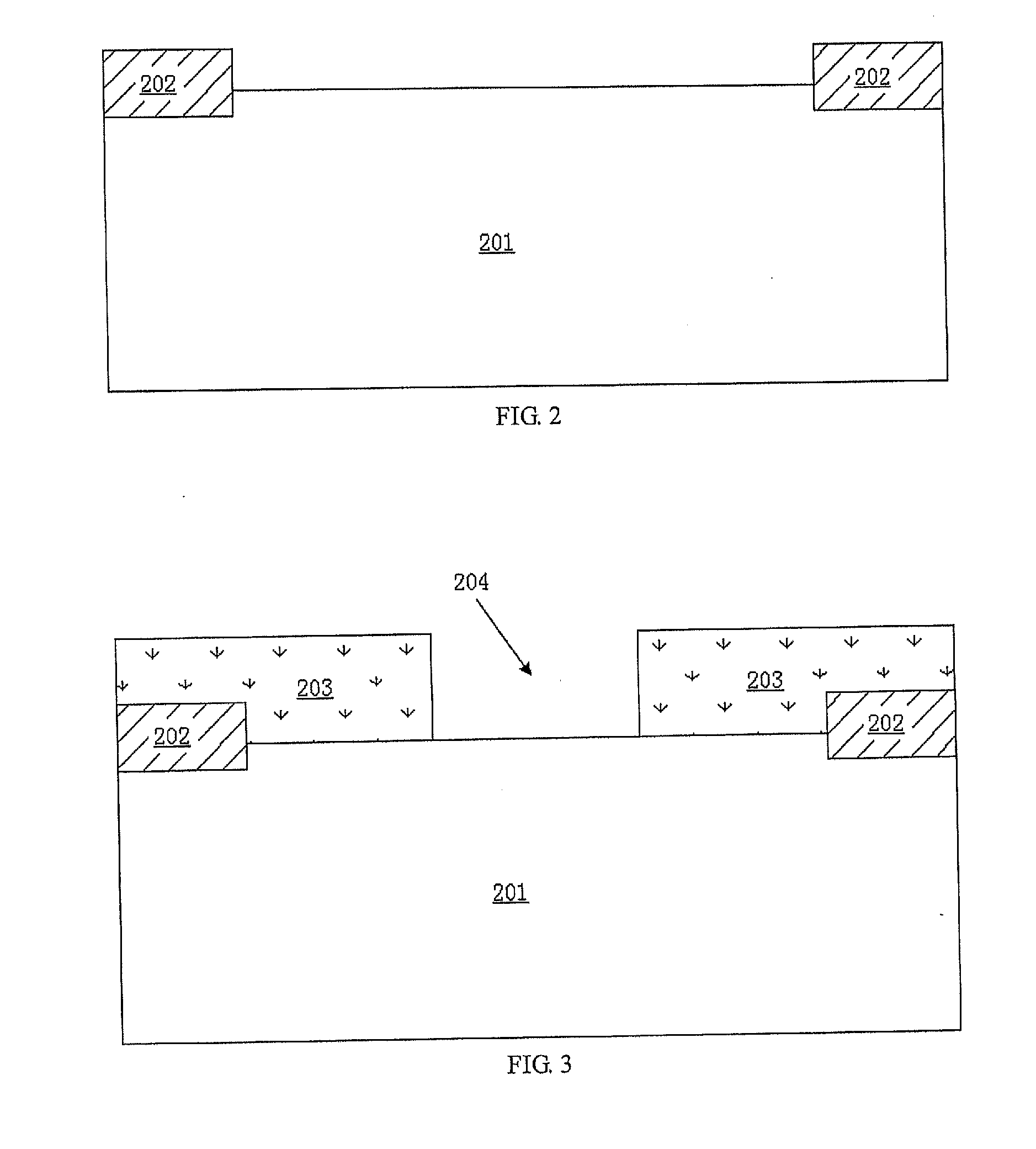

Method for depositing a gate oxide and a gate electrode selectively

InactiveUS20130078793A1Reduce wasteReduce difficultySemiconductor/solid-state device manufacturingSemiconductor devicesEtchingSemiconductor

The present invention belongs to the technical field of integrated semiconductor circuits, and relates to a method for depositing a gate oxide and a gate electrode selectively. The present invention makes use of Octadecyltriethoxysilane's (ODTS') easy attachment to the Si—OH interface and difficult attachment to the Si—H interface, and selectively deposits the gate oxide and gate electrode materials, which avoids the unnecessary waste of materials and saves cost. Meanwhile, the present invention will transfer the etching of the gate oxide and gate electrode into the etching of SiO2 so as to reduce the difficulty of the etching process and increase the production efficiency.

Owner:FUDAN UNIV

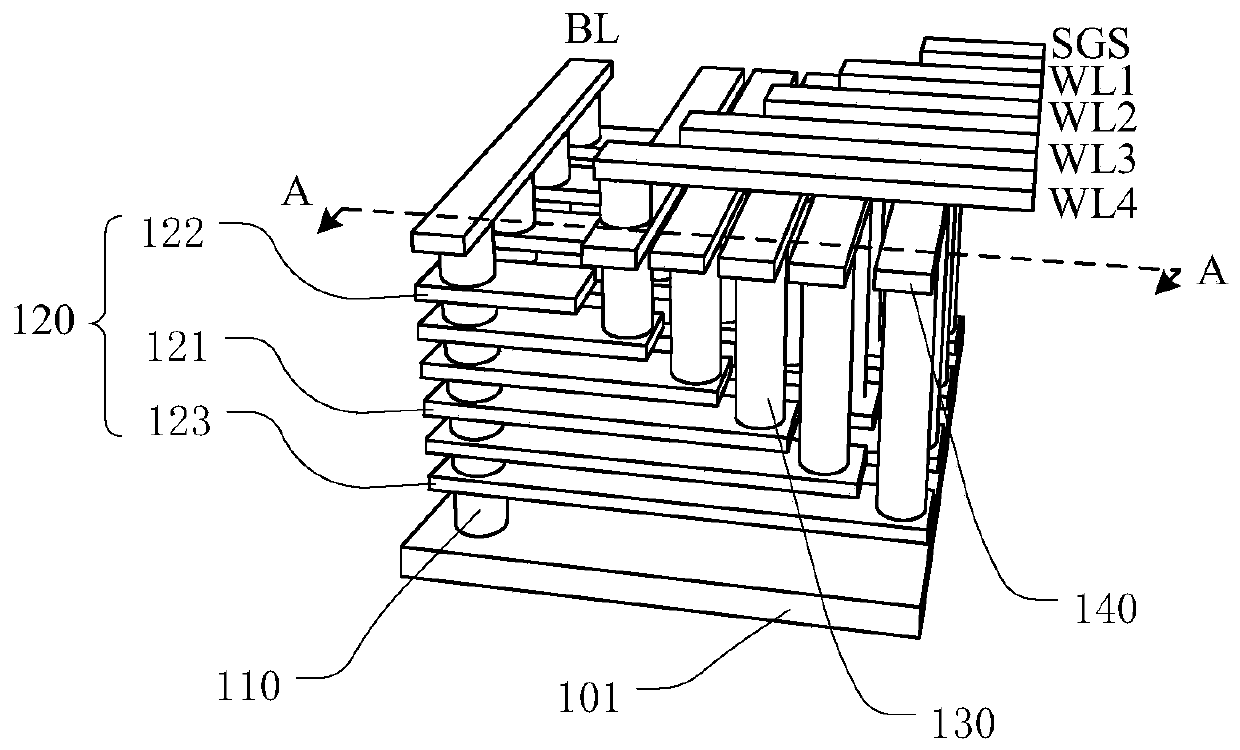

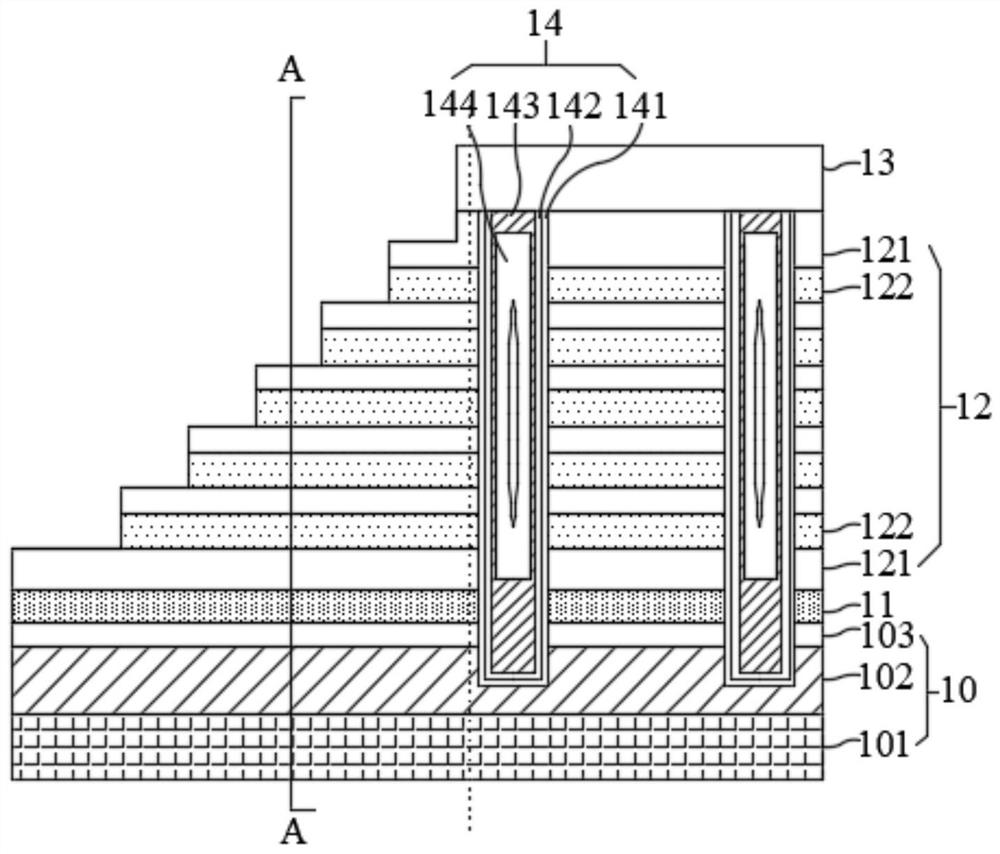

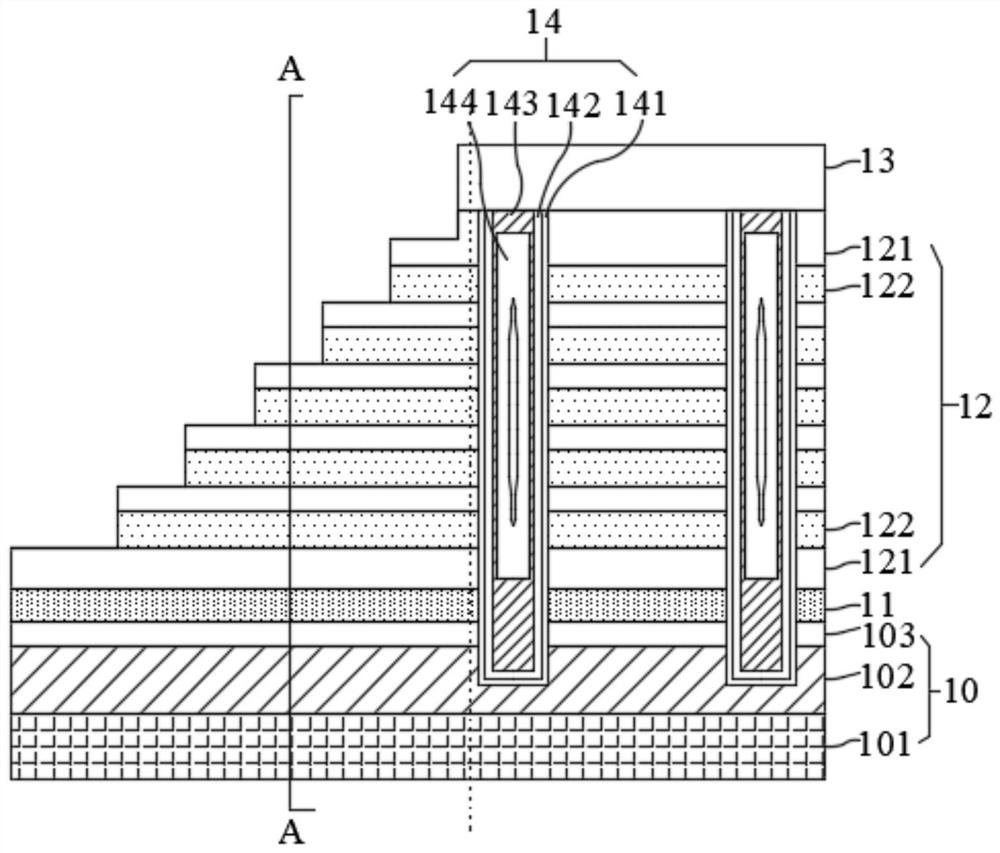

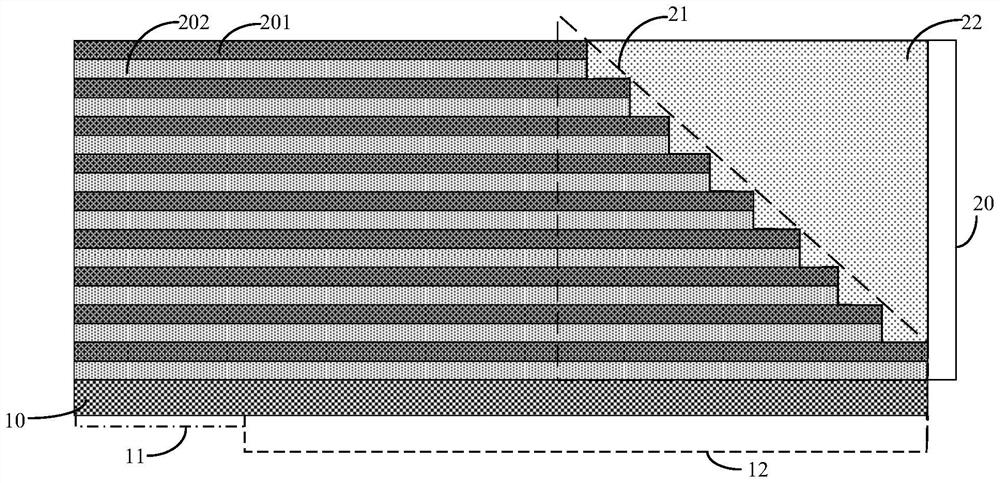

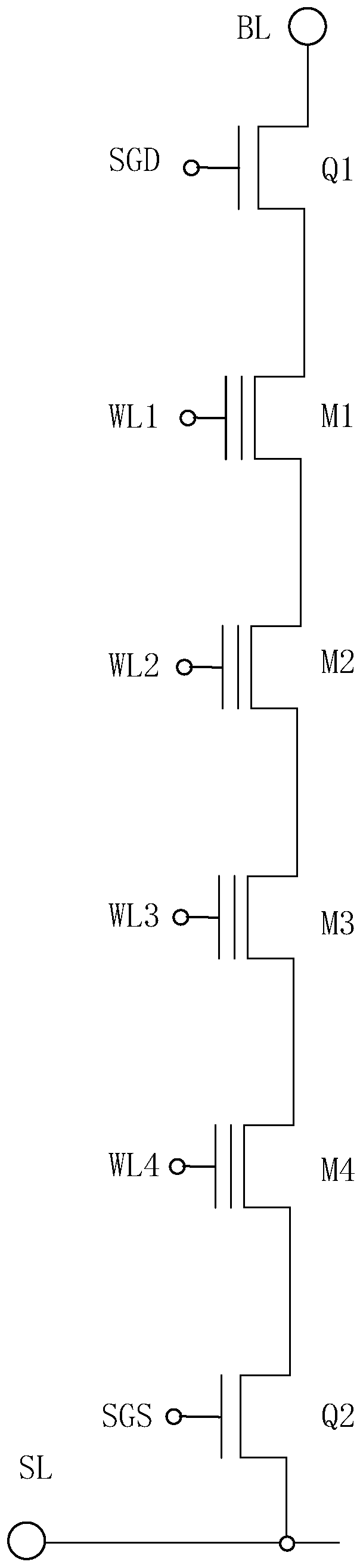

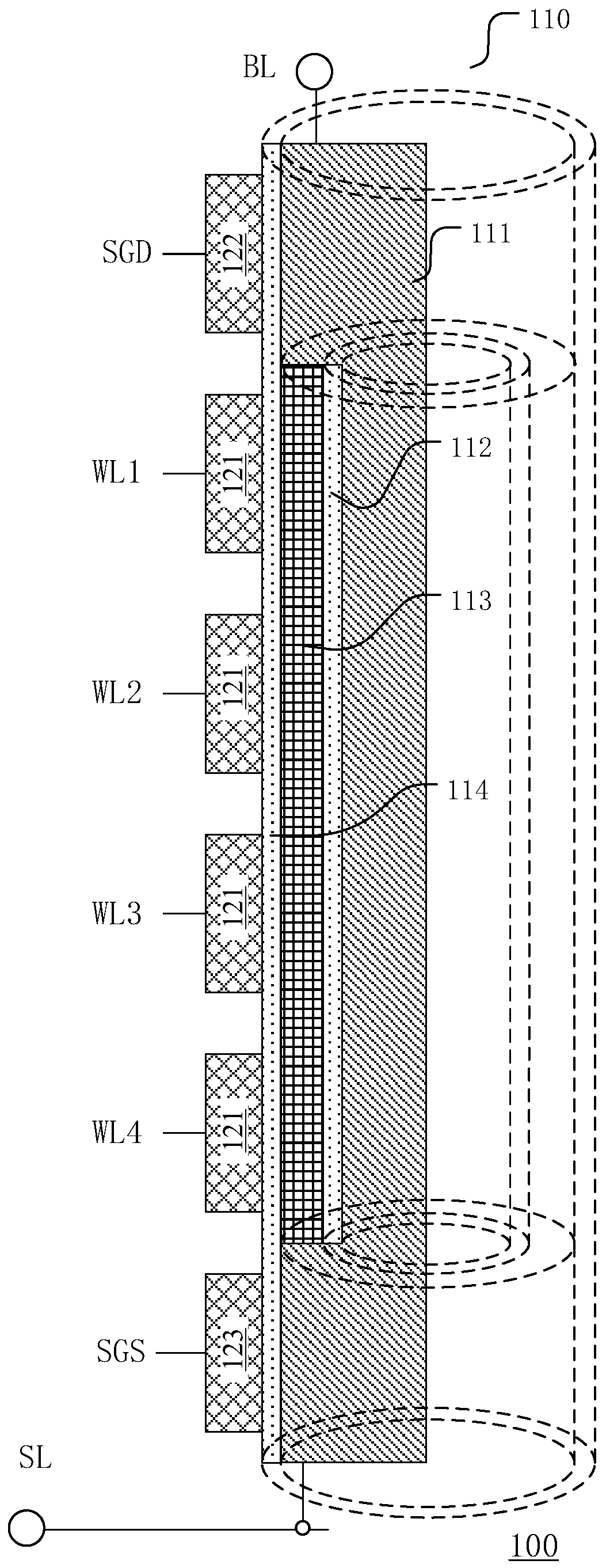

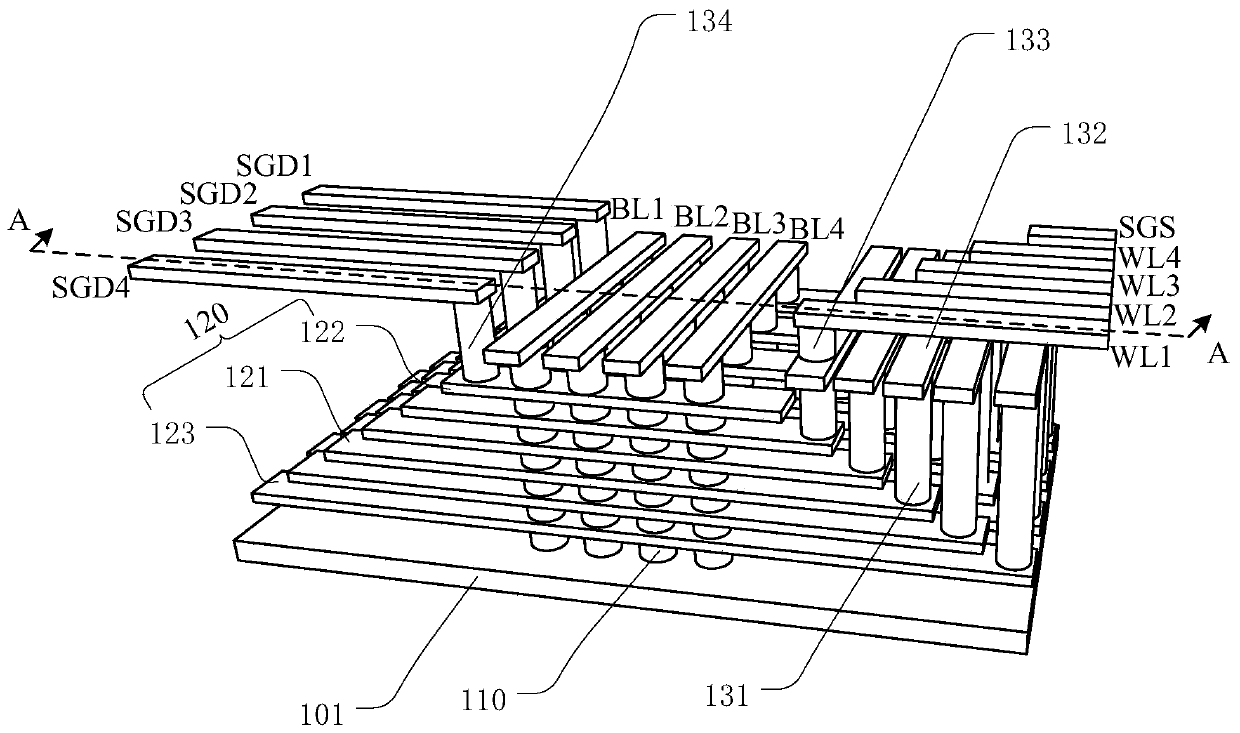

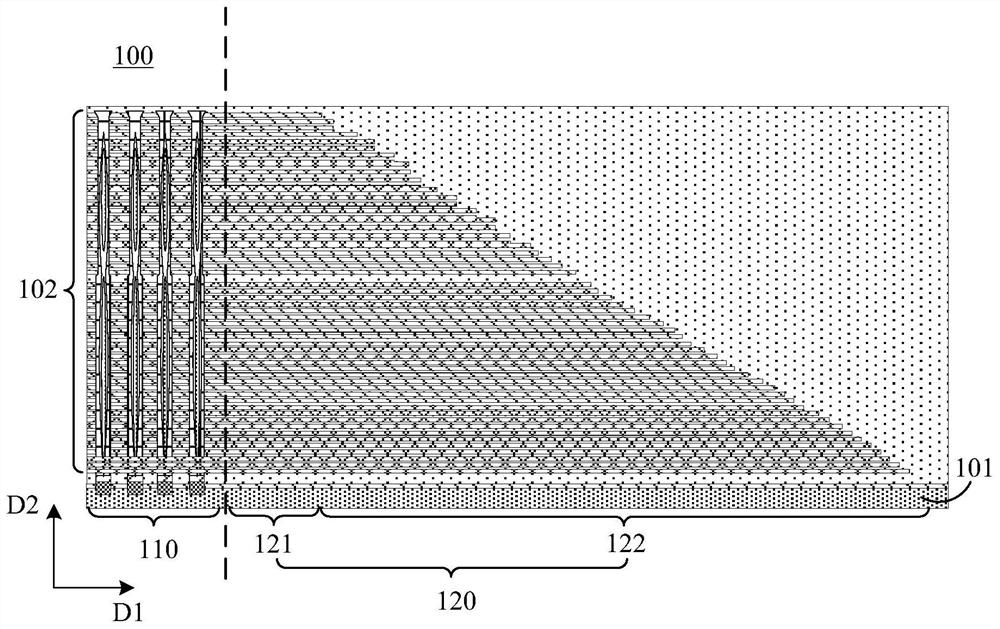

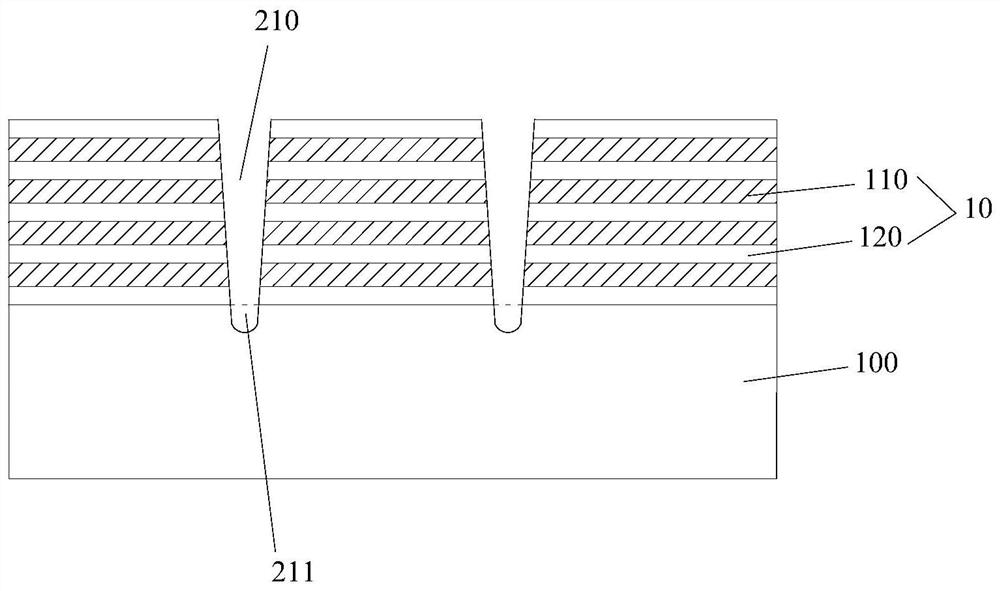

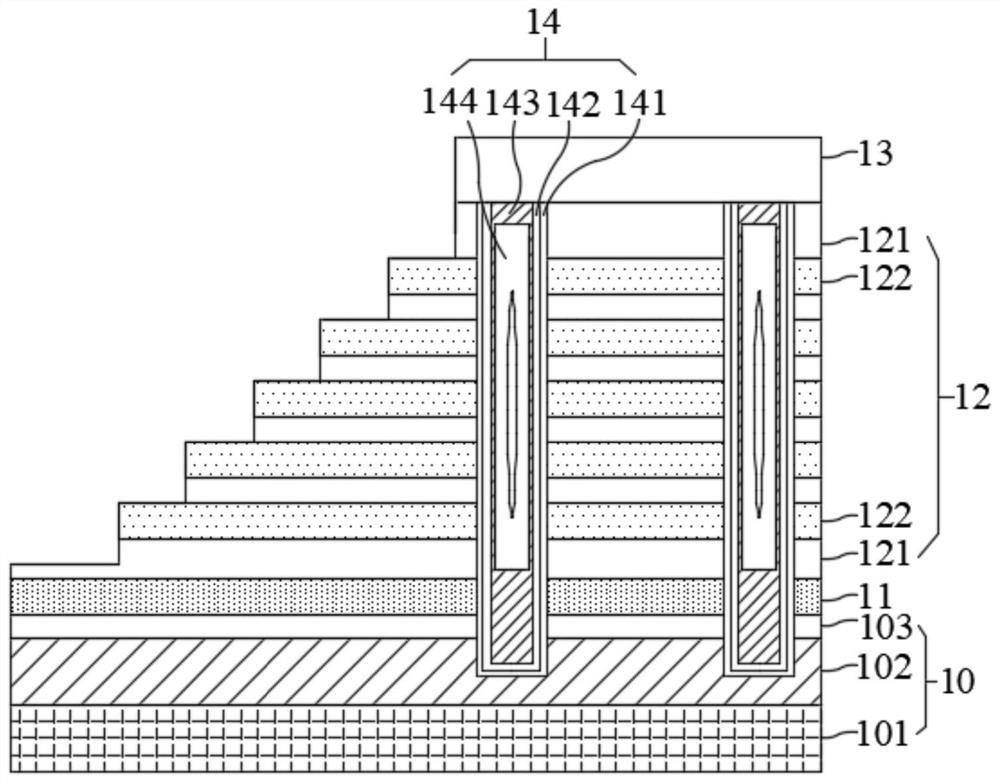

3D memory device and manufacturing method thereof

ActiveCN111564445AImprove reliabilityReduce the difficulty of etchingSolid-state devicesSemiconductor devicesStructural engineeringDielectric layer

The invention discloses a 3D memory device and a manufacturing method thereof. The manufacturing method of the 3D memory device comprises the following steps: forming a stepped insulating laminated structure on a semiconductor substrate, wherein each step comprises a sacrificial layer and an interlayer insulating layer positioned below the sacrificial layer; forming a protective layer on at leastpart of the exposed surface of the sacrificial layer; forming a dielectric layer covering the insulating laminated structure above the protective layer; replacing the sacrificial layer with a gate conductor layer to form a gate laminated structure; and forming a conductive channel communicated with the gate conductor layer on at least one step, wherein the protective layer serves as a stop layer for forming the conductive channel, and the conductive channel is at least partially contacted with the gate conductor layer. According to the manufacturing method, the protective layer is formed on the surface of the laminated structure through treatment, and the protective layer is used as a stop layer to execute an etching process to form step region contact, so that the etching difficulty is reduced under the condition that the thickness of the single-layer dielectric laminated layer is reduced, and the reliability of the memory device is improved.

Owner:YANGTZE MEMORY TECH CO LTD

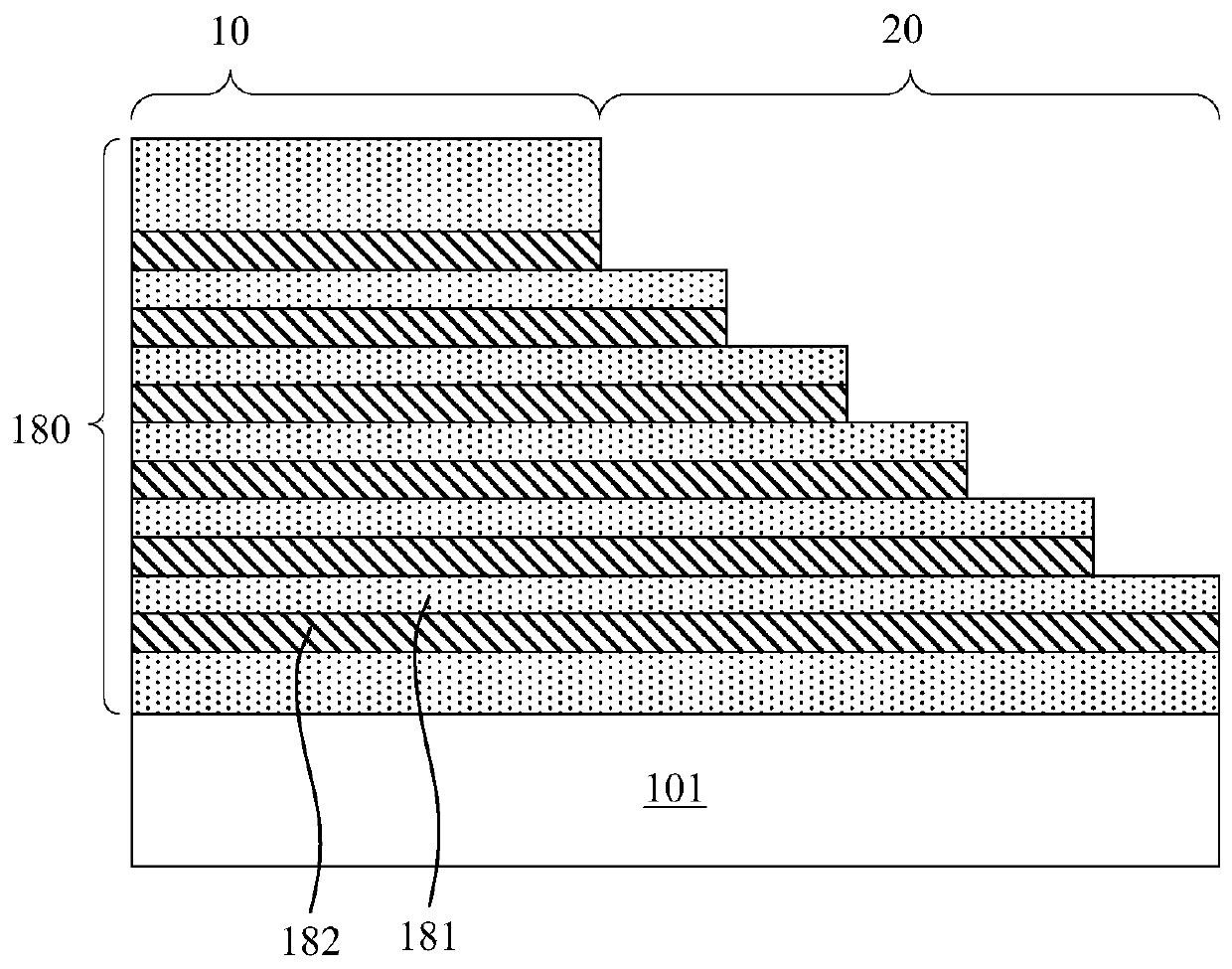

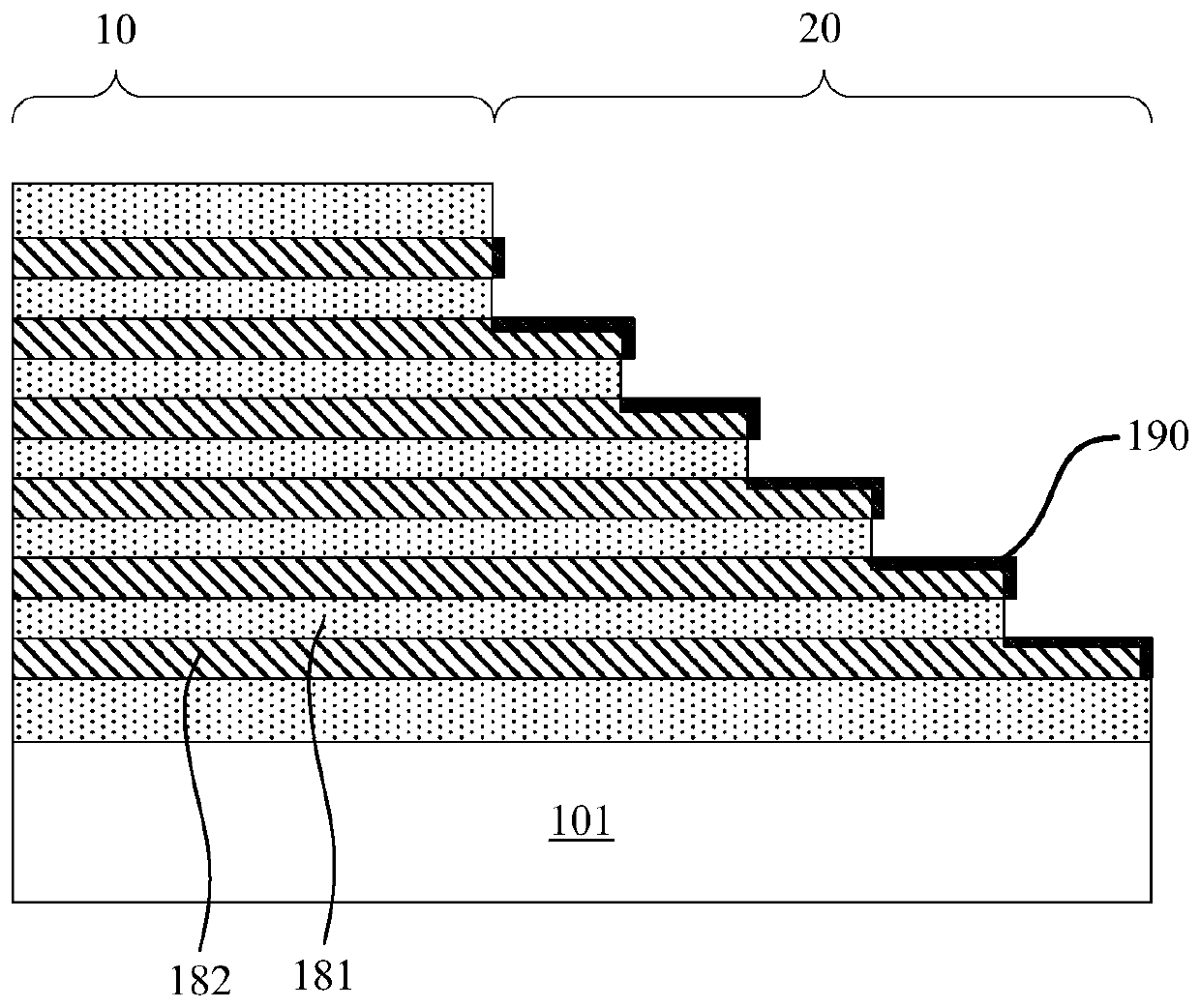

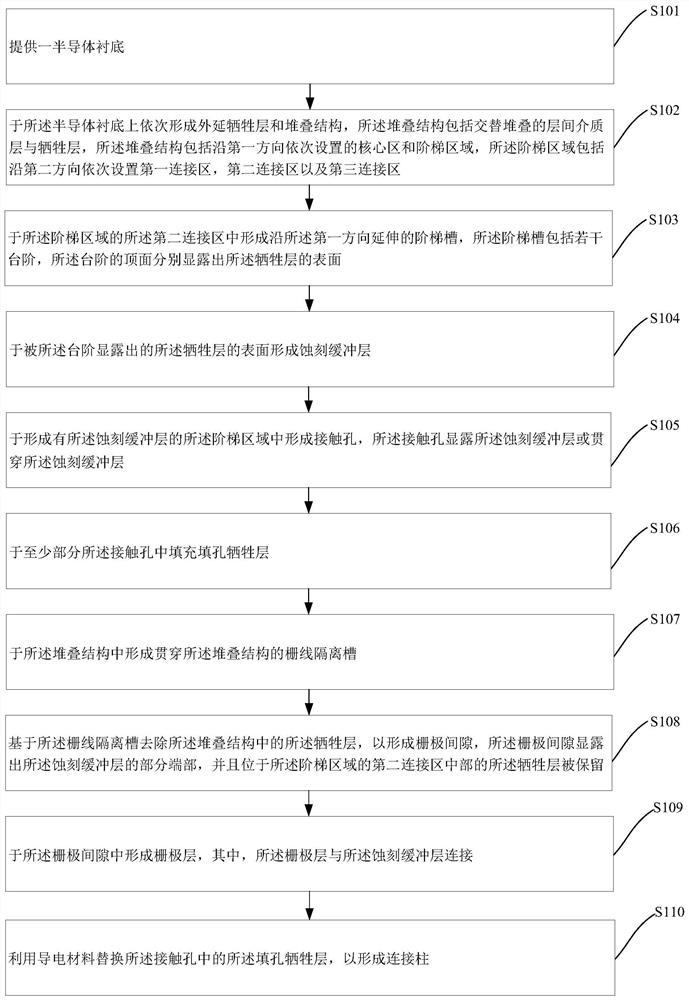

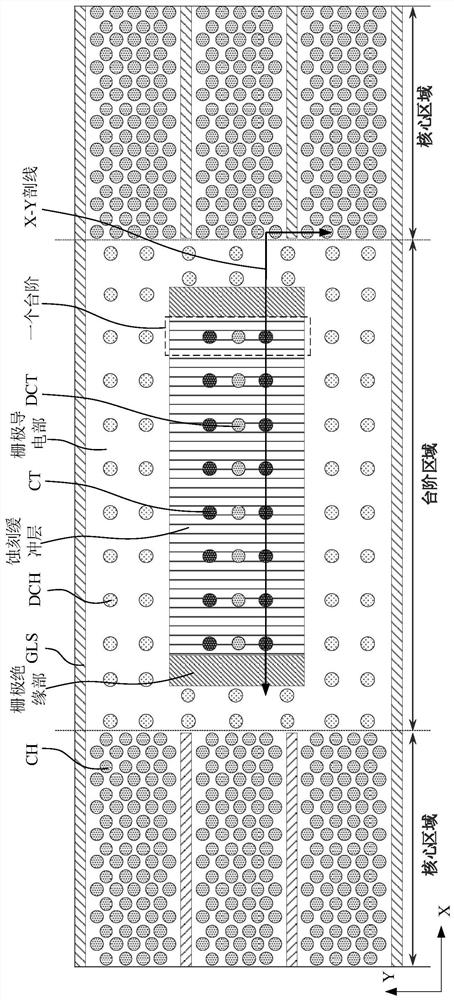

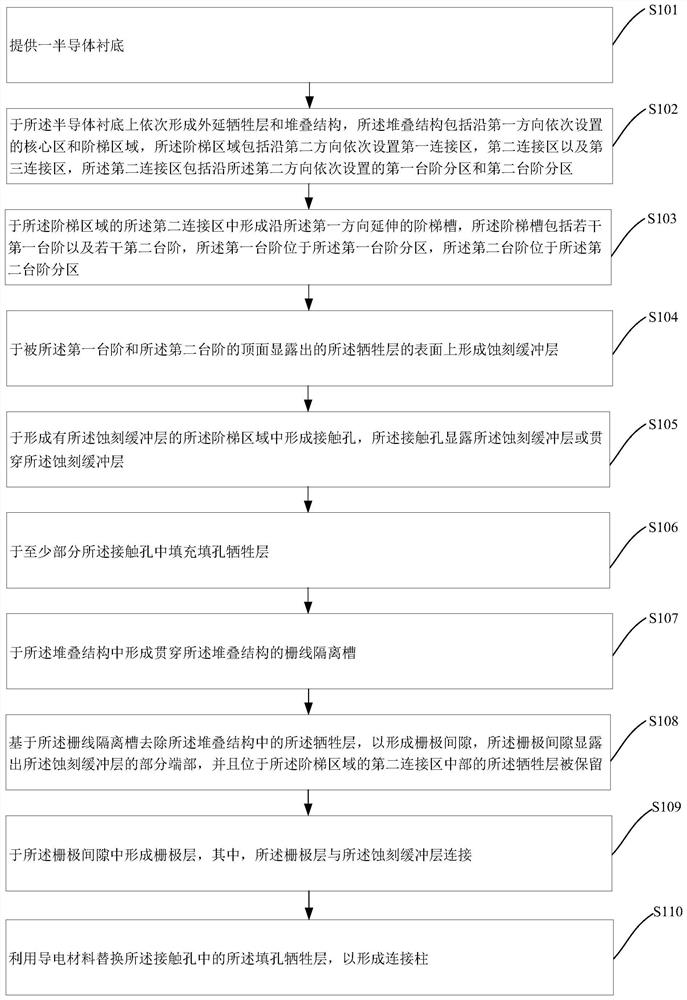

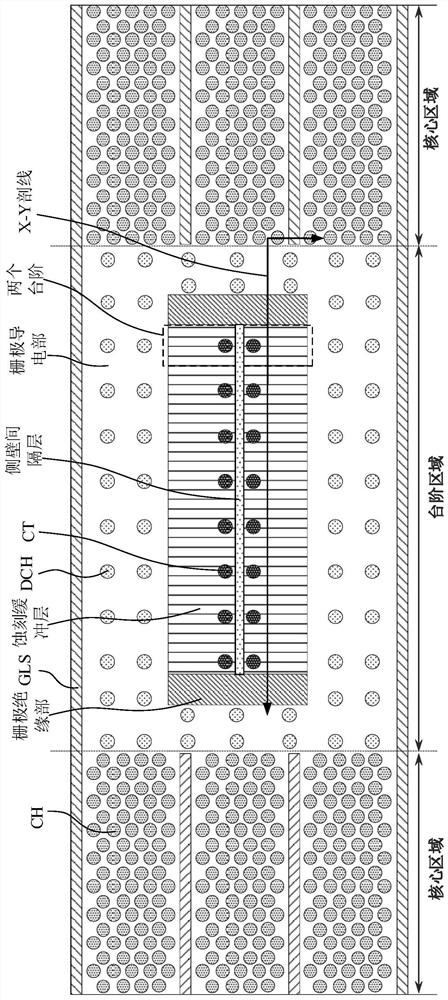

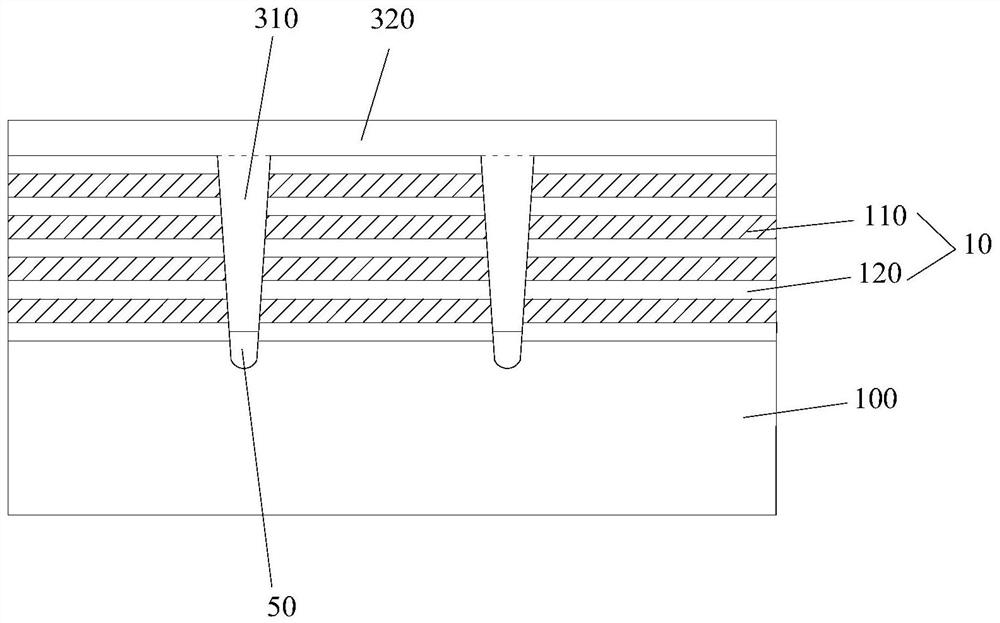

Three-dimensional memory structure and preparation method thereof

ActiveCN111769114AReduce processing difficultyImprove performanceSolid-state devicesSemiconductor devicesElectrical connectionEngineering

The invention provides a three-dimensional memory structure and a preparation method thereof. The preparation method of a three-dimensional memory structure comprises: dividing the step region into afirst connecting region along a second direction, a second connection area and a third connection area, forming an etching buffer layer on the surface of a sacrificial layer of a stacked structure, which is exposed from the top surface of a step formed in a second connection region; forming a contact hole in the step region on which the etching buffer layer is formed, and when the sacrificial layer of the stacked structure is replaced by the gate conductive material, reserving the sacrificial layer in the middle of the second connection region, and ensuring the gate conductive material to be electrically connected with the etching buffer layer in the edge region of the second connection region, so that the connection column in the contact hole can be electrically connected with the gate layer through the etching buffer layer. By utilizing the method, the process difficulty of etching the contact hole in the step region can be reduced, and the risk of bridging word lines of different layers during etching of the contact hole is eliminated.

Owner:YANGTZE MEMORY TECH CO LTD

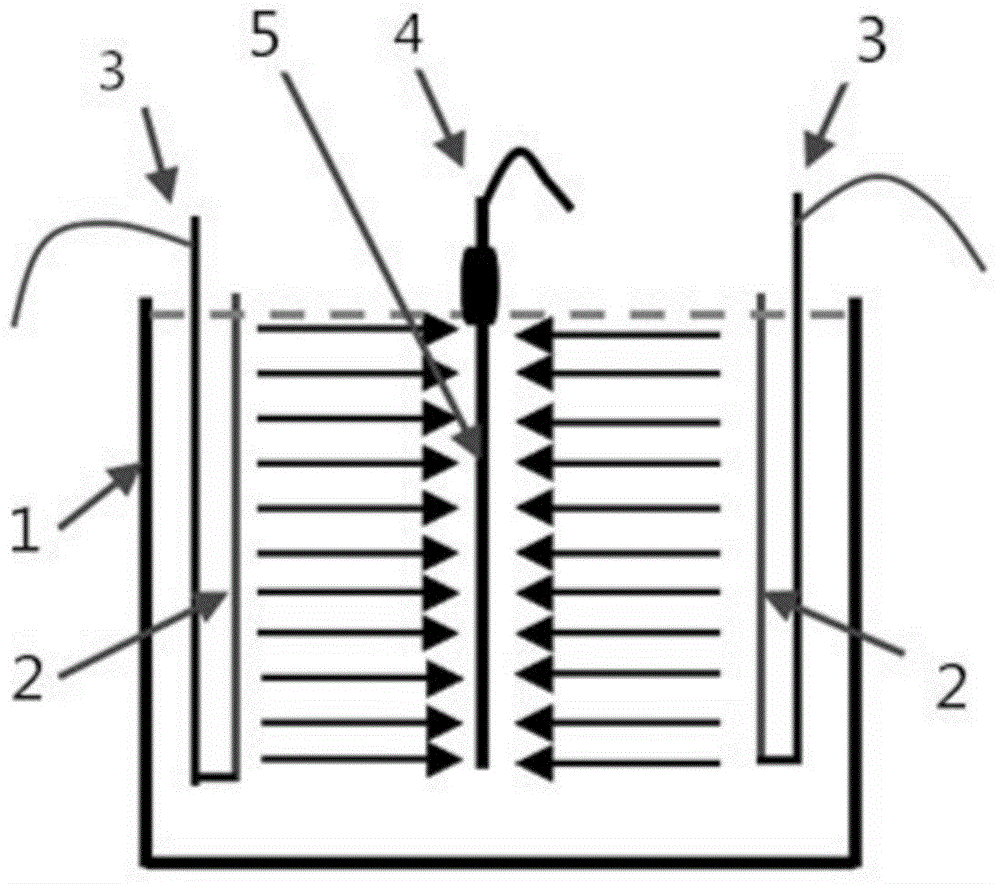

Method for improving electroplating layer uniformity of PCB (printed circuit board) vertical electroplating line

InactiveCN104878424AEliminate vertical length differencesUniform current distributionElectrodesEtchingEngineering

The invention belongs to the field of circuit board processing, and relates to a method for improving the electroplating uniformity of a PCB (printed circuit board). By adopting the method disclosed by the invention, an anode is converted into an up-and-down sliding mode from a position fixing mode so as to ensure that the vertical length difference between a cathode and the anode can be eliminated, and uniform current distribution in an electroplating process can be ensured; a conventional wire connection mode of the anode can be changed so as to ensure that the electrical potential size difference of the current distribution of the anode can be changed and can be complementary with the electrical potential size difference of the current distribution of the cathode; the uniformity of an electroplating copper layer can be improved, and the copper consumption per unit area can be reduced; in a copper electroplating process, integral resistance in an electroplating cylinder is relatively balanced, so that power lines distributed in the electroplating cylinder are uniform, and thus the electrical potential size difference of upper and lower current distribution in the electroplating cylinder can be effectively eliminated; and by adopting the electroplating copper layer with good uniformity, difficulties of circuit etching can be reduced, the purposes of reducing the production scrap rate and improving the quality of the PCB can be achieved, and great market economic values and application prospects can be achieved.

Owner:SHENZHEN SUNTAK MULTILAYER PCB

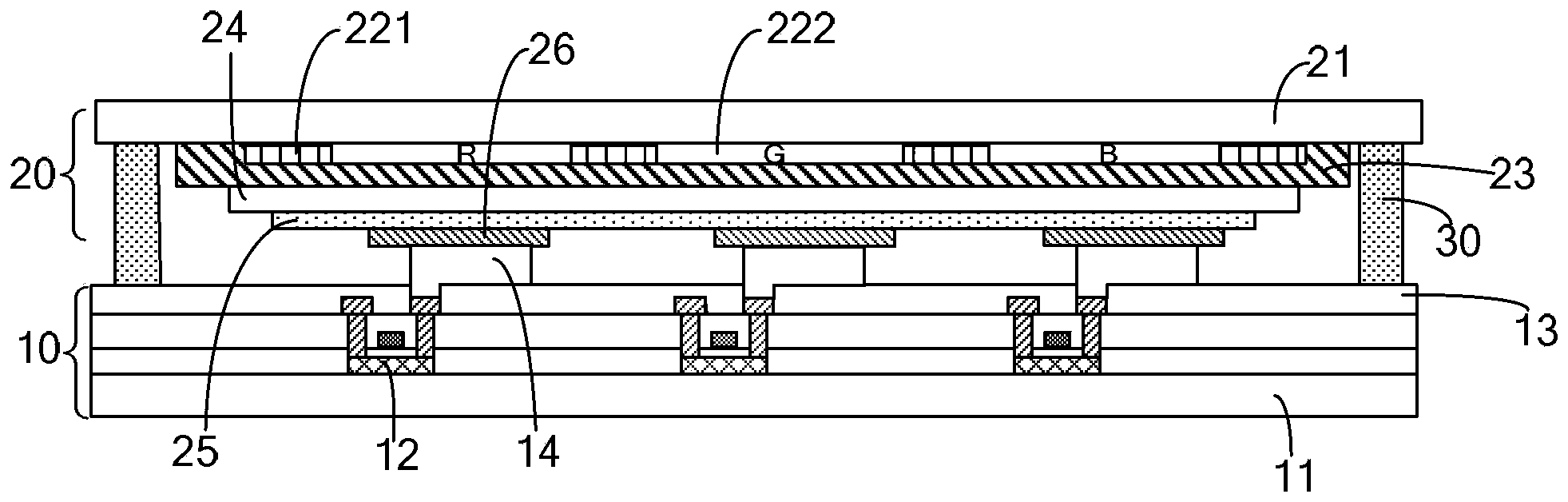

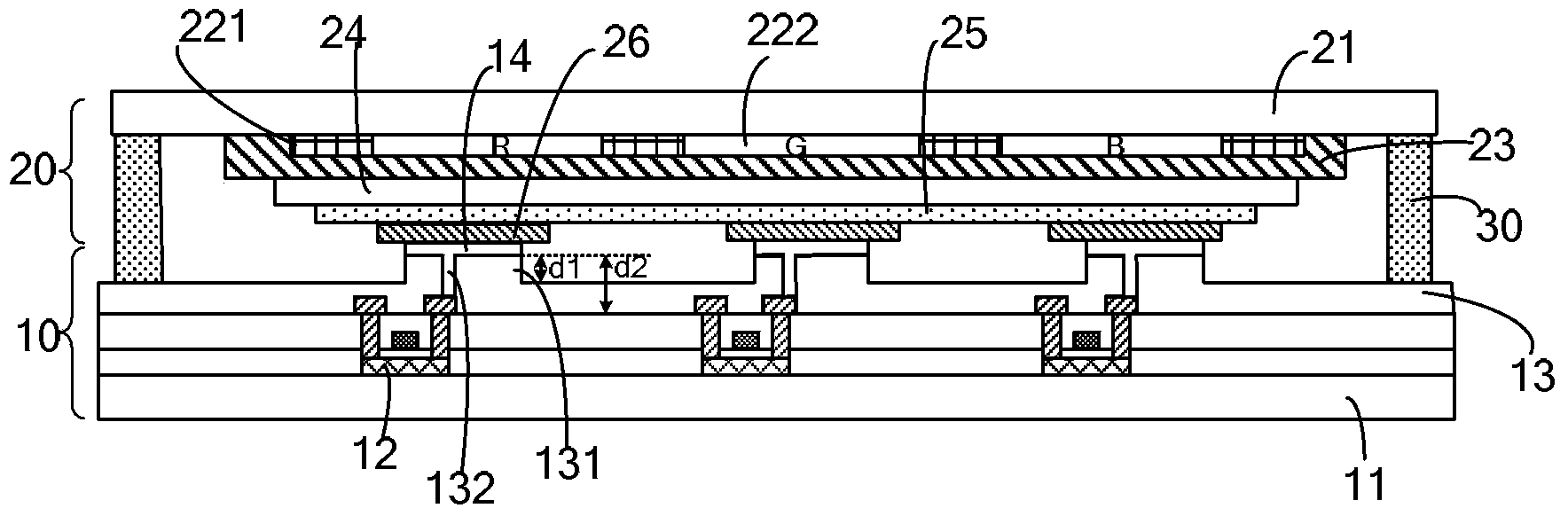

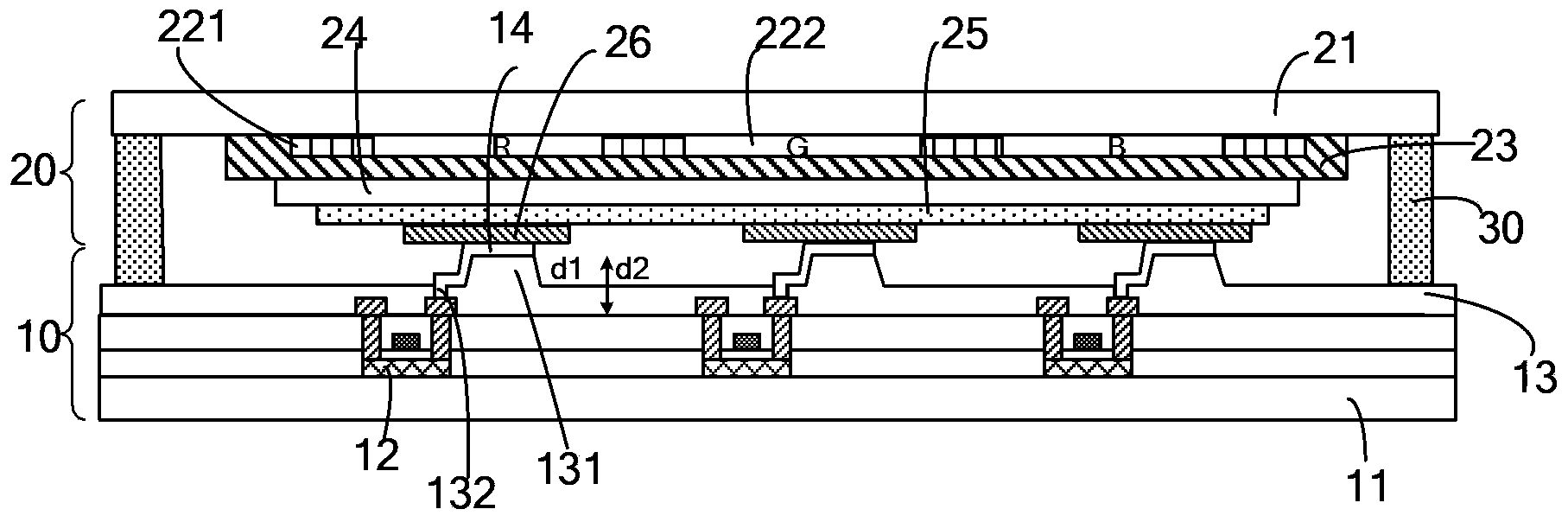

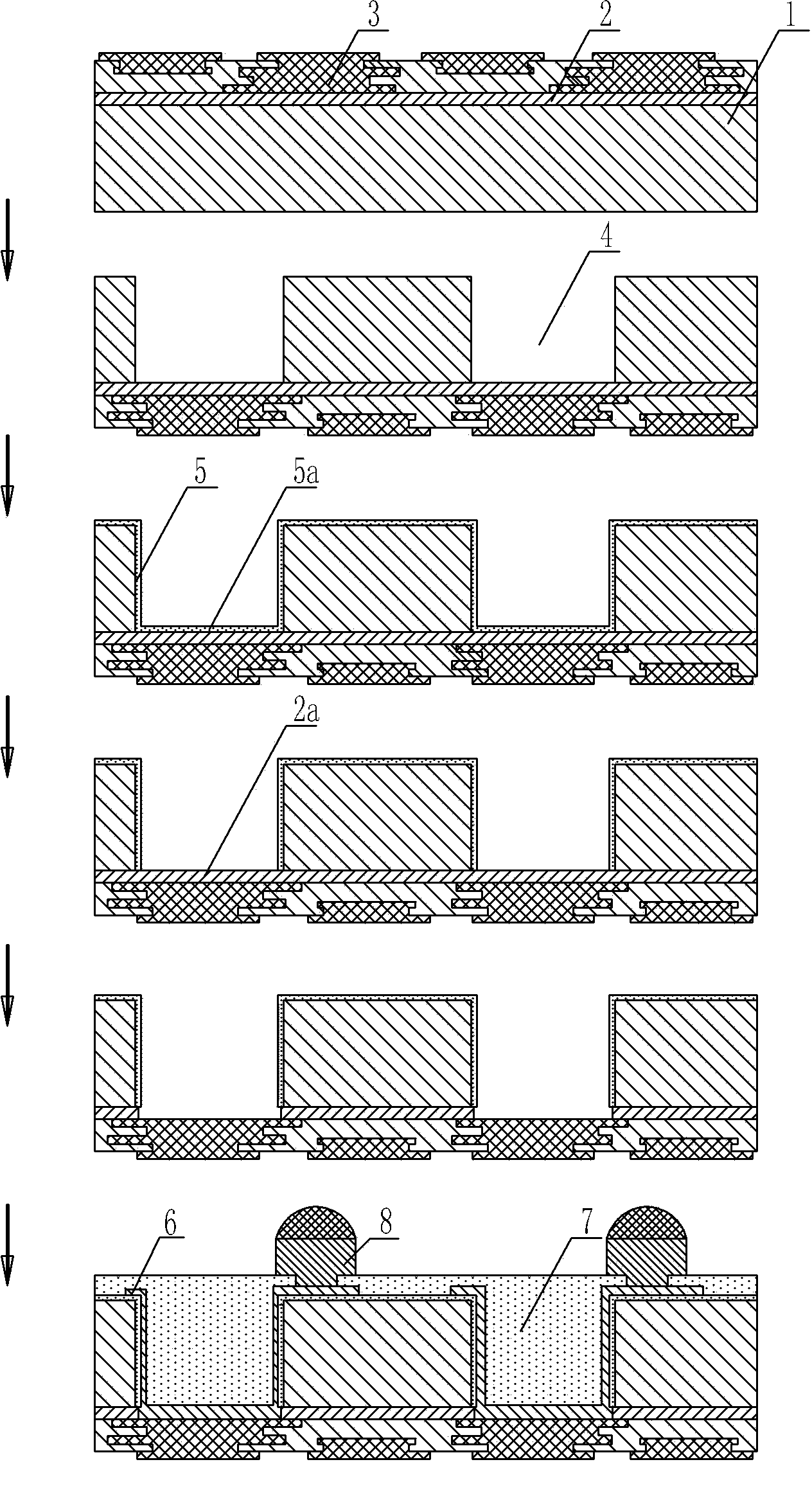

Electroluminescence device and manufacturing method thereof

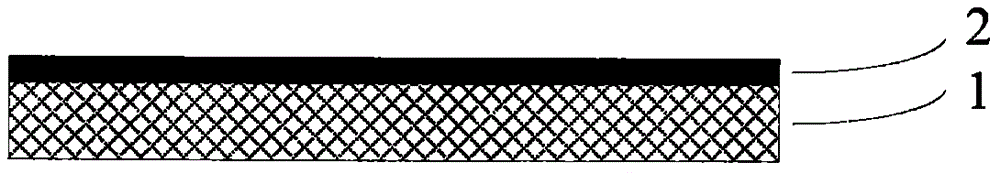

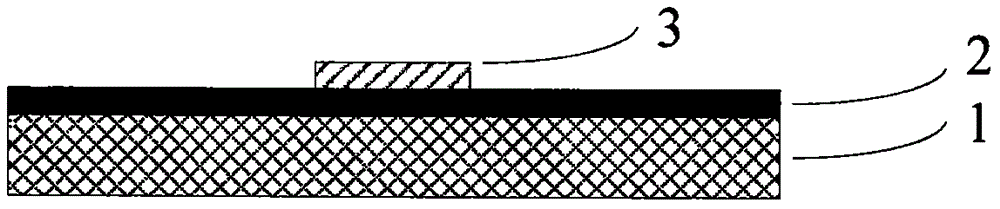

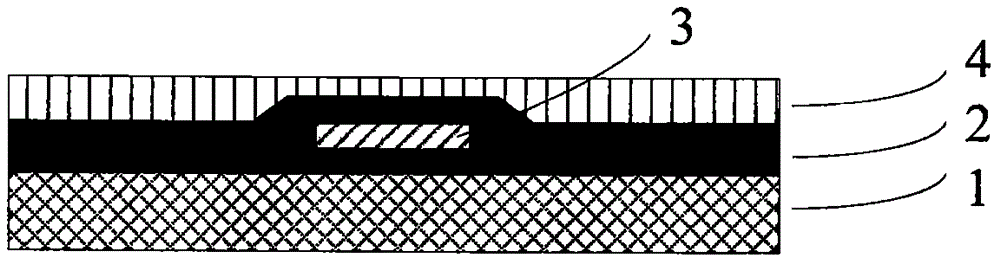

ActiveCN103474453AReduce thicknessShort film forming timeSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringTransistor

An embodiment of the invention discloses an electroluminescence device and a manufacturing method thereof, and relates to the display field. The reliability of electric connection of a thin film transistor and a second electrode is ensured, and in the meanwhile, film forming time can be shortened, the etching difficulty can be reduced and accordingly the production efficiency can be improved in the connecting electrode manufacturing process. The electroluminescence device comprises an array substrate, wherein the array substrate comprises a substrate body, thin film transistors sequentially arranged on the substrate body, protective layers covering the thin film transistors and connecting electrodes arranged on the protective layers. The protective layers under the connecting electrodes protrude towards one side away from the substrate body to form bosses. Protective layer through holes are formed in the positions, corresponding to drain electrodes of the thin film transistors, of the protective layers, and the connecting electrodes are connected with the drain electrodes of the thin film transistors through the protective layer through holes.

Owner:BOE TECH GRP CO LTD

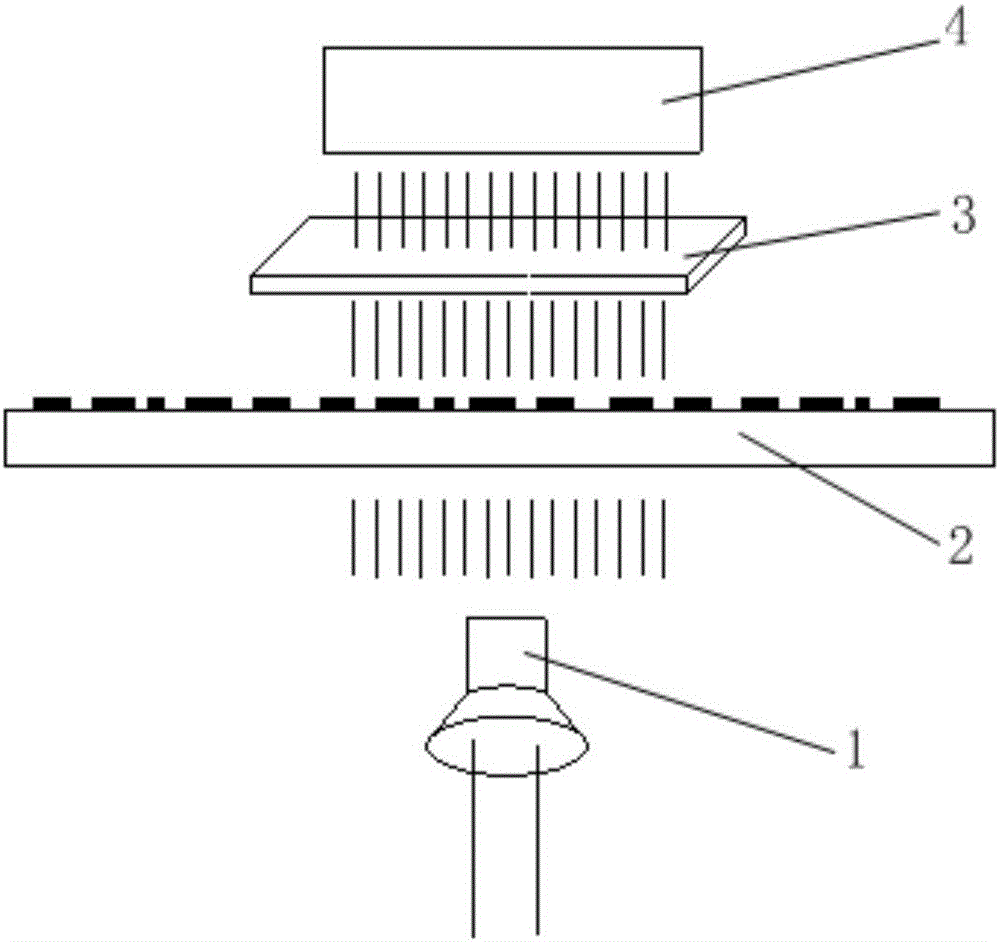

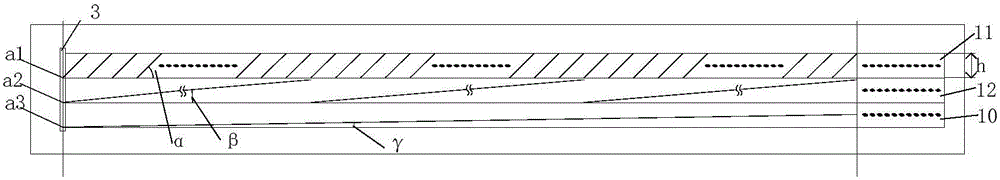

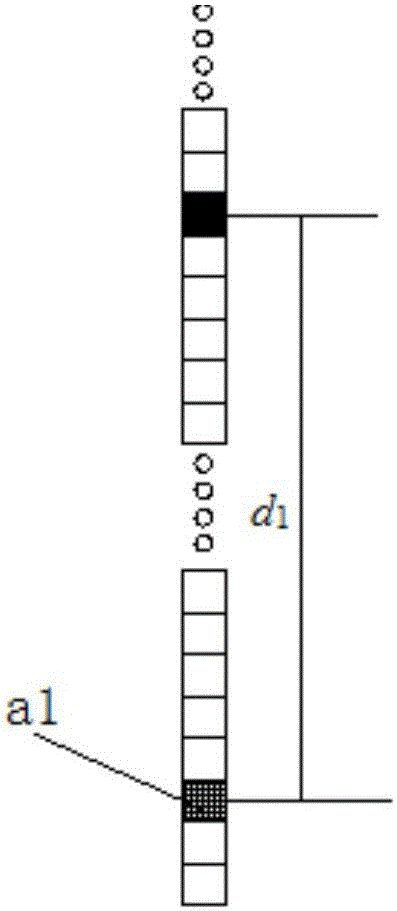

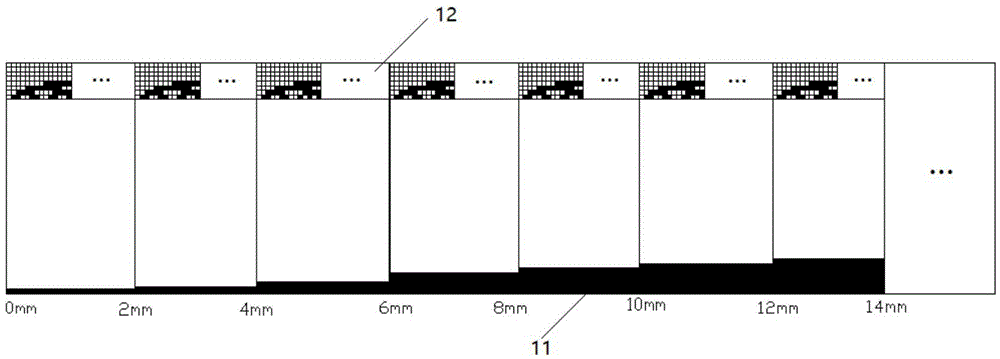

Absolute type grating ruler and measurement method

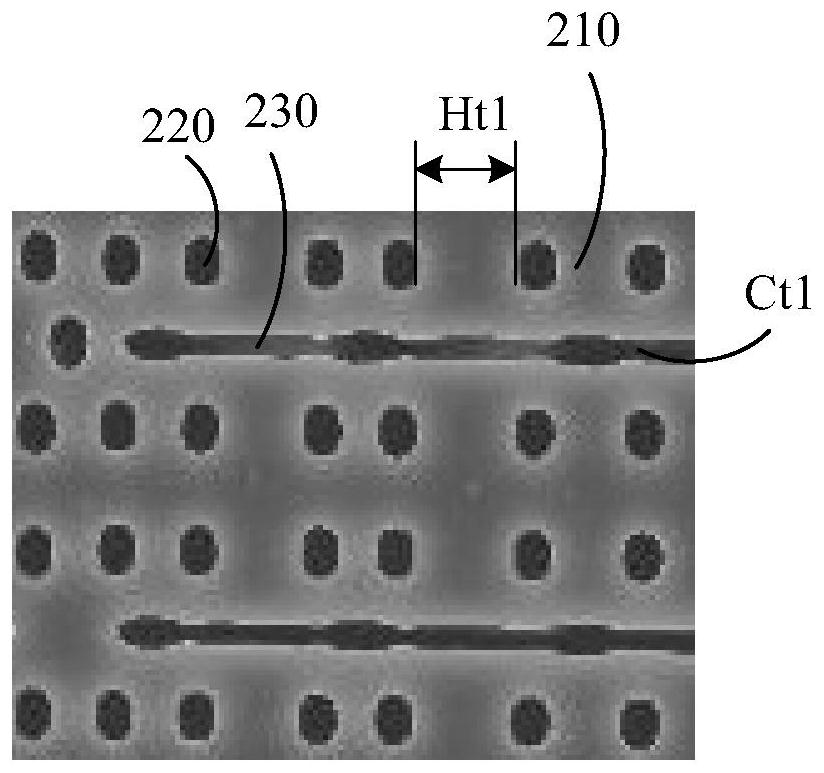

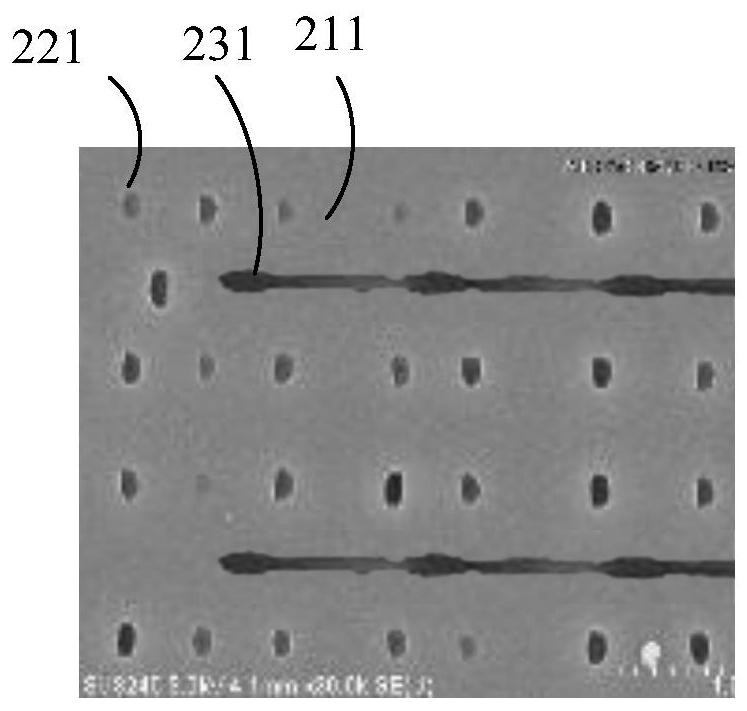

InactiveCN105910631AReduce the difficulty of etchingReduce error rateConverting sensor output opticallyPhotovoltaic detectorsLight source

The invention discloses an absolute type grating ruler and a measurement method thereof. The absolute type grating ruler comprises a parallel light source module, a scale grating, a photoelectric detector and a signal processing module; the scale grating is provided with a basic track and a plurality of coding tracks; the basic track comprises a grating stripe which is inclined relative to the measurement direction; each coding track comprises a plurality of grating stripes which are uniformly and periodically arranged and inclined relative to the measurement direction; each coding track has a different period; parallel light beams emitted by the parallel light source module are radiated to the photoelectric detector after passing through the scale grating; the photoelectric detector is used for collecting arrival light signals and transmitting the measurement electric signals to the signal processing module after converting the arrival light signals to measurement electric signals ; and the signal processing module is used for obtaining measurement values a plurality of the coding tracks after performing processing and analyzing on the measurement electric signals and then obtaining the absolute position measurement value through calculation. The absolute type grating ruler and the measurement method are low in etching difficulty, reduce the manufacture cost, have high measurement accuracy and can be applicable to the grating measurement industry.

Owner:GUANGDONG UNIV OF TECH

Three-dimensional memory structure and preparation method thereof

ActiveCN111769115AEnsure electrical connectionImprove performanceSolid-state devicesSemiconductor devicesElectrically conductiveElectrical connection

The invention provides a three-dimensional memory structure and a preparation method thereof. The preparation method of a three-dimensional memory structure comprises: dividing the step region into afirst connecting region along a second direction, a second connection area and a third connection area, dividing the second connection area into two step subareas along a second direction, forming anetching buffer layer on the surface of the sacrificial layer of the stacked structure exposed by the top surfaces of the steps of the two step partitions; forming a contact hole in the step region onwhich the etching buffer layer is formed, and when the sacrificial layer of the stacked structure is replaced by the gate conductive material, reserving the sacrificial layer in the middle of the second connection region, and ensuring the gate conductive material to be electrically connected with the etching buffer layer at the edge of the second connection region, so that the connection column inthe contact hole can be electrically connected with the gate layer through the etching buffer layer. By utilizing the method, the process difficulty of etching the contact hole in the step region canbe reduced, and the risk of bridging word lines of different layers during etching of the contact hole is eliminated.

Owner:YANGTZE MEMORY TECH CO LTD

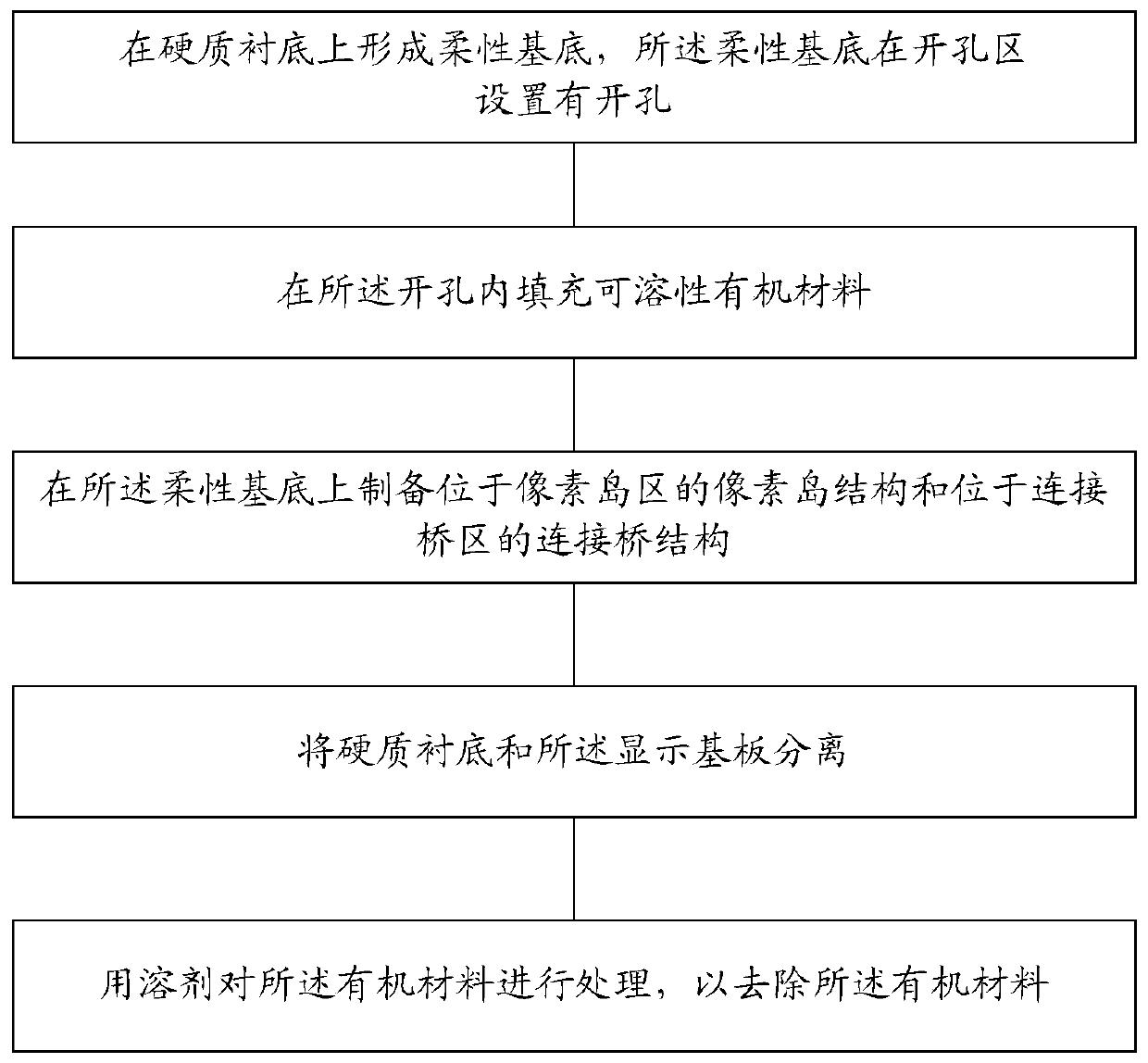

Display substrate, preparation method thereof and display device

The invention discloses a display substrate, a preparation method thereof and a display device. The preparation method of the display substrate comprises the steps that a flexible substrate is formedon a hard substrate, and the flexible substrate is provided with an open hole in an open hole region; the open hole is filled with a soluble organic material; a pixel island structure located in a pixel island region and a connecting bridge structure located in a connecting bridge region are prepared on the flexible substrate; the hard substrate and the display substrate are separated; and a solvent is used for treating the organic material so as to remove the organic material. In the process of preparing the display substrate by the adoption of the method, tensile fracture caused by the openhole region to the pixel island region and the connecting bridge region in the separating process of the hard substrate and the display substrate is reduced, damage to the display substrate is avoided, and the yield of the display substrate is increased; and meanwhile, in the production process of a flat layer, exposure and etching difficulty is lowered, production cost is lowered, and the production difficulty of the display substrate is lowered.

Owner:BOE TECH GRP CO LTD

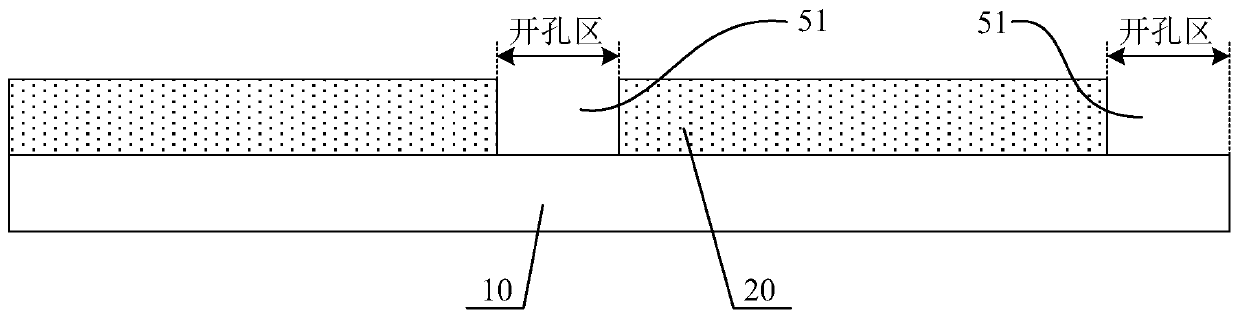

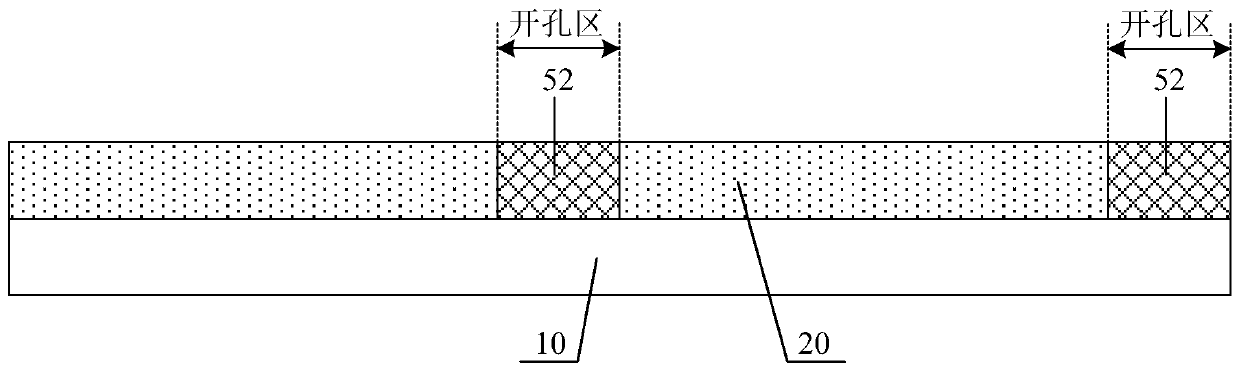

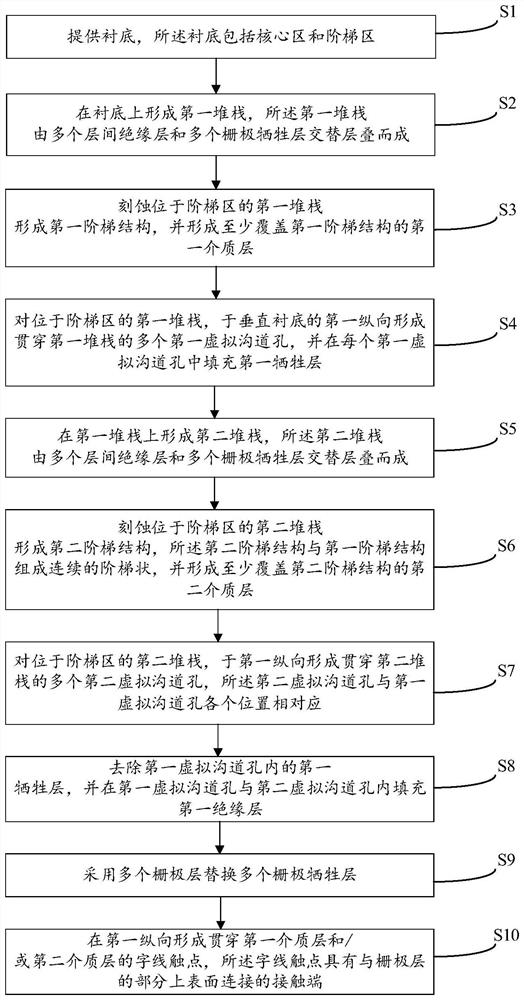

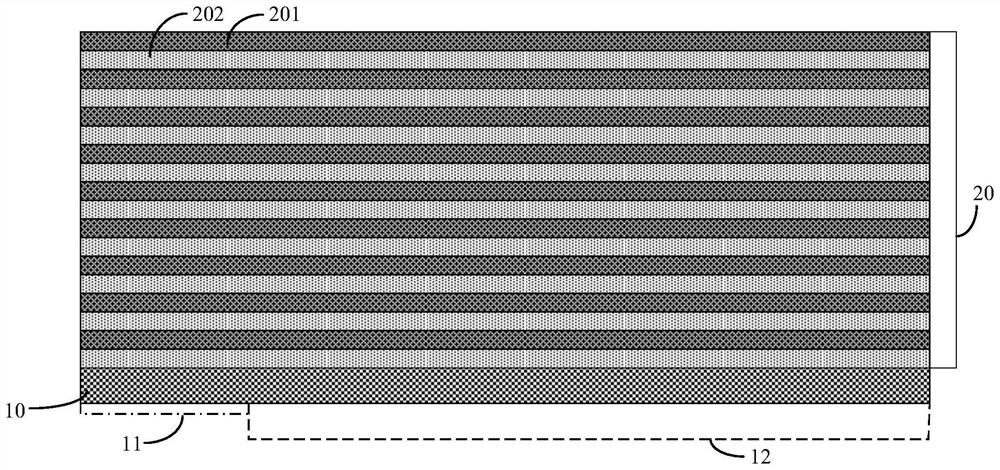

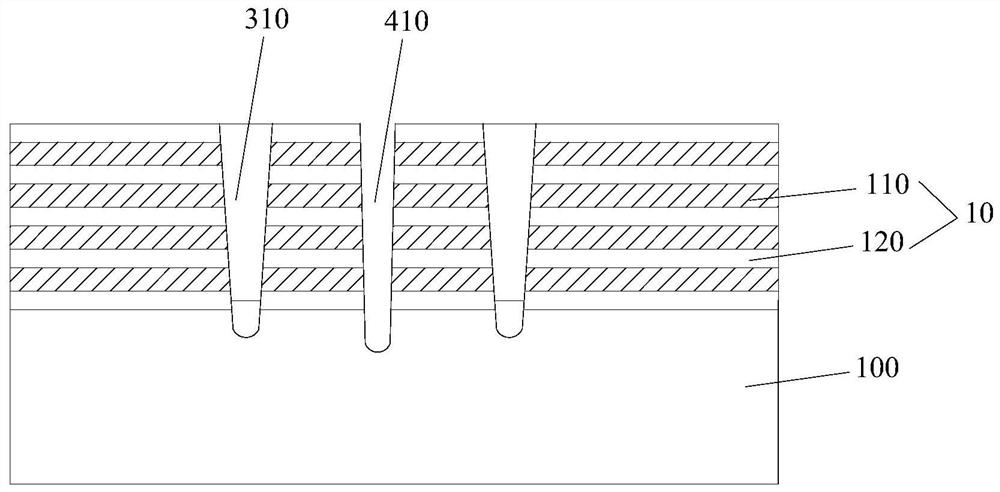

Semiconductor device and manufacturing method thereof

InactiveCN111799273AReduce the difficulty of etchingSmall sizeSolid-state devicesSemiconductor devicesDevice materialMechanical engineering

The invention discloses a semiconductor device and a manufacturing method thereof. The method comprises the following steps: forming a first stack and a first step structure, forming a first virtual channel hole penetrating through the first stack in a step region, forming a second stack and a second step structure, forming a second virtual channel hole penetrating through the second stack in thestep region, and filling a first insulating layer in the first virtual channel hole and the second virtual channel hole. The step structure is formed by etching twice, so that the virtual channel holecan also be formed by etching twice, only half of the stack layer needs to be etched once, the etching difficulty of the virtual channel hole is reduced, the size of the virtual channel hole at the bottom is greatly improved, and the support of the bottom structure is facilitated.

Owner:YANGTZE MEMORY TECH CO LTD

Method of manufacturing high-aperture ratio fine printed circuit board

InactiveCN104105354AAvoid adding surface copperAvoid uniformityPrinted circuit manufactureEngineeringPrinted circuit board

The invention relates to a method of manufacturing a high-aperture ratio fine printed circuit board. The method is characterized by comprising the following steps: (1) a multi-layered board is manufactured; (2) drilling is carried out; (3) hole technology is carried out; (4) first pattern transfer is carried out; (5) electroplating is carried out; (6) polishing is carried out; (7) second pattern transfer is carried out; and (8) alkaline etching is carried out and then the printed circuit board is manufactured. Compared with the prior art, the problems that surface copper is added and surface copper is uneven can be solved, etching amount at the etching side is changed, the etching difficulty is reduced, and the method can be applied to the 3 / 3mil line production.

Owner:SHANGHAI FAST PCB CIRCUIT TECH CORP LTD

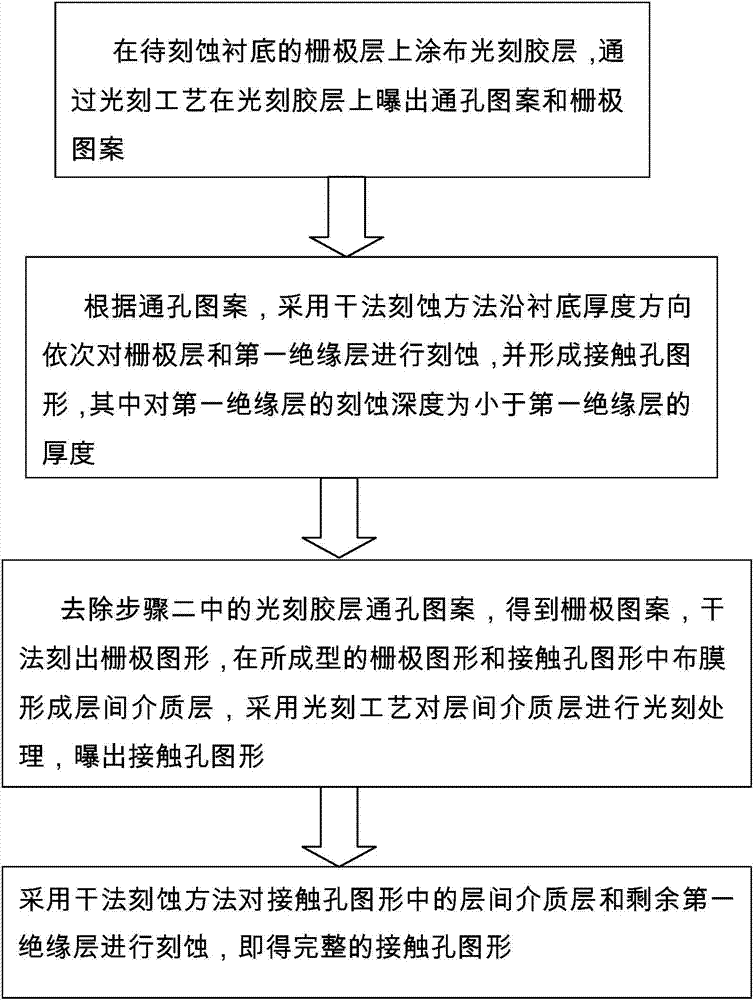

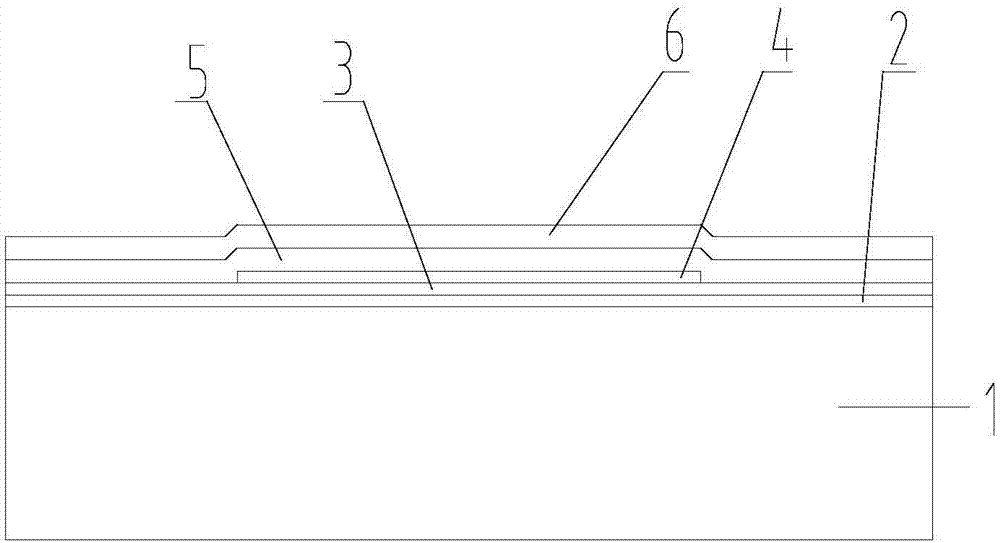

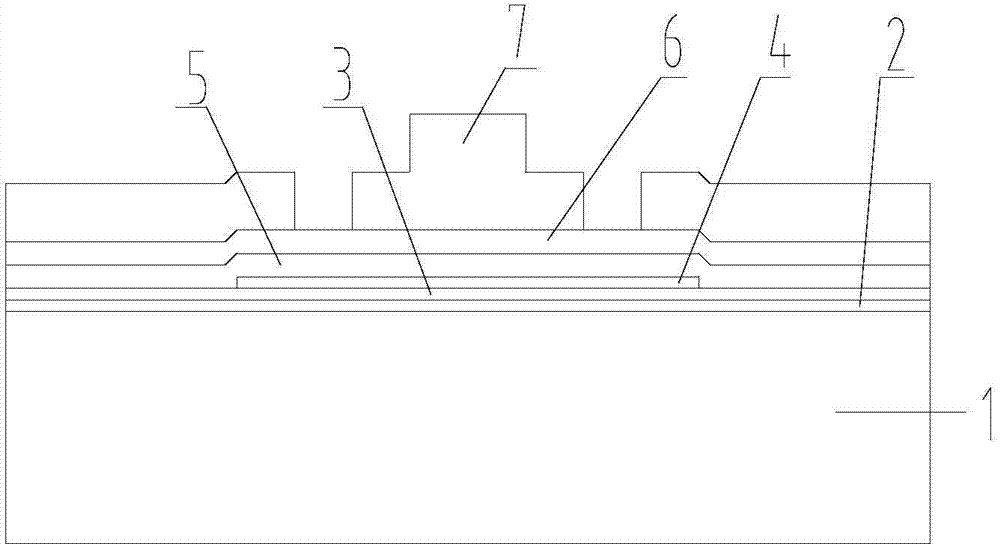

Contact hole etching process, organic light-emitting display device and display device

ActiveCN104505368AReduce the difficulty of etchingPrevent overshootSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceMedia layer

The invention discloses a contact hole etching hole, an organic light-emitting display device and a display device. The etching process comprises the following steps: coating a photoresist layer on a gate electrode layer to expose a through hole pattern and a gate electrode pattern; according to the through hole pattern, etching the gate electrode layer and a first insulating layer in sequence along the substrate thickness direction to form a contact hole figure, removing the through hole pattern of the photoresist layer to etch out a gate electrode figure; arranging a membrane in the molded gate electrode figure and the molded contact hole figure to form an interlayer medium layer, performing photoetching treatment on the interlayer medium layer to expose the contact hole figure; etching the interlayer medium layer and the residual first insulating layer in the contact hole figure to obtain a complete contact hole figure. The etching and molding of the contact hole can be completed only by dry-process etching, the first insulating layer at the lower layer is firstly etched and then the interlayer medium layer on the upper face is etched, so that the problems that the contact hole etching process is difficult in hole depth etching and the etching end point is difficult to detect are avoided.

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD

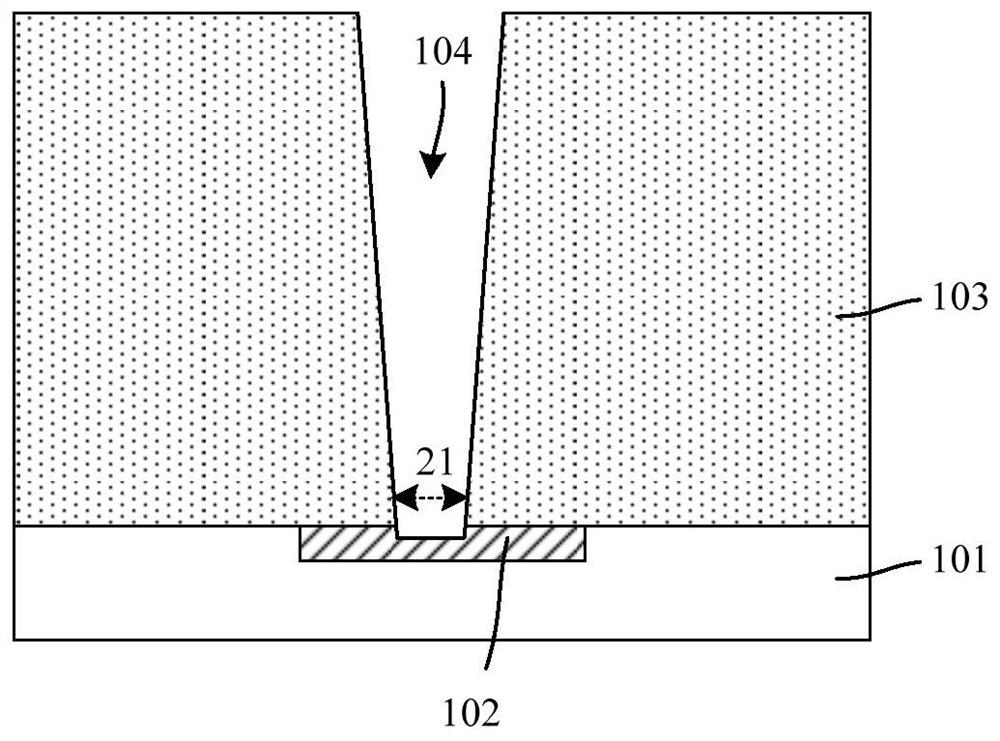

TSV hole bottom medium layer etching method

ActiveCN103367139AReduce the difficulty of etchingAvoid damageSemiconductor/solid-state device manufacturingEtchingWafer

The invention provides a TSV hole bottom medium layer etching method. For TSV holes with small hole diameters, the TSV hole bottom medium layer etching method can reduce TSV hole bottom medium layer etching difficulty and avoid damage to TSV side wall insulating layer materials in the etching process. The TSV hole bottom medium layer etching method includes the steps of step 1, carrying out back face thinning on a wafer comprising an IC device, step 2, manufacturing a TSV hole in a position, corresponding to a metal bonding pad, of the back face of the wafer comprising the IC device, step 3, manufacturing a polymer insulating layer in the TSV hole, step 4, removing the polymer insulating layer at the bottom of the TSV hole and enabling an oxide insulating layer at the bottom of the TSV hole to be exposed, step 5, etching the oxide insulating layer exposed out of the bottom of the TSV hole through wet processing and enabling the metal bonding pad to be exposed, and step 6, manufacturing an RDL through metal connection wires, enabling the RDL and the metal bonding pad at the bottom of the TSV to be connected, and further manufacturing a surface metal bonding pad and slight solder bumps to enable the surface metal bonding pad and the slight solder bumps to be connected with the RDL.

Owner:NAT CENT FOR ADVANCED PACKAGING

Method for improving morphology of capacitor holes

ActiveCN110943163AGood lookingReduce difficultySolid-state devicesCapacitorsCapacitanceMiniaturization

Owner:CHANGXIN MEMORY TECH INC

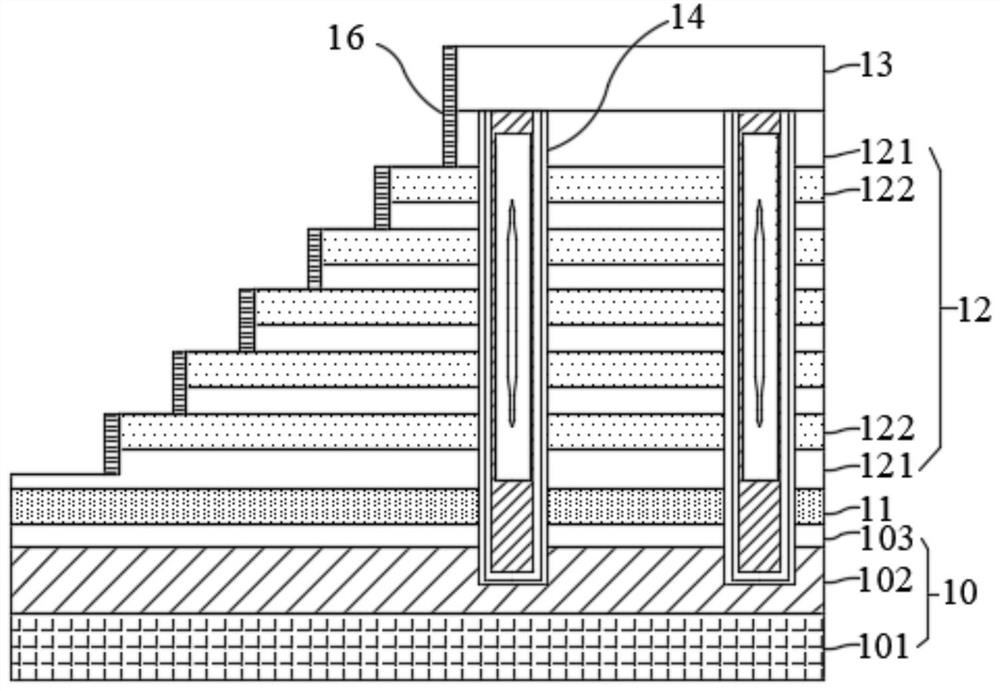

3D memory device and manufacturing method thereof

ActiveCN111180454AImprove flatnessComplete structureSolid-state devicesSemiconductor devicesEngineeringMechanical engineering

The invention discloses a 3D memory device and a manufacturing method thereof. The manufacturing method comprises the steps: forming a first laminated structure on a substrate, wherein the first laminated structure comprises a plurality of interlayer insulating layers and gate conductor layers which are stacked alternately, and the first laminated structure is provided with a first step structure;forming a first filling layer covering the first step structure and the substrate; forming a second laminated structure covering the first laminated structure, the second laminated structure comprising a plurality of interlayer insulating layers and gate conductor layers which are alternately stacked, the second laminated structure having a second step structure; and forming a plurality of firstvirtual channel columns, wherein at least a part of the first virtual channel columns are located in the second step structure, and the top surface of at least one first virtual channel column is thestep surface of the second step structure. According to the manufacturing method, the top surface of the virtual channel column and the step surface of the step structure are coplanar, so that the problem of poor flatness of the device is solved.

Owner:YANGTZE MEMORY TECH CO LTD

Three-dimensional memory and manufacturing method thereof

InactiveCN111952313AReduce the difficulty of etchingStable supportSolid-state devicesSemiconductor devicesStructural engineeringProcess window

The invention relates to a three-dimensional memory and a manufacturing method thereof. The three-dimensional memory comprises a substrate; a core storage area and a step area which are formed on thesubstrate, wherein the core storage area comprises a stacking structure formed on the substrate, and the step area comprises a step structure formed by the stacking structure; a grid line which penetrates through the core storage area and the step area; grooves which are located between every two adjacent grid lines, wherein the length of each groove is less than that of each grid line. The three-dimensional memory provided by the invention comprises the support structure formed by the plurality of grooves, so the problems of insufficient support, even collapse and the like caused by the defects of the deep hole structure can be avoided. The manufacturing method of the three-dimensional memory is simple in process, the etching difficulty of a higher depth-to-width ratio in the three-dimensional memory is greatly reduced, and a process window of a subsequent process is enlarged.

Owner:YANGTZE MEMORY TECH CO LTD

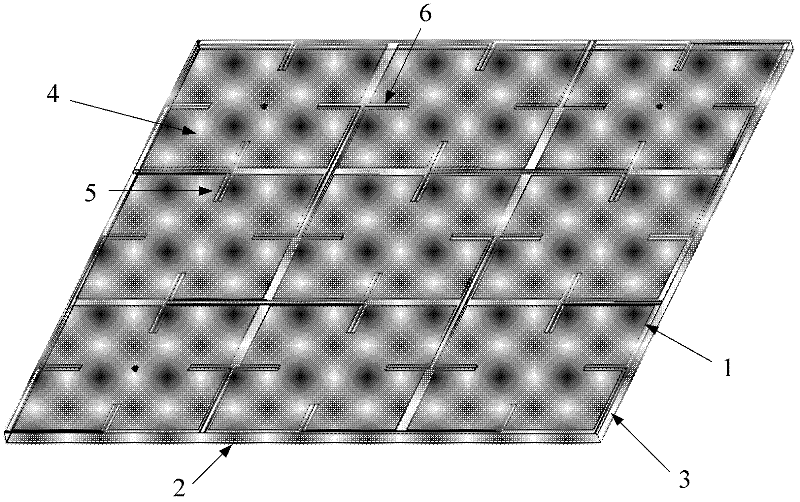

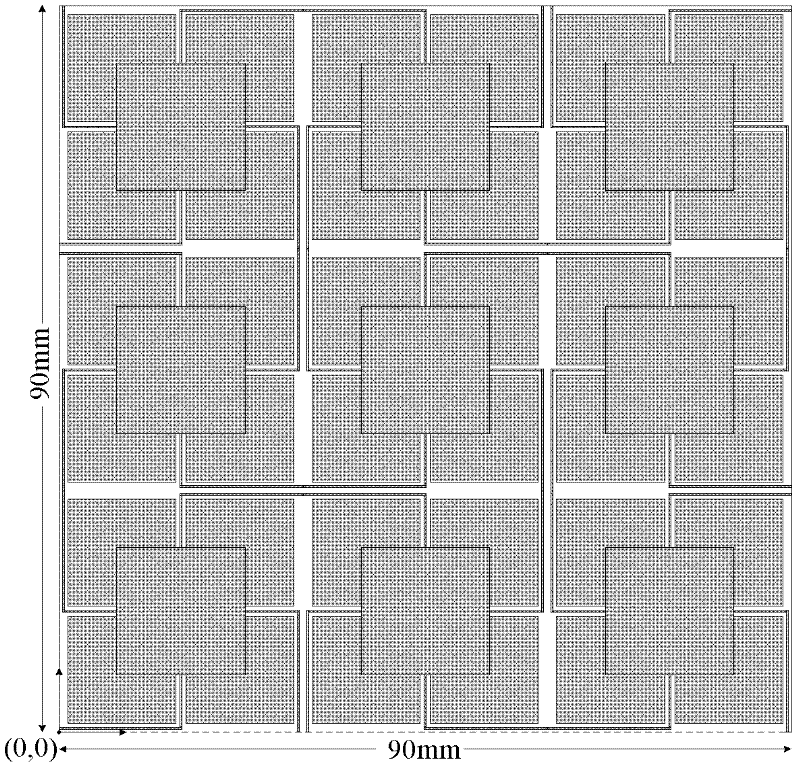

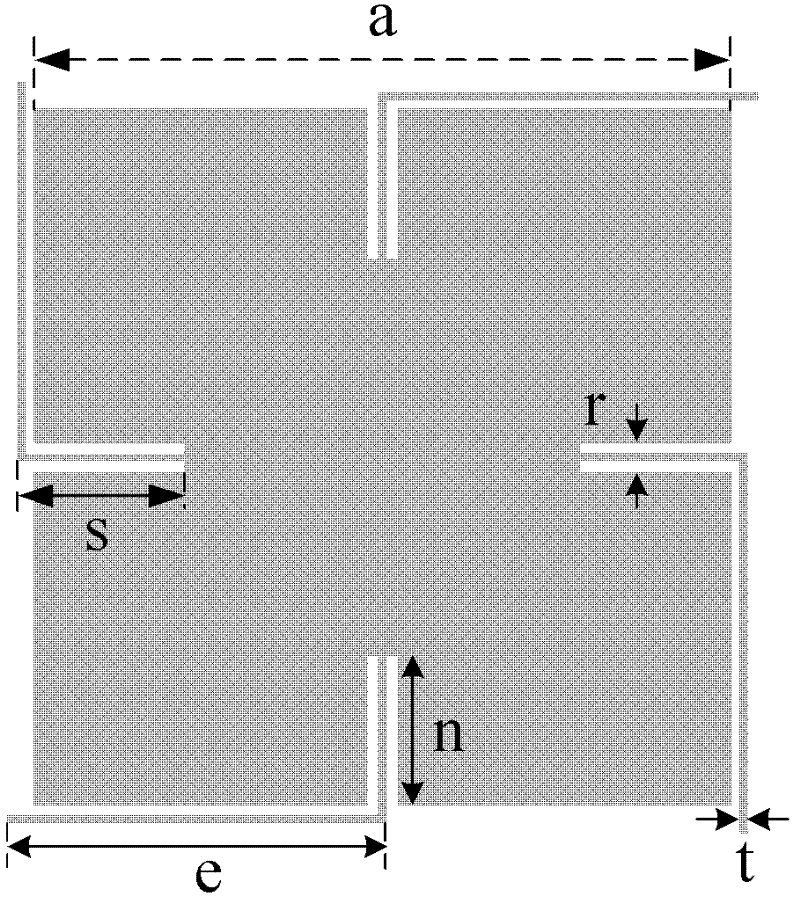

U-shaped electromagnetic band gap circuit board with low-frequency simultaneous switching noise inhibiting function

The invention discloses a U-shaped electromagnetic band gap circuit board with a low-frequency simultaneous switching noise inhibiting function, which mainly solves the problem that the existing electromagnetic band gap circuit board has limited capacity on inhibiting low-frequency simultaneous switching noise with the frequency lower than 1GHz. The electromagnetic band gap circuit board consistsof an electromagnetic band gap layer (1), a stratum (2) and a dielectric layer (3), wherein the electromagnetic band gap layer (1) is formed by connecting n electromagnetic band gap units (4) and thenumber n is determined according to actual engineering needs. The middle position of each edge of the electromagnetic band gap units (4) is provided with a rectangular slot (5), an L-shaped connecting line (6) is led out from the middle position of the rectangular groove from inside to outside, and every two electromagnetic band gap units (4) are symmetrically connected through one L-shaped connecting line to form a U-shaped bridging line, so the electromagnetic band gap units (4) are connected to form the electromagnetic band gap layer (1). The U-shaped electromagnetic band gap circuit boarddisclosed by the invention has stronger capacity in inhibiting the low frequency range simultaneous switching noise, can reduce the interference of the noise on signal transmission and the false operation of electronic devices, and can be used in high frequency electronic circuits of microwaves, antennae and communication.

Owner:XIDIAN UNIV

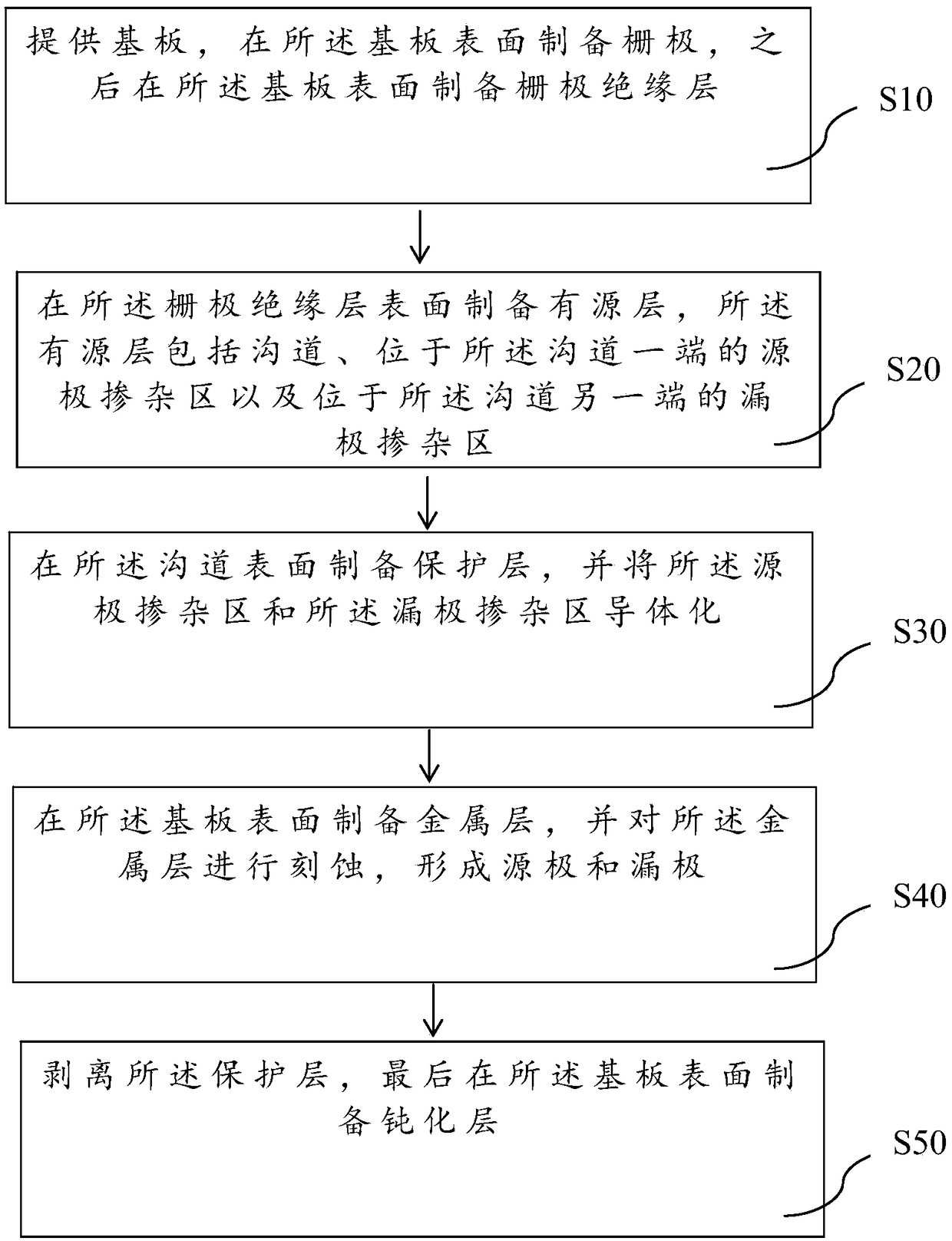

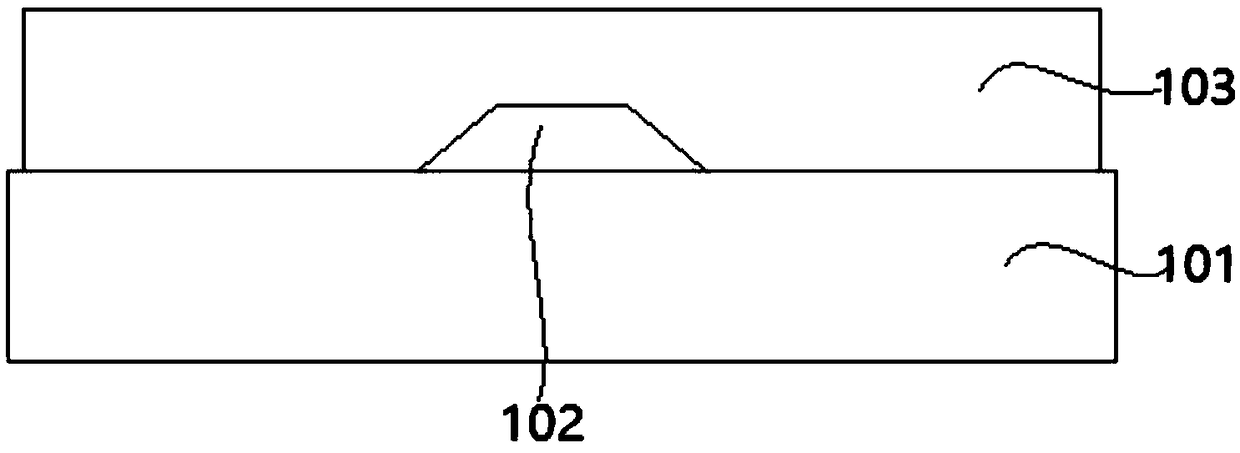

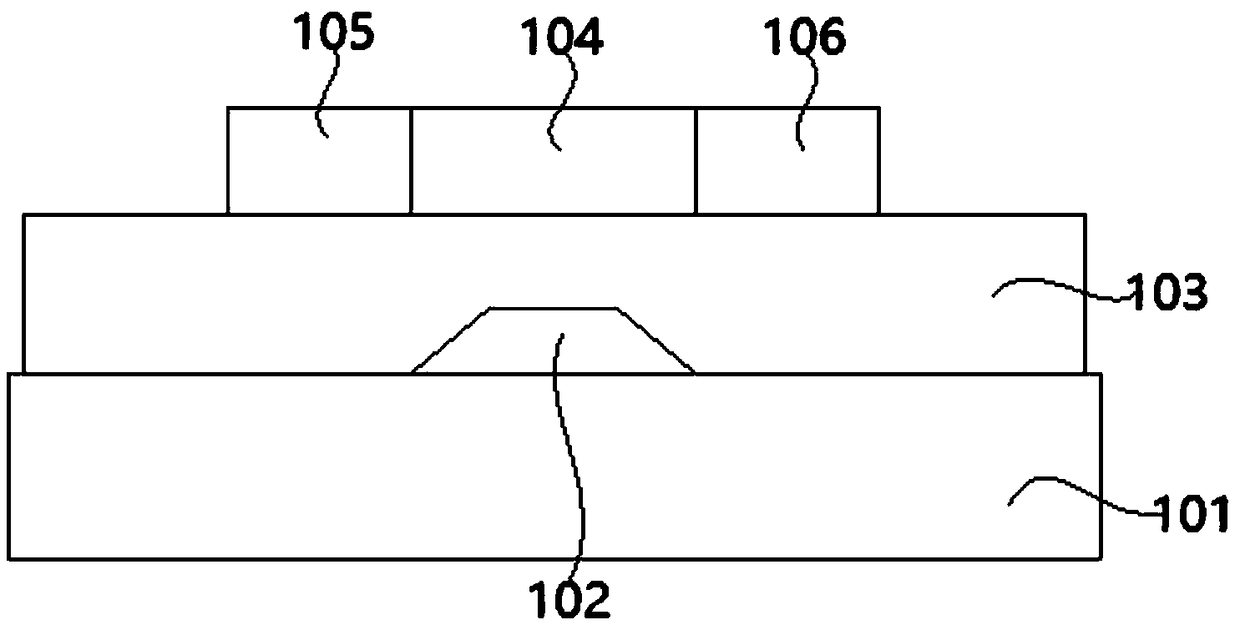

Manufacturing method of TFT array substrate and TFT array substrate

InactiveCN108847408AReduce manufacturing costEasy to solveSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorEngineering

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Beam lead capacitor processing method

ActiveCN106024379AReduce the difficulty of etchingChange multiple depositsFixed capacitor electrodesFixed capacitor dielectricCapacitancePolyimide dielectric

The invention relates to a beam lead capacitor processing method, and the method comprises the following steps: 1, providing a nickel plate, and forming a TiW metal film on the nickel plate through employing a sputter coating method; 2, forming a polyimide dielectric film on the nickel plate through employing a photoetching method; 3, forming a TiW / Au metal layer structure through employing the sputter coating method, and covering the polyimide dielectric film; 4, forming the upper and lower electrodes of a beam lead capacitor through employing a photoetching electroplating method; 5, selectively etching the nickel plate through employing the photoetching method, maintaining the mechanical supporting action of the nickel plate, and enabling the upper and lower electrodes to form circuit break. The invention aims at providing the method which is simpler in processing. Compared with a method provided by a foreign manufacturer, the method improves the production efficiency, reduces the cost, and is worthy of polularization in production.

Owner:THE 41ST INST OF CHINA ELECTRONICS TECH GRP

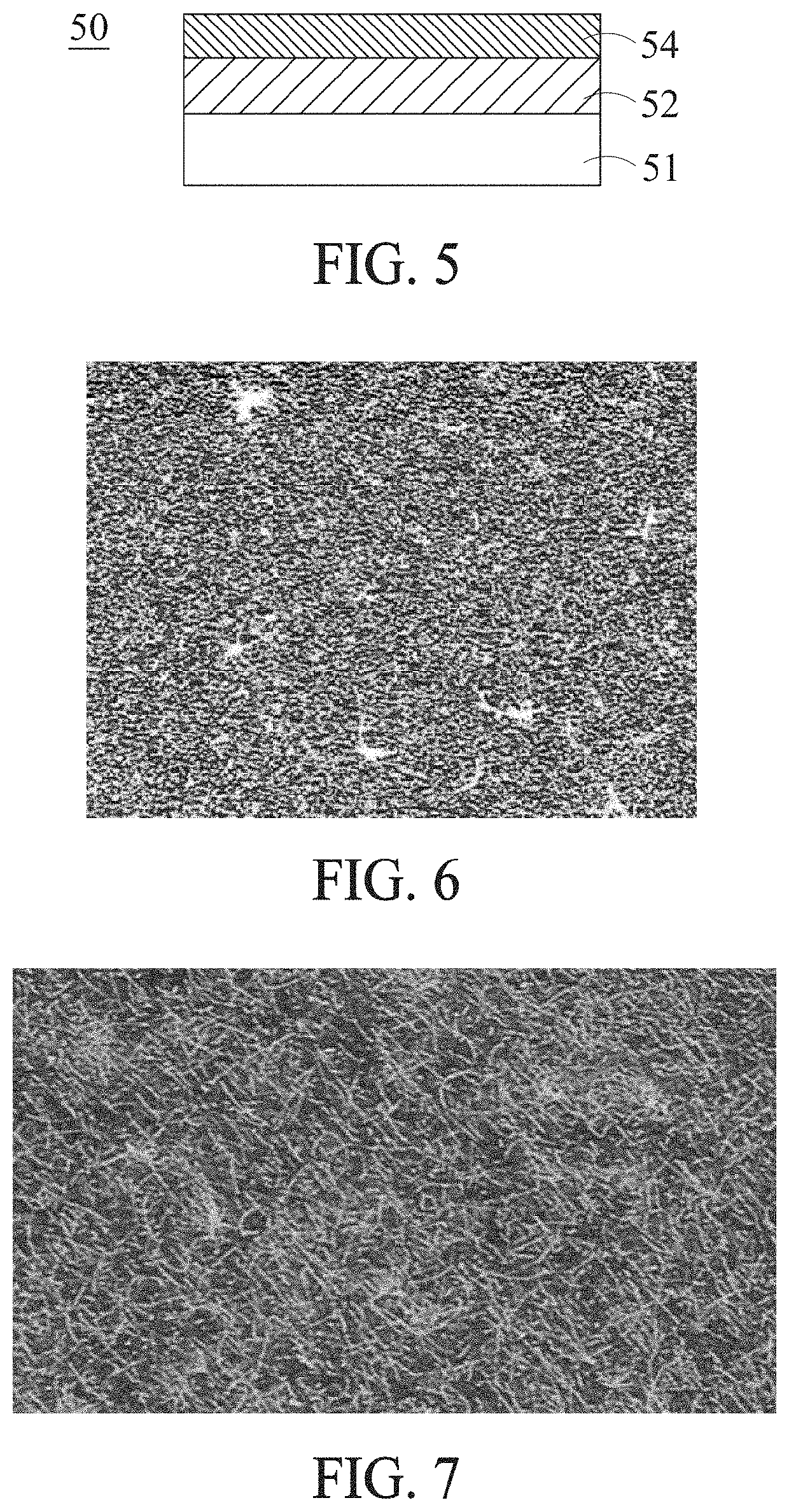

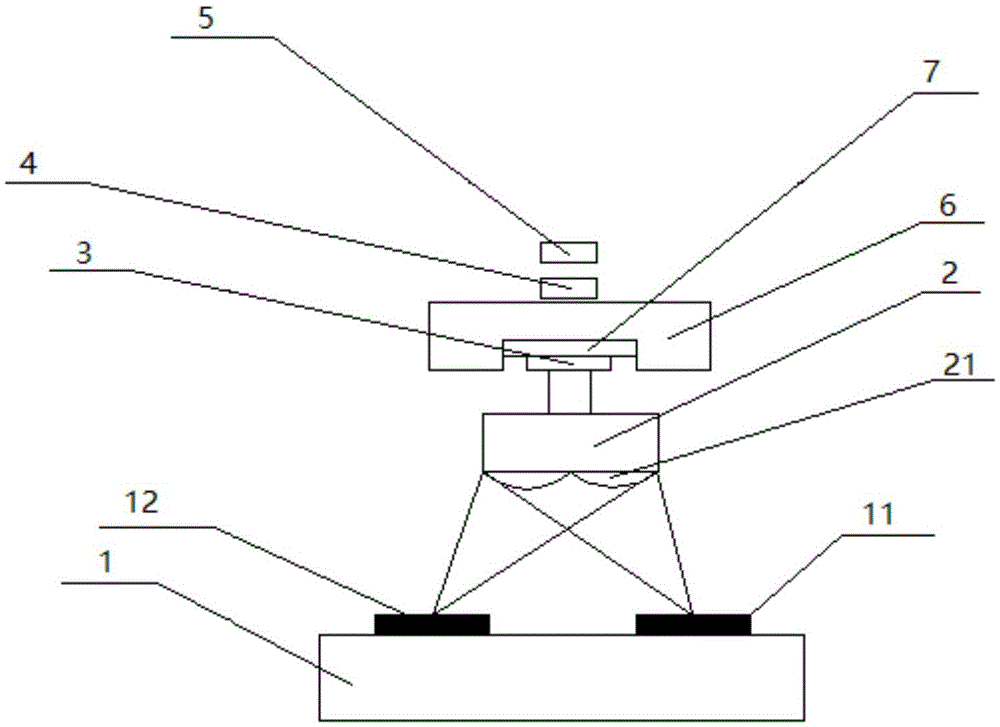

Stack structure and touch sensor

ActiveUS11360622B2Increase in sizeIncrease wire diameterInput/output processes for data processingEngineeringCopper

A stack structure includes: a substrate, a copper layer disposed on the substrate, a migration-proof layer disposed on the copper layer, and a silver-nanowire layer disposed on the migration-proof layer, wherein the migration-proof layer is made of materials between copper and silver in galvanic series. A touch sensor includes the stack structure.

Owner:CAMBRIOS FILM SOLUTIONS CORP

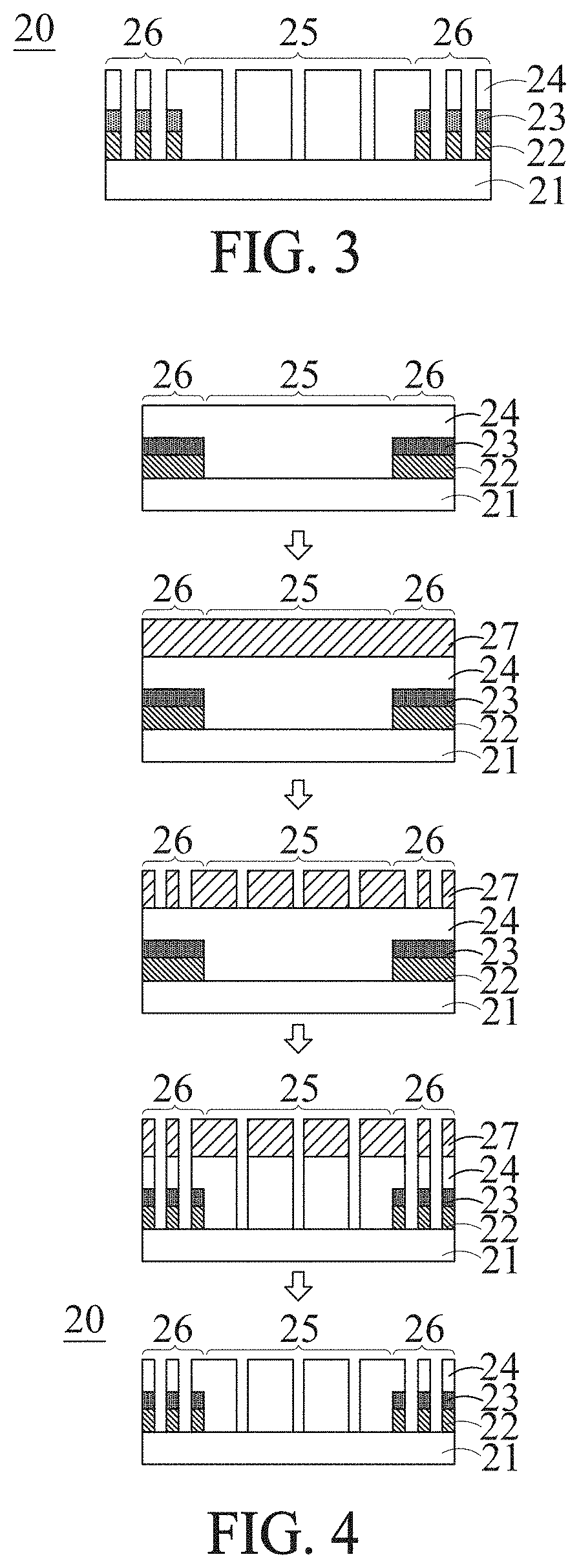

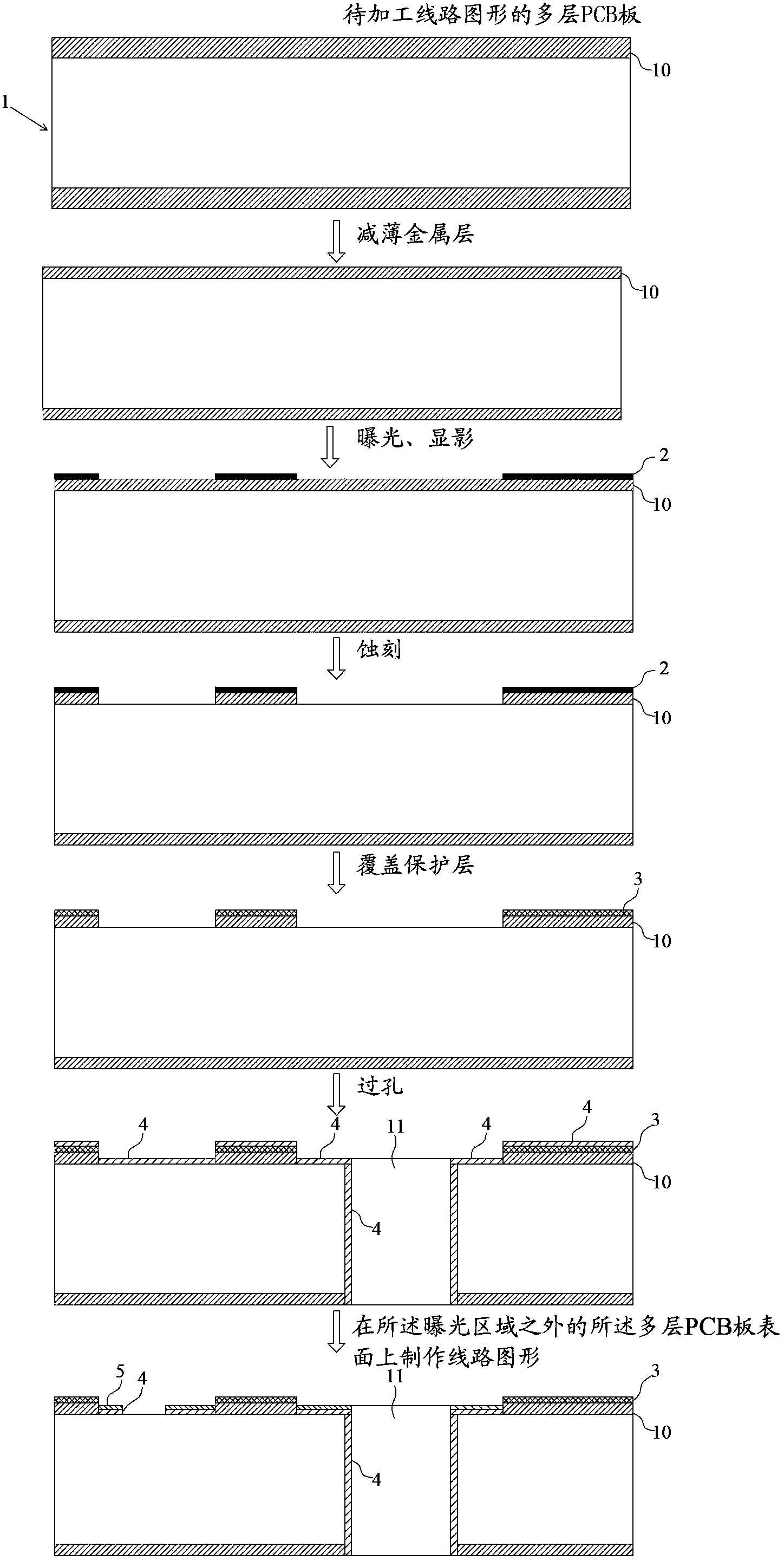

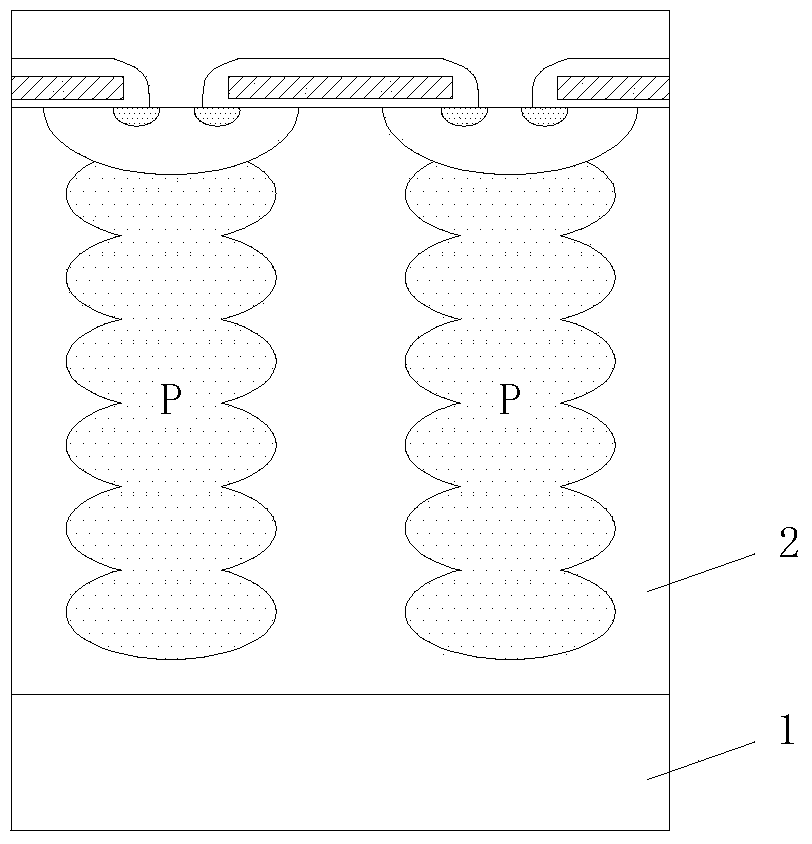

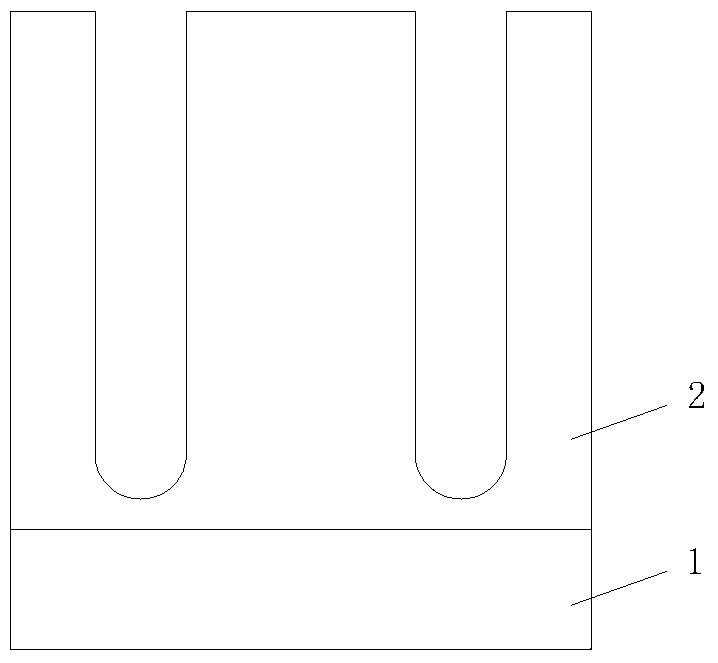

Method for making circuit pattern on multilayer PCB

ActiveCN103582323AHigh precisionAccuracy impactMultilayer circuit manufactureEngineeringProtection layer

The embodiment of the invention discloses a method for making a circuit pattern on a multilayer PCB and relates to the technical field of PCB manufacturing methods. The method is used for manufacturing the circuit pattern with higher precision on the multilayer PCB. The method includes the steps that a dry film is pasted to the surface of a metal layer of the multilayer PCB, exposure is carried out on the multilayer PCB with the dry film pasted to obtain an exposed area and a non-exposed area, and the portion, located in the non-exposed area, of the dry film is removed; etching treatment is carried out on the portion, located in the non-exposed area, of the metal layer so that the circuit pattern corresponding to the exposed area can be formed on the portion, located in the exposed area, of the metal layer; the surface, corresponding to the exposed area, of the circuit pattern is covered by a protective layer; a via hole is formed in the portion, where the circuit pattern corresponding to the exposed area is located, of the multilayer PCB. The method is mainly applied to manufacturing PCB circuit patterns.

Owner:HUAWEI TECH CO LTD

Production process of super-junction device

ActiveCN104201099AReduce aspect ratioImprove balanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringWidth ratio

The invention discloses a production process of a super-junction device. Trenches are etched and filled to form a super-junction. Each trench is etched section by section, so that etching difficulty is greatly reduced, and the sidewall of the trench is more vertical. During a filling process, a depth-to-width ratio of each trench is small, so that filling difficulty is greatly reduced and defects are greatly lessened; meanwhile, by the use of the sectional process, charge balance can be easily maintained for all positions, and breakdown voltage is increased. In addition, by the use of sectional process, the quantity of electric charge can be locally changed, and more device feature optimization methods are provided for designers.

Owner:CHINA RESOURCES MICROELECTRONICS (CHONGQING) CO LTD

Absolute grating scale and measuring method based on CMOS image sensor

The invention discloses an absolute grating scale and a measuring method based on a CMOS image sensor, the absolute grating scale comprises a grating scale main body, an optical amplification system, a CMOS image sensor, a signal processing module and a master control module, a measurement code track and a subdivision code track are arranged on the grating scale main body, the optical amplification system is used for collecting light rays reflected or transmitted through the measurement code track and the subdivision code track, the light rays converge and are incident on the CMOS image sensor, the CMOS image sensor is used for collecting the reached light signal to obtain an analog image of the present measuring position and transmitting the analog image to the signal processing module, the signal processing module is used for converting the analog image into a digital image and transmitting the digital image to the master control module, and the master control module is used for processing the digital image to separately obtain a rough measurement position value and a subdivision position value and combining the position values to obtain an absolute position measured value. According to the invention, the measurement accuracy is high, the measurement resolution is greatly improved, and the grating scale and the method can be widely applied in grating measurement industry.

Owner:GUANGDONG UNIV OF TECH

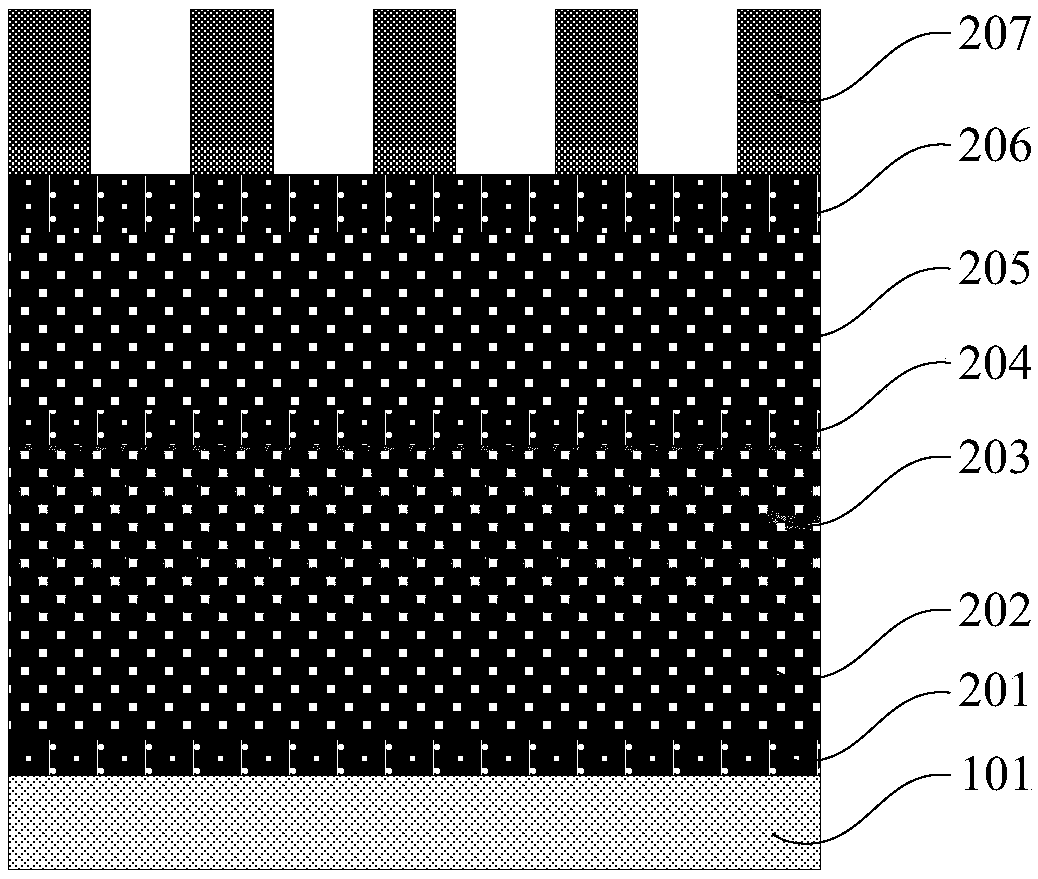

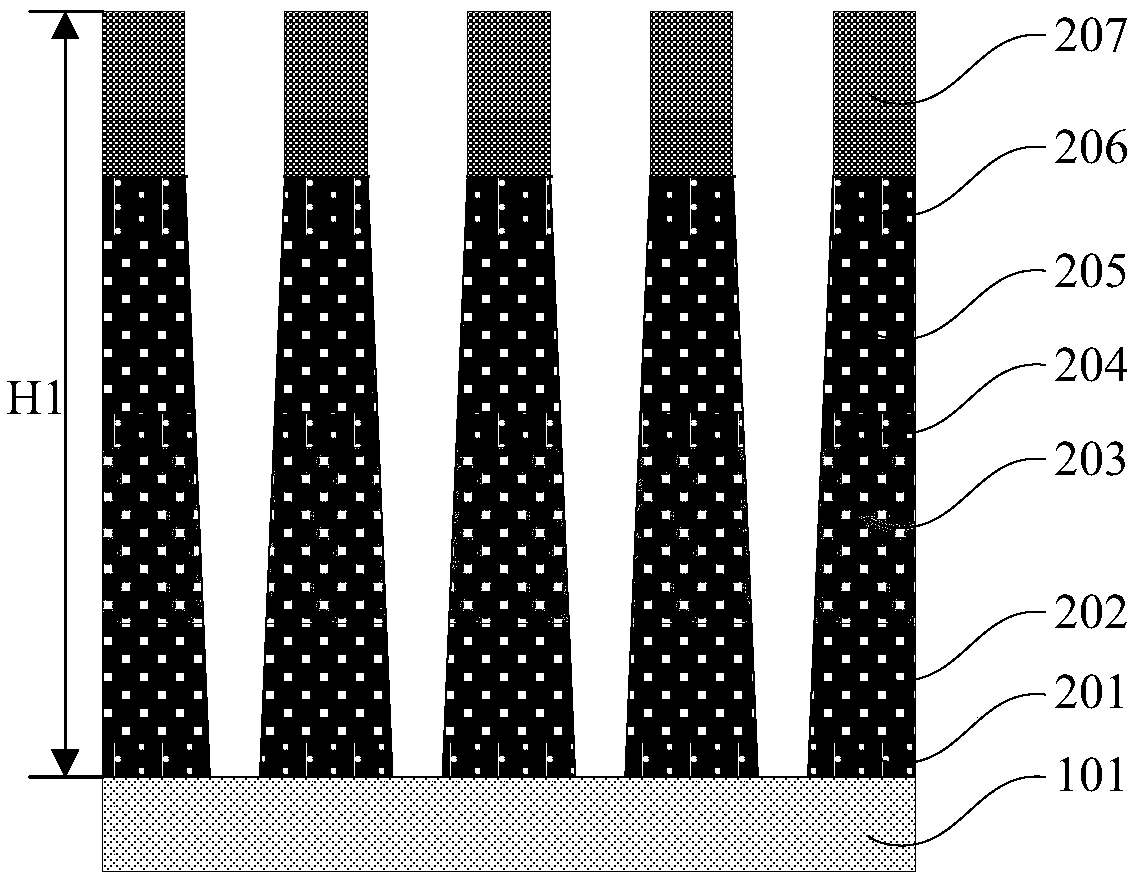

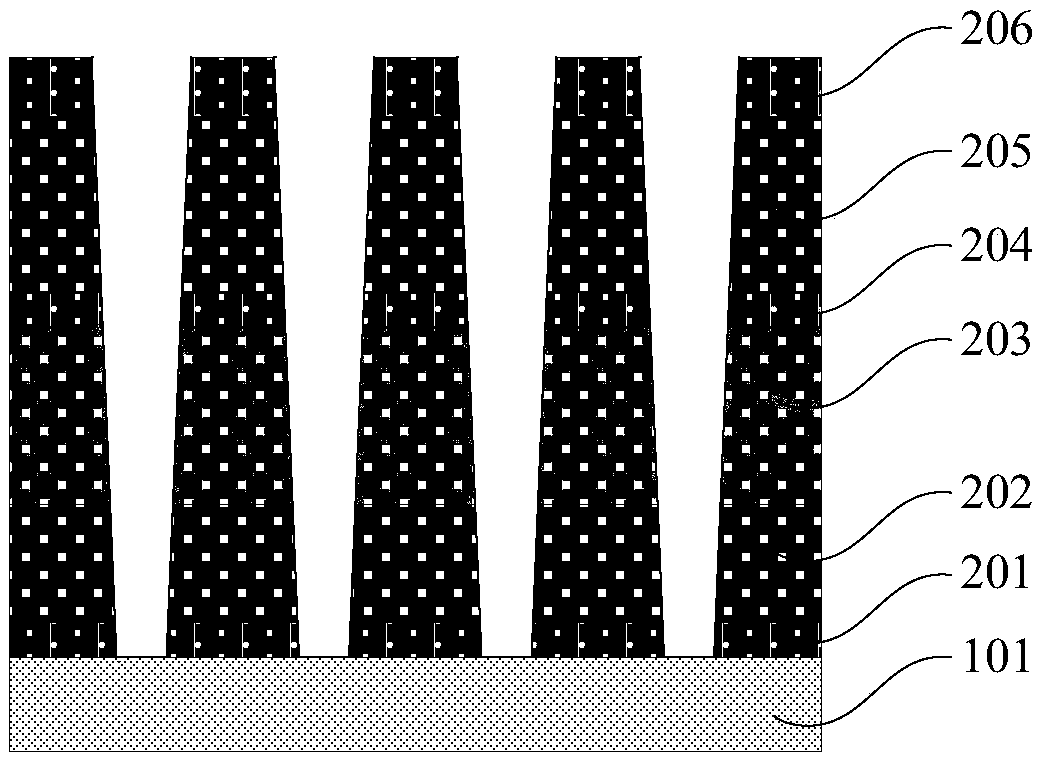

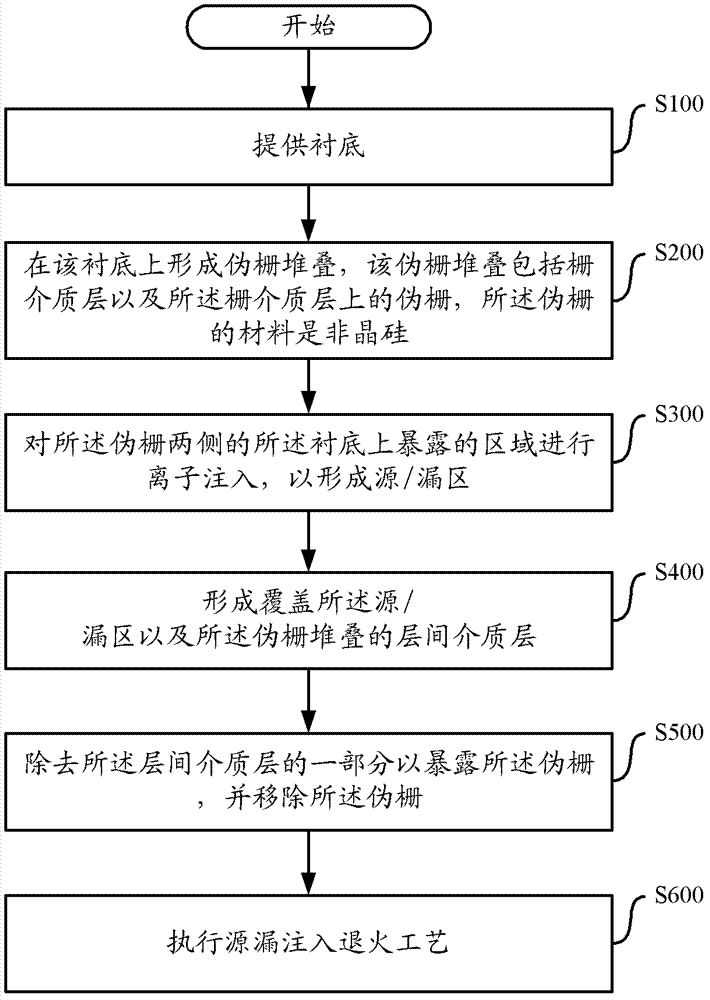

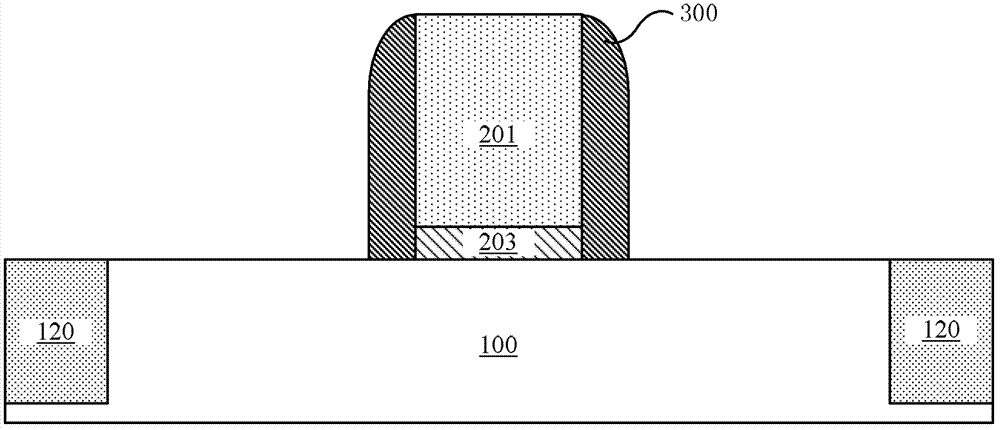

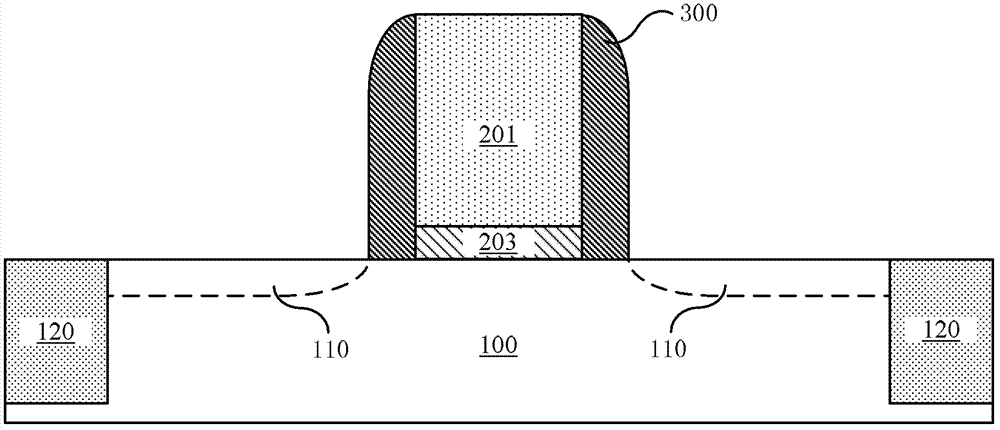

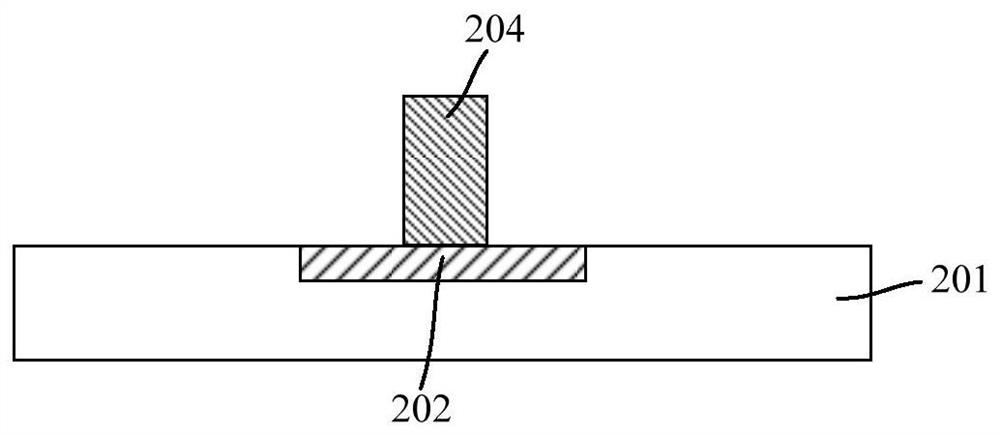

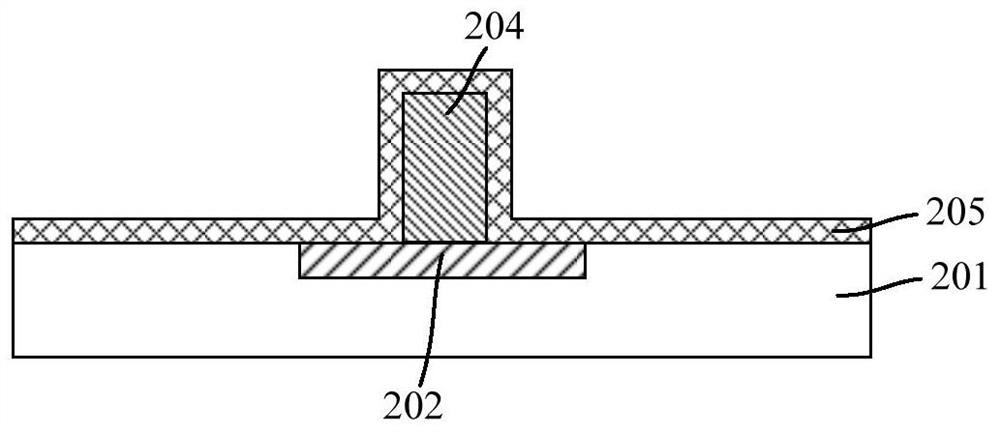

Manufacturing method of semiconductor structure

InactiveCN103094120AGuaranteed stabilityEasy to control etching timeSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureMedia layer

The invention provides a manufacturing method of a semiconductor structure. The manufacturing method includes that (a) substrates (100) are provided; (b) false grid stacking is formed above the substrates (100), wherein the false grid stacking comprises a grid electrode medium layer (203) and a false grid (201) which is arranged above the grid electrode medium layer (203), and the false grid (201) is made of non-crystalline silicon materials; (c) ion implantation is conducted on exposure areas of the substrates (100) on two sides of the false grid (201), so that a source / leaking area (110) is formed; (d) an interlayer medium layer (400) which covers the source / leaking area (110) and the false grid stacking is formed; (e) a part of the interlayer medium layer (400) is removed so as to expose the false grid (201), and the false grid (201) is removed; (f) source and leaking implantation craft is executed. A traditional process of replacing grid craft is changed by the manufacturing method of the semiconductor structure, so that corrosion time is easy to control, corrosion difficult is reduced, and stability of corrosion craft is guaranteed.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

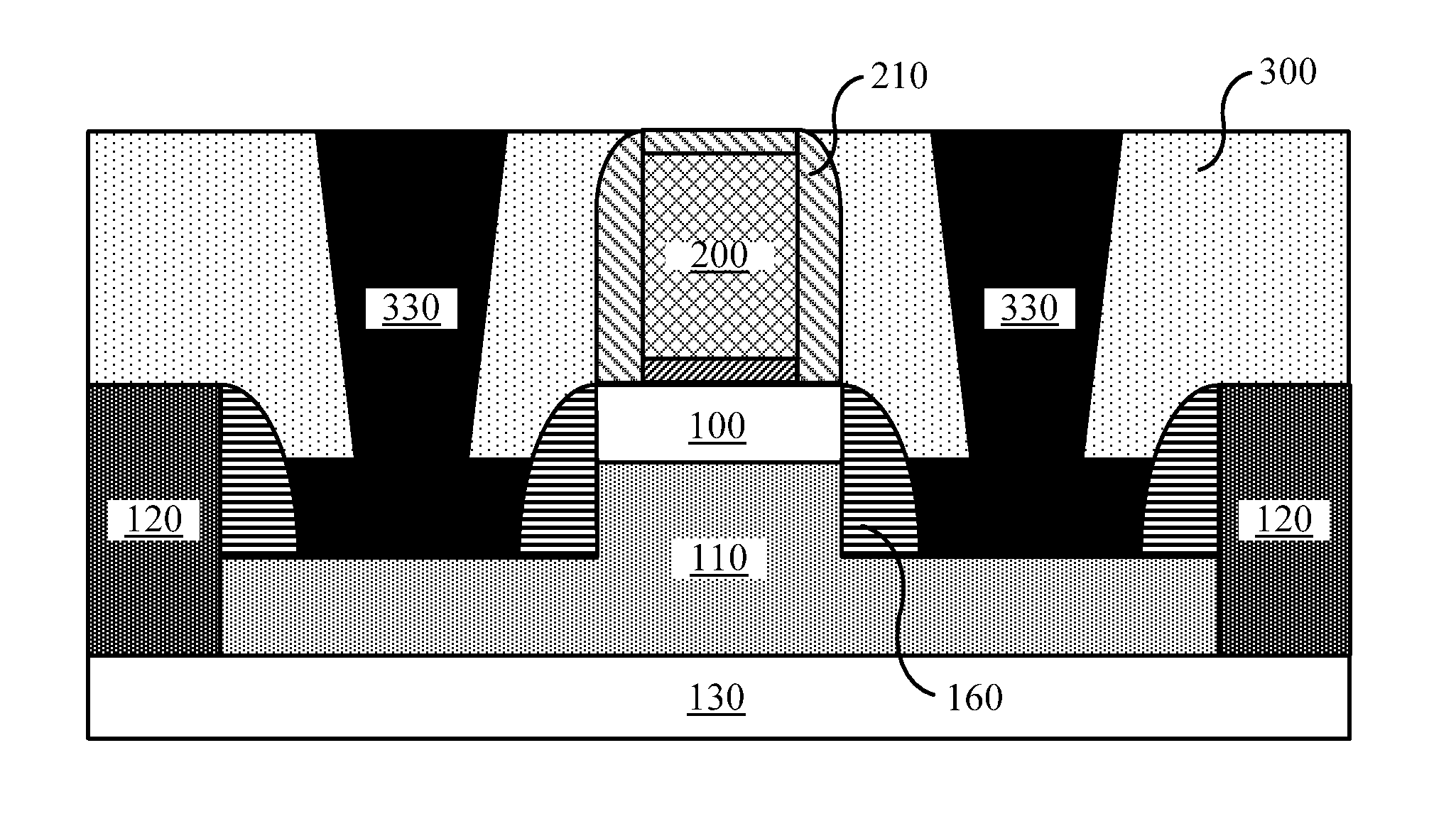

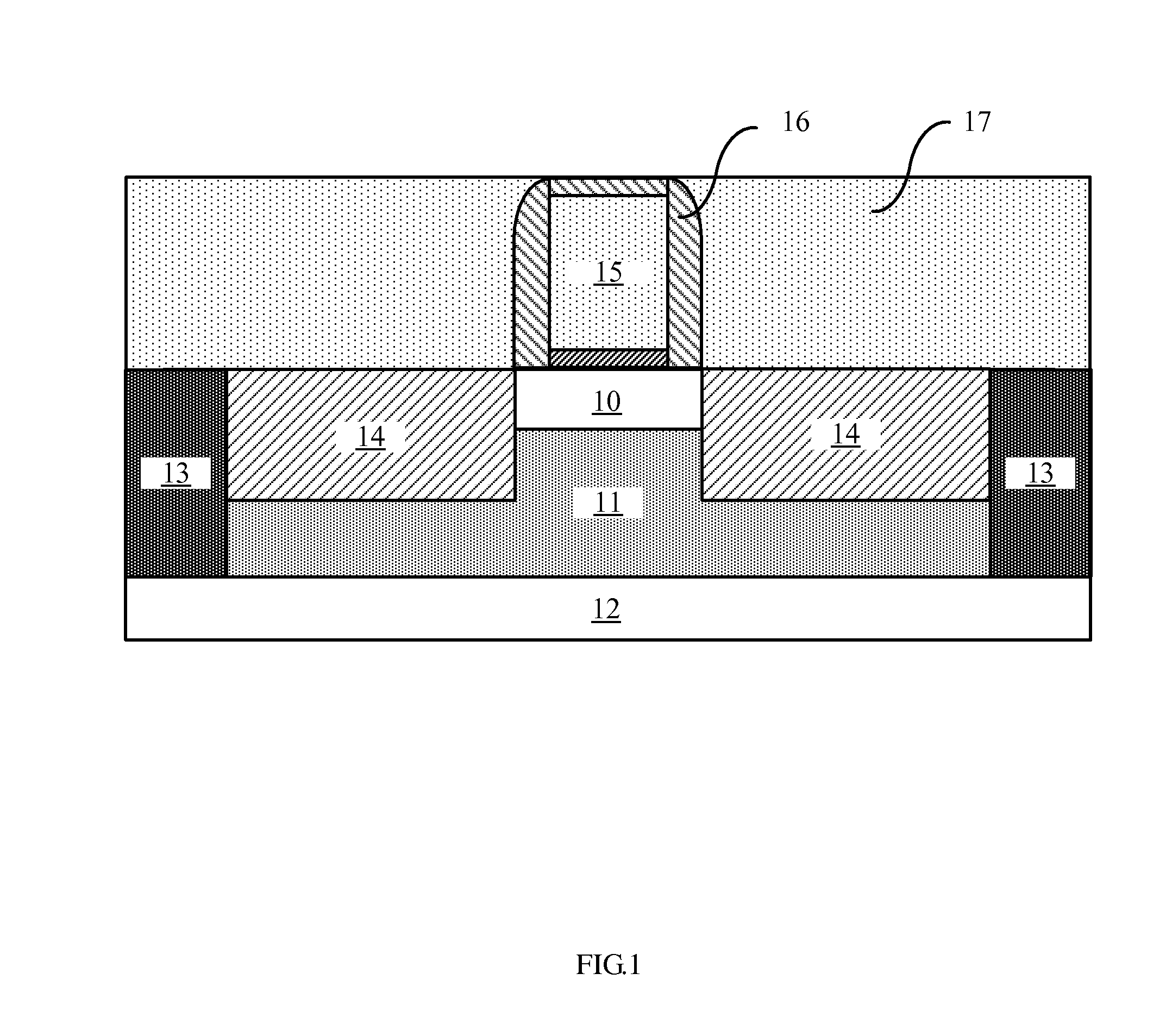

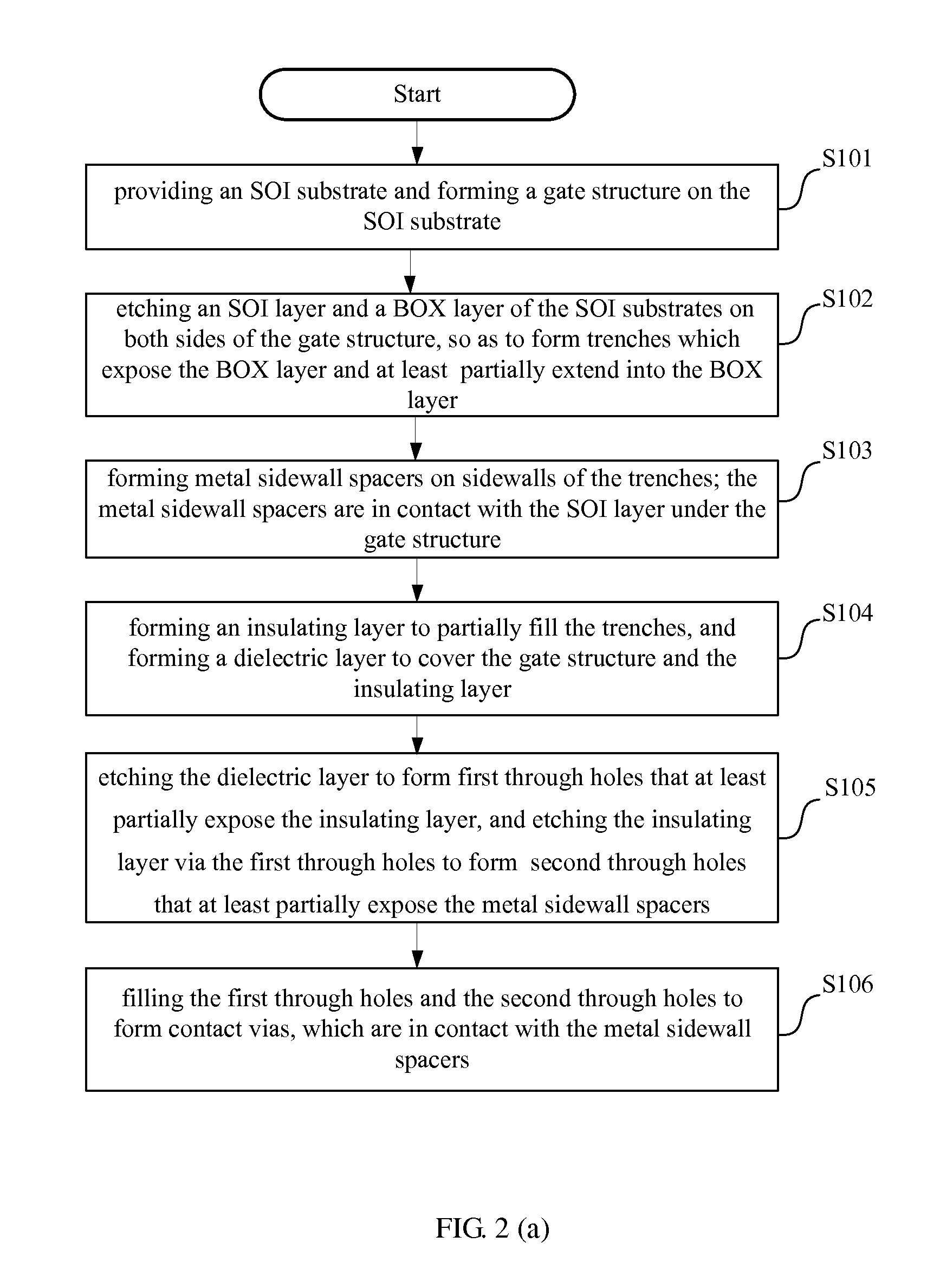

Method for manufacturing a semiconductor structure

ActiveUS8466013B2Reduce contact resistanceReduce capacitanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureSoi substrate

The present invention provides a method for manufacturing a semiconductor structure, which comprises: providing an SOI substrate, and forming a gate structure on the SOI substrate; etching an SOI layer and a BOX layer of the SOI substrates on both sides of the gate structure, so as to form trenches exposing the BOX layer and extending partially into the BOX layer; forming metal sidewall spacers on sidewalls of the trenches, wherein the metal sidewall spacers is in contact with the SOI layer under the gate structure; forming an insulating layer filling partially the trenches, and forming a dielectric layer to cover the gate structure and the insulating layer; etching the dielectric layer to form first contact through holes that expose at least partially the insulating layer, and etching the insulating layer from the first contact through holes to form second contact through holes that expose at least partially the metal sidewall spacer; filling the first contact through holes and the second contact through holes to form contact vias, which are in contact with the metal sidewall spacers. The method provided by the present invention is capable of improving performance of semiconductor devices and alleviating manufacturing difficulty at the mean time.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

Manufacturing method of semiconductor device

PendingCN112563286AGuaranteed electrical performanceAvoid the phenomenon that the size is enlargedSolid-state devicesSemiconductor devicesEtchingDevice material

The invention provides a manufacturing method of a semiconductor device. The manufacturing method comprises the following steps: providing a substrate with a first stacking structure on a surface, forming a plurality of first channel through holes penetrating through the first stacking structure to a substrate, and forming a first filling layer in each first channel through hole; forming a first gate isolation groove penetrating through the first stack structure to the substrate, enabling the first gate isolation groove to be located between the adjacent first channel through holes, and forming a second filling layer in the first gate isolation groove; forming a second stacking structure on the first stacking structure, forming a second channel through hole penetrating through the second stacking structure to the first filling layer, and removing the first filling layer to enable the second channel through hole to be connected with the first channel through hole; and forming a second gate isolation groove penetrating through the second stack structure to the second filling layer, and removing the second filling layer to enable the second gate isolation groove to be connected with the first gate isolation groove. The step-by-step etching of the gate isolation groove can better control an etching key size, and the electrical performance of the device is ensured.

Owner:YANGTZE MEMORY TECH CO LTD

Contact window structure, metal plug and forming method thereof, and semiconductor structure

PendingCN114256136AIncrease contact areaReduce contact resistanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureDielectric layer

The invention discloses a contact window structure, a metal plug and a forming method thereof, the forming method of the contact window structure and a semiconductor structure, an annular gasket is formed on the surface of a target layer, and the middle of the annular gasket is provided with a central through hole exposing part of the surface of the target layer; forming a dielectric layer covering the substrate, the target layer and the annular gasket; etching the dielectric layer, and forming an etching hole communicated with the central through hole in the dielectric layer; and the annular gasket is removed along the etching hole and the central through hole, so that the size of the central through hole is enlarged, and the etching hole and the central through hole with the enlarged size form a contact window structure. Through the formed annular gasket, when the contact window structure is formed and the annular gasket is removed, the size of the central through hole can be increased, so that the size of the bottom of the contact window structure can be increased, and when a metal plug is formed in the contact window structure, the contact area between the bottom of the metal plug and a target layer is increased; and the contact resistance between the two is reduced.

Owner:CHANGXIN MEMORY TECH INC

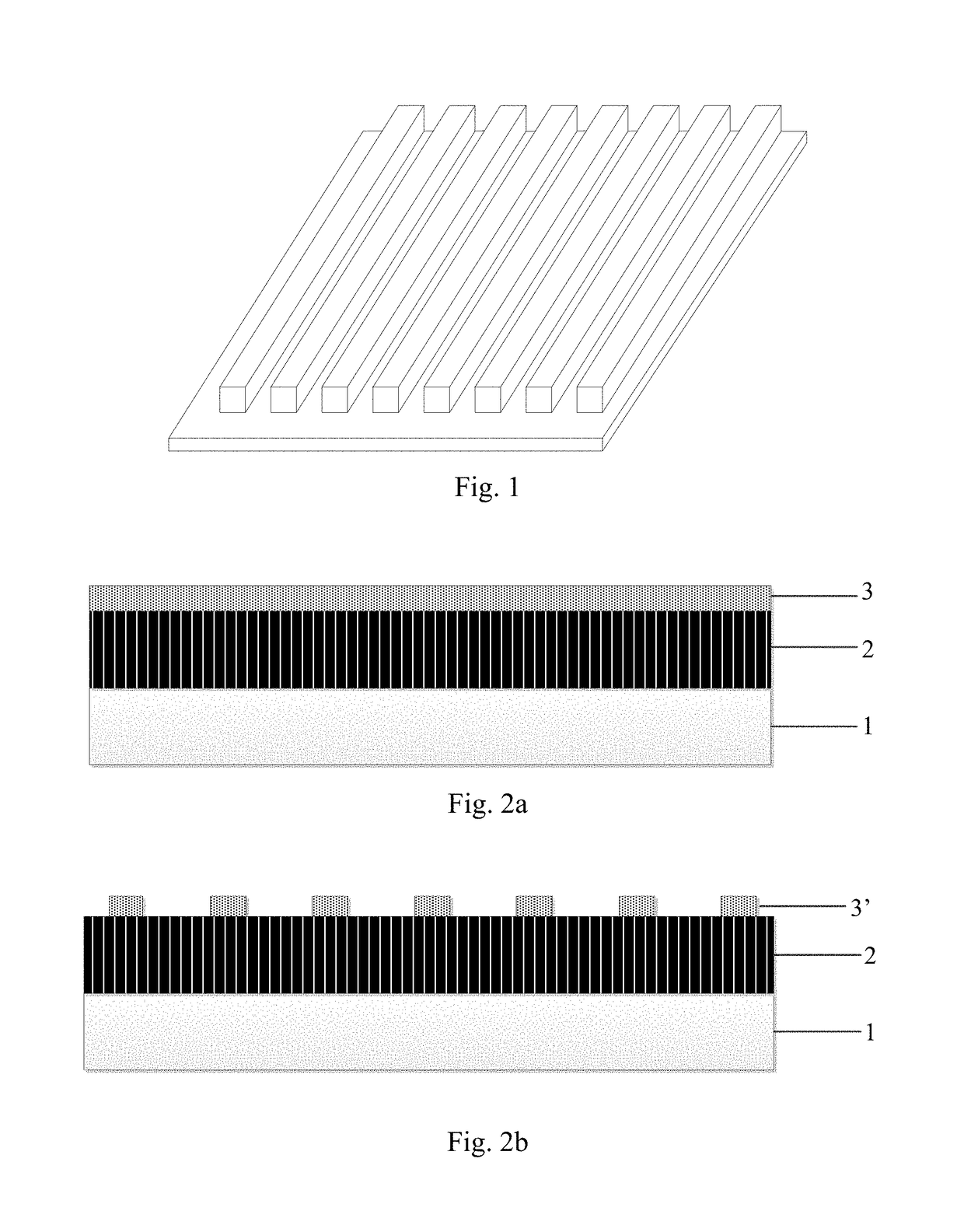

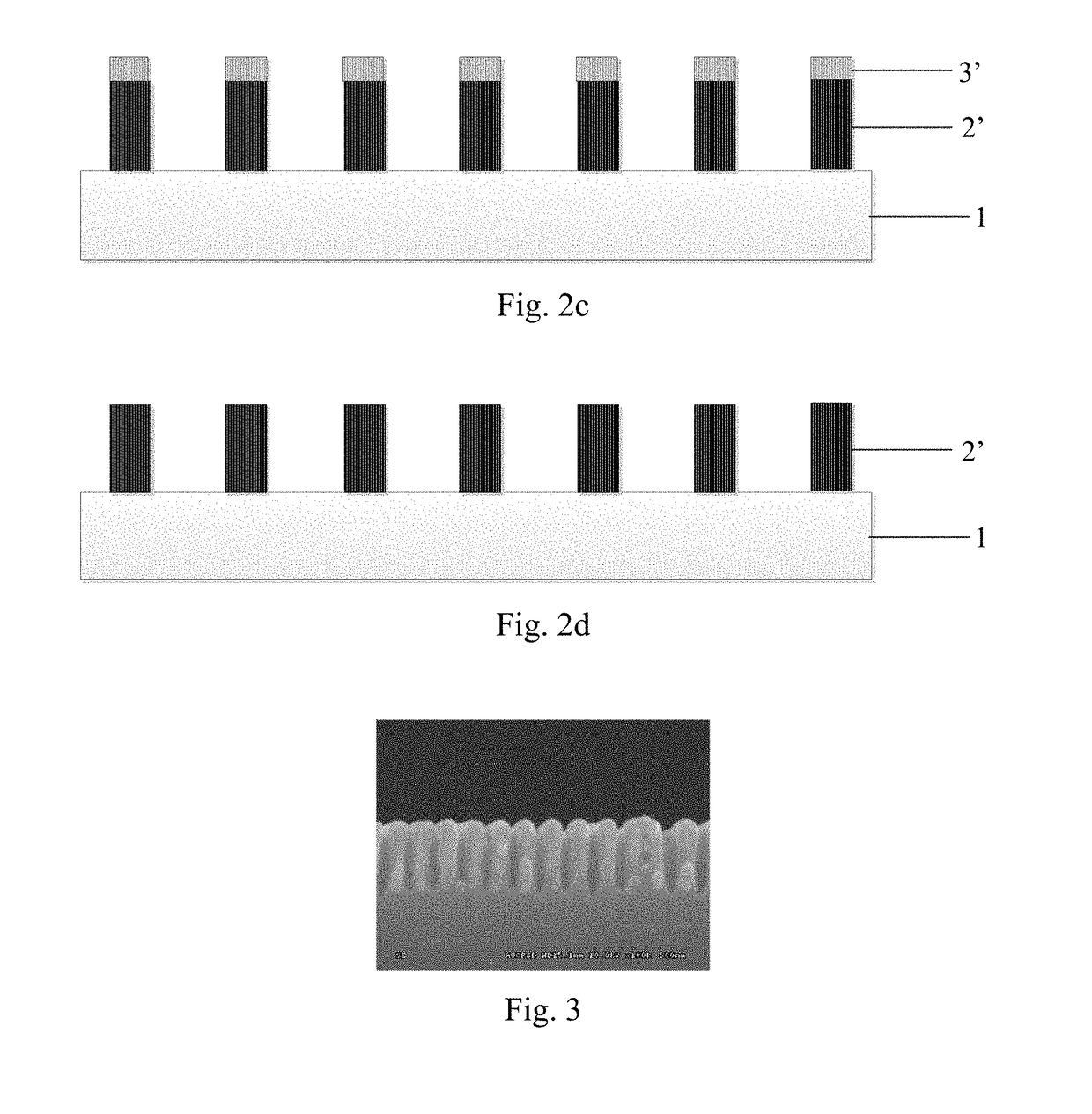

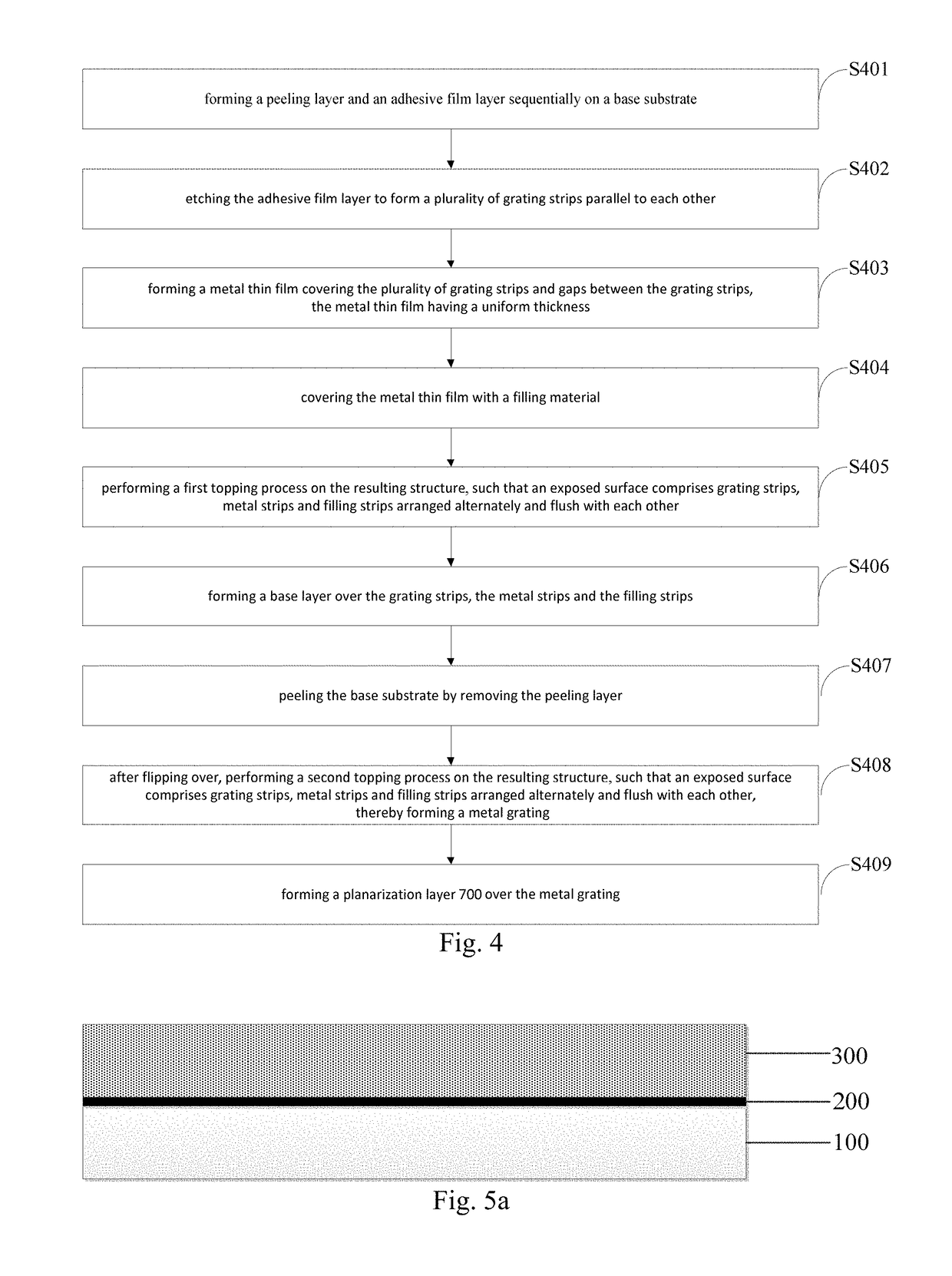

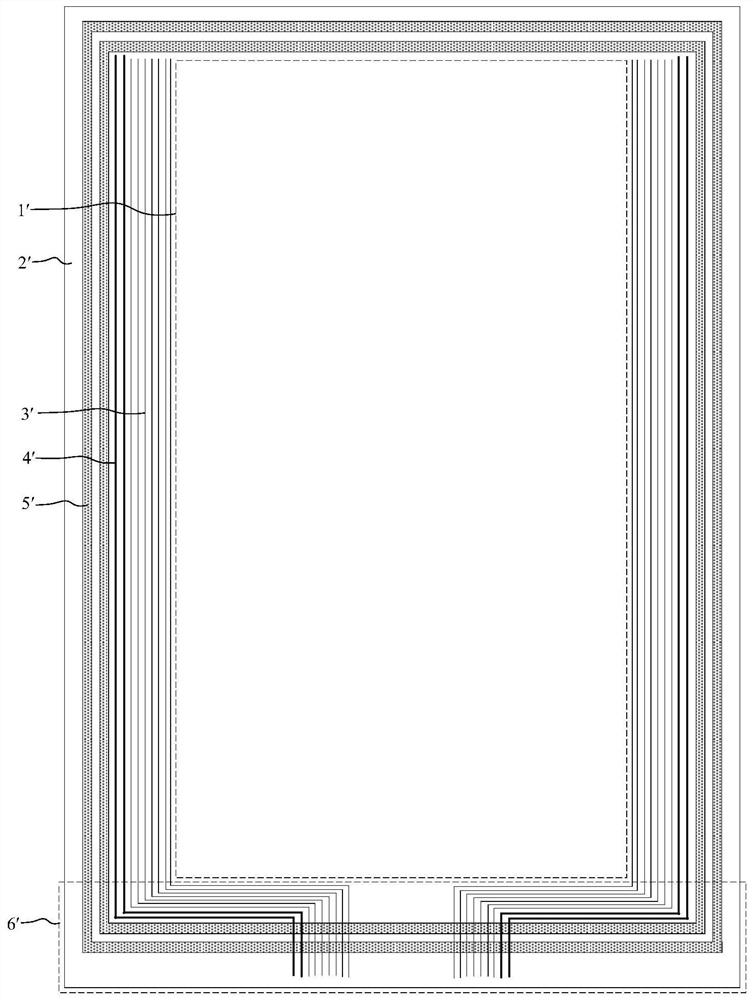

Manufacturing method for metal grating, metal grating and display device

ActiveUS20190041563A1Small thicknessReduce the difficulty of etchingSolid-state devicesPolarising elementsDisplay deviceMetal grating

The present disclosure relates to a manufacturing method for a metal grating, a metal grating, and a display device. In this manufacturing method, after forming a plurality of parallel grating strips by means of an adhesive film layer, a metal thin film with a uniform thickness is formed over the plurality of grating strips and gaps between the grating strips. Furthermore, a metal grating is formed by performing topping treatments on both of an upper surface and a lower surface of the resulting structure.

Owner:BOE TECH GRP CO LTD +1

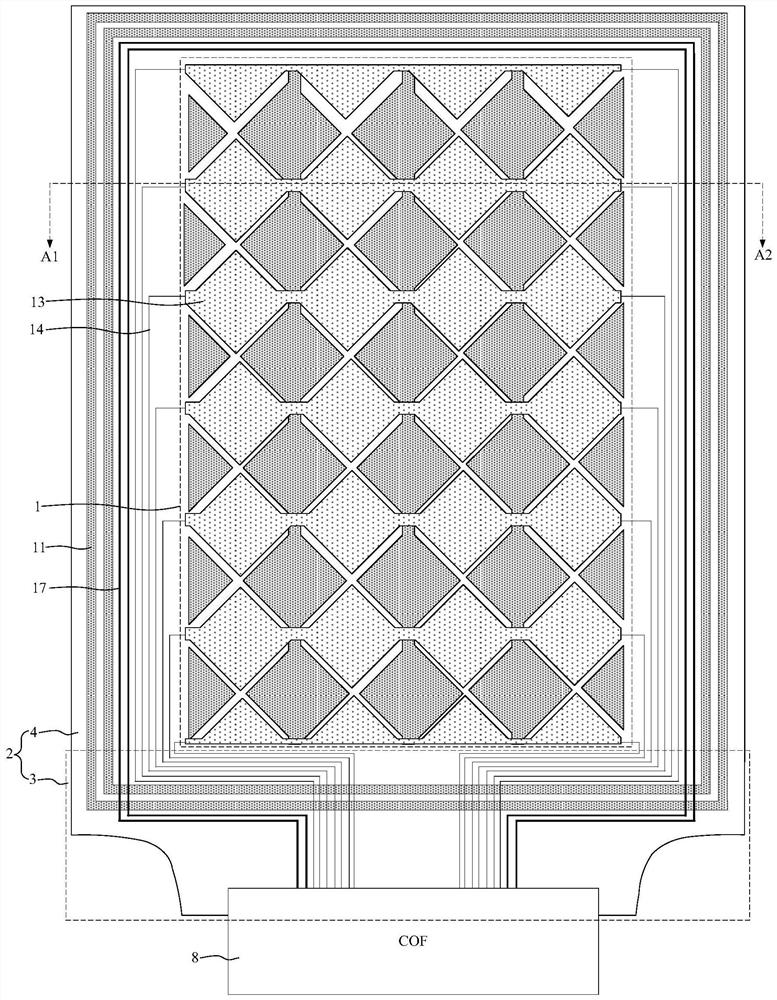

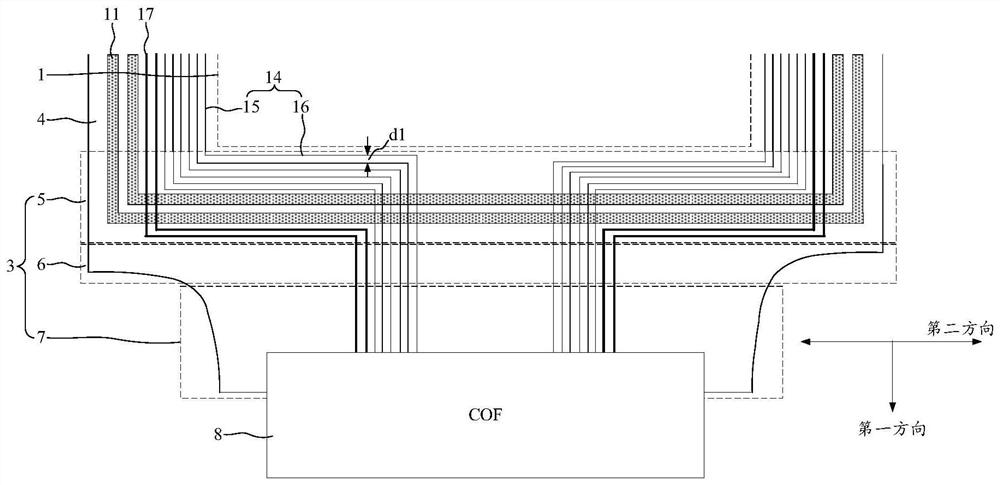

Touch display panel and touch display device

PendingCN112612371AAvoid getting leads too close togetherReduce the difficulty of etchingInput/output processes for data processingElectrostatic chargesEngineeringDisplay device

The embodiment of the invention provides a touch display panel and a touch display device, relates to the technical field of display, and increases the distance between touch signal lines in a step area. The panel comprises a display area and a non-display area. The non-display area comprises a step area and a non-step area, and the step area comprises a wiring area, a bending area and a functional area; The panel also comprises a retaining wall which is arranged around the display area in the non-display area; touch electrodes and touch signal lines, wherein the touch signal lines extend to the functional area from the non-step area, the routing area and the bending area, the parts, located in the non-step area, of the touch signal lines are touch routing lines, the touch routing lines are located on the sides, close to the display area, of the retaining walls, and the parts, located in the step area, of the touch signal lines are touch leads; an electrostatic shielding signal line which is located in the non-display area, wherein the part, extending in the second direction in the step area, of the electrostatic shielding signal line is located on the side, away from the display area, of the retaining wall, and the second direction is the extending direction of the retaining wall in the step area.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

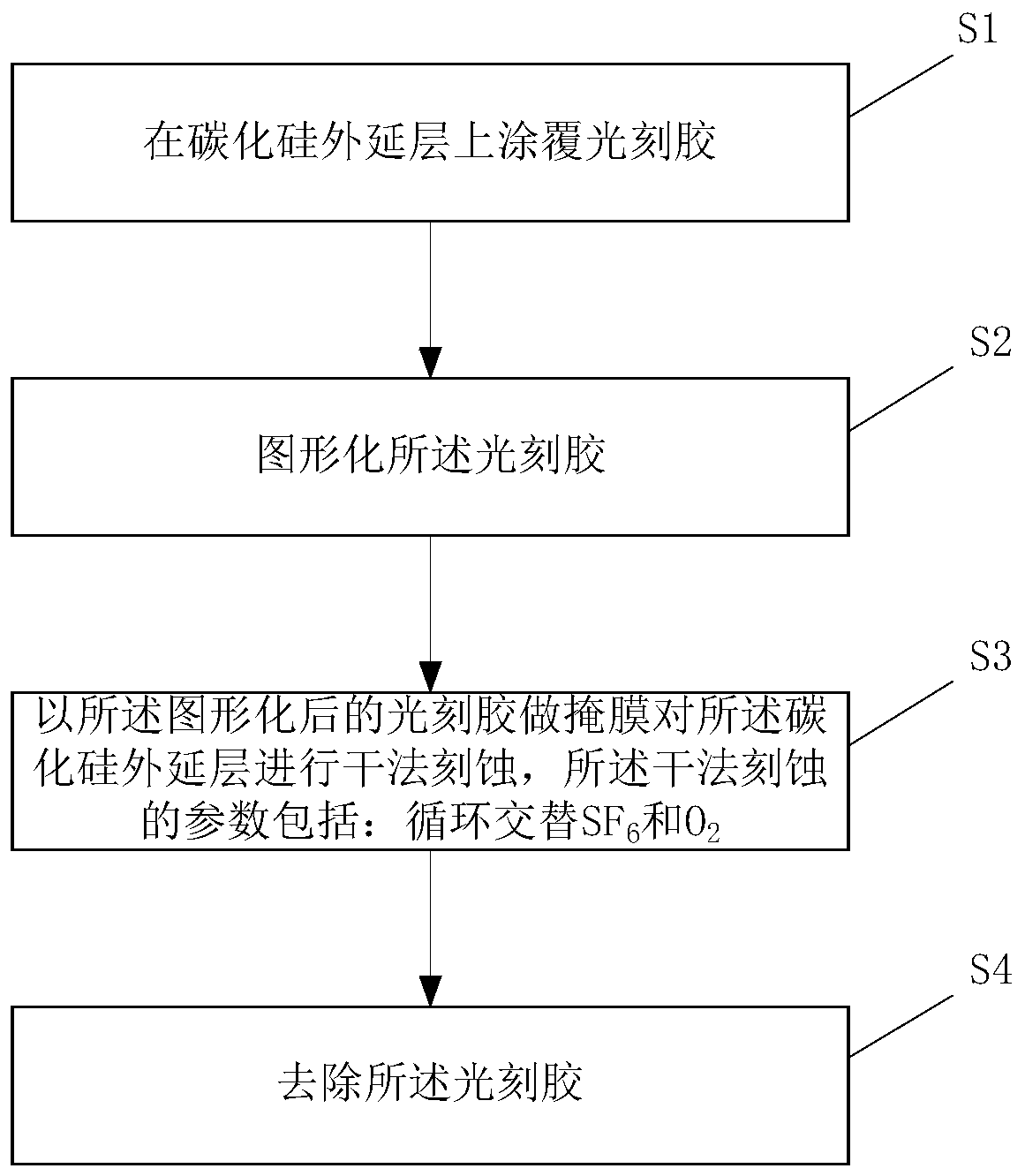

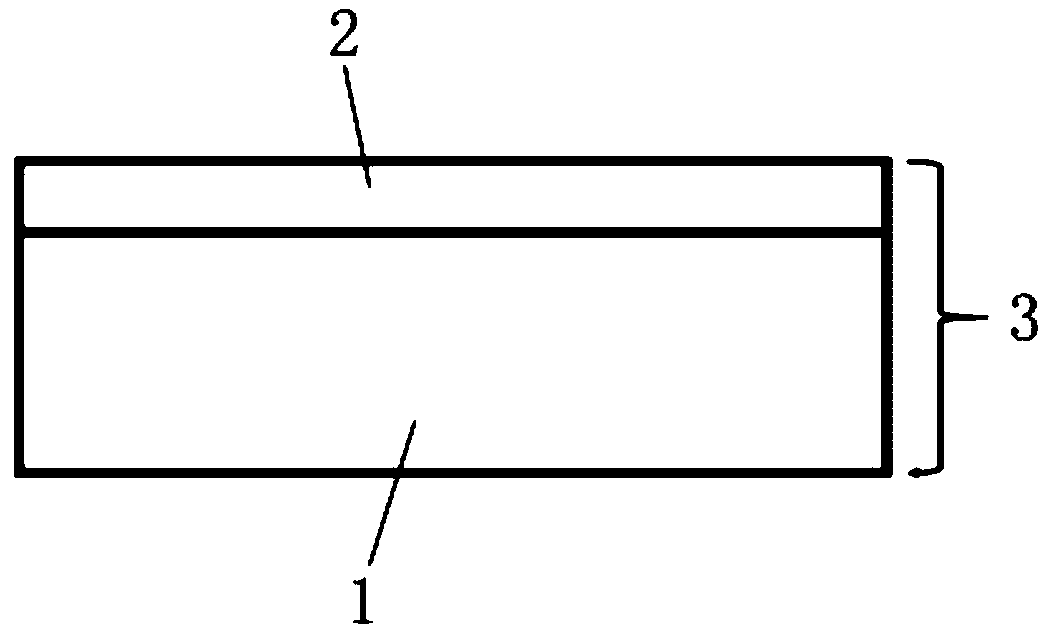

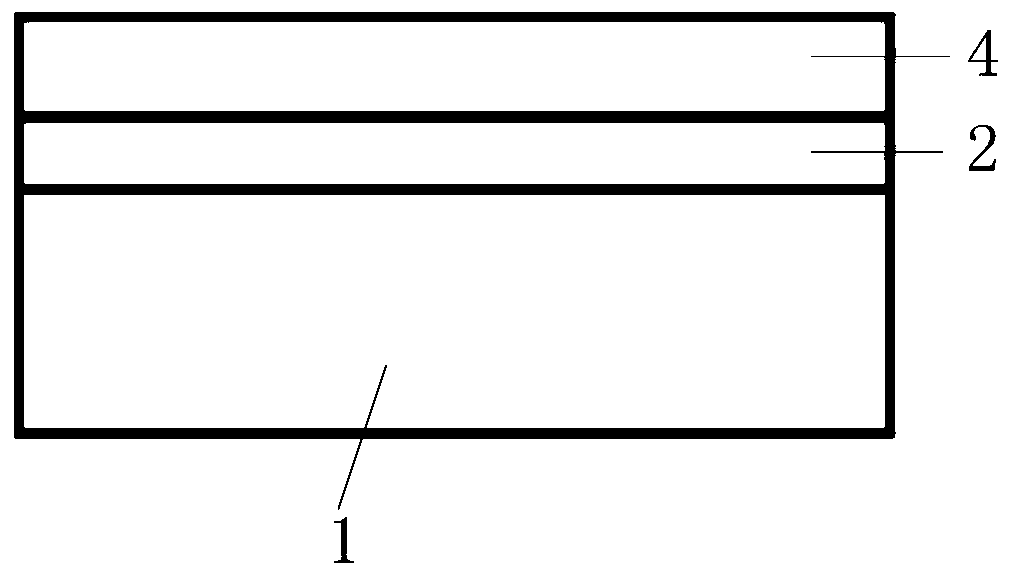

Method for etching silicon carbide shallow trench

InactiveCN110277315ALow mass production costReduce the number of masksSemiconductor/solid-state device manufacturingPhotoresistDry etching

The invention discloses a method for etching a silicon carbide shallow trench, which comprises the steps of coating a silicon carbide epitaxial layer with a photoresist; patterning the photoresist; performing dry etching on the silicon carbide epitaxial layer by taking the patterned photoresist as a mask, wherein the parameters of the dry etching include SF6 and O2 which are cyclically and alternately introduced; and removing the photoresist. According to the method provided by the embodiment of the invention for etching the silicon carbide shallow trench, the silicon carbide epitaxial layer is coated with the photoresist, and the etching is performed by directly taking the photoresist as a mask, so that the number of masks is reduced, the etching efficiency is improved, the etching difficulty is reduced, and the batch production cost of silicon carbide devices is effectively reduced. The gases SF6 and O2 are cyclically and alternately act on the material, so that the etching rate of the photoresist can be reduced on one hand, and the side wall angle of the silicon carbide trench is facilitated to be improved on the other hand.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +1

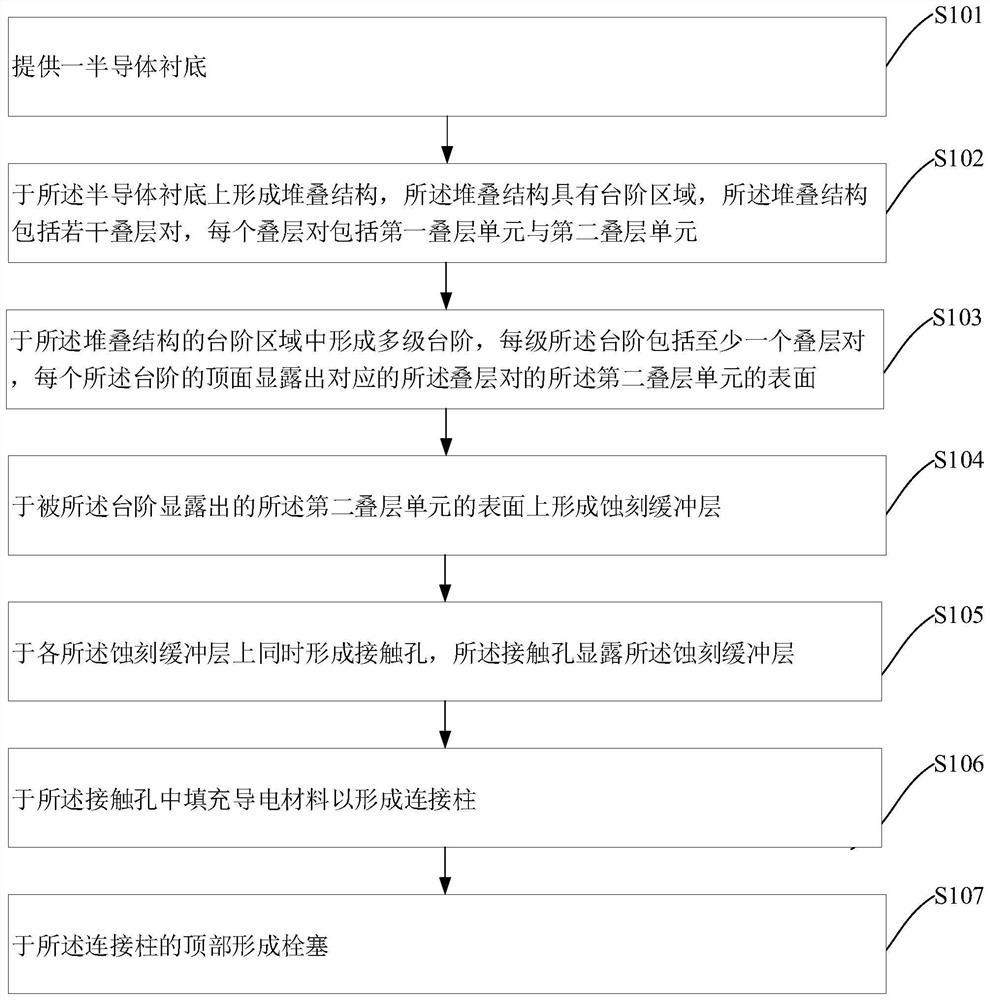

Semiconductor structure and preparation method thereof

ActiveCN111769120AReduce the difficulty of etchingThe process steps are simpleSolid-state devicesSemiconductor devicesSemiconductor structureEngineering

The invention provides a semiconductor structure and a preparation method thereof. The preparation method comprises the following steps: providing a semiconductor substrate; forming a stack structureon the semiconductor substrate, the stack structure comprising a plurality of stack pairs, each stack pair comprising a first stack unit and a second stack unit; forming a step structure in the stacked structure, the step structure comprising multiple steps, each step comprising at least one stacked layer pair, and the top surface of each step exposing the surface of the second stacked layer unitof the corresponding stacked layer pair; forming an etching buffer layer on the surface of the second lamination unit exposed by the step; and forming contact holes in the etching buffer layers at thesame time, wherein the contact holes expose the etching buffer layers. According to the invention, by arranging the etching buffer layer on the surface of the step, etching of all the contact holes can be completed simultaneously in one etching process, so that the process steps are simplified, the etching difficulty of the contact holes is reduced, and the cost is saved.

Owner:YANGTZE MEMORY TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com