Patents

Literature

117results about How to "Reduce the number of masks" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Phase change memory devices with reduced programming current

ActiveUS20070075347A1High resistivityReduce programming currentTransistorSolid-state devicesPhase-change memoryEngineering

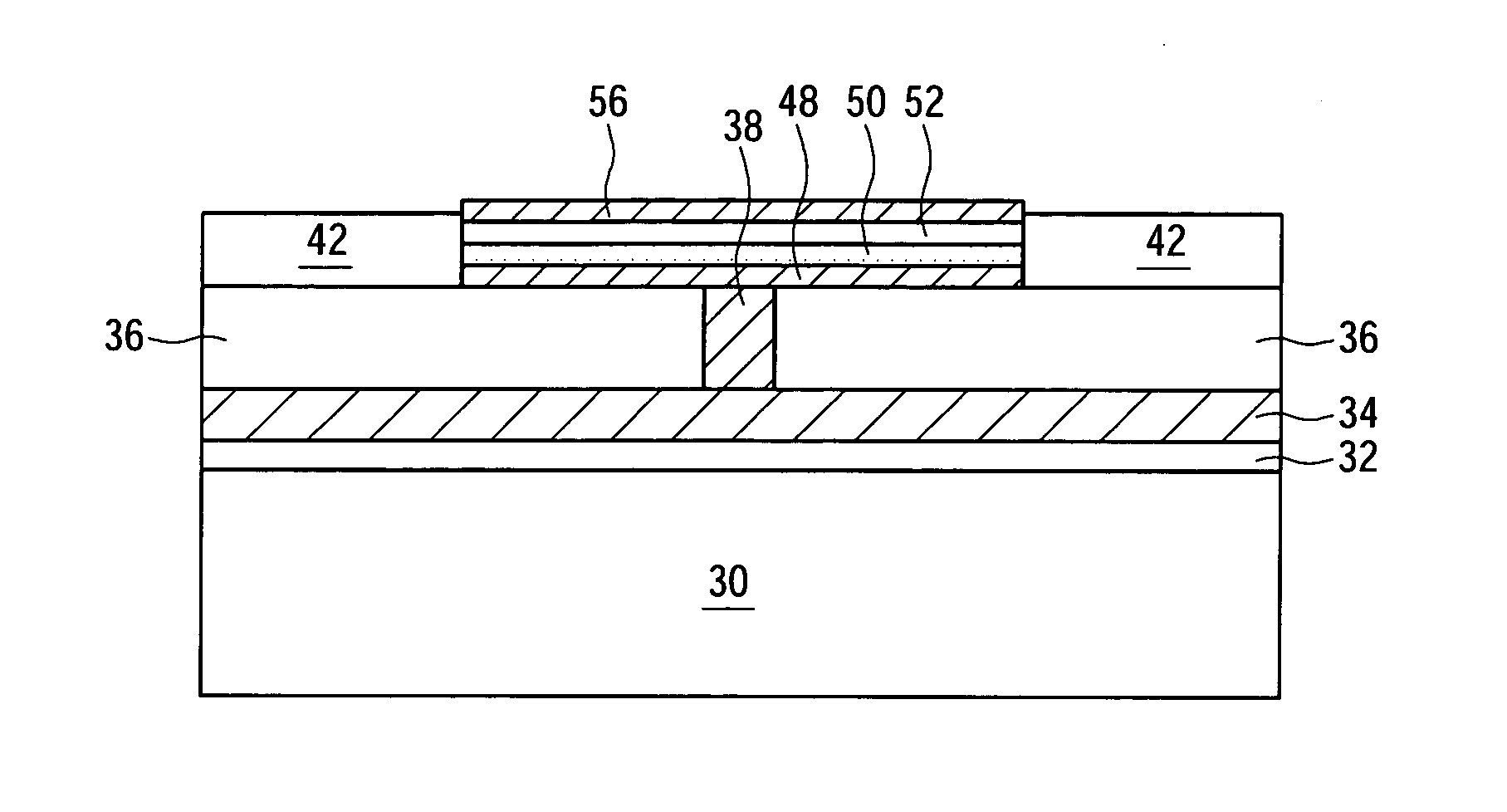

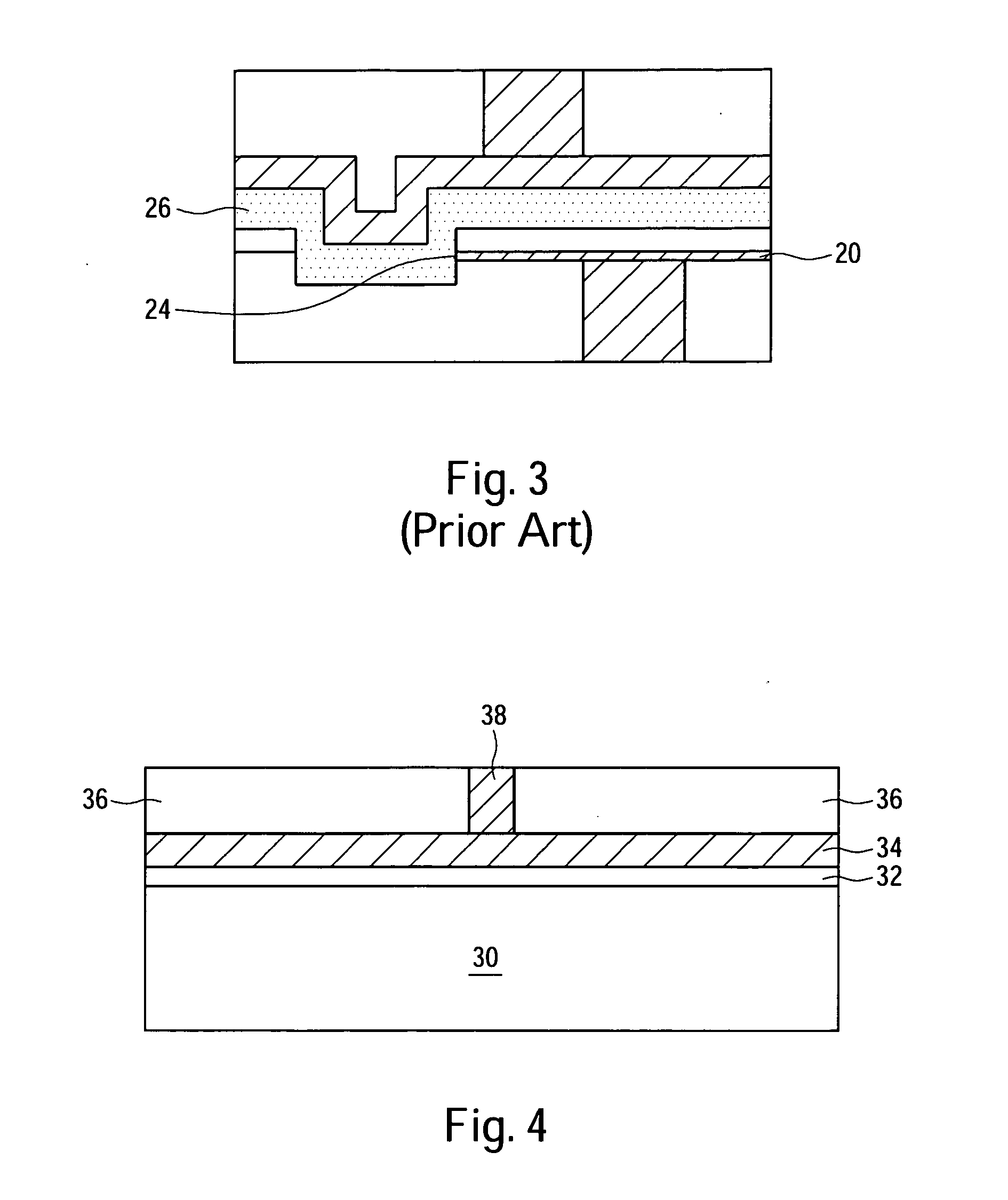

A phase change memory device and a method of forming the same are provided. The phase change memory device includes a conducting electrode in a dielectric layer, a bottom electrode over the conducting electrode, a phase change layer over the bottom electrode, and a top electrode over the phase change layer. The phase change memory device may further include a heat sink layer between the phase change layer and the top electrode. The resistivities of the bottom electrode and the top electrode are preferably greater than the resistivity of the phase change material in the crystalline state.

Owner:TAIWAN SEMICON MFG CO LTD +1

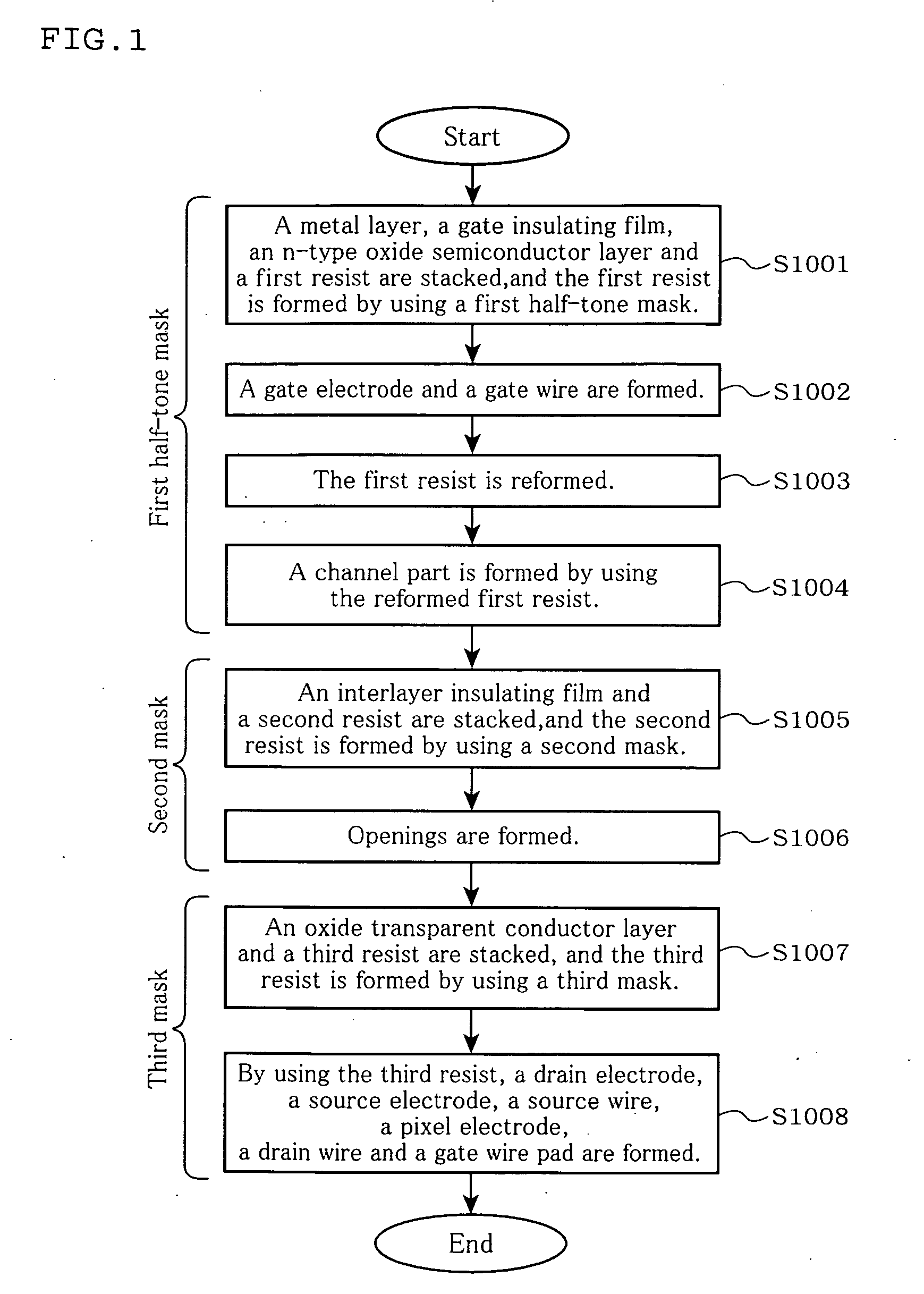

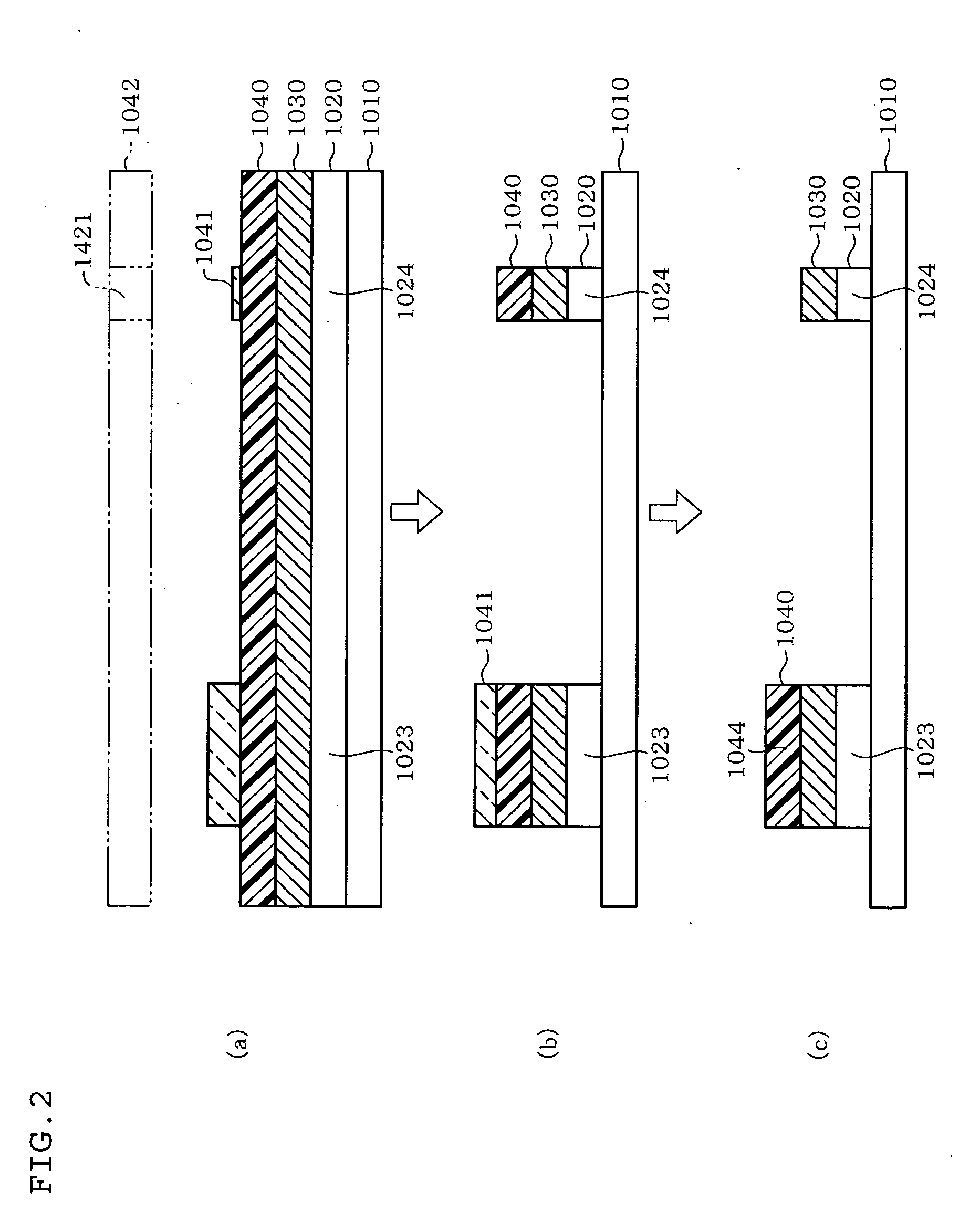

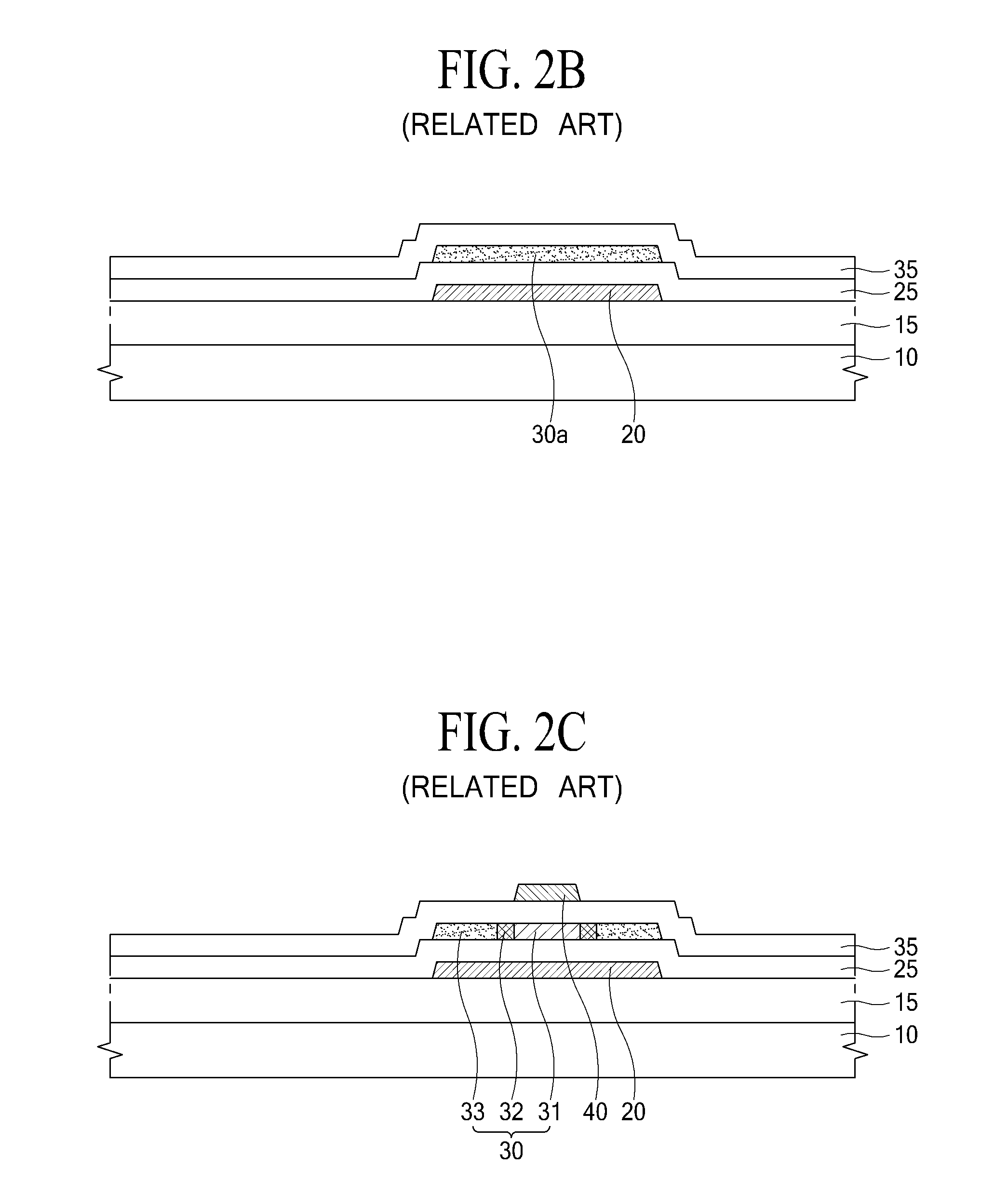

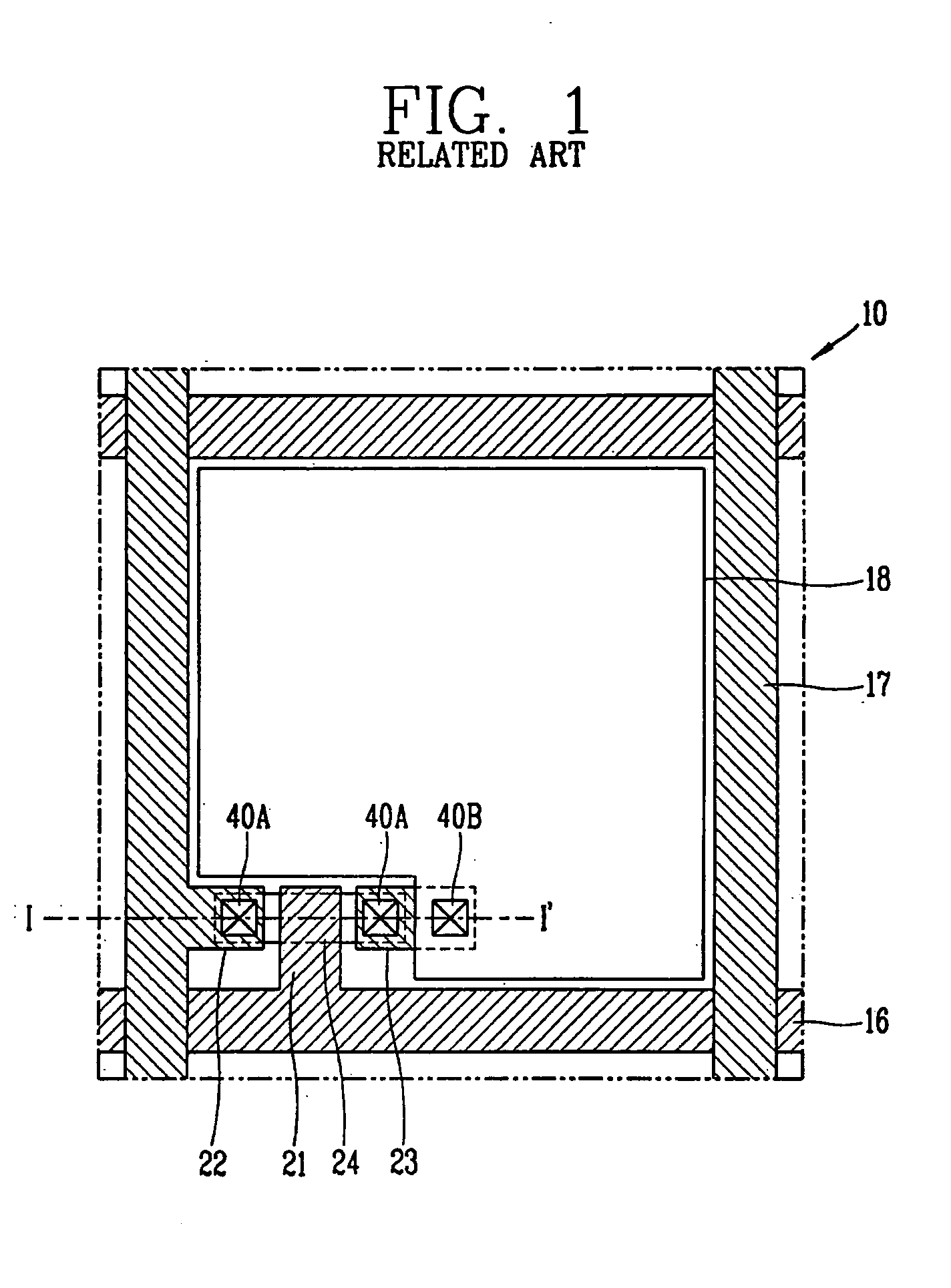

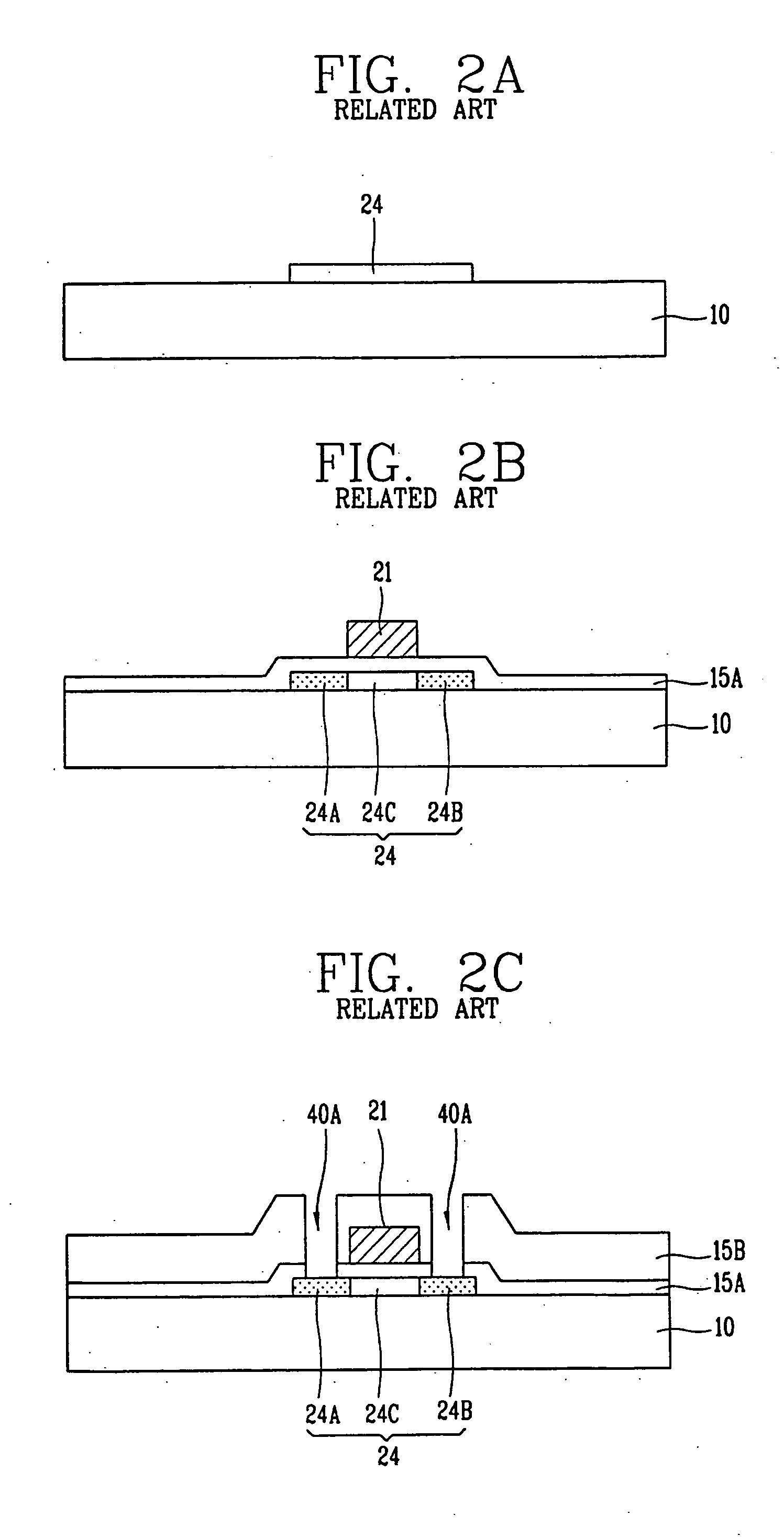

Tft Substrate, Reflective Tft Substrate and Method for Manufacturing These Substrates

InactiveUS20090001374A1Reduce production stepsReduce the number of masksTransistorSolid-state devicesManufacturing cost reductionElectrical conductor

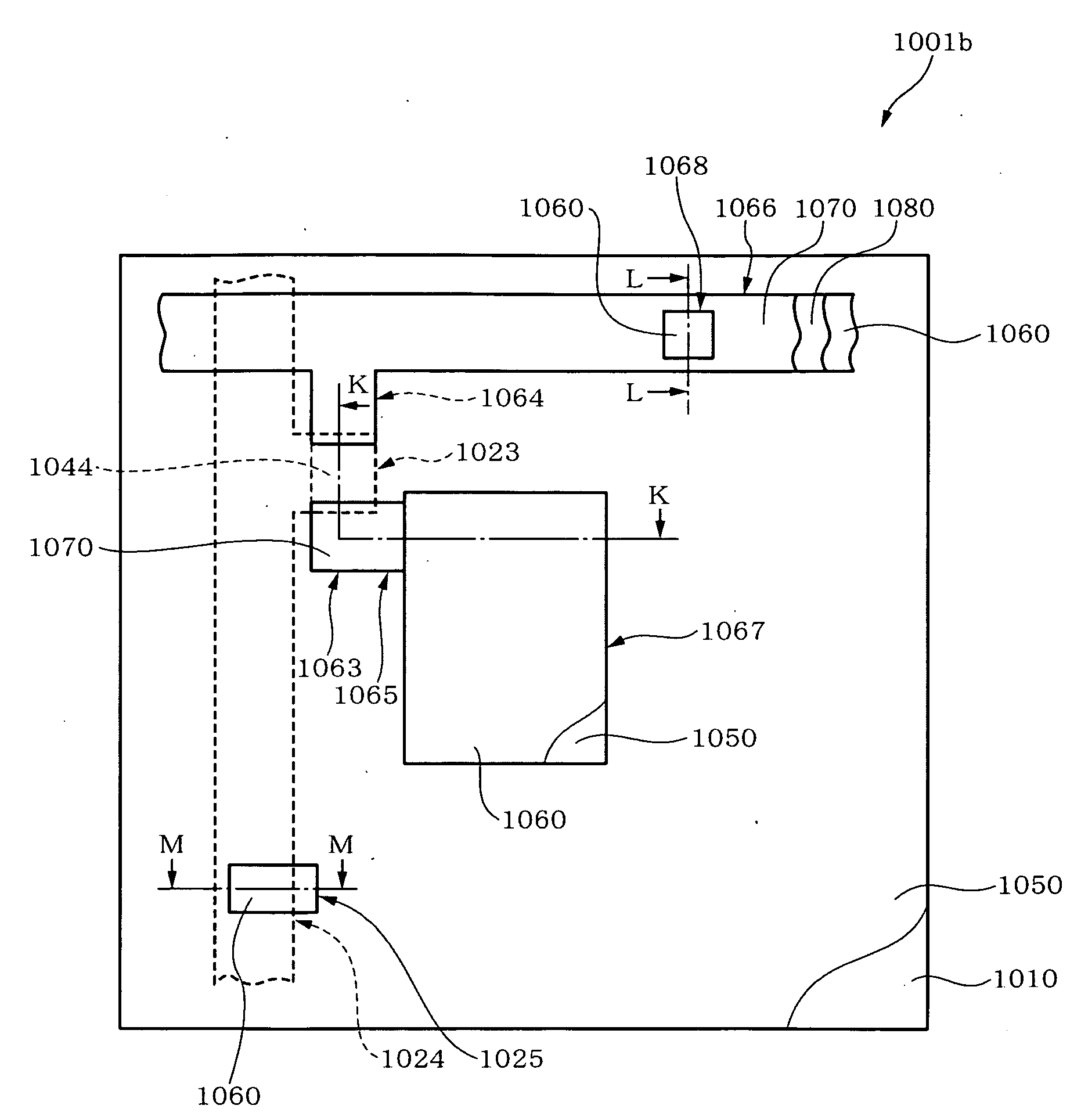

An object of the invention is to propose a TFT substrate and a reflective TFT substrate which can be operated stably for a prolonged period of time, can be prevented from being suffering from crosstalk, and is capable of significantly reducing manufacturing cost by decreasing the number of production steps, as well as to propose the method for producing these substrates.A TFT substrate 1001 comprises: a glass substrate 1010; a gate electrode 1023 and a gate wire 1024 insulated by having their top surfaces covered with a gate insulating film 1030 and by having their side surfaces covered with an interlayer insulating film 1050; an n-type oxide semiconductor layer 1040 formed on the gate insulating film 1030 above the gate electrode 1023; an oxide transparent conductor layer 1060 formed on the n-type oxide semiconductor layer 1040 with a channel part 1044 interposed therebetween; and a channel guard 1500 for protecting the channel part 1044.

Owner:IDEMITSU KOSAN CO LTD

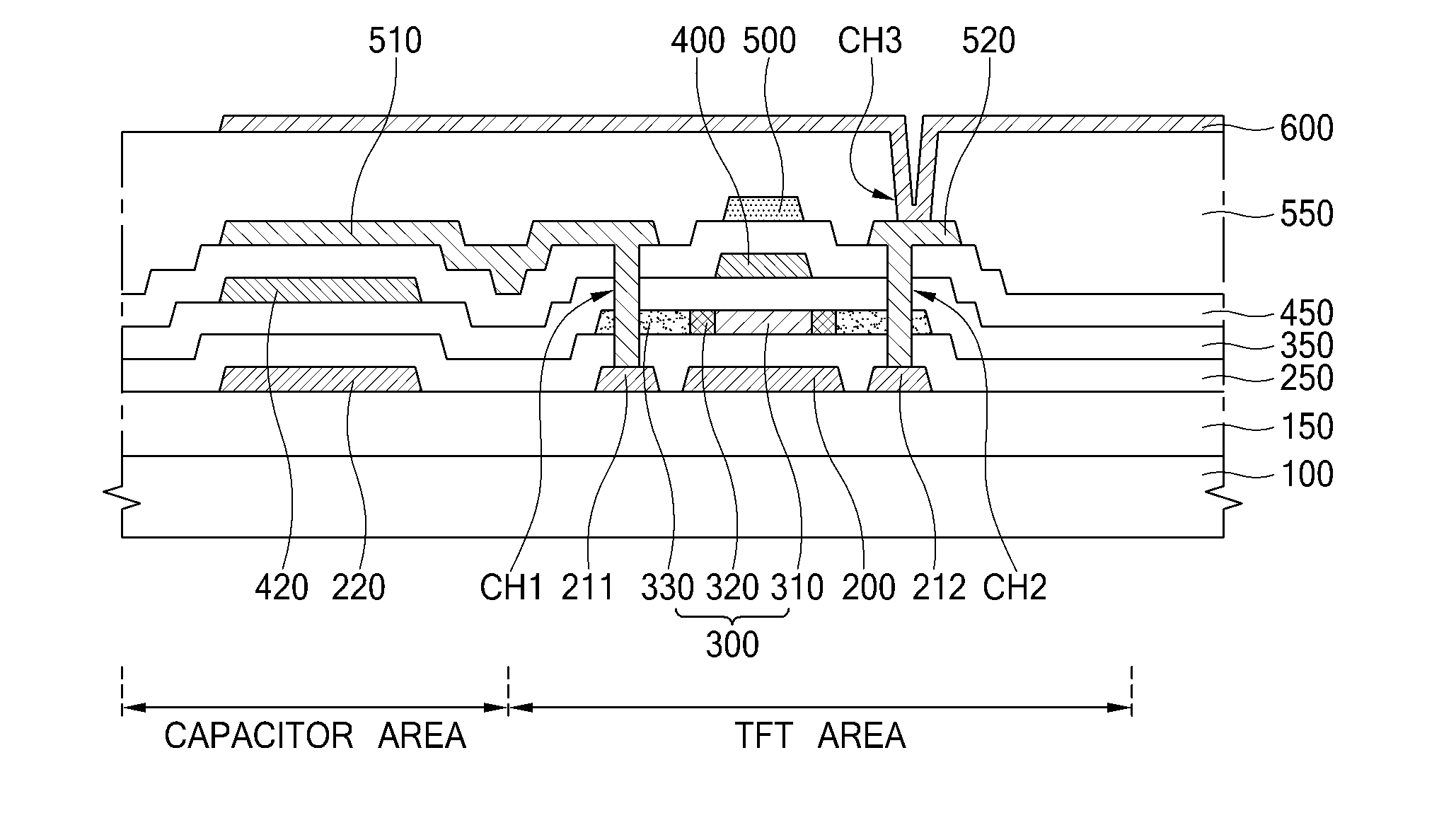

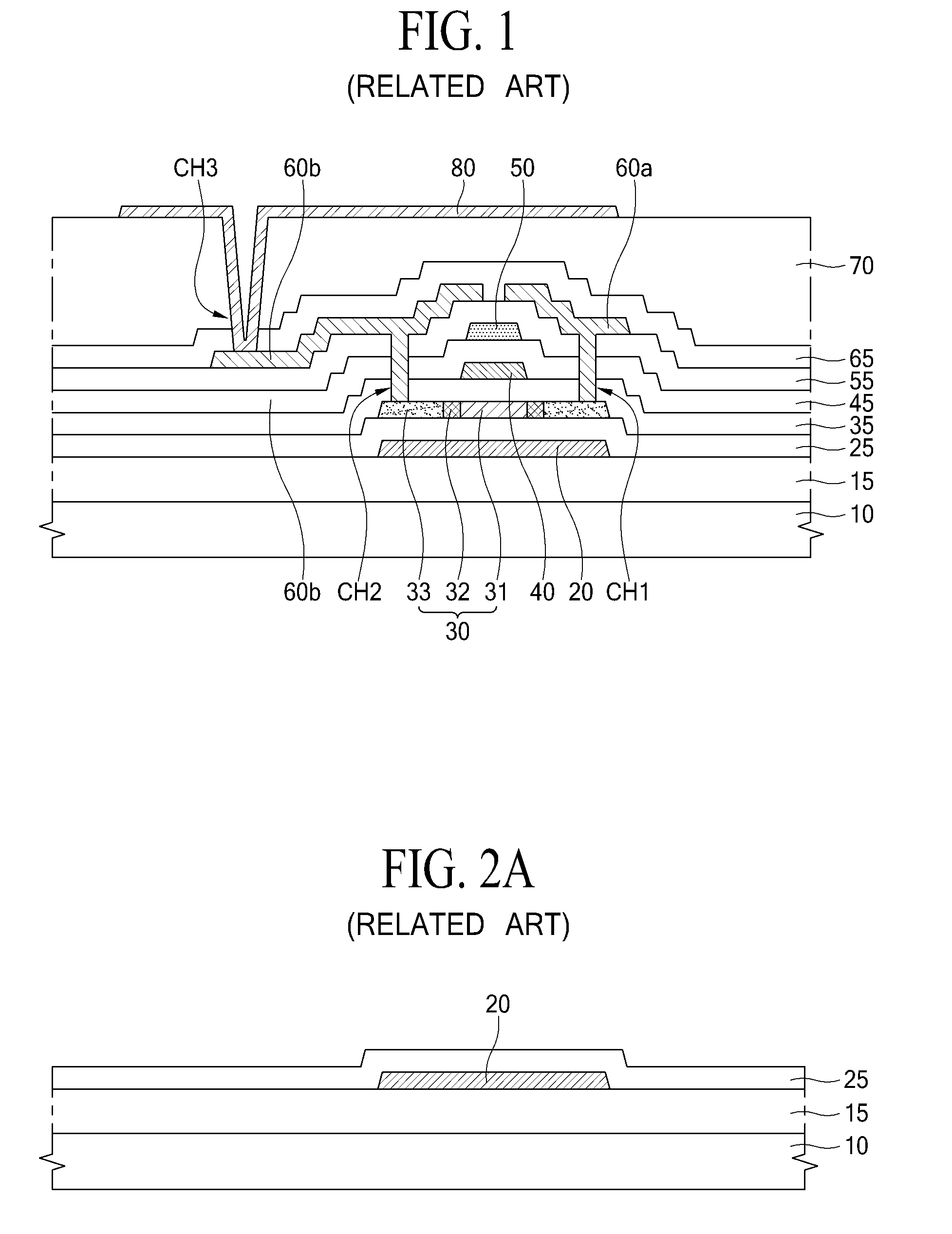

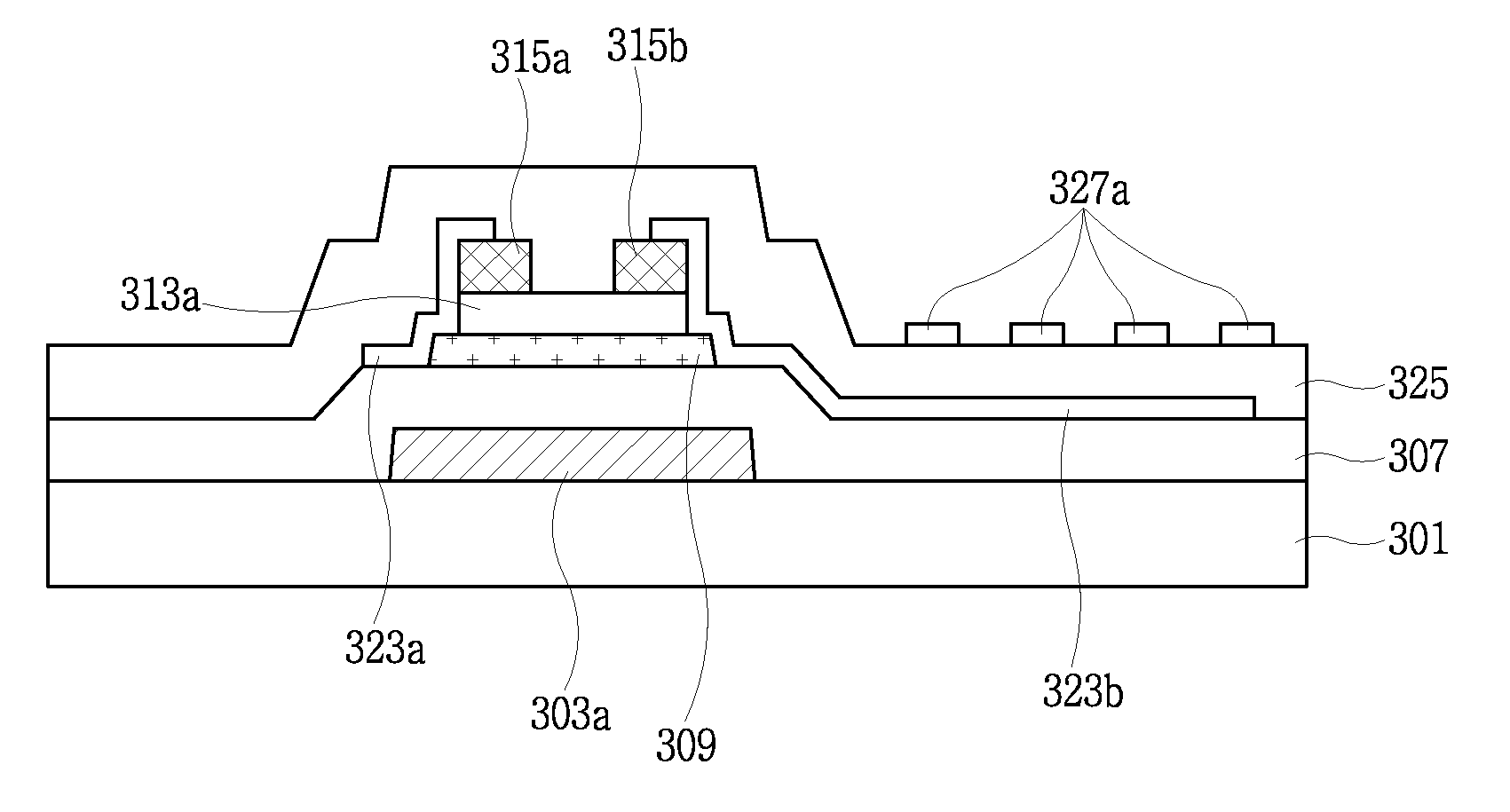

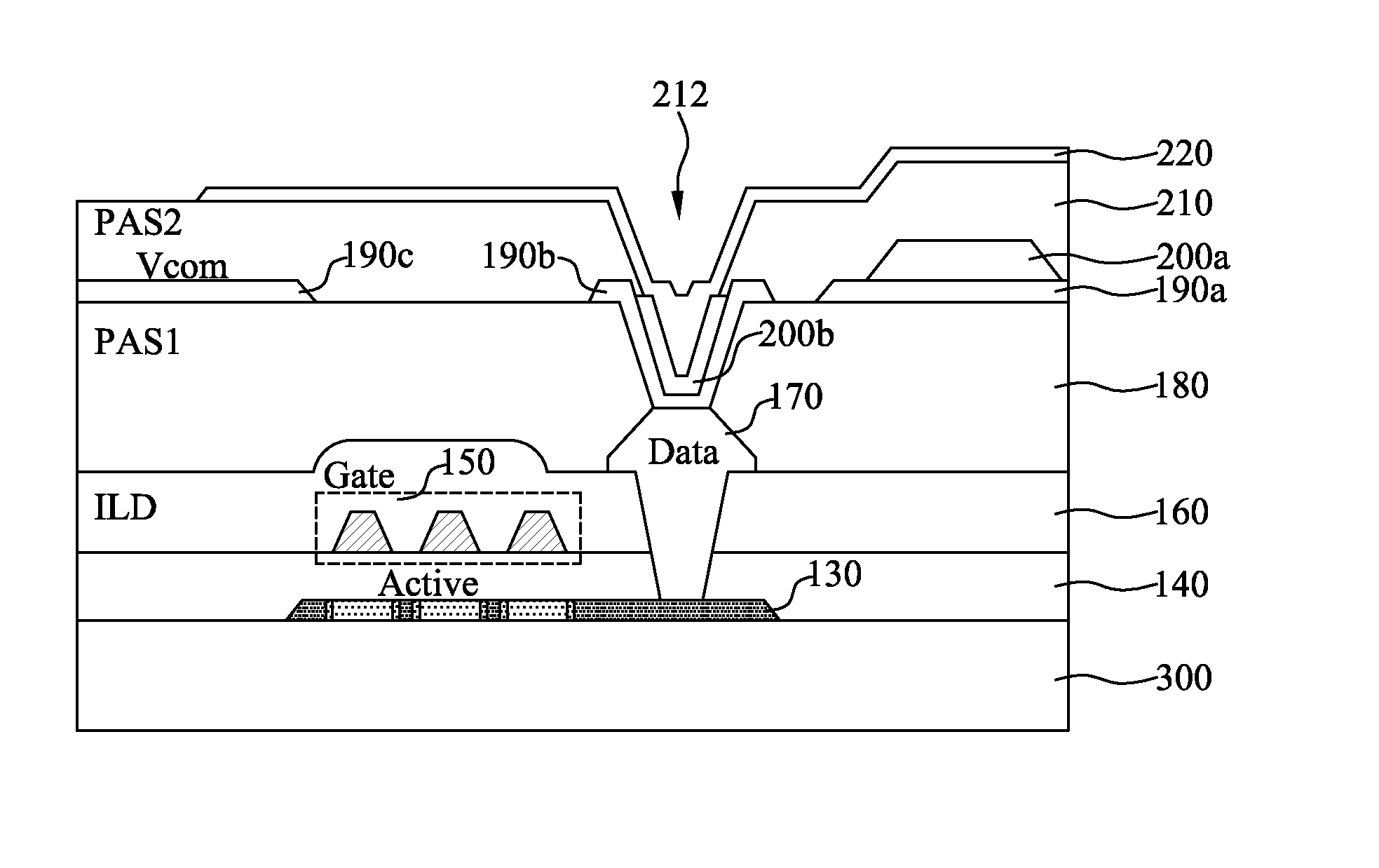

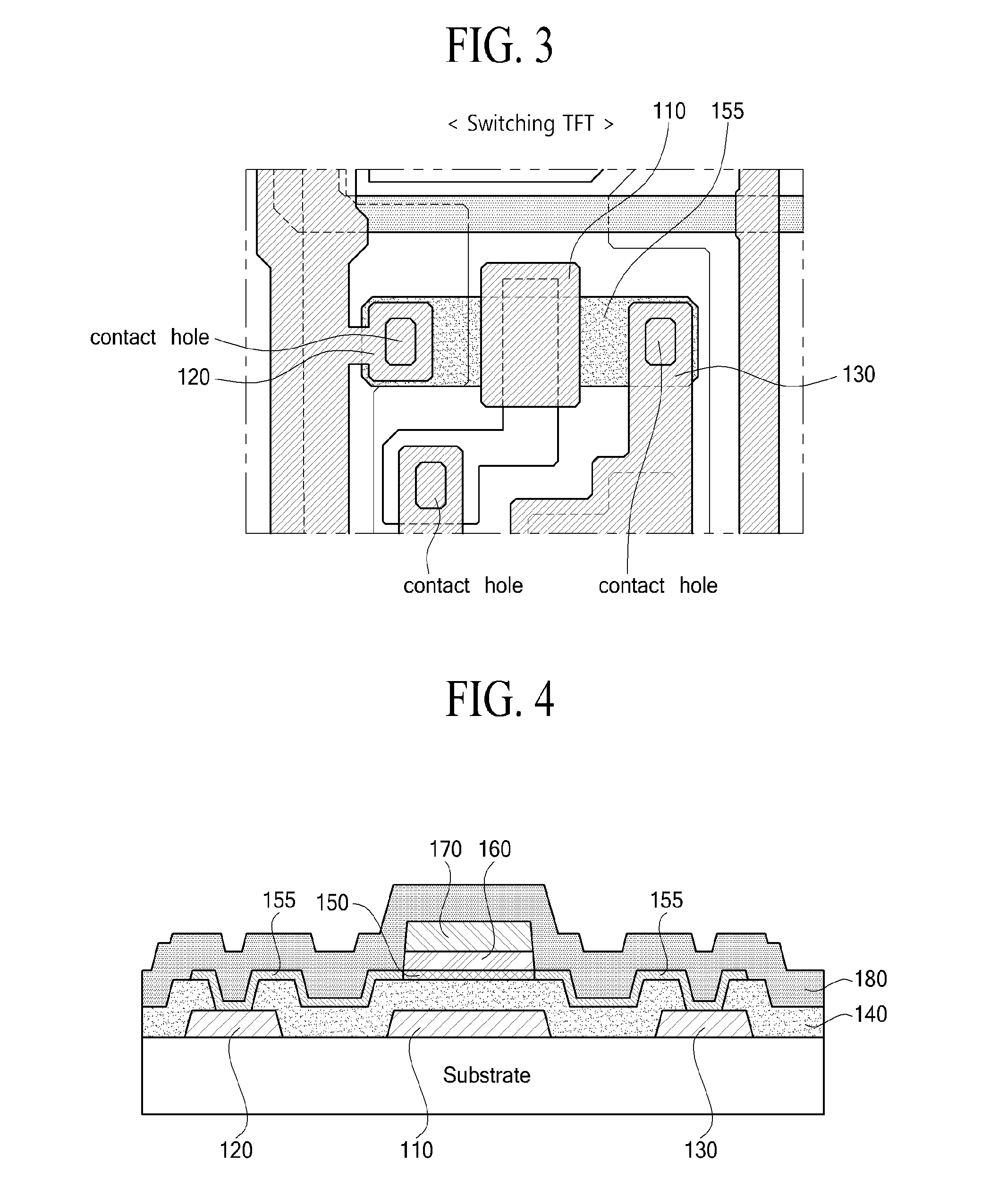

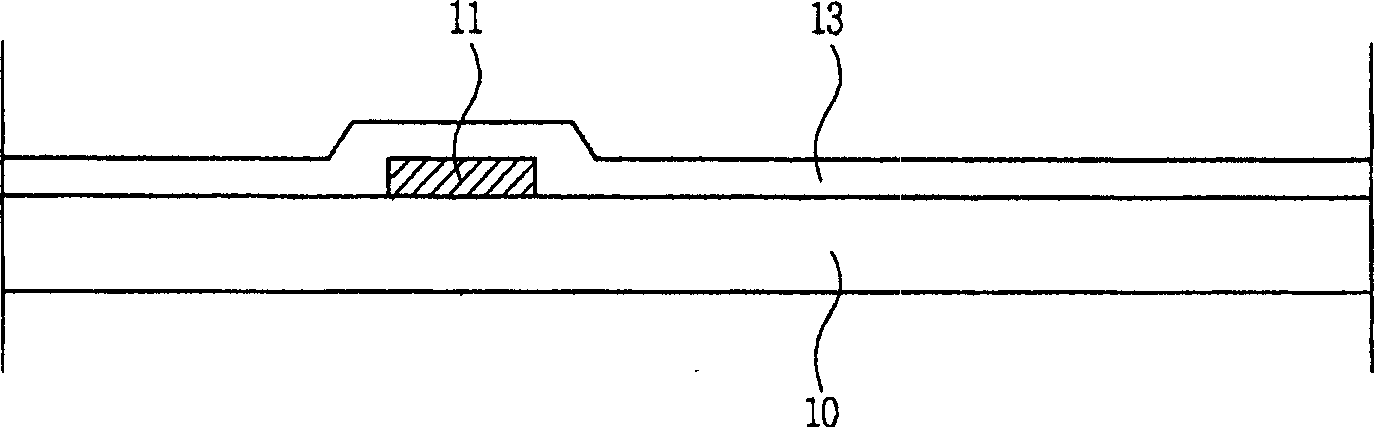

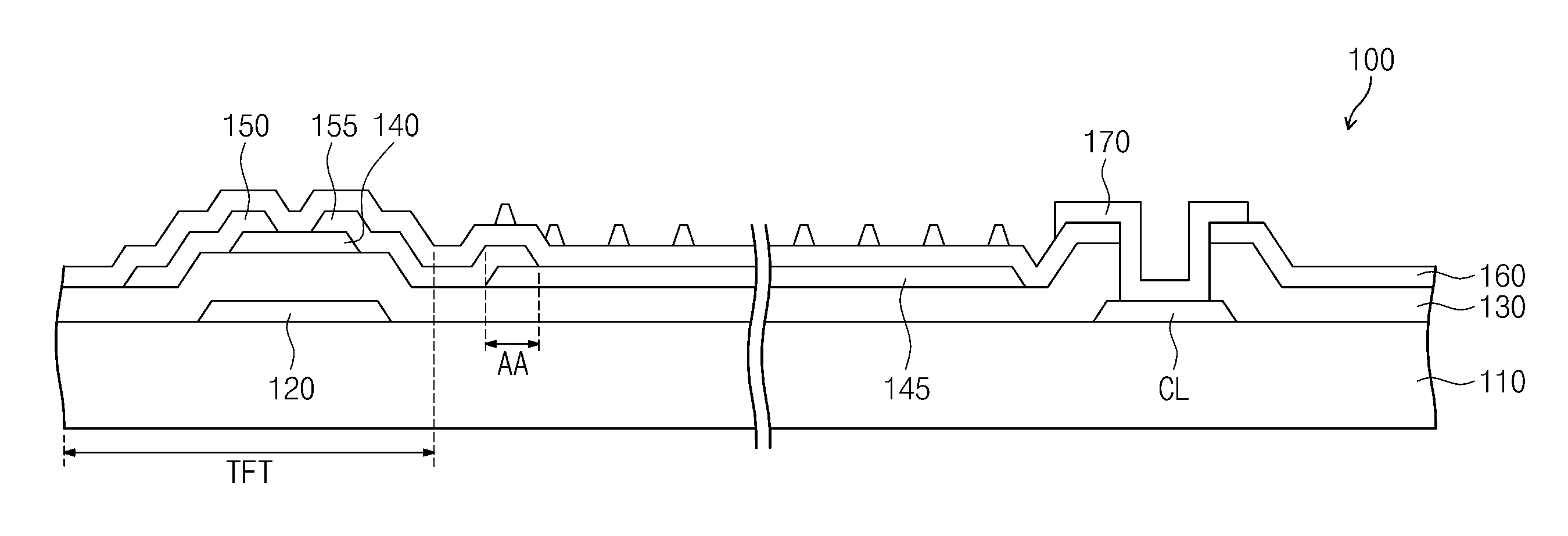

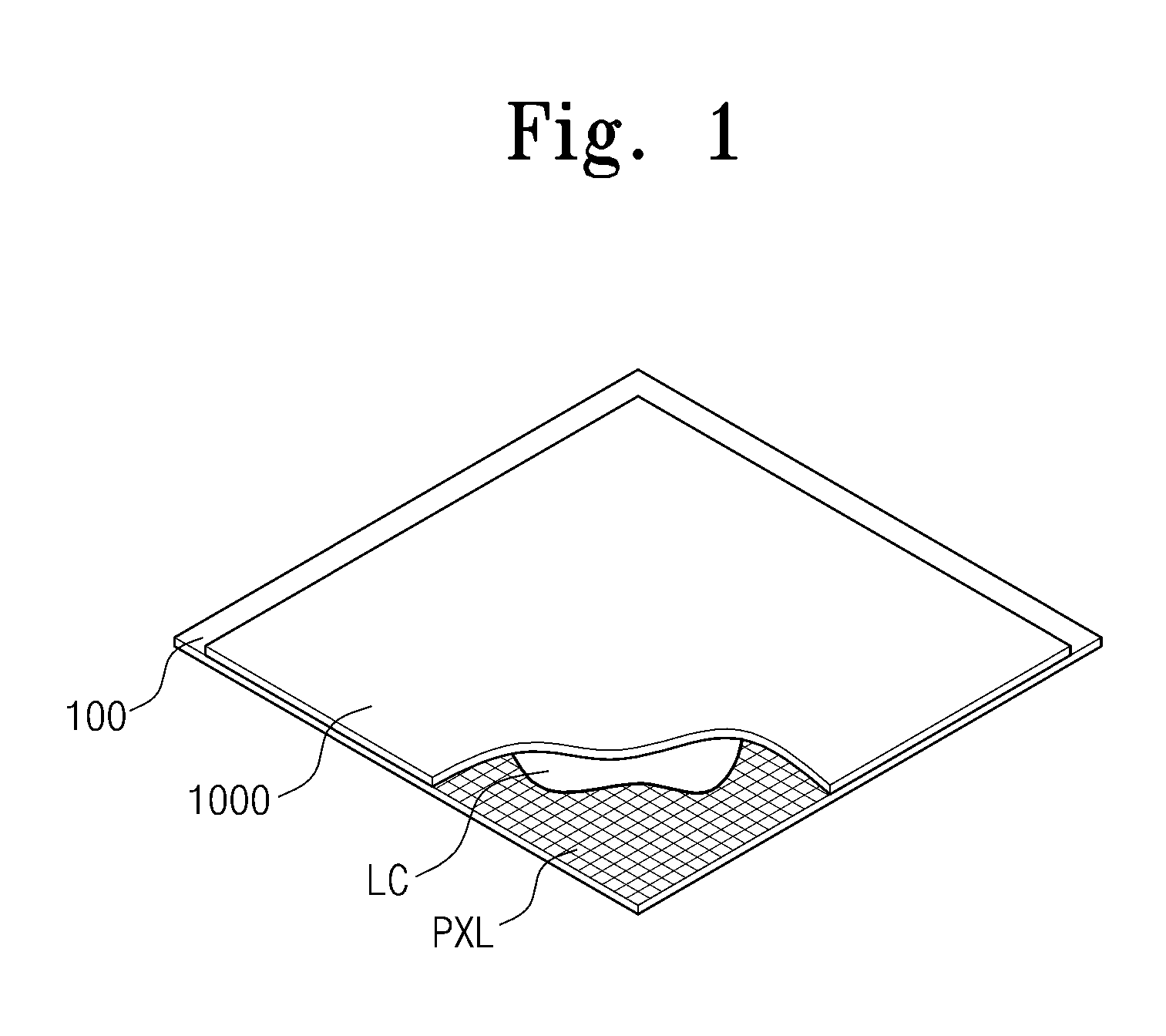

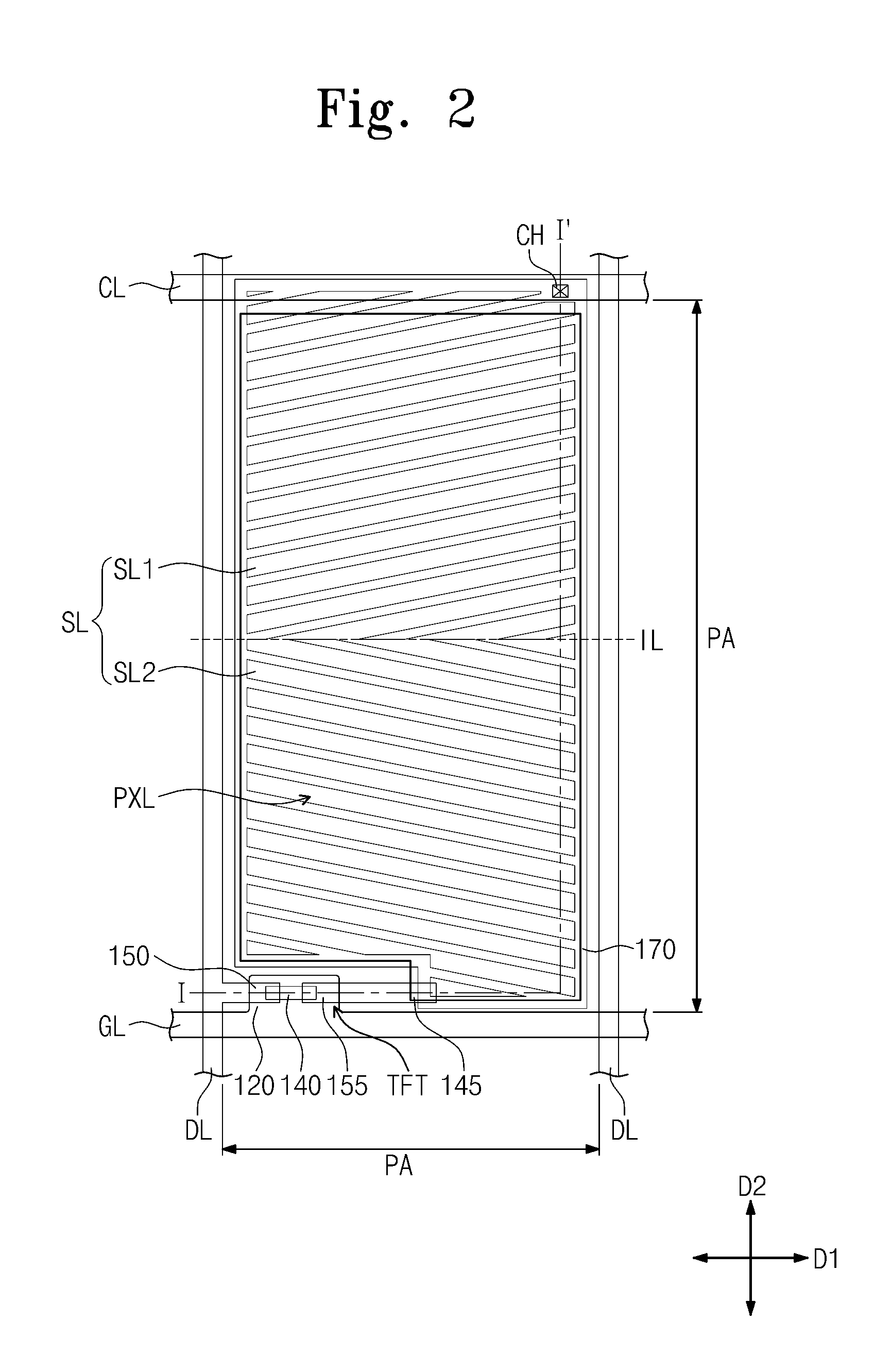

Thin film transistor substrate and display apparatus using the same

ActiveUS20160093647A1Reduce the number of masksReduce in quantityTransistorSolid-state devicesDielectricInsulation layer

A thin film transistor (TFT) substrate is disclosed. The TFT substrate includes a substrate, a blocking layer, a source electrode, and a drain electrode on a same layer over the substrate, an active layer overlapping the blocking layer, the source electrode, and the drain electrode, a gate insulation layer over the active layer, a first gate electrode over the gate insulation layer, an interlayer dielectric over the first gate electrode, a first connection electrode over the interlayer dielectric and connected to the active layer and the source electrode through a first contact hole, a second connection electrode over the interlayer dielectric and connected to the active layer and the drain electrode through a second contact hole, a planarization layer over the first connection electrode and the second connection electrode, and a pixel electrode over the planarization layer and connected to the second connection electrode through a third contact hole.

Owner:LG DISPLAY CO LTD

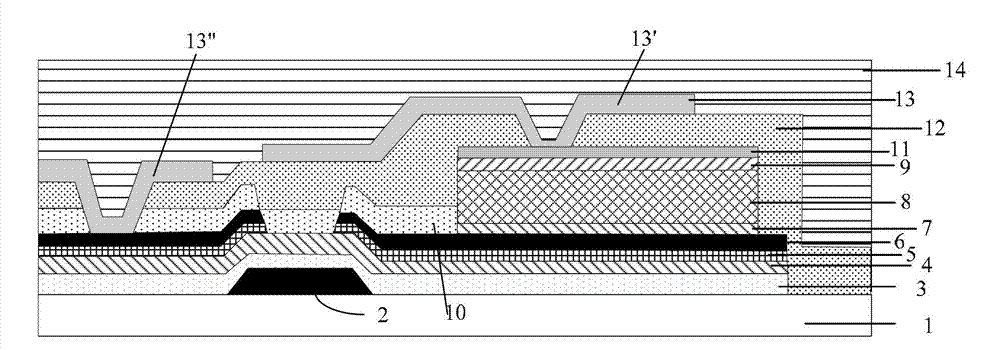

Oxide Thin Film Transistor, Method for Fabricating TFT, Array Substrate for Display Device and Method for Fabricating the Same

ActiveUS20130313546A1Enhancing element uniformity characteristicAvoid misalignmentTransistorSolid-state devicesOxide thin-film transistorDisplay device

Owner:LG DISPLAY CO LTD

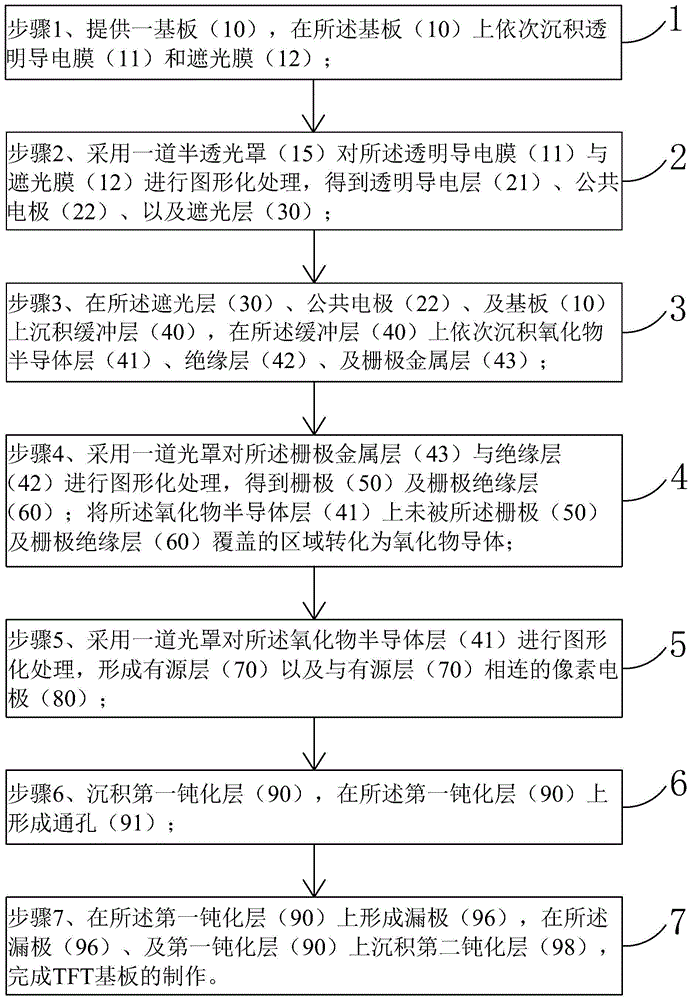

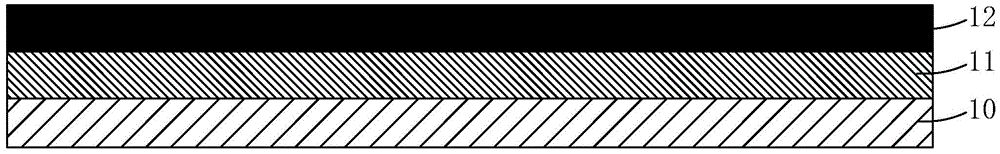

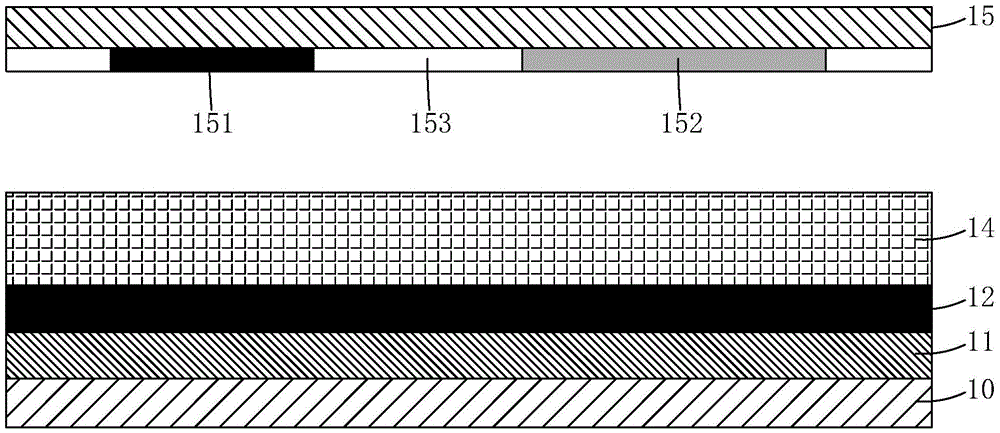

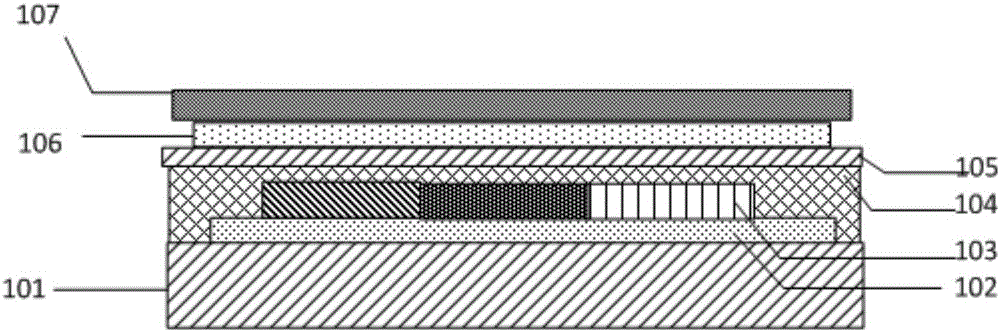

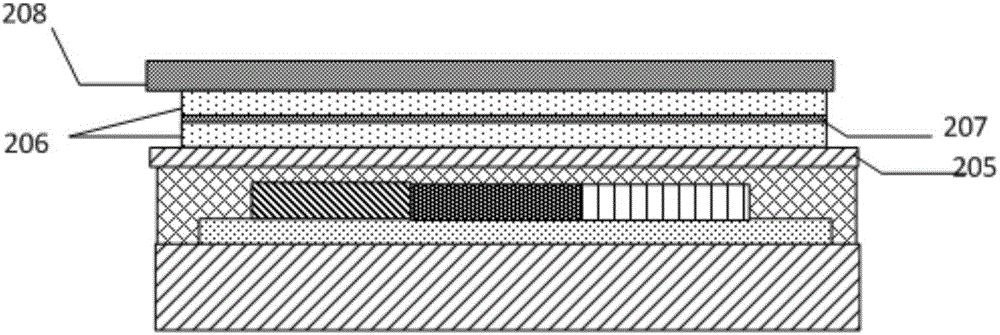

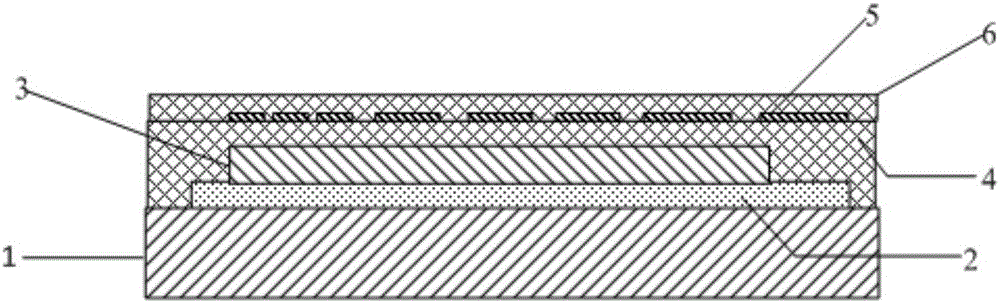

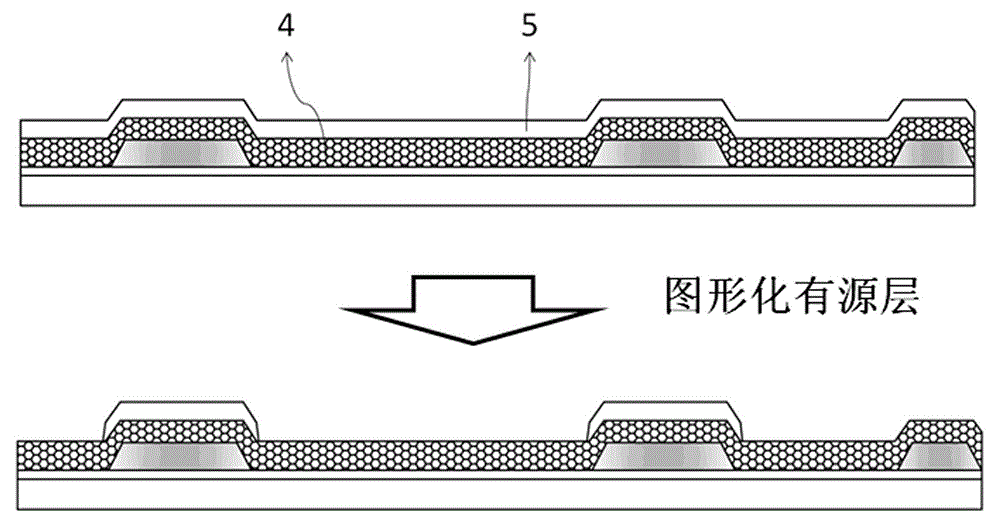

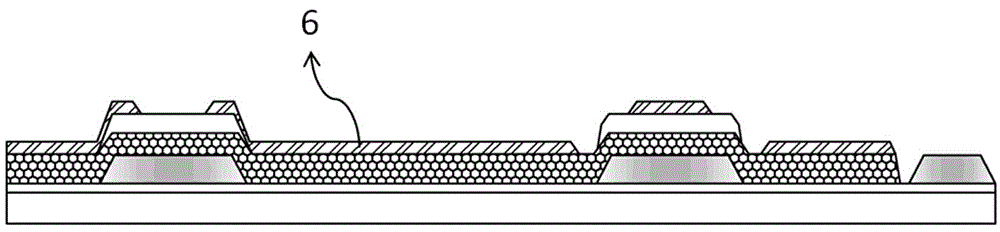

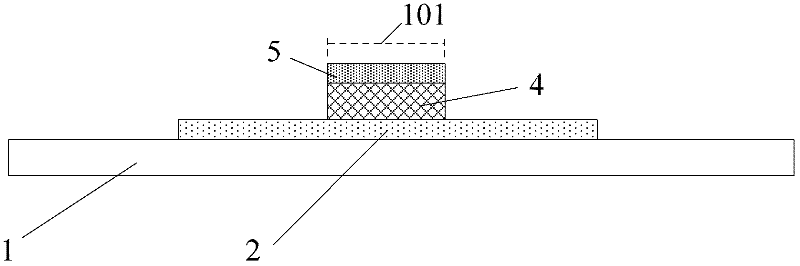

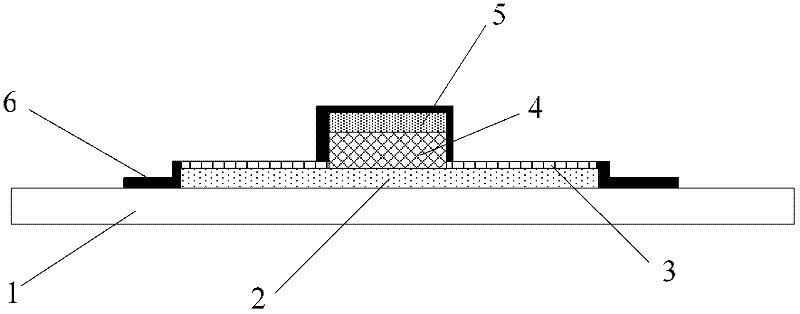

Manufacturing method of TFT substrate and prepared TFT substrate

ActiveCN105633016AReduce the number of masksIncrease productivitySolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorEtching

The invention provides a manufacturing method of a TFT substrate and a prepared TFT substrate. According to the manufacturing method of the TFT substrate, based on the characteristic of high visible light transmittance of a transparent metal oxide semiconductor material and doping processing is performed on a transparent metal oxide semiconductor, so that a transparent metal oxide conductor can be obtained, and at the same time, an active layer and a pixel electrode are formed, and therefore, the number of the times of photo masking can be decreased, production efficiency can be improved, and production cost can be reduced; in addition, based on only one semi-transparent photo mask, exposure and etching are performed, so that a common electrode, and a stack light shielding layer formed by a light shielding layer and a transparent conductive layer can be obtained, and therefore, the number of the times of photo masking can be further decreased; and the light shielding layer is arranged at the lower part of a TFT, so that the electrical stability of the TFT will not be affected by illumination. The TFT substrate of the invention is simple in manufacturing process and low in production cost; and the light shielding layer is arranged at the lower part of the TFT, so that the electrical stability of the TFT will not be affected by illumination.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Liquid crystal display device and method for manufacturing the same

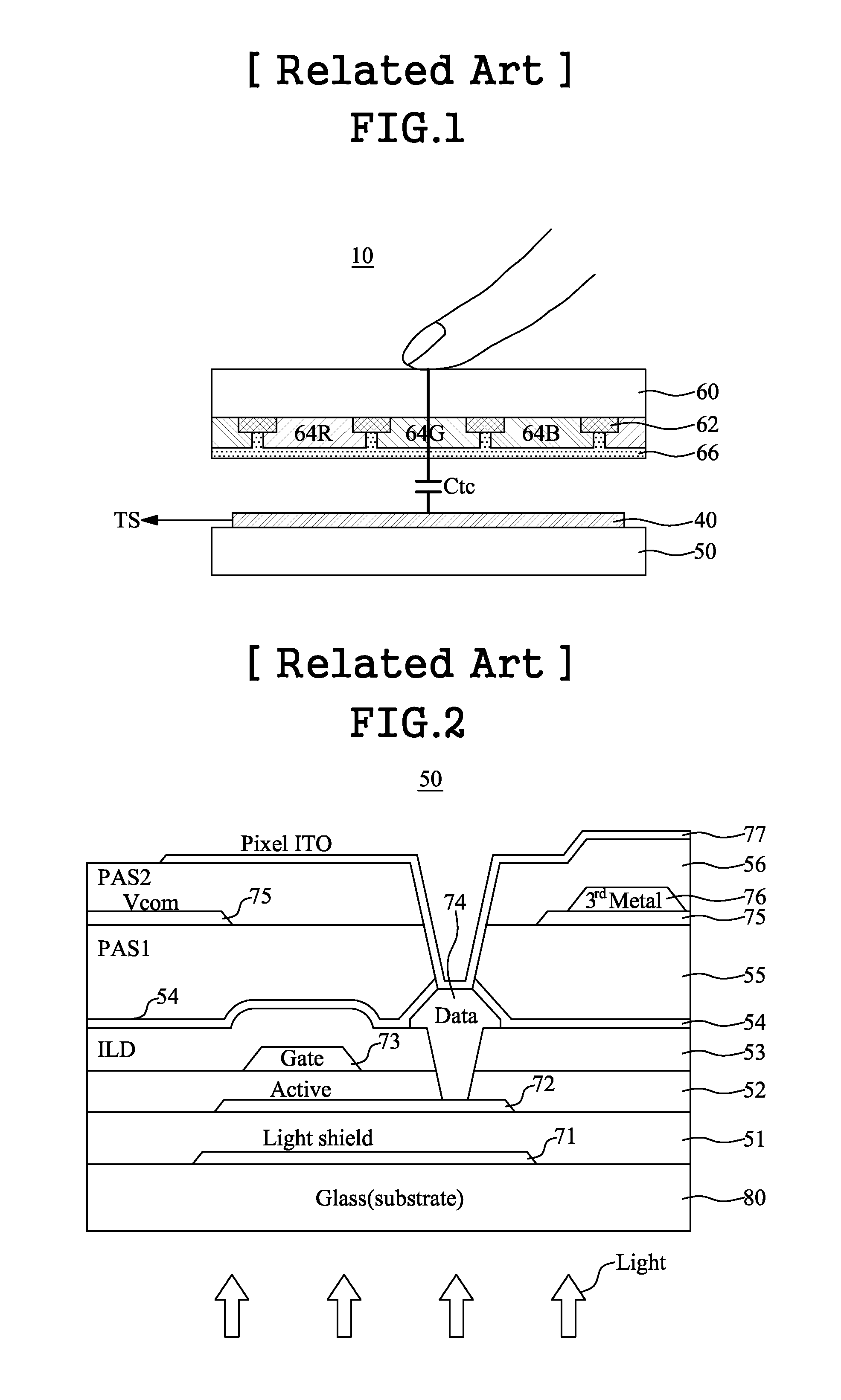

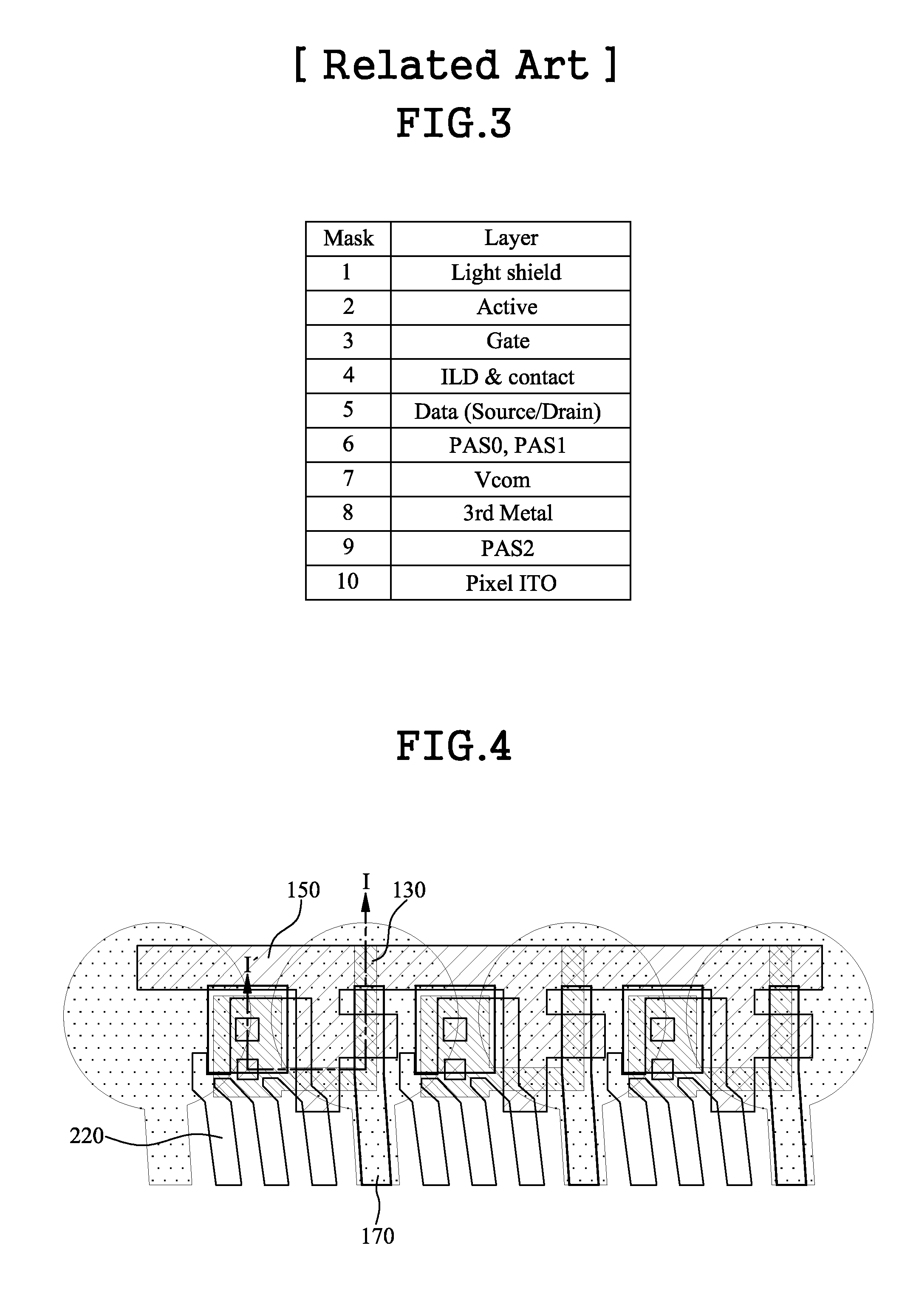

ActiveUS20120069259A1Reduce manufacturing costReduce the number of masksSolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayEngineering

Disclosed is a liquid crystal display device with a built-in touch screen, which facilitates enhanced driving performance, and reduces manufacturing cost by a simplified manufacturing process, and a method for manufacturing the same. The device comprises a first substrate with a plurality of pixel regions defined by gate lines and data lines; an active layer in each pixel region of the first substrate; a gate pattern including a plurality of gate electrodes, a portion of the gate electrodes overlapping with a predetermined portion of the active layer with an insulating layer interposed in-between; a plurality of channel regions in the areas of the active layer overlapped with the plurality of gate electrodes; a plurality of lightly doped drain regions in the active layer and directly adjacent to the plurality of channel regions; and a data electrode electrically connected to the active layer.

Owner:LG DISPLAY CO LTD

Organic light emitting diode (OLED) display panel, preparation method thereof and display device

ActiveCN105161514AReduce the number of masksSimple manufacturing processSolid-state devicesSemiconductor/solid-state device manufacturingManufacturing technologyDisplay device

The invention discloses an organic light emitting diode (OLED) display panel, a preparation method thereof and a display device. The organic light emitting diode display panel comprises a white organic light-emitting diode and a metal color filter of a period nanostructure. By arranging a layer of the metal color filter of the period nanostructure to be integrated with a backlight source of the white organic light-emitting diode, a color OLED display structure can be achieved. Compared with the conventional OLED color display structure, the organic light emitting diode display panel provided by an embodiment of the invention only uses one manufacturing process to form the metal color filter. Compared with that a RGB color film layer by more than once evaporation technology in the prior art, the invention can reduce the mask number, simplify the manufacturing technology of the OLED display panel and reduce the production cost. In addition, the metal color filter of the period nanostructure is used for facilitating development of high-resolution products.

Owner:BOE TECH GRP CO LTD

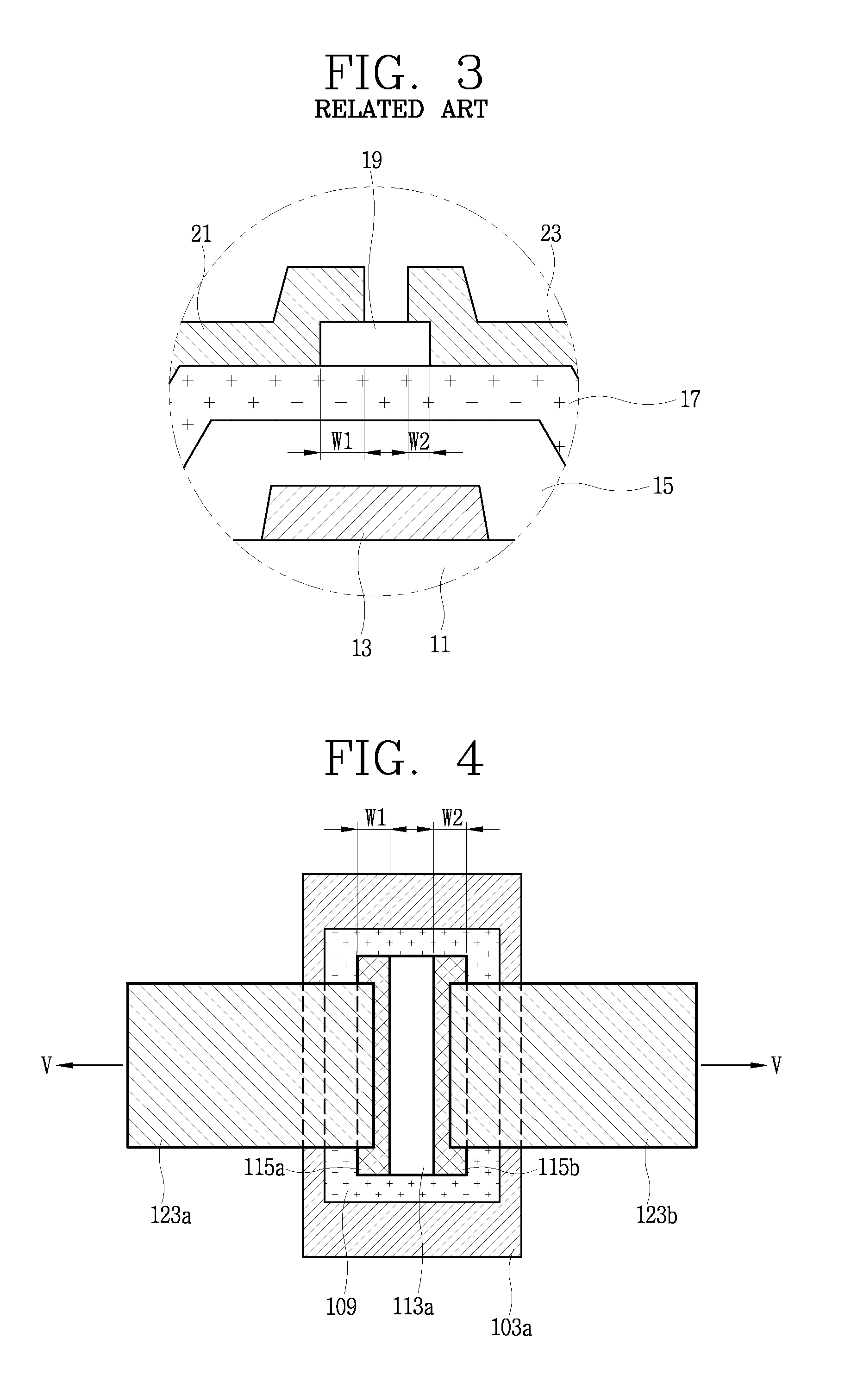

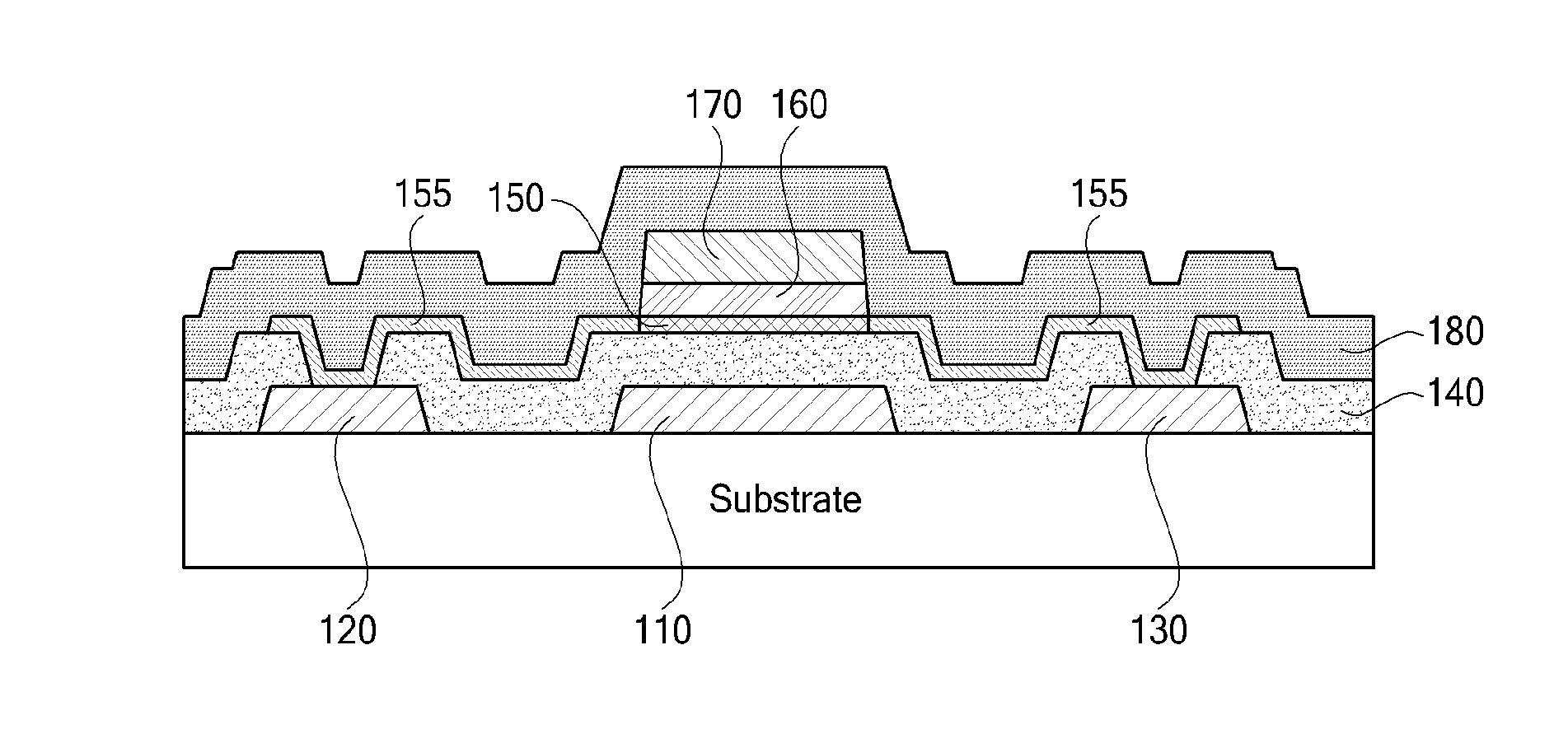

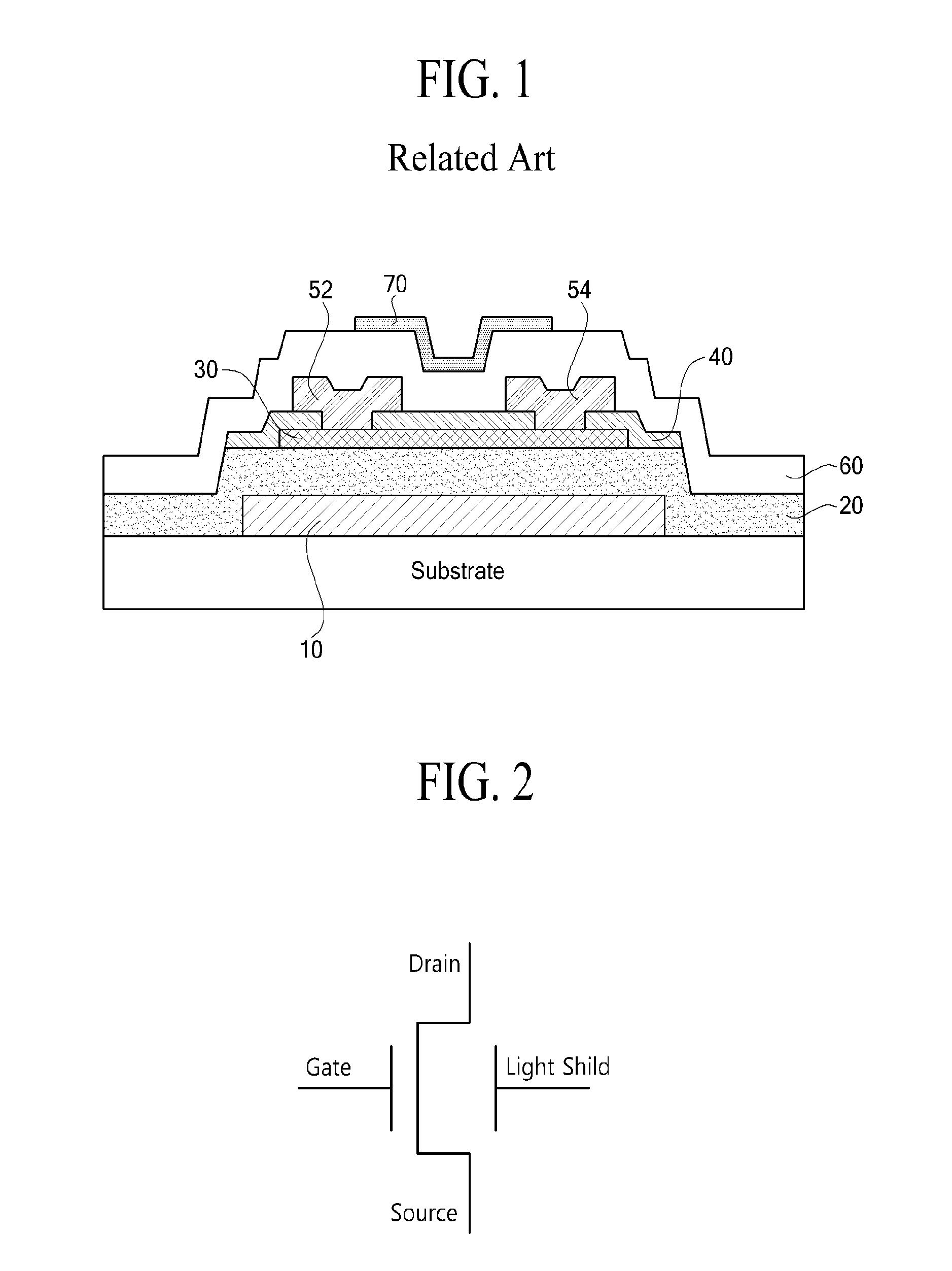

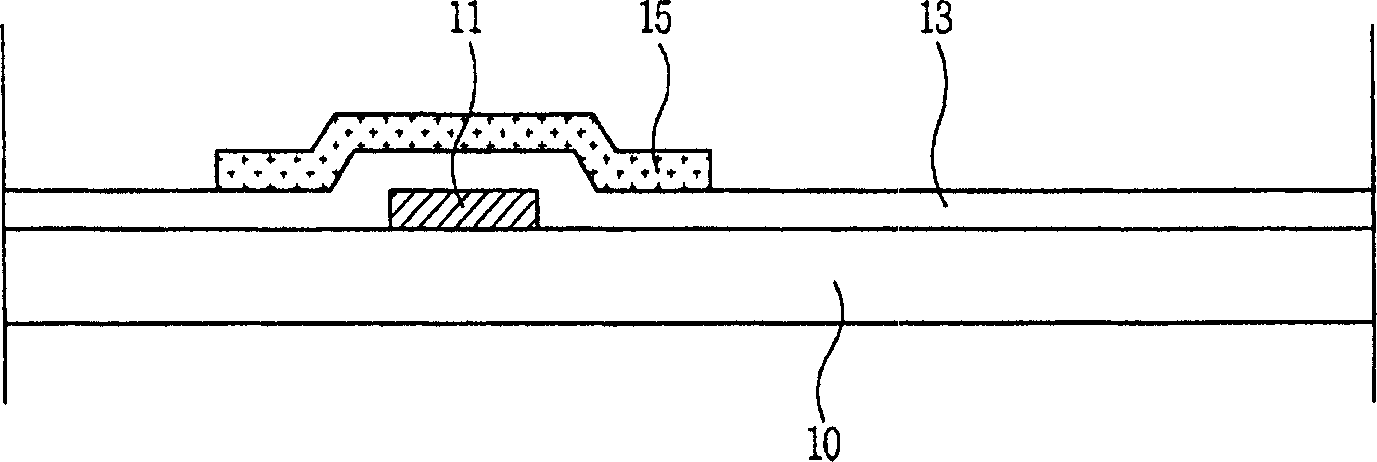

Organic light emitting display device and method of manufacturing the same

ActiveUS20150187860A1Reduce the number of masksImprove production efficiencyTransistorSolid-state devicesDisplay deviceEngineering

Disclosed is an organic light emitting display device. The organic light emitting display device includes a switching thin film transistor (TFT) that includes a lower gate, a source, and a drain formed on a substrate and on the same layer, a first gate insulating layer formed to cover the lower gate, the source, and the drain, an active layer formed on the first gate insulating layer, a conductive line formed to contact the source and the drain, a second gate insulating layer formed on the active layer, and an upper gate formed on the second gate insulating layer. The lower gate of the switching TFT is a light shield that blocks light from being irradiated onto the active layer.

Owner:LG DISPLAY CO LTD

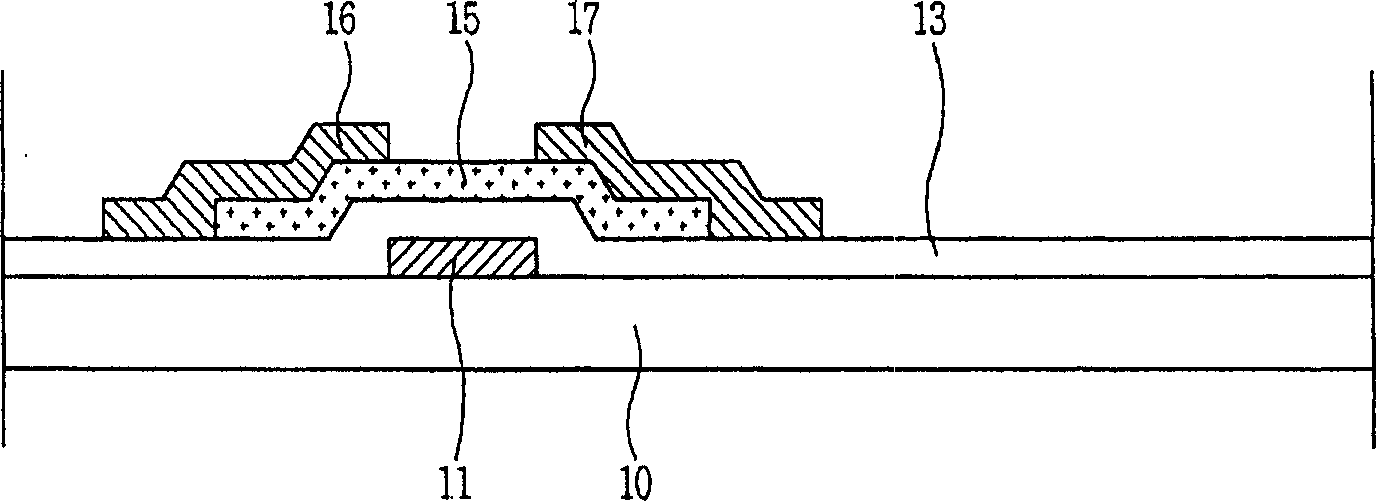

Method for making organic thin film transistor and method for making liquid crystal display using same

ActiveCN1743930AReduce the number of masksSimple manufacturing processTransistorStatic indicating devicesLiquid-crystal displayThin-film transistor

The invention provides a method for fabricating organic thin film transistor and a method for fabricating liquid crystal display device using the same. A method for fabricating an organic thin film transistor includes forming a gate electrode on a substrate, forming a gate insulating layer on the substrate including the gate electrode, forming an organic active pattern on the gate insulating layer using a rear exposing process, and forming source and drain electrodes on the organic active pattern.

Owner:LG DISPLAY CO LTD

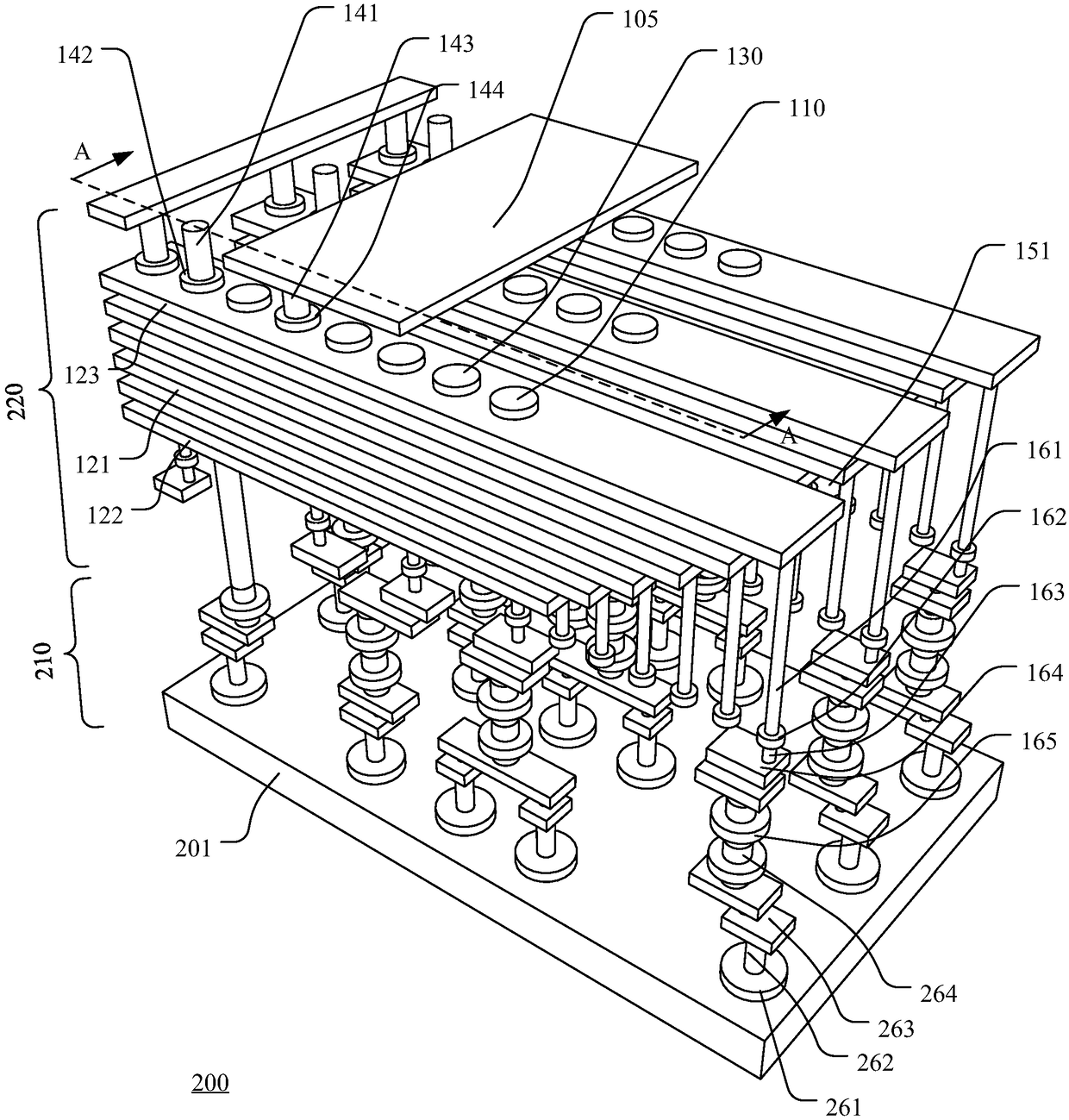

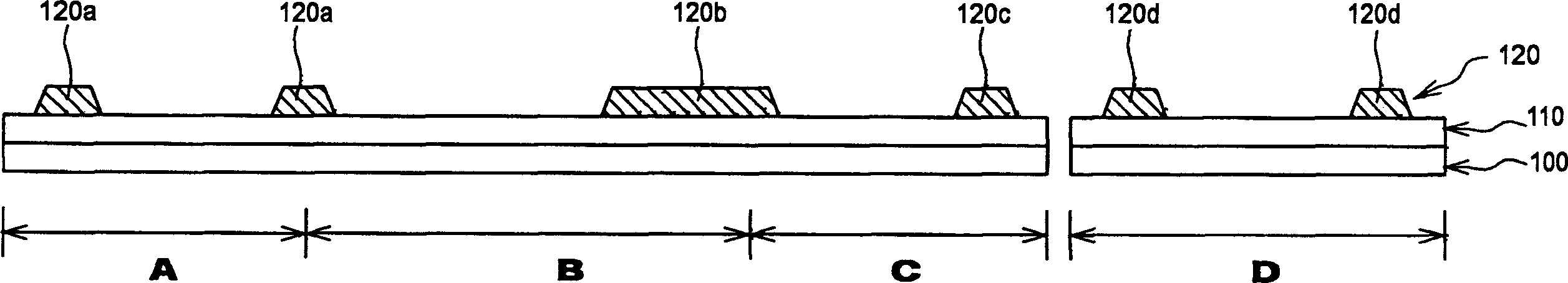

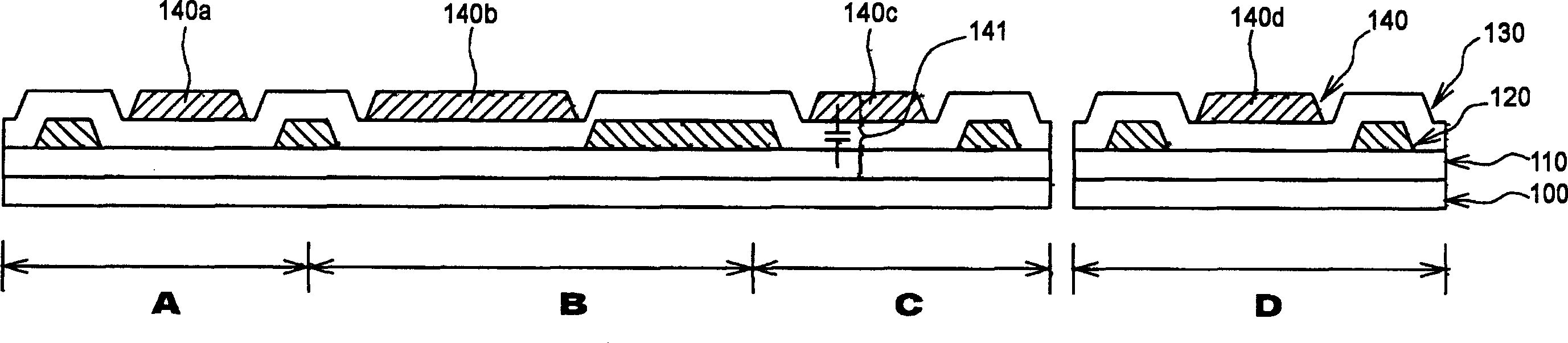

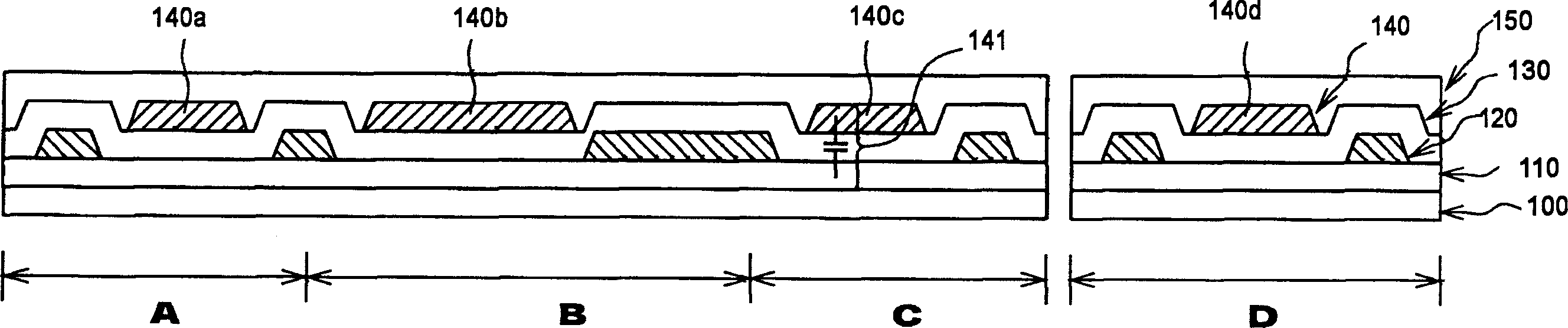

Active matrix organic light emitting diode driving back plate and preparation method of active matrix organic light emitting diode driving back plate

InactiveCN102945828AReduce breakdown phenomenonReduce manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceActive matrix

The invention relates to an active matrix organic light emitting diode driving back plate and a preparation method of the active matrix organic light emitting diode driving back plate. The preparation method comprises the steps that a metal conducting layer is deposited and patterned on a substrate to be used as a grid electrode metal layer; an insulating film is deposited on the grid electrode metal layer to be used as a grid electrode insulating layer; a metal oxide film is deposited and patterned on the grid electrode insulating layer to be used as an active layer; another insulating film is deposited on the active layer to be used as an etching barrier layer; contact holes, the effective area of a memory capacitor and a source drain electrode region of a film transistor are patterned and defined on the etching barrier layer; and a conducting film is deposited and patterned on the etching barrier layer to be used as a source drain electrode layer of the film transistor. The memory capacitor uses the grid electrode metal layer as a lower electrode plate, uses the grid electrode insulating layer as a dielectric layer and uses the active source as a protecting layer of the grid electrode insulating layer, the effective area of the capacitor is defined by the etching barrier layer, and in addition, the conducting film layer is used as an upper electrode plate of the capacitor. The active matrix organic light emitting diode driving back plate and the preparation method have the characteristics that the preparation process is simple, and the cost is low. The important industry application value technology is realized.

Owner:GUANG ZHOU NEW VISION OPTO ELECTRONICS TECH

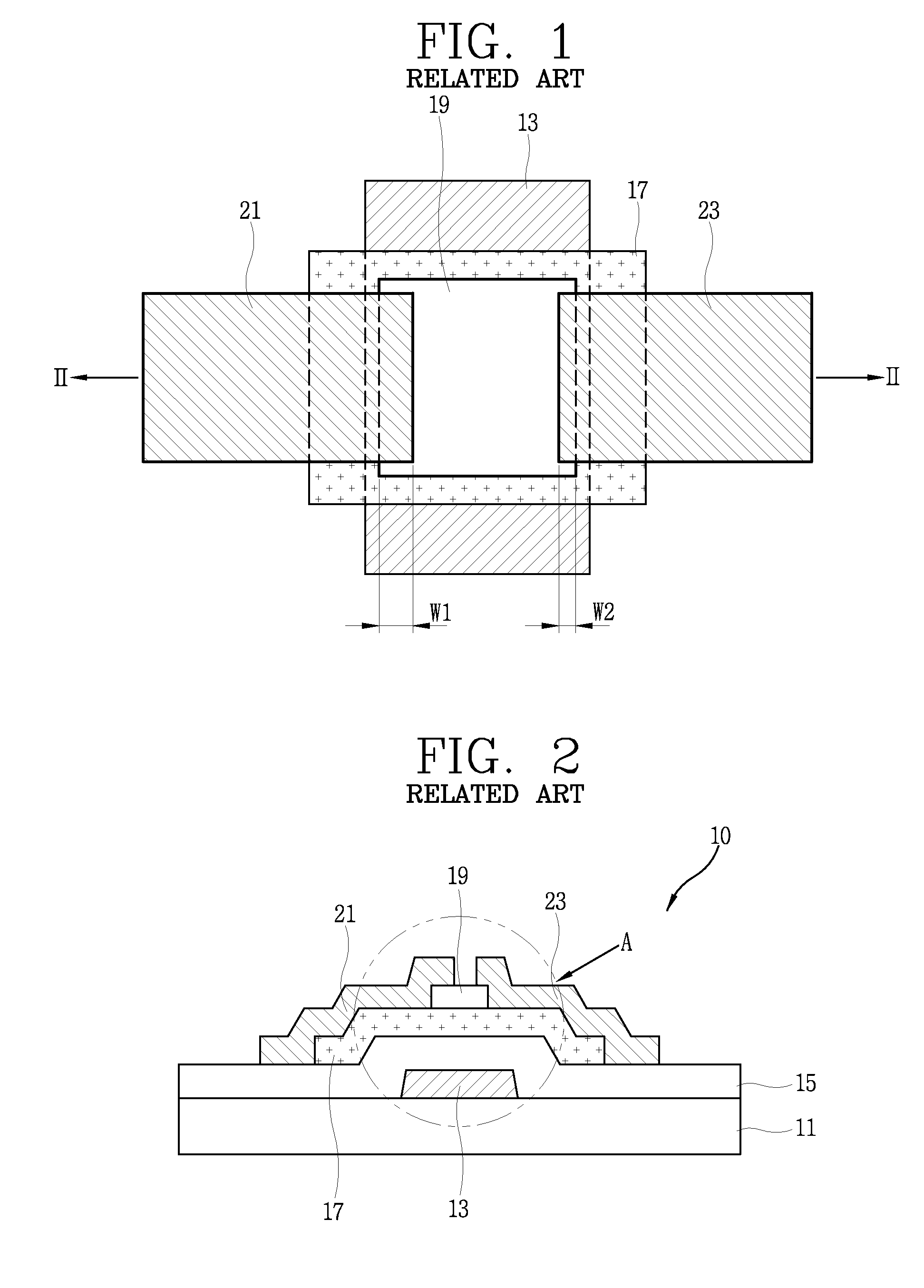

Polysilicon film transistor of liquid crystal display device and its mfg. method

InactiveCN1383214AAvoid surface damageReduce in quantityTransistorSolid-state devicesLiquid-crystal displayEngineering

The invention discloses a polysilicon TFT used for LCD and a manufacturing method thereof. The TFT includes an effective pattern formed on the substrate, a gate insulating layer formed on the substrate including the effective pattern, and a gate insulating layer formed on the gate insulating layer across the effective pattern and includes a method for defining the first impurity region, the second impurity region and the The gate line of the gate electrode of the channel region, the insulating interlayer formed on the gate insulating layer including the gate line, the data line formed on the insulating interlayer and connected to the second impurity region through the first contact hole, and formed on the The pixel electrode on the same insulating interlayer as the data line and connected to the first impurity region through the second contact hole, wherein the first contact hole is formed on the second impurity region through the gate insulating layer and the insulating interlayer, and the second contact A hole is formed on the first impurity region through the gate insulating layer and the insulating interlayer. The number of masks can be reduced to 5 or 6, thus simplifying the production process.

Owner:SAMSUNG DISPLAY CO LTD

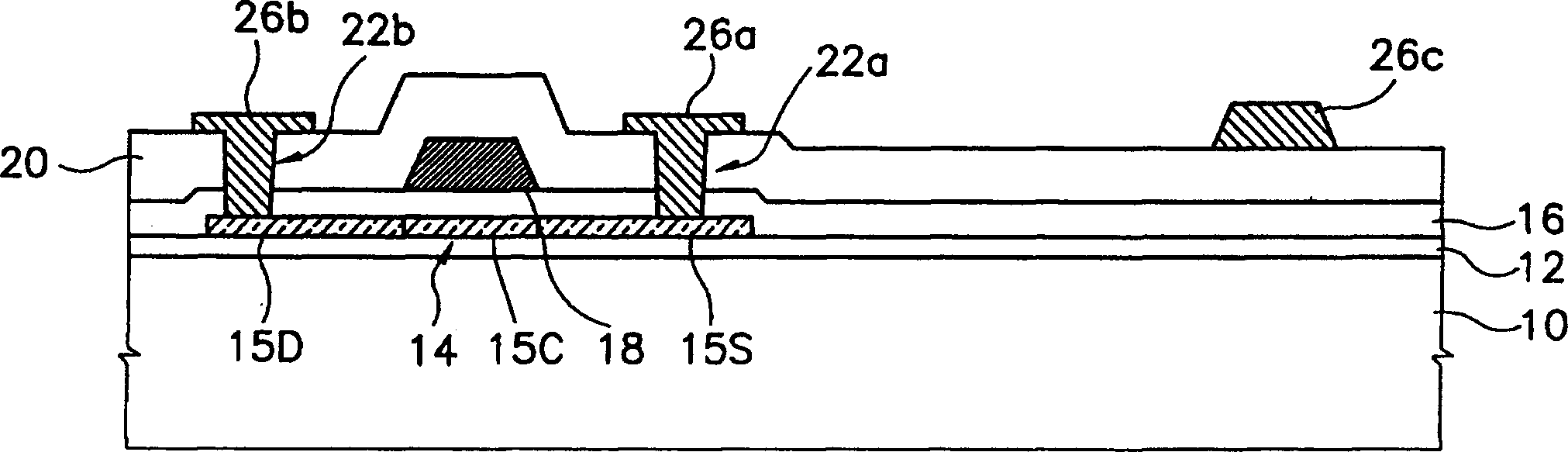

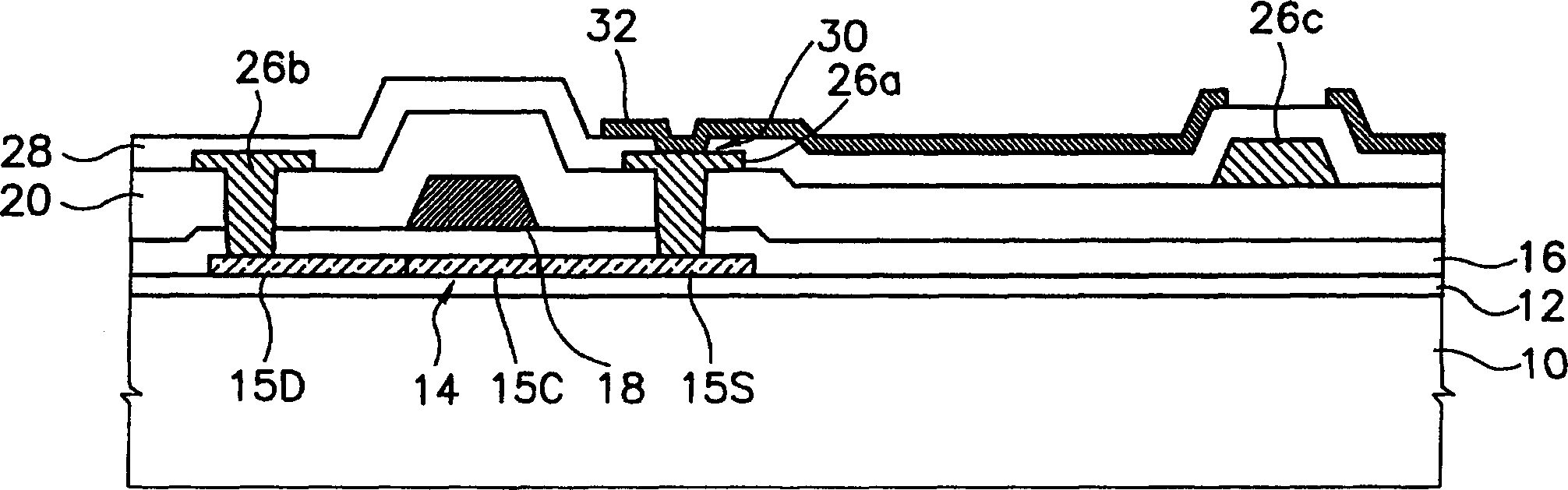

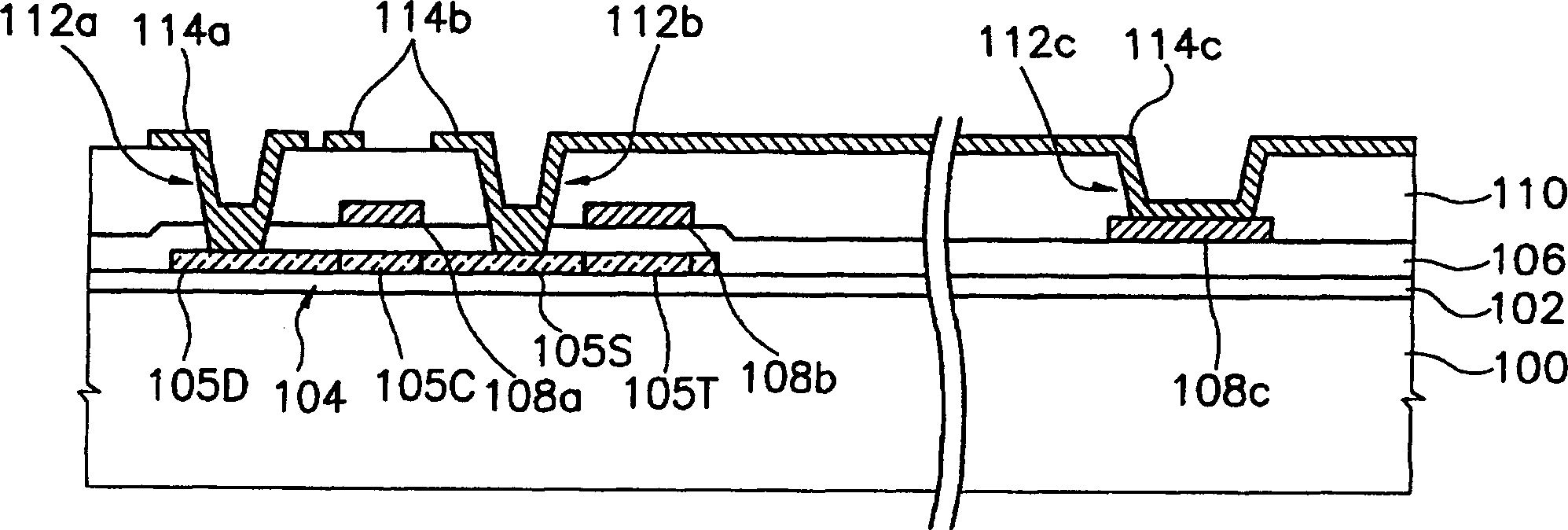

Semiconductor device and method for manufacturing the same

InactiveUS20080237876A1Improve featuresReduce the number of masksSemiconductor/solid-state device detailsSolid-state devicesSemiconductorSemiconductor device

A method for easily manufacturing a semiconductor device in which variation in thickness or disconnection of a source electrode or a drain electrode is prevented is proposed A semiconductor device includes a semiconductor layer formed over an insulating substrate; a first insulating layer formed over the semiconductor layer; a gate electrode formed over the first insulating layer; a second insulating layer formed over the gate electrode; an opening which reaches the semiconductor layer and is formed at least in the first insulating layer and the second insulating layer; and a step portion formed at a side surface of the second insulating layer in the opening.

Owner:SEMICON ENERGY LAB CO LTD

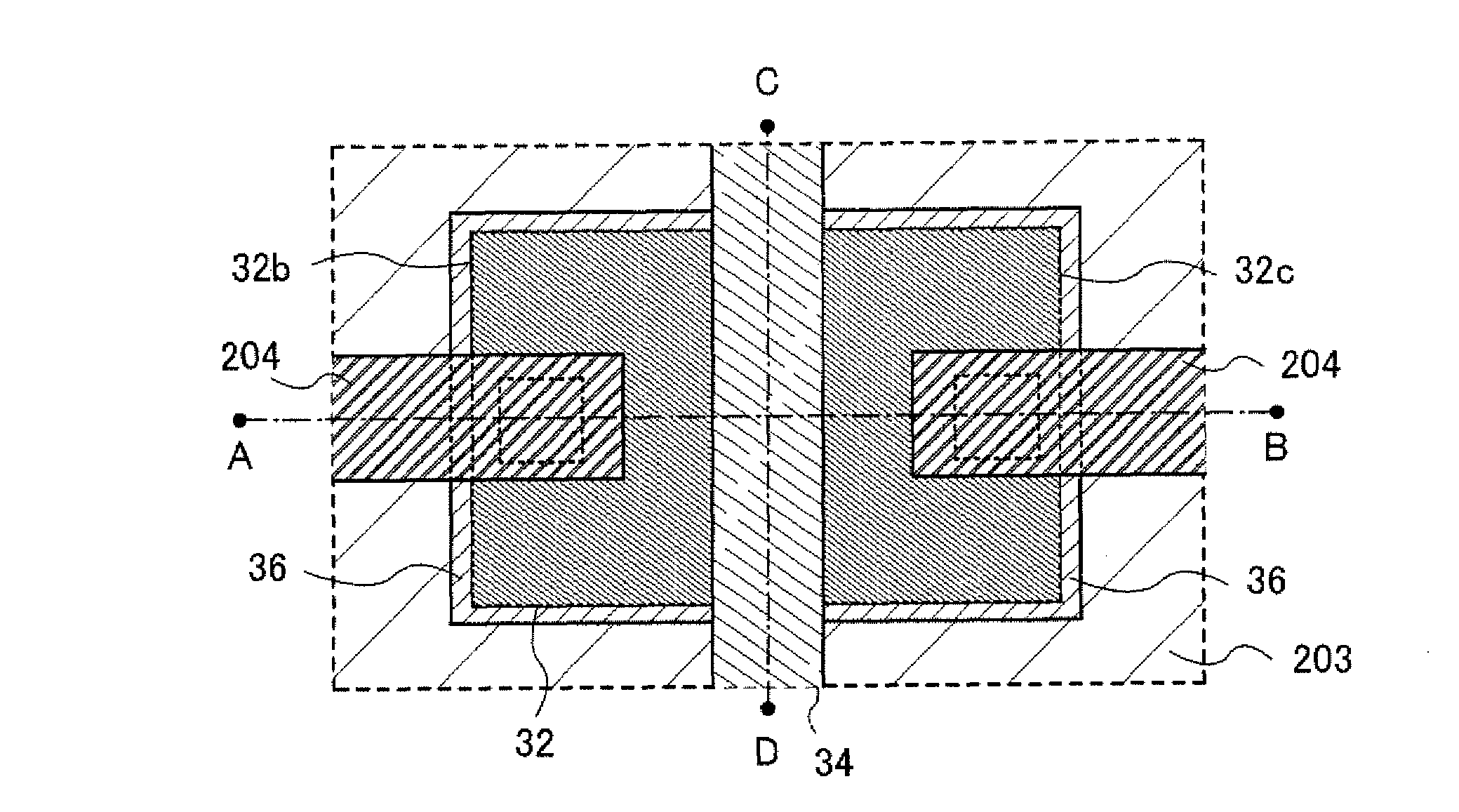

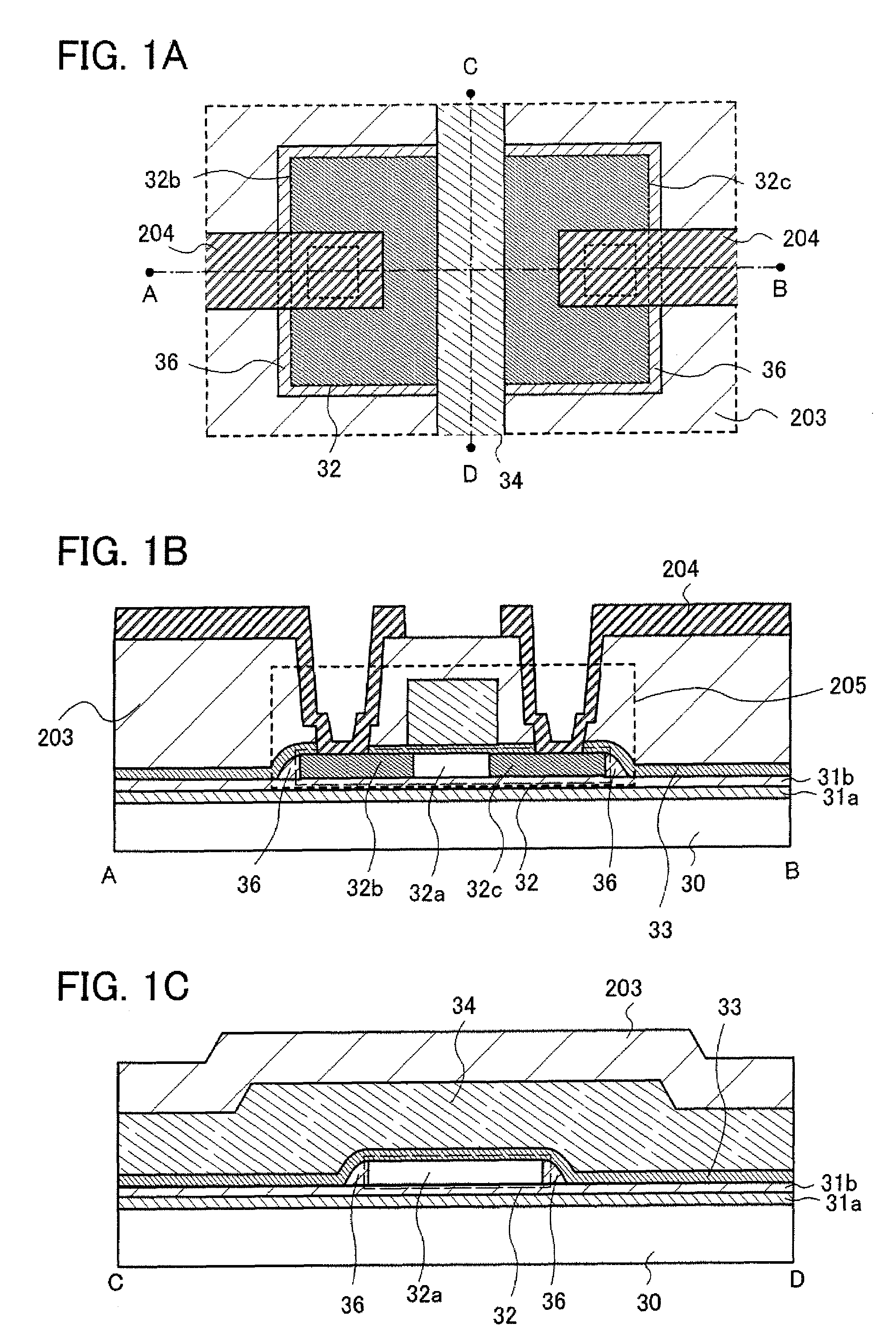

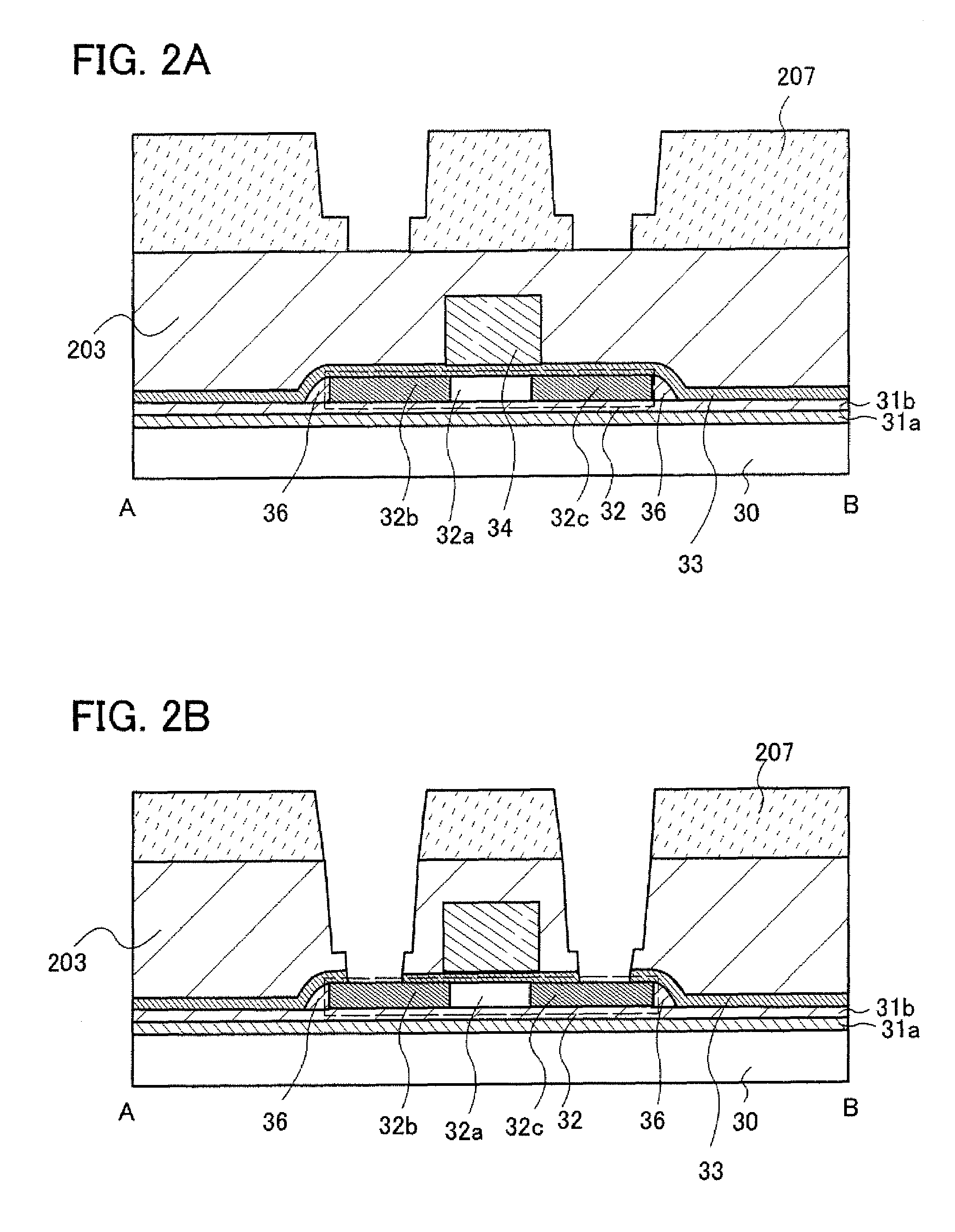

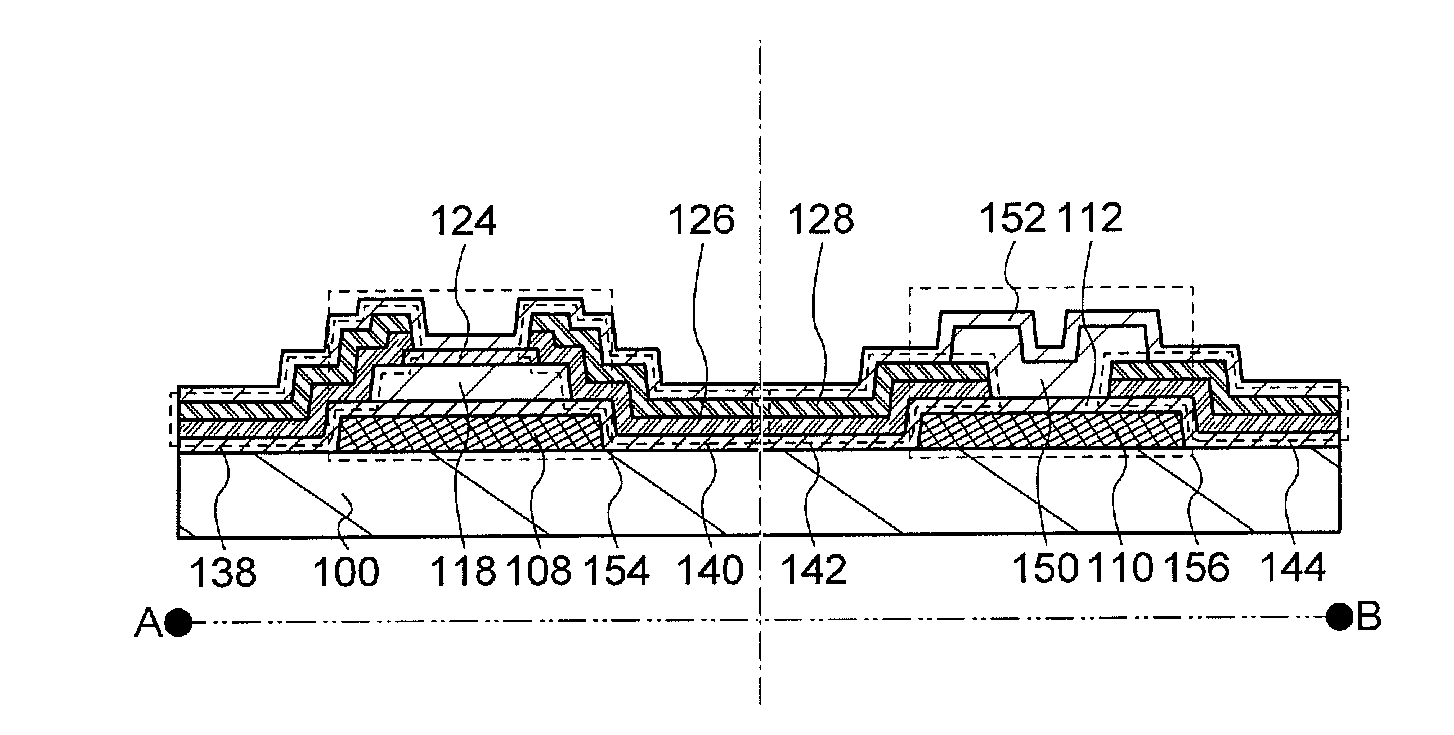

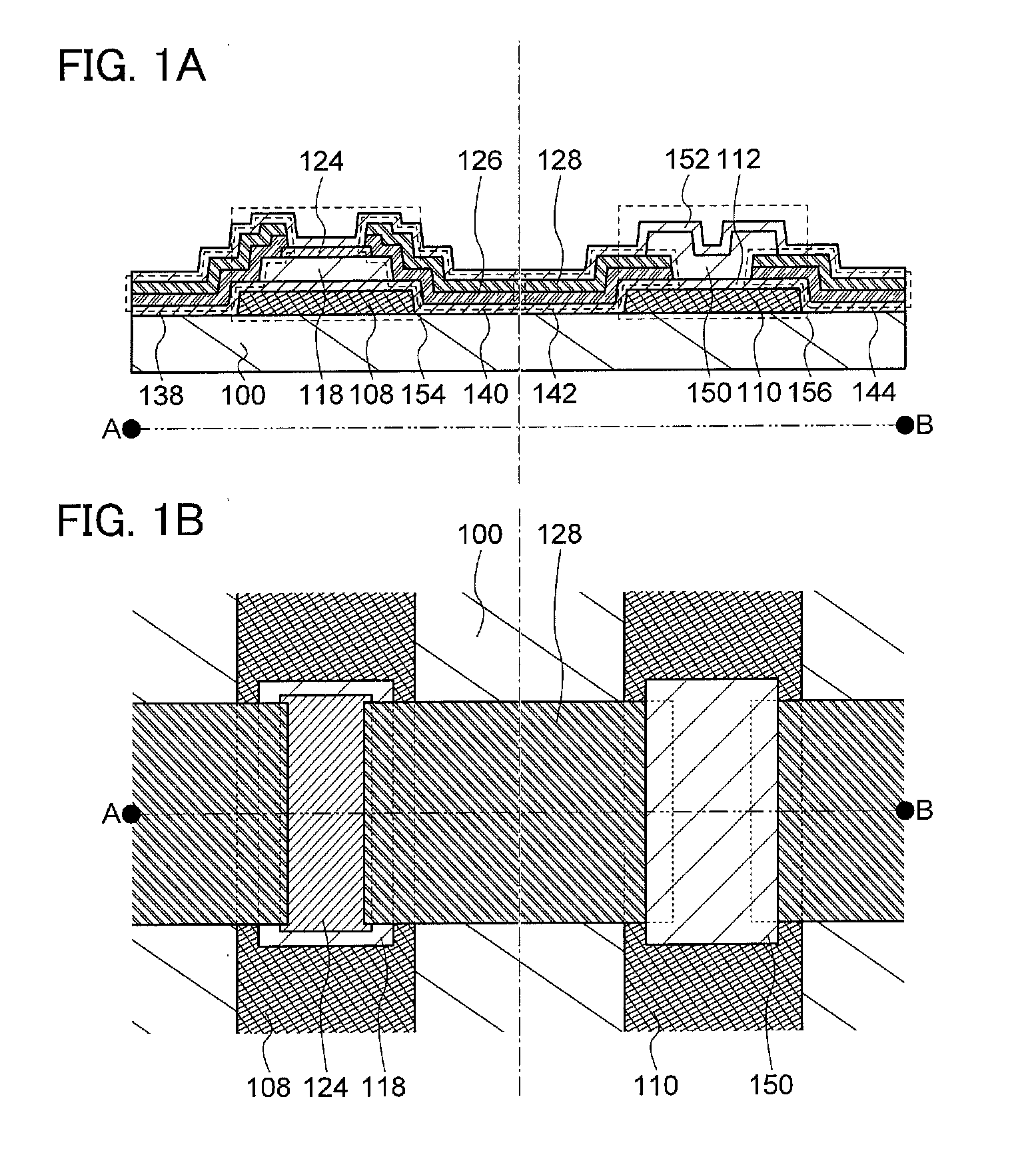

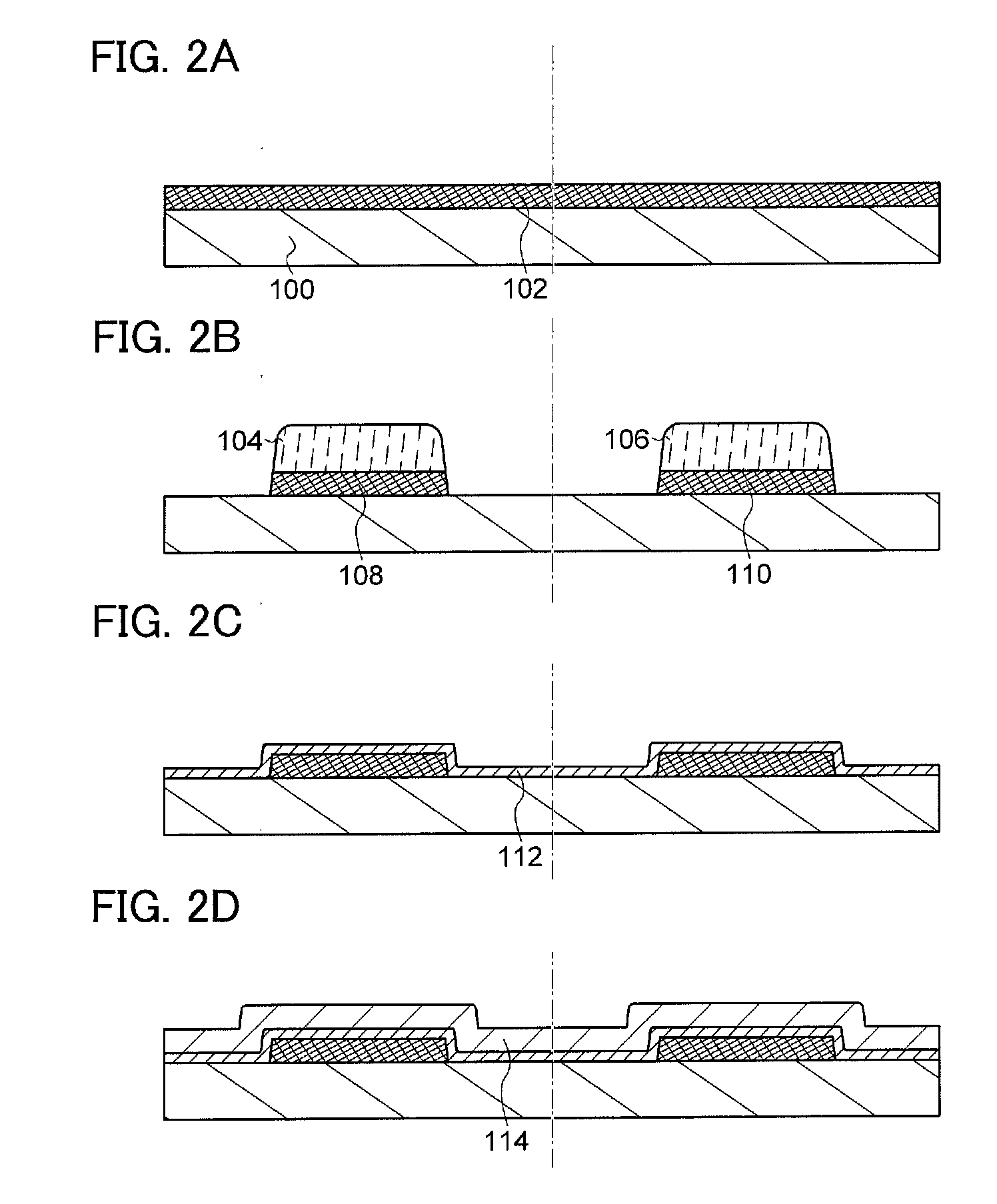

Semiconductor Device and Method for Manufacturing the Same

ActiveUS20100258802A1Reduce the number of masksImprove featuresTransistorSolid-state devicesP channelSemiconductor

An object is to provide an n-channel transistor and a p-channel transistor having a preferred structure using an oxide semiconductor. A first source or drain electrode which is electrically connected to a first oxide semiconductor layer and is formed using a stacked-layer structure including a first conductive layer containing a first material and a second conductive layer containing a second material, and a second source or drain electrode which is electrically connected to a second oxide semiconductor layer and is formed using a stacked-layer structure including a third conductive layer containing the first material and a fourth conductive layer containing the second material are included. The first oxide semiconductor layer is in contact with the first conductive layer of the first source or drain electrode, and the second oxide semiconductor layer is in contact with the third and the fourth conductive layers of the second source or drain electrode.

Owner:SEMICON ENERGY LAB CO LTD

Array substrate, manufacturing method thereof and display device

InactiveCN102646632AImprove stabilityReduce the number of masksSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerDisplay device

The invention discloses a manufacturing method of an array substrate, which relates to the technical field of display and comprises the following steps of: S1, forming graphs of a semiconductor layer, a gate insulation layer, a grid electrode and a grid line on the substrate; S2, forming a metal diffusion layer on the semiconductor graph which is not covered by the gate insulation layer on the substrate after step 1, and forming barrier layers in other areas; S3, forming a passivation layer on the substrate after step 2; and S4, forming graphs of a through hole, a source drain, a data line and a pixel electrode on the passivation layer, wherein the source drain is connected with the metal diffusion layer through the through hole. The invention also discloses an array substrate and a display device. Compared with the conventional mask manufacturing process more than four times, the process flow of the manufacturing method disclosed by the invention is reduced, and the process cost is reduced.

Owner:BOE TECH GRP CO LTD

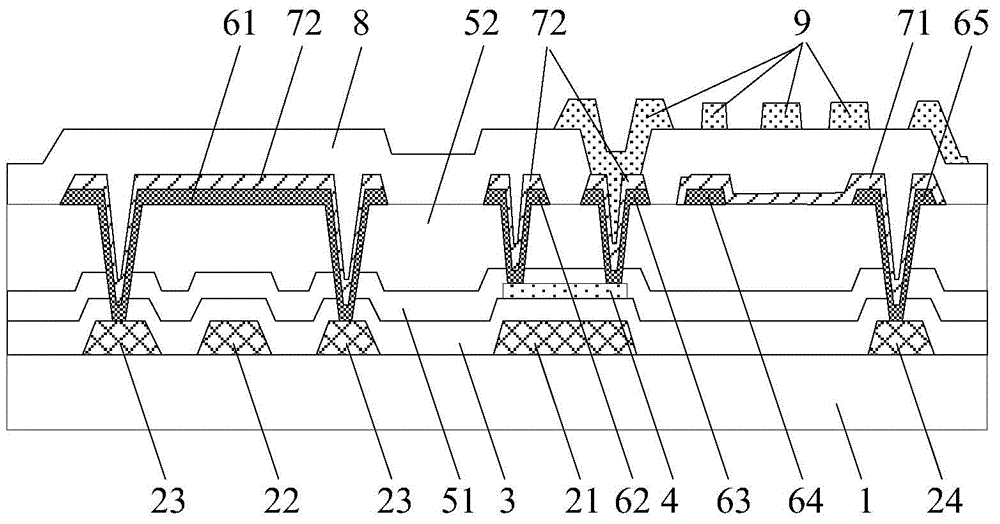

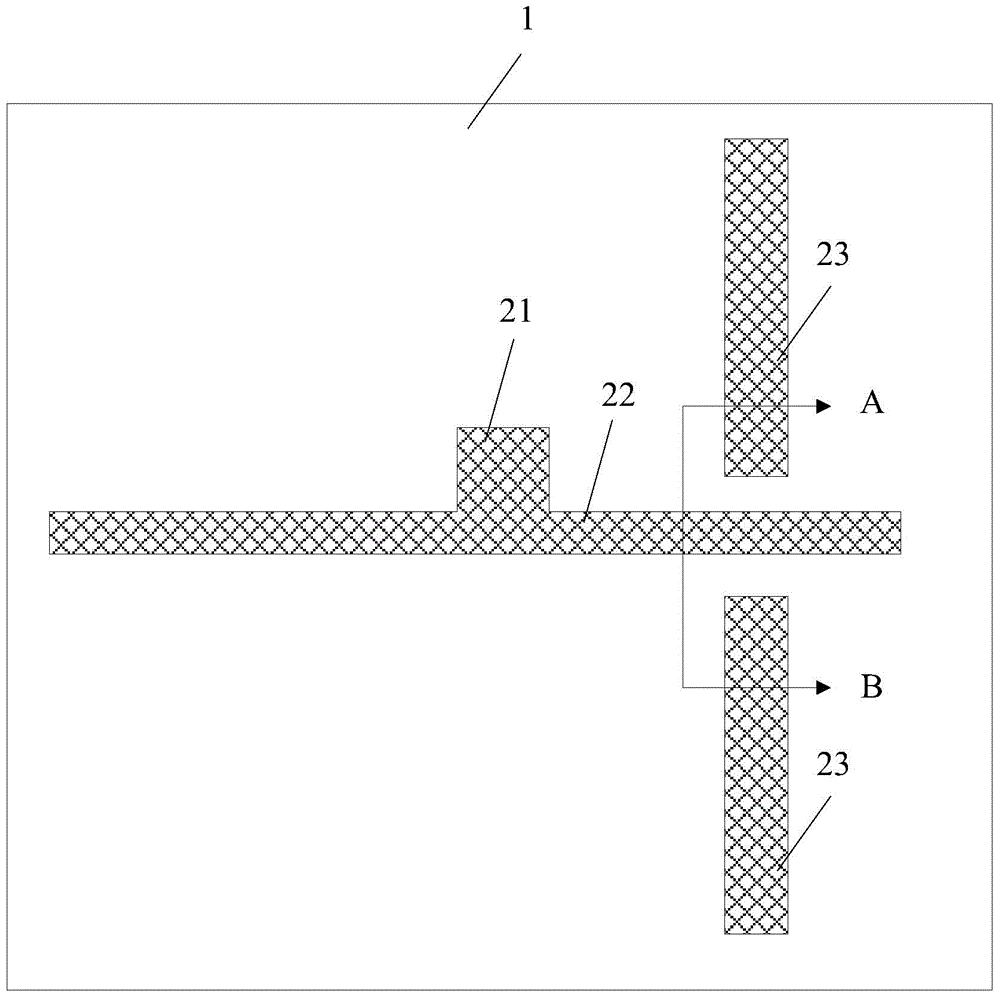

Array substrate and manufacturing method thereof, display panel and display apparatus

ActiveCN104966721AReduce parasitic capacitanceReduce the number of masksSolid-state devicesSemiconductor/solid-state device manufacturingManufacturing technologyInsulation layer

The invention discloses an array substrate and a manufacturing method thereof, a display panel and a display apparatus. In the prior art, a manufacturing technology of the array substrate is complex and a stray capacitance between a gate electrode and source and drain electrodes of a film transistor is large so that power consumption is large. By using the array substrate and the manufacturing method thereof, the display panel and the display apparatus of the invention, the above problems are solved. The array substrate comprises a gate metal layer, a gate insulation layer, an active layer, an etching barrier layer, a source and drain metal layer, a common electrode layer, a passivation layer and a pixel electrode layer which are successively formed on a substrate. An organic insulating layer is arranged between the etching barrier layer and the source and drain metal layer. The gate metal layer comprises the gate electrode, a gate line and a data line, wherein the gate line and the data line are arranged in a cross mode. The gate electrode is located below the active layer. The data line is separated into several segments by the gate line. The source and drain metal layer comprises a source electrode, a drain electrode and a plurality of first connecting lines. The source electrode and the drain electrode are located above the active layer and are connected to the active layer through first through holes of different positions respectively. The several segments of each data line are connected into one body through the plurality of first connecting lines.

Owner:BOE TECH GRP CO LTD

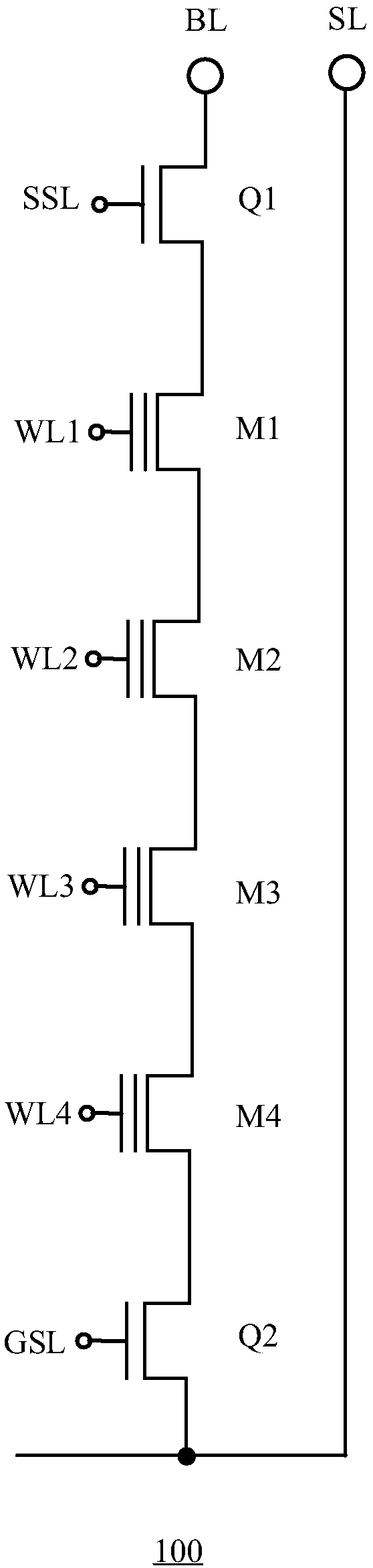

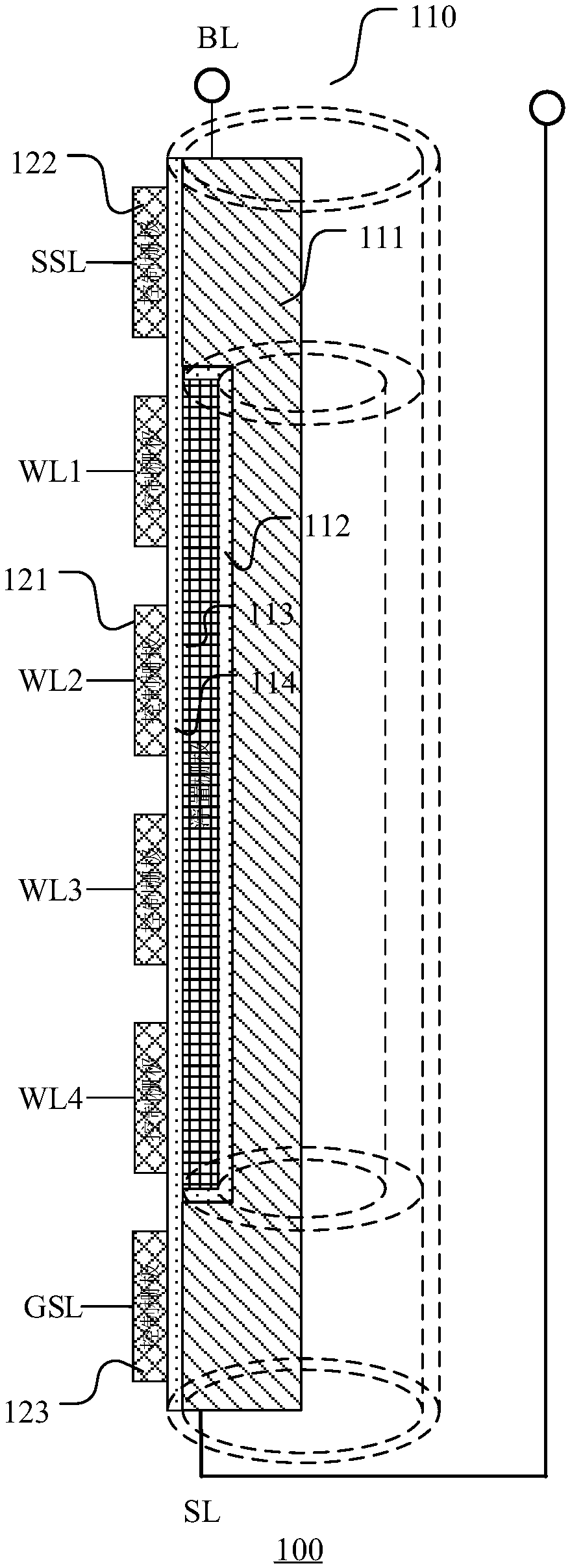

3D storage device

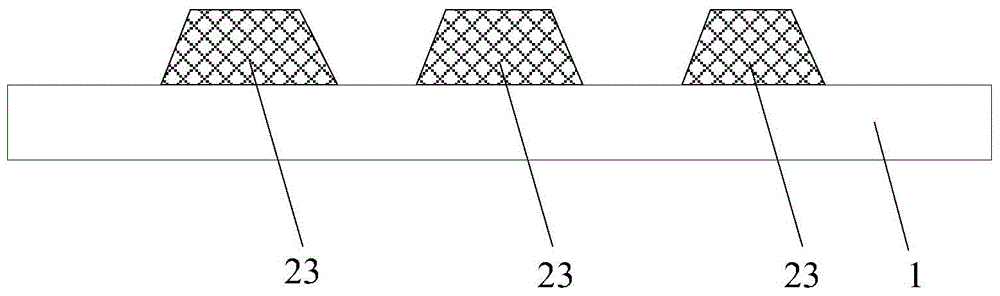

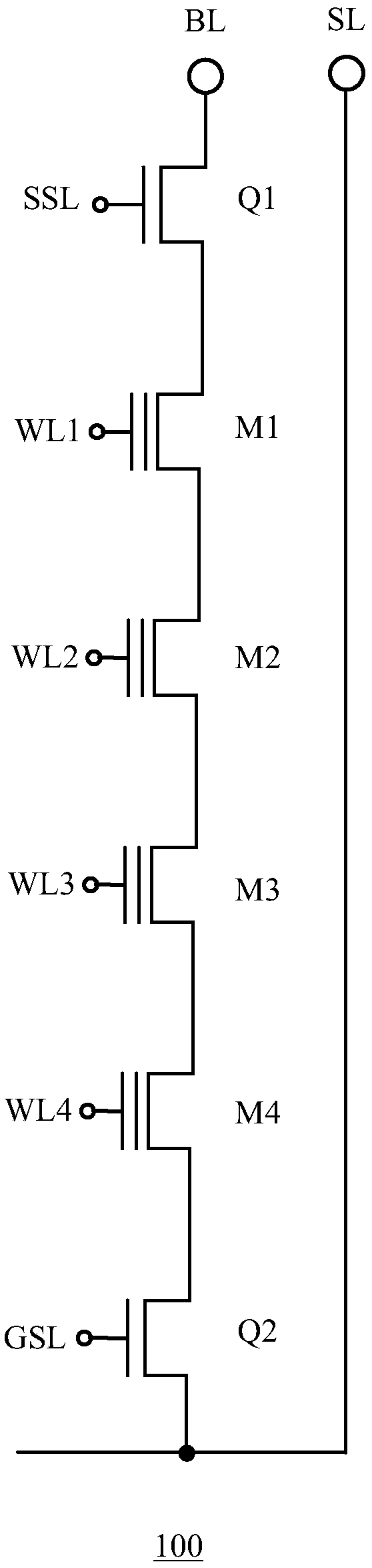

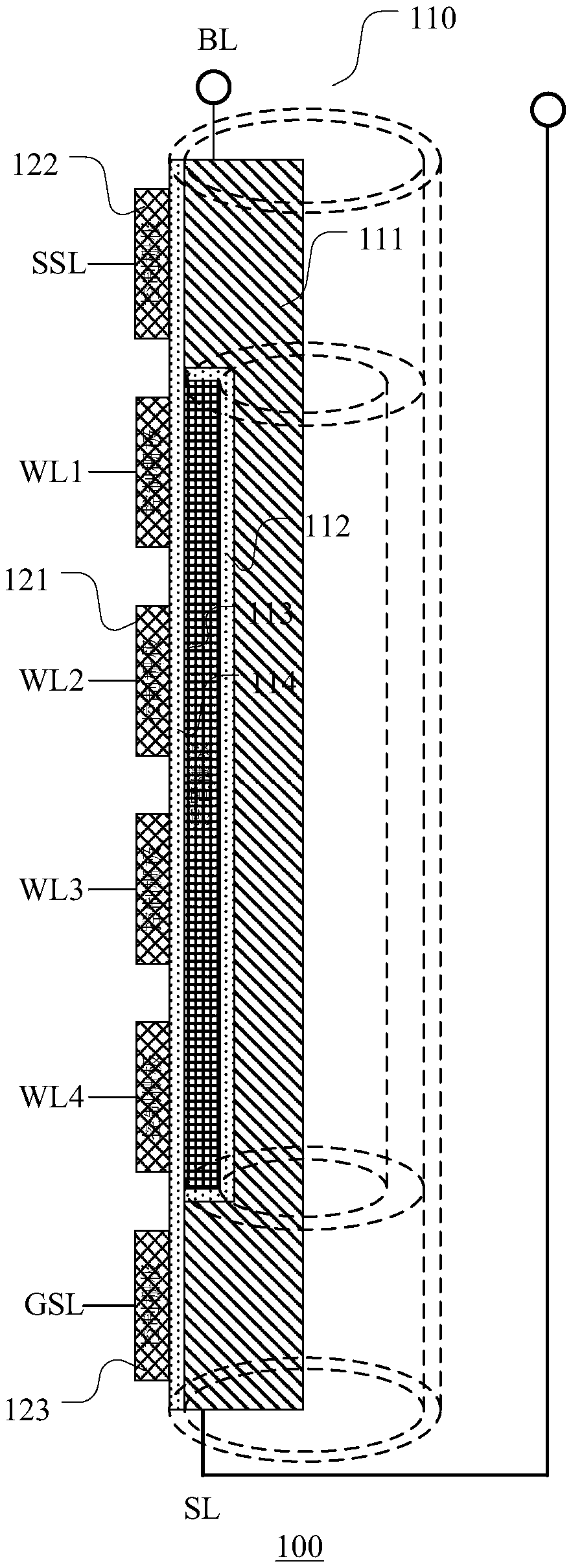

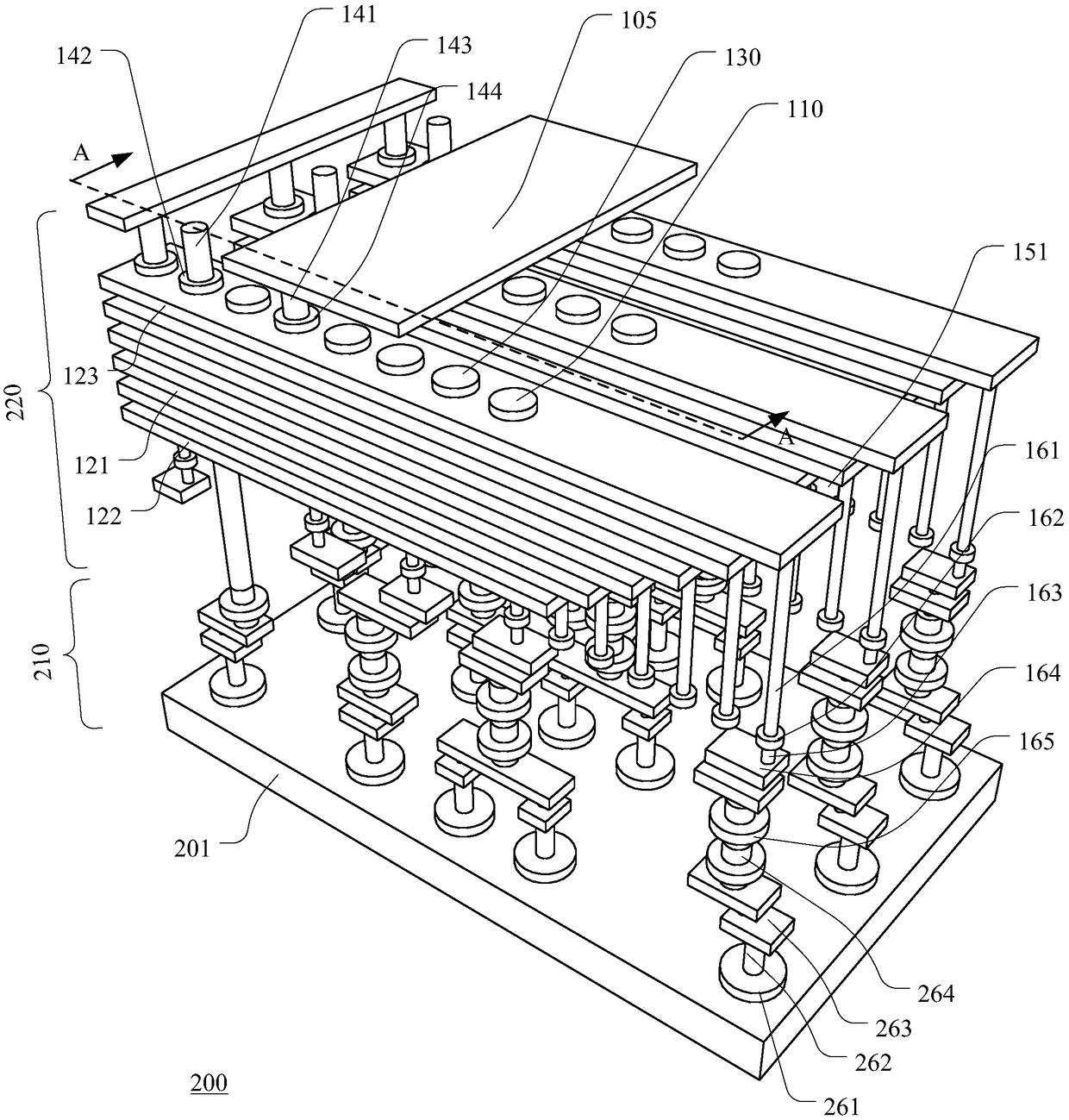

PendingCN109300902AAvoid device damageImprove yield and reliabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringGate stack

The present invention discloses a 3D memory device. The 3D memory device includes a gate stack structure, a plurality of channel pillars, and a plurality of dummy channel pillars; the gate stack structure includes a plurality of gate conductors and a plurality of interlayer insulating layers which are alternately stacked; the plurality of channel pillars penetrate the gate stack structure so as toform a transistor; and the plurality of dummy channel pillars pass through at least some of the gate conductors in the gate stack structure so as to provide support, wherein at least one of the dummychannel pillars is connected with a heat dissipation structure. According to the 3D memory device of the invention, the dummy channel pillars are connected to the heat dissipation structure, so thata heat dissipation path can be provided, and therefore, the yield and reliability of the 3D memory device can be improved.

Owner:YANGTZE MEMORY TECH CO LTD

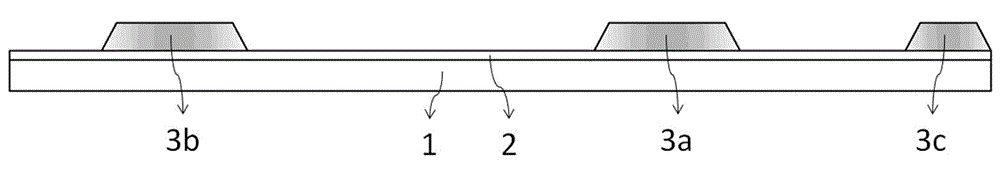

Thin film transistor substrate and method of manufacturing the same

ActiveUS20130228772A1Reduce manufacturing costIncrease the aperture ratioTransistorSolid-state devicesEngineeringElectrode Grid

A thin film transistor substrate includes a substrate; a gate electrode on the substrate; a semiconductor pattern on the gate electrode; a source electrode on the semiconductor pattern; a drain electrode on the semiconductor pattern and spaced apart from the source electrode; a pixel electrode connected to the drain electrode; and a common electrode partially overlapped with the pixel electrode. The semiconductor pattern is in a same layer of the thin film transistor substrate as the pixel electrode and has an electrical property different from an electrical property of the pixel electrode.

Owner:SAMSUNG DISPLAY CO LTD

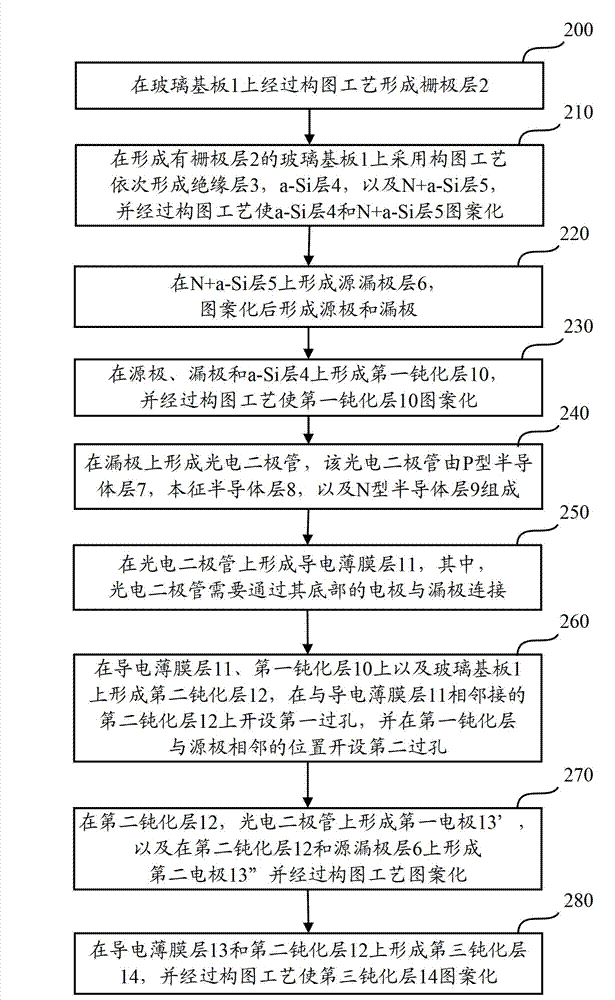

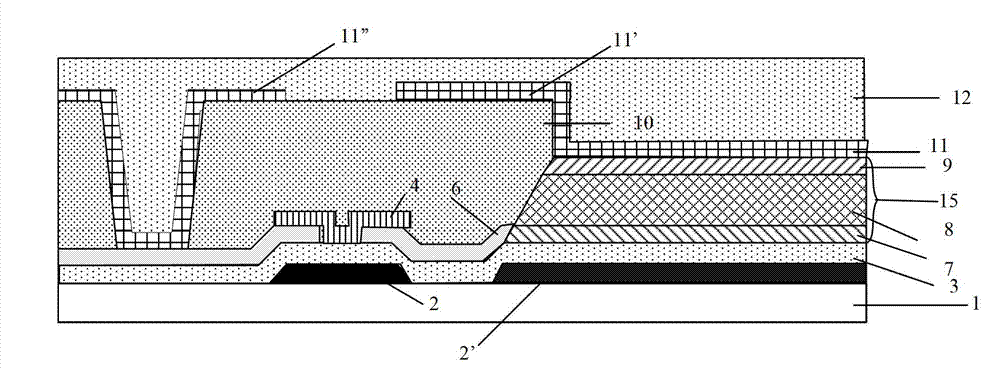

Ray detector and manufacturing method thereof

ActiveCN103165635AHigh sensitivityReduce power consumptionSolid-state devicesRadiation controlled devicesPhotodiodeActive layer

The invention discloses a ray detector and a manufacturing method thereof. A grid layer and an insulating layer are sequentially formed on a substrate, a photoelectric diode and a source drain layer are formed on the substrate with the insulating layer, a drain of the source drain layer is connected with the photoelectric diode, an active layer is formed on the source drain layer and contacts with the insulating layer, a first passivation layer is formed on the active layer and the source drain layer, a conductive film layer is formed on the photoelectric diode, the source drain layer and the first passivation layer, and a second passivation layer is manufactured on the conductive film layer. By the aid of the technical scheme, compared with the prior art, the ray detector has the advantages that masking frequency is decreased, production cycle is effectively shortened, production efficiency is improved, manufacturing cost is reduced, the sensitivity of the ray detector is improved, and power consumption of the ray detector is reduced.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD

3D memory device

ActiveCN109192734AAvoid damageImprove yieldSemiconductor/solid-state device detailsSolid-state devicesGate stackEngineering

A 3D memory device is disclosed. The 3D memory device includes a gate stack structure including a plurality of gate conductors and a plurality of interlayer insulating layers alternately stacked; a plurality of channel posts penetrating the gate stack structure to form a transistor; and a plurality of conductive channels penetrating the gate stack structure to provide electrical connection with aperipheral circuit, wherein at least one conductive channel of the plurality of conductive channels is connected with a heat dissipation structure. As that conductive channel is connected to the heatdissipation structure to provide a heat dissipation path, the yield and reliability of the 3D memory device can be improved.

Owner:YANGTZE MEMORY TECH CO LTD

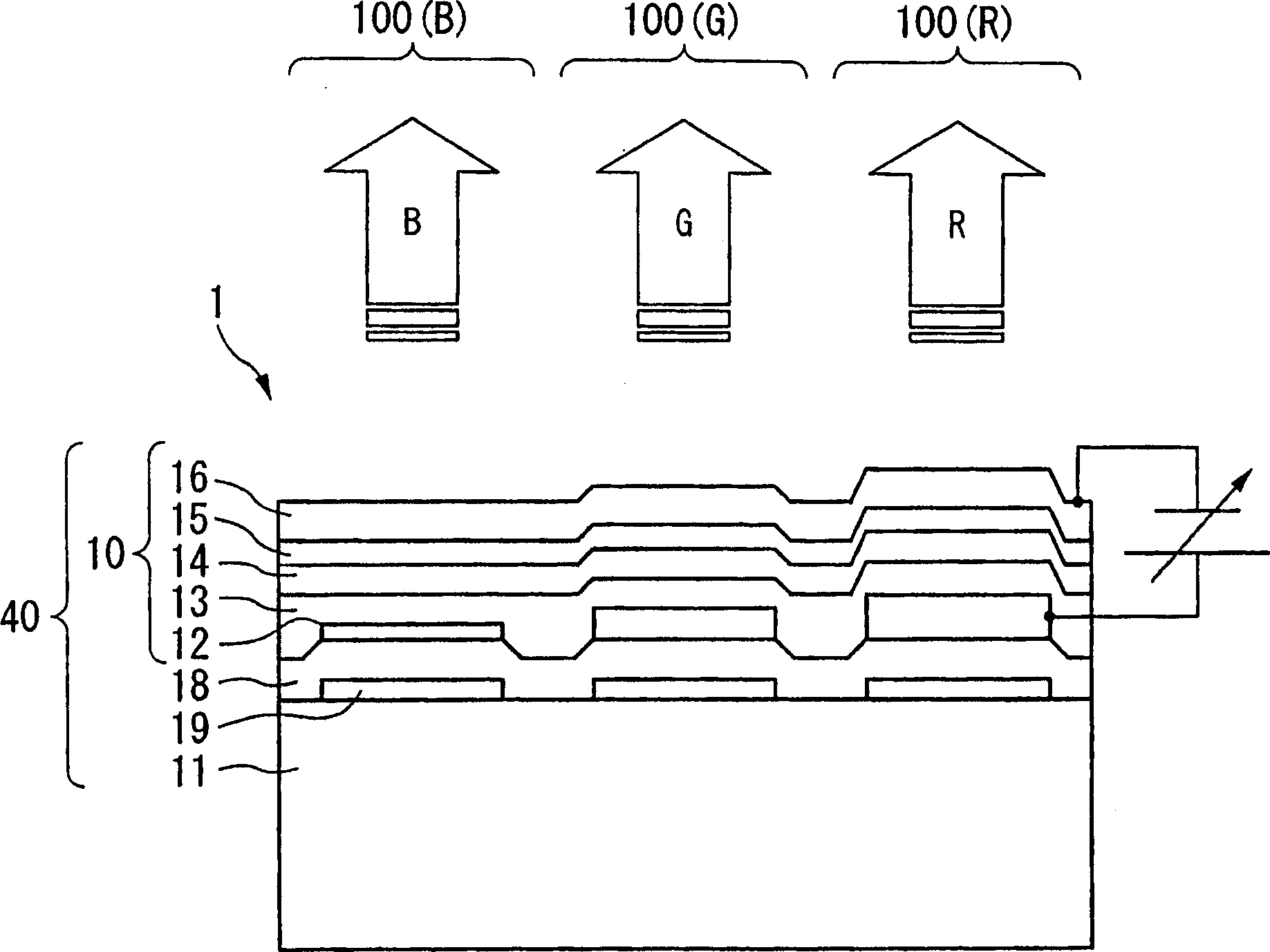

Electroluminescence device, method of manufacturing electroluminescence device, and electronic apparatus

ActiveCN1897252AEasy to manage stepsLow costElectroluminescent light sourcesSolid-state devicesTransparent conducting filmLight emission

Provided is a method of manufacturing an electroluminescence device, in which a plurality of pixel forming regions is formed on a substrate, a light emitting element, in which an anode having a light transmission property, a light emission function layer including at least a light emitting layer and a cathode are laminated, is provided in each of the plurality of pixel forming regions, the pixel forming regions include a pixel forming region of first color and a pixel forming region of second color different from the first color, and the anode includes a first anode formed in the pixel forming region of the first color with a first thickness and a second anode formed in the pixel forming region of the second color with a second thickness, including: forming a first transparent conductive film in the pixel forming region of the first color with a thickness obtained by subtracting the second thickness from the first thickness; and forming a second transparent conductive film in the pixel forming region of the second color with the second thickness.

Owner:SEIKO EPSON CORP

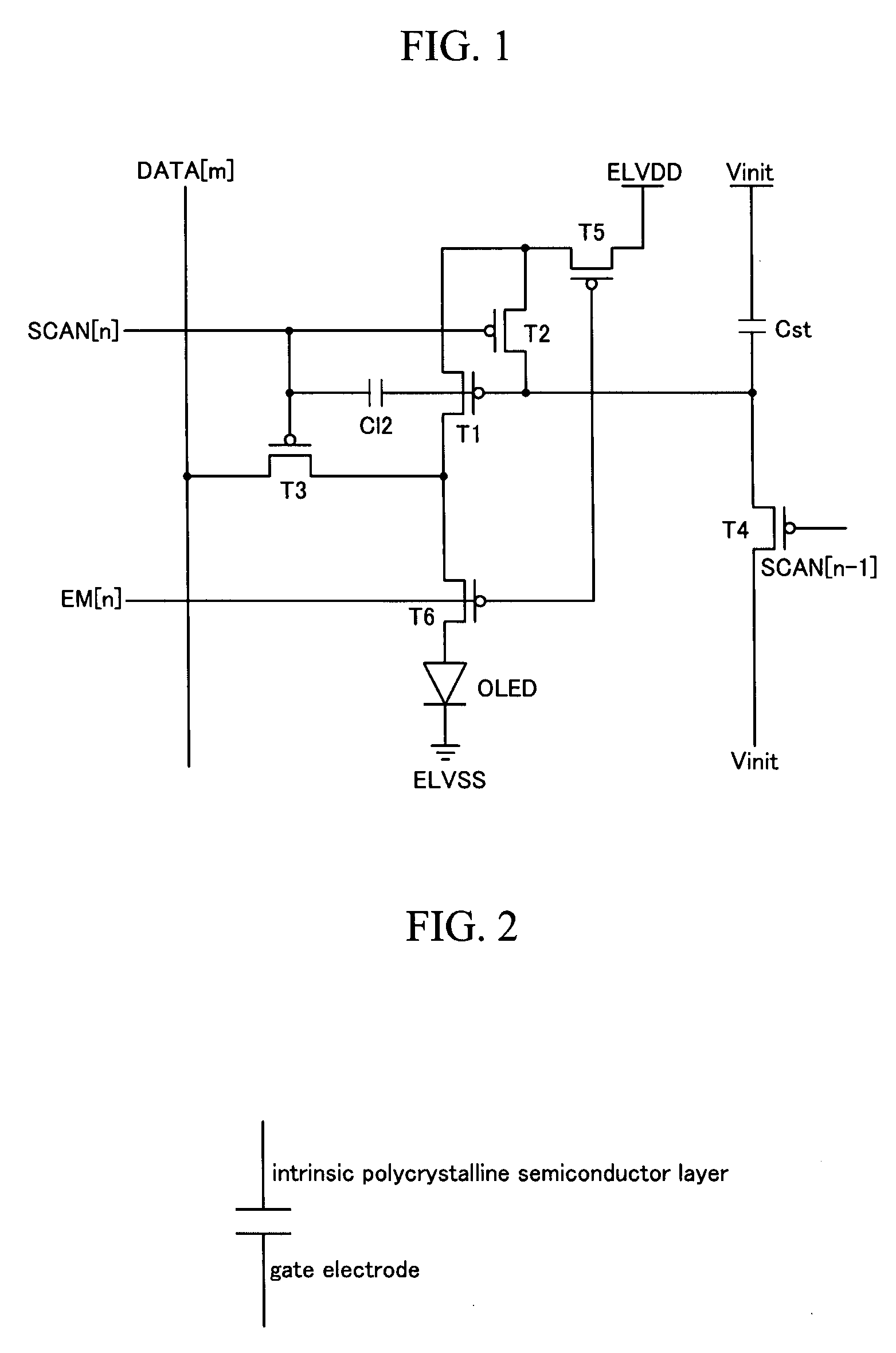

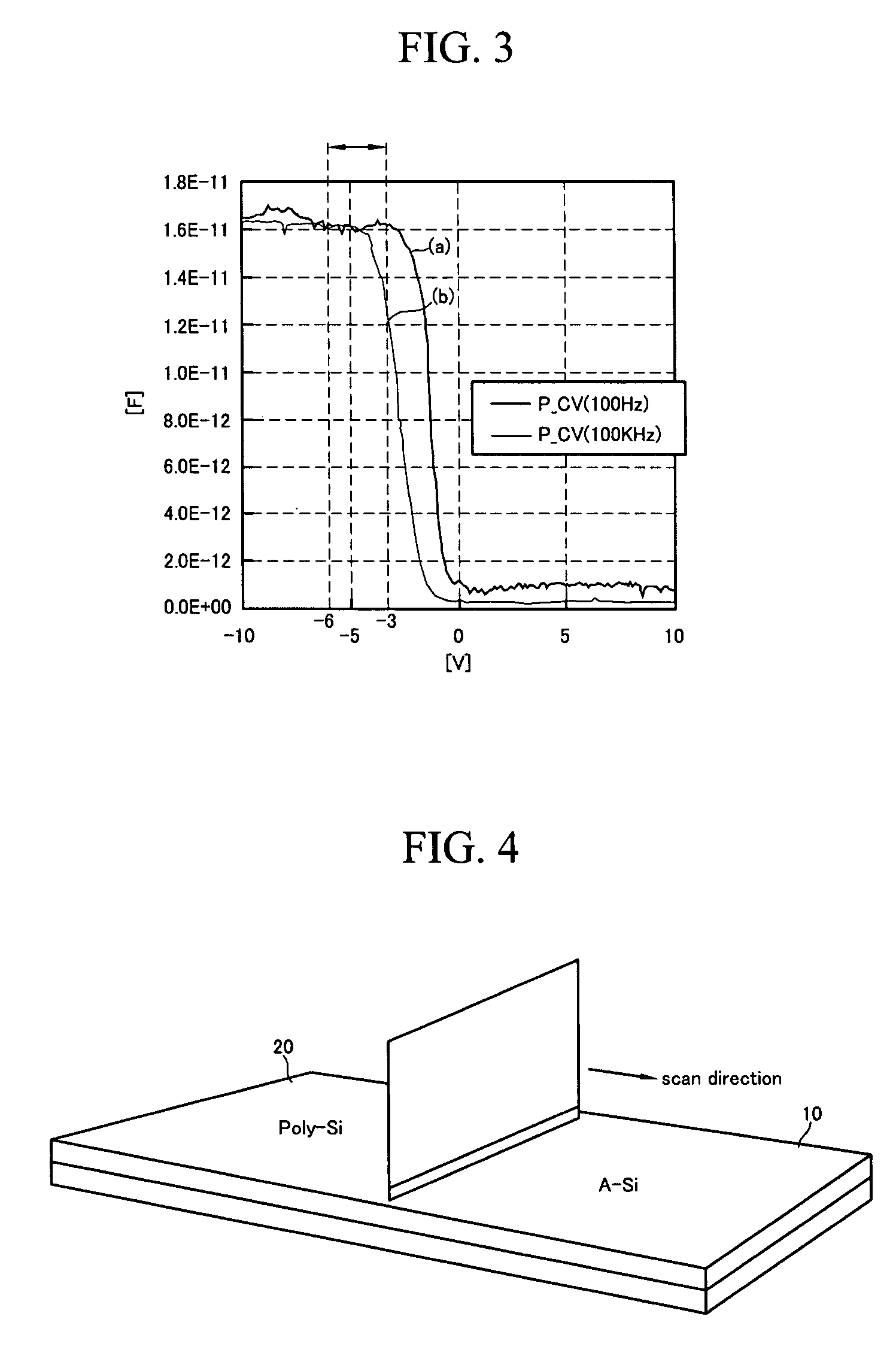

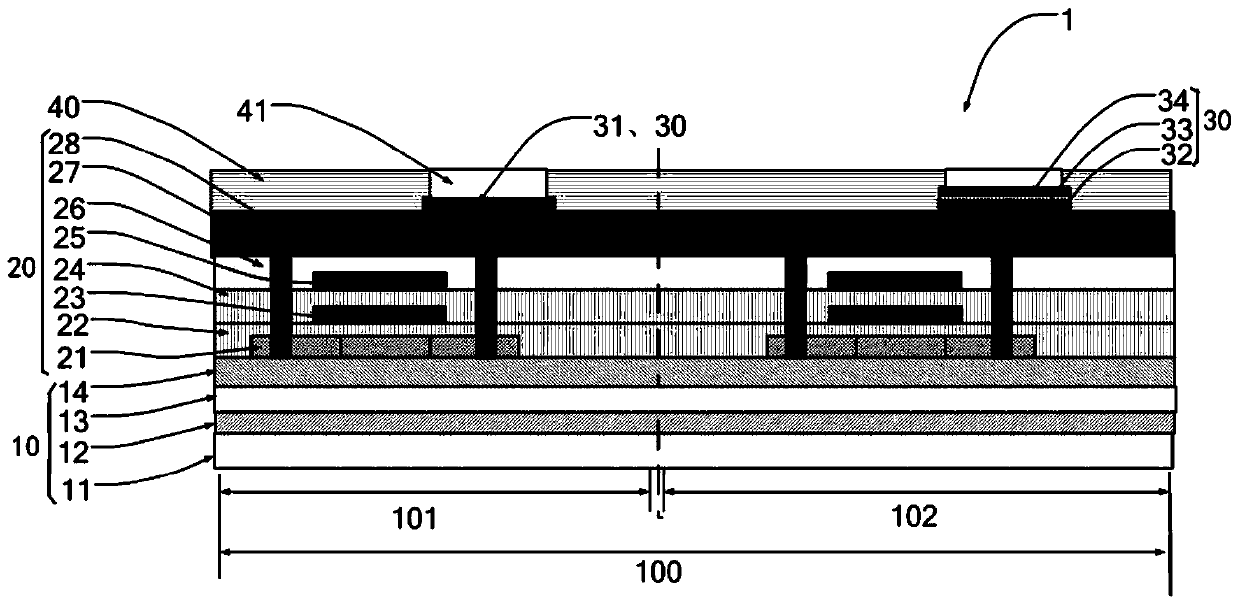

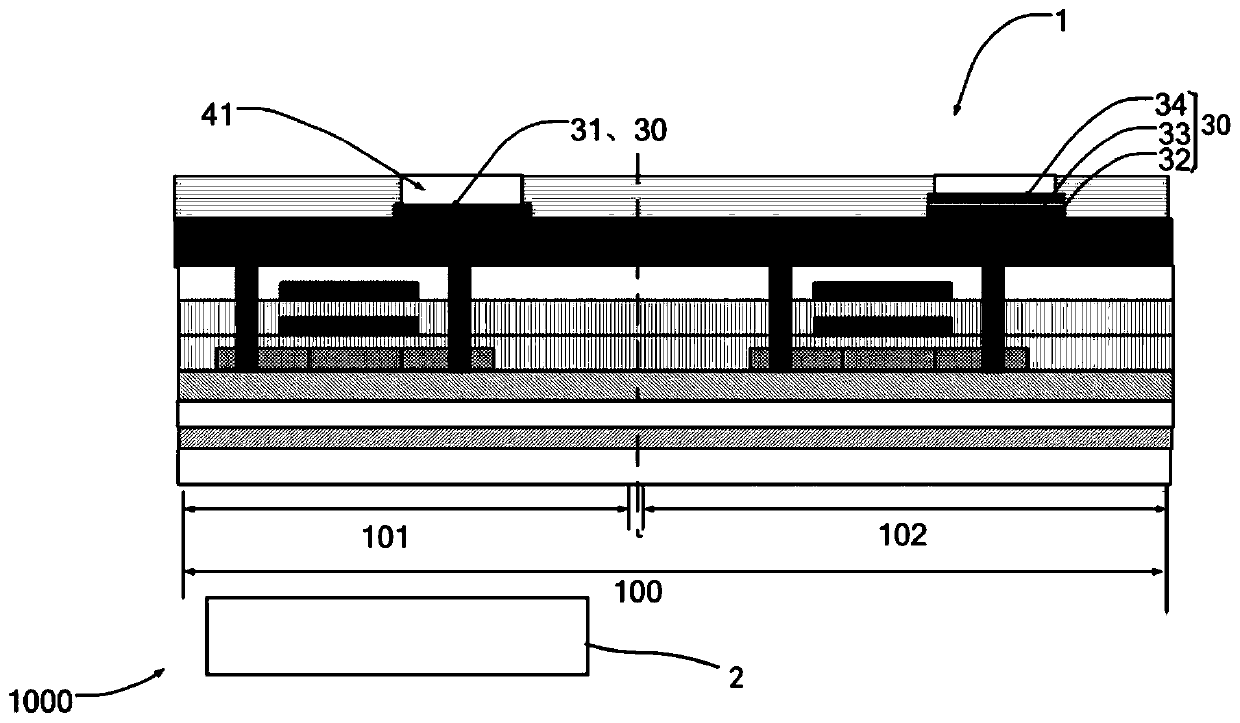

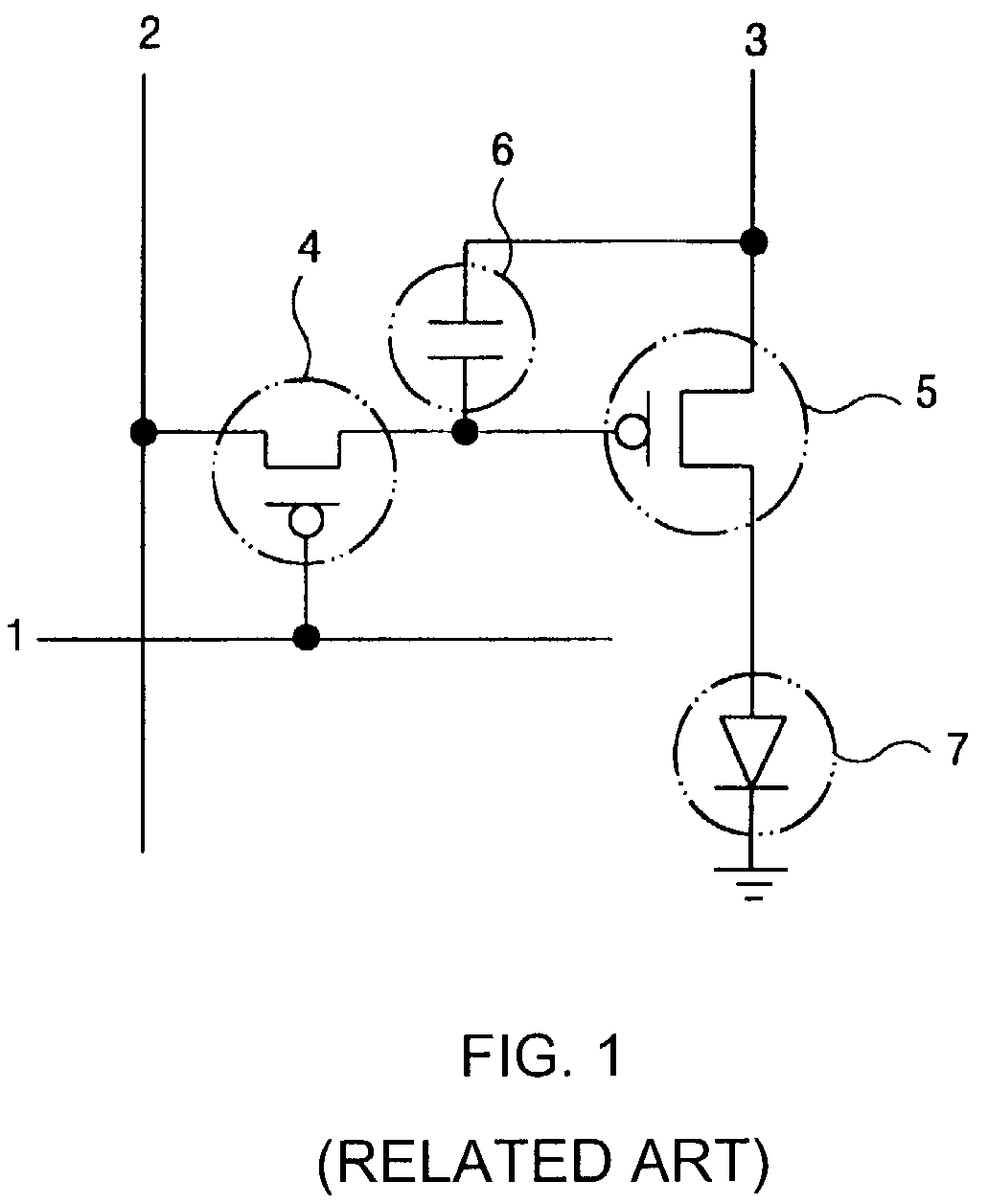

Pixel having intrinsic semiconductor as an electrode and electroluminescent displays employing such a pixel

ActiveUS20080035931A1Reduce processing stepsReduce the number of masksStatic indicating devicesElectroluminescent light sourcesCapacitorTransistor

A pixel employable by a display device, including a plurality of transistors, including a first transistor having a gate electrode, and a capacitor including a first terminal connected to the gate electrode of the first transistor and a second terminal that is an intrinsic semiconductor.

Owner:SAMSUNG DISPLAY CO LTD

Display panel and preparation method thereof and display device

ActiveCN110085766ASimple stepsHigh light transmittanceFinal product manufactureSolid-state devicesTransmittanceDisplay device

The invention discloses a display panel and a preparation method thereof and a display device. The display panel comprises a display area including a transparent display area and a non-transparent display area surrounding the transparent display area. The display panel further comprises an array substrate in the display area. The display panel also comprises a first electrode which is arranged onthe array substrate. The thickness of the first electrode of the transparent display area is less than the thickness of the first electrode of the non-transparent display area, and the transmittance of the first electrode of the transparent display area is greater than or equal to 70%. According to the display panel and the display device, the transmittance of the transparent display area can be effectively increased. The preparation method of the display panel has simple steps and can reduce the number of times of using the light mask and the number of the light mask and effectively improvesthe production efficiency.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

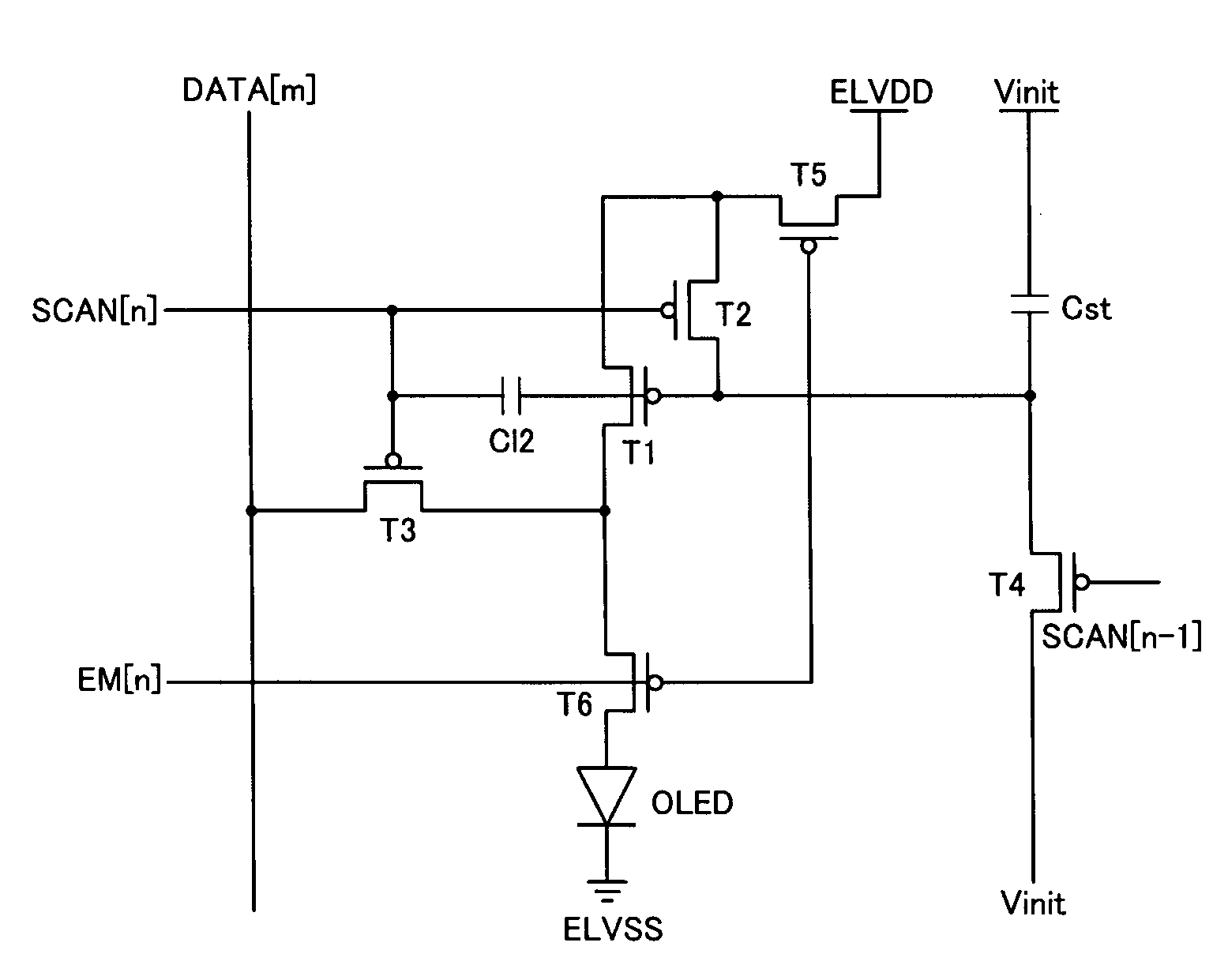

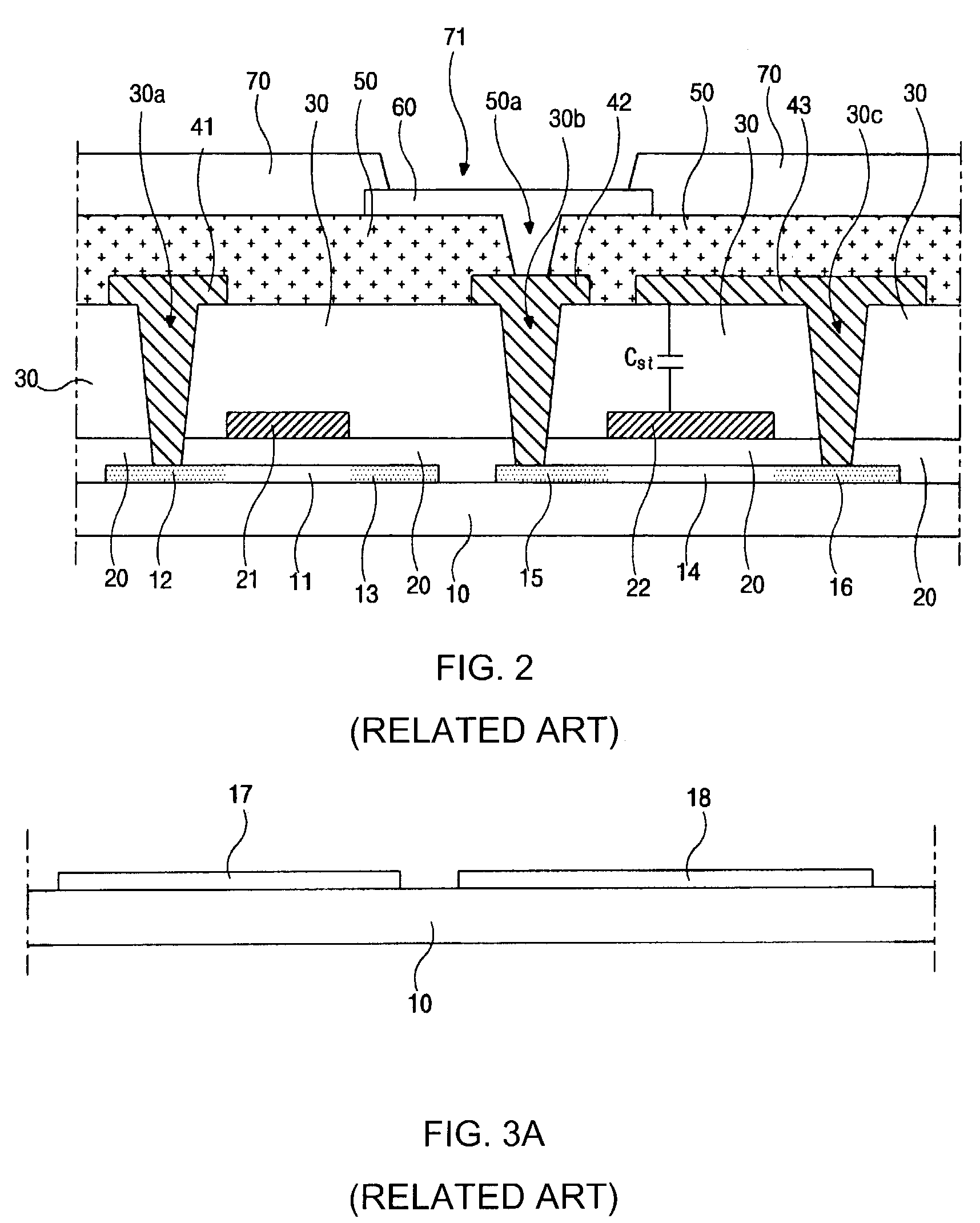

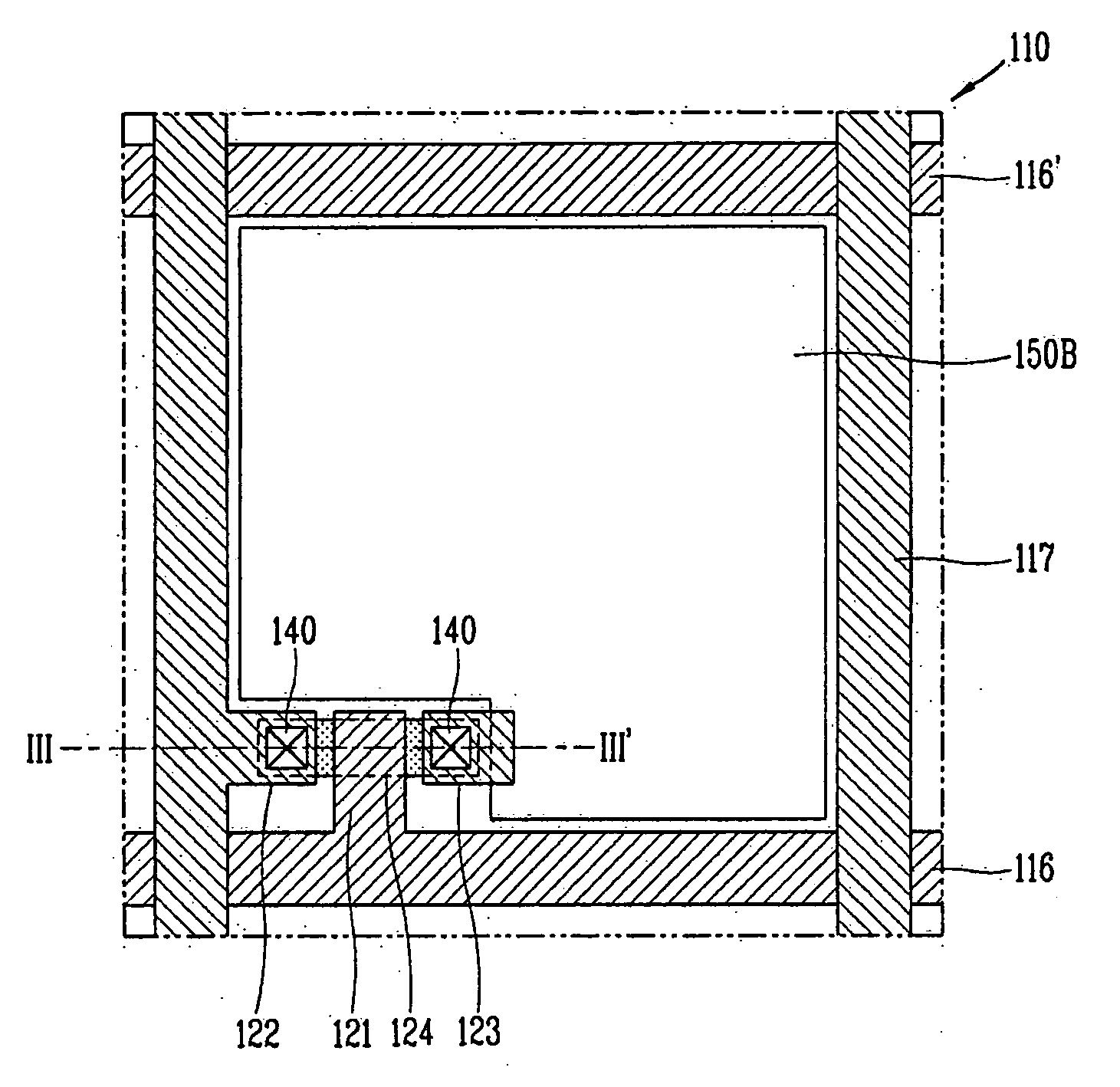

Active matrix organic electro luminescence display device and manufacturing method for the same

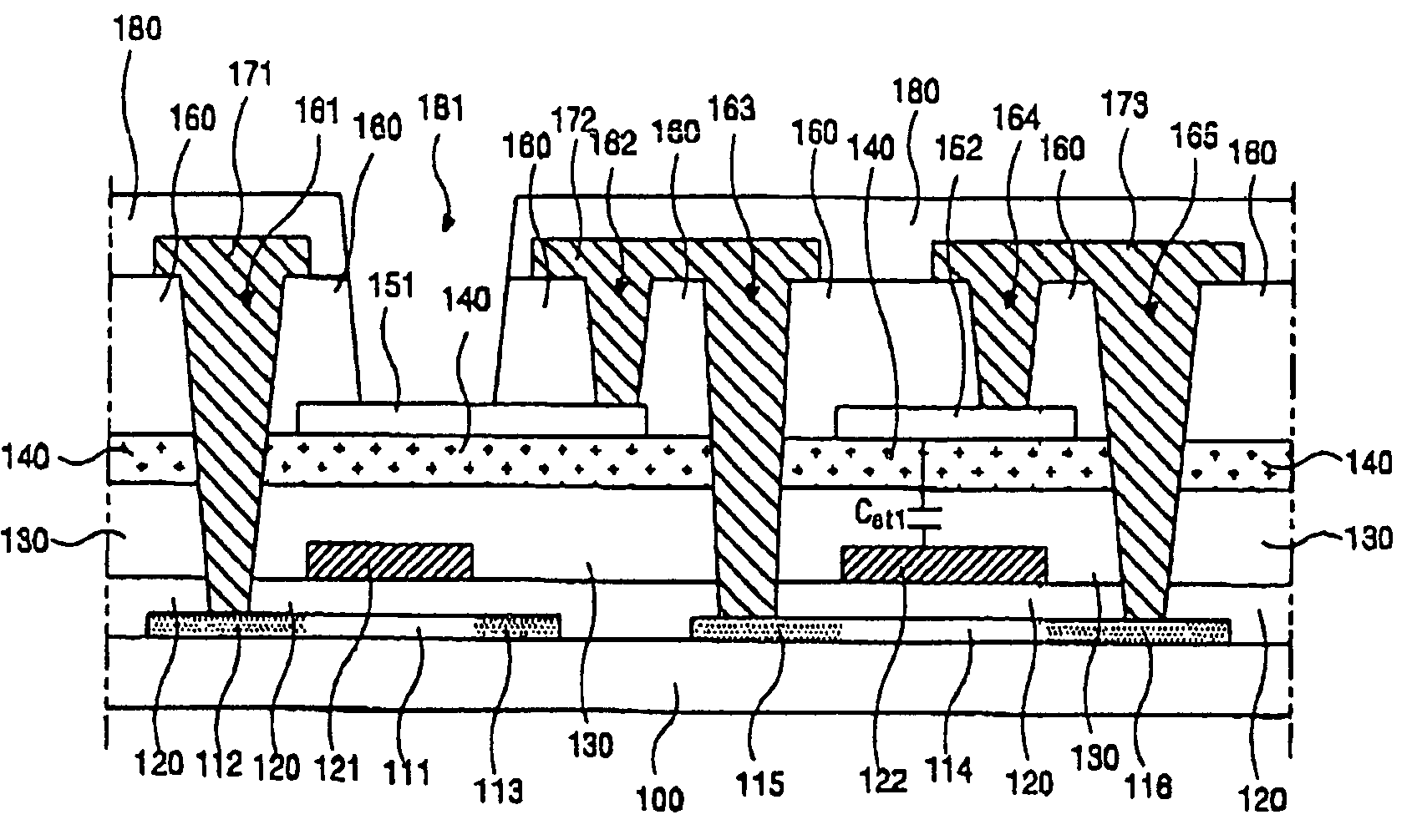

InactiveUS7227184B2Reduce aperture ratioStorage capacitance is increasedTransistorElectroluminescent light sourcesInter layerActive matrix

An active matrix organic electro luminescent display (ELD) device comprises a substrate, first and second active layers formed of polycrystalline silicon on the substrate, first source and drain regions and second source and drain regions, the first source and drain regions neighboring the first active layer and the second source and drain regions neighboring the second active layer, a gate insulating layer on the first and second active layers, first and second gate electrodes on the gate insulating layer, a first inter layer on the first and second gate electrodes, an anode electrode and a capacitor electrode on the first inter layer, a first passivation layer on the anode electrode and the capacitor electrode, a power line on the first passivation layer, first source and drain electrodes on the first passivation layer, the first source electrode being connected to the first source region and the first drain electrode being connected to the first drain region, second source and drain electrodes on the first passivation layer, the second source electrode being connected to the second source region, the power line and the capacitor electrode and the second drain electrode being connected to the second drain region and the anode electrode, and a second passivation layer on the first source and drain electrodes and the second source and drain electrodes, the second passivation layer having a bank that exposes the anode electrode.

Owner:LG DISPLAY CO LTD

Liquid crystal display device and fabrication method thereof

InactiveUS20060051886A1Reduce the number of masksReduce in quantitySolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerLiquid-crystal display

A method for fabricating a liquid crystal display device includes providing first and second substrates; forming an active layer on the first substrate, wherein the active layer includes a source region, a drain region, a channel region, and a storage region; forming a first insulation layer on the first substrate; forming a gate electrode, a gate line, a pixel electrode, and a storage line on the first substrate, wherein storage line overlaps the storage region; forming a second insulation layer on the first substrate; forming first and second contact holes through the first and second insulation layers, wherein the first and second contact holes expose respective ones of the source and drain regions; forming a pixel hole through the second insulation layer, wherein the pixel hole exposes the pixel electrode; forming a source electrode electrically connected to the source region through the first contact hole and a drain electrode electrically connected to the drain region through the second contact hole; and forming a liquid crystal layer between the first and second substrates.

Owner:LG DISPLAY CO LTD

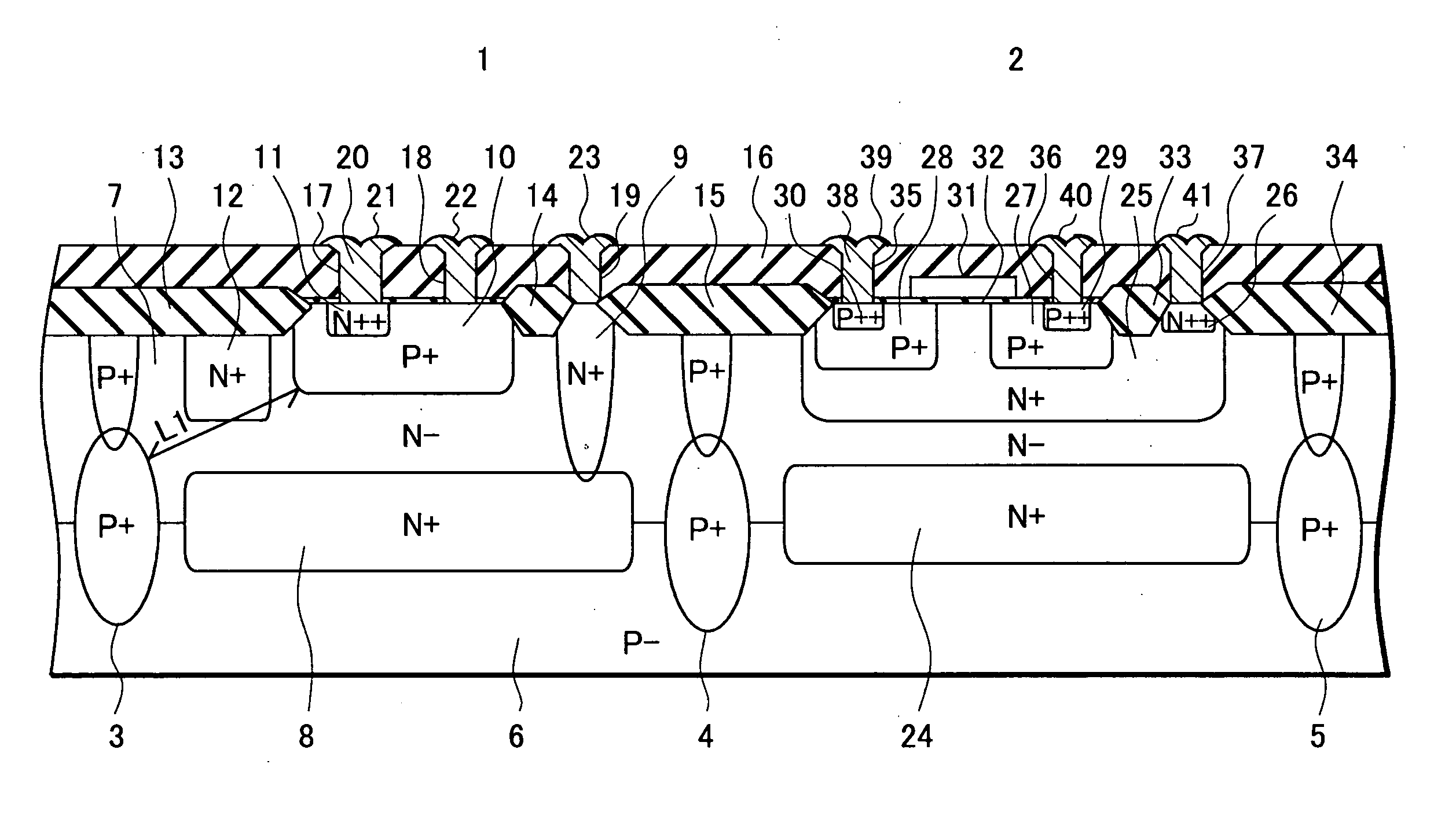

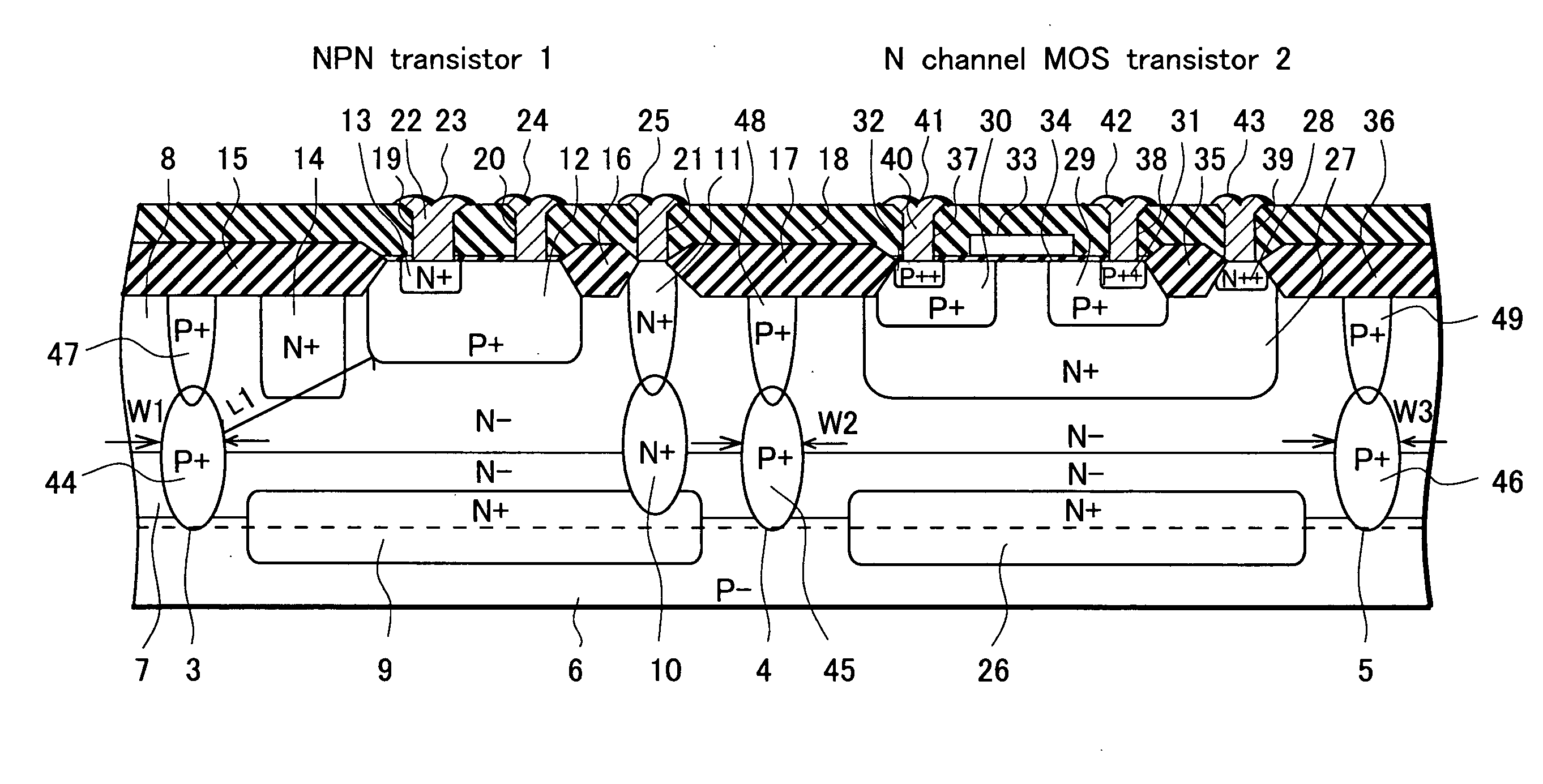

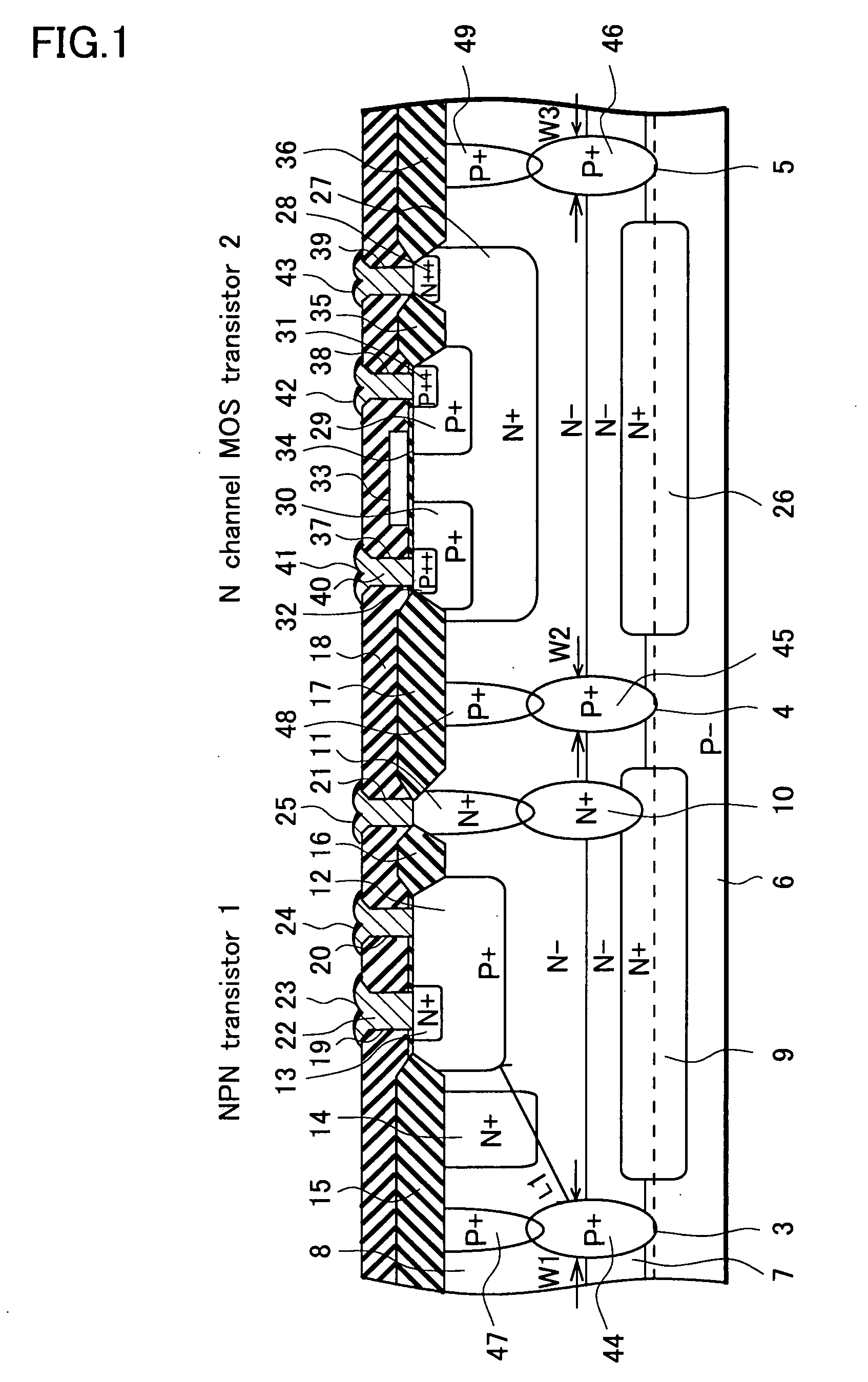

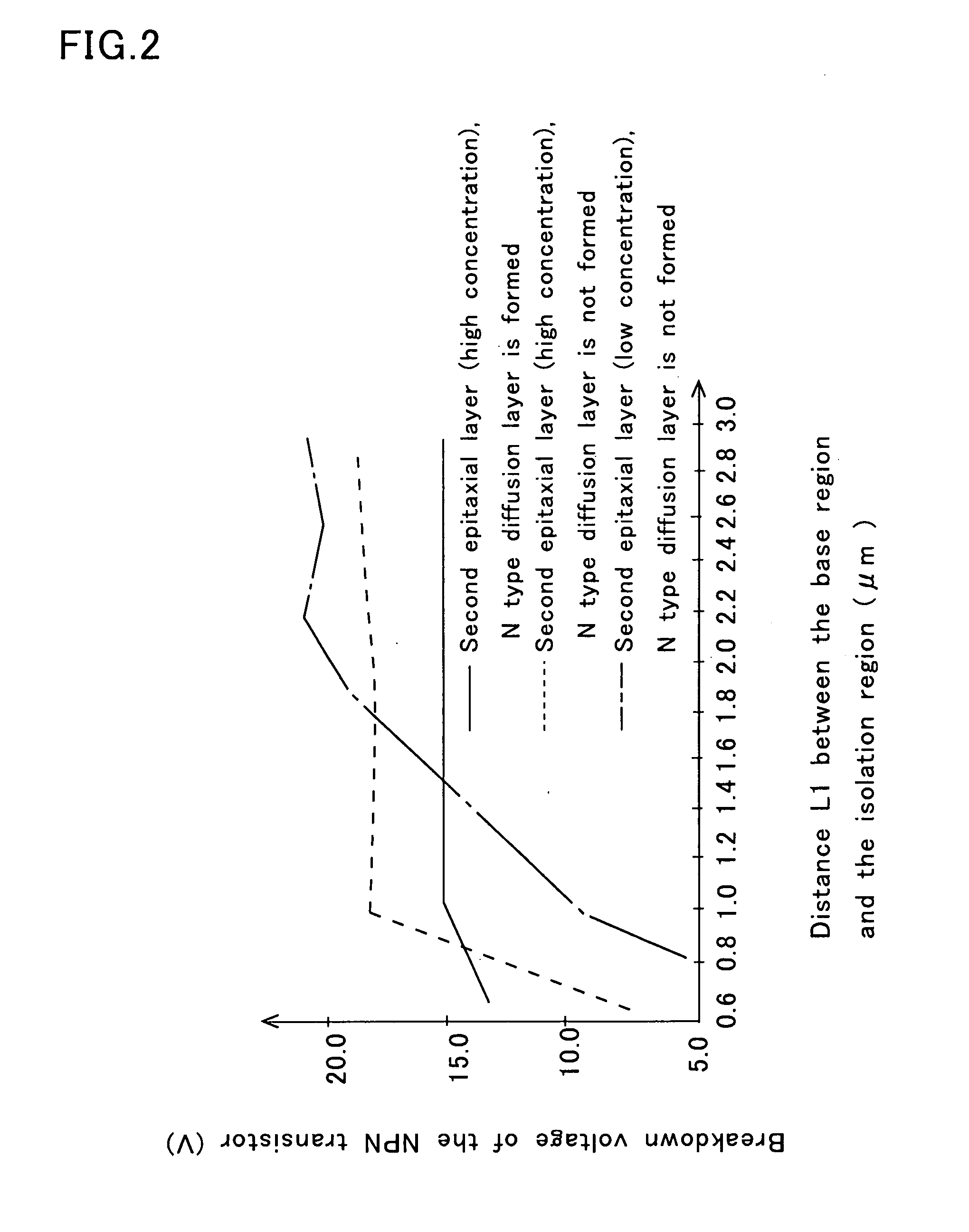

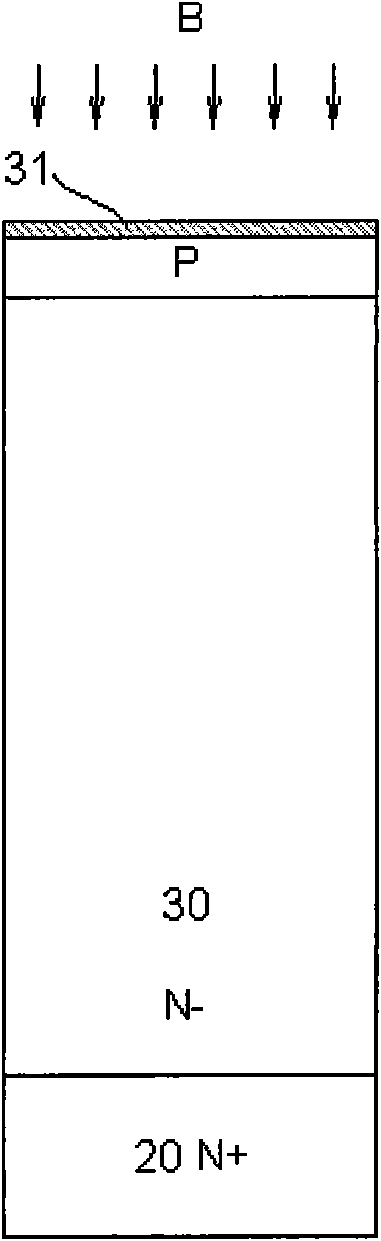

Semiconductor device and method of manufacturing the same

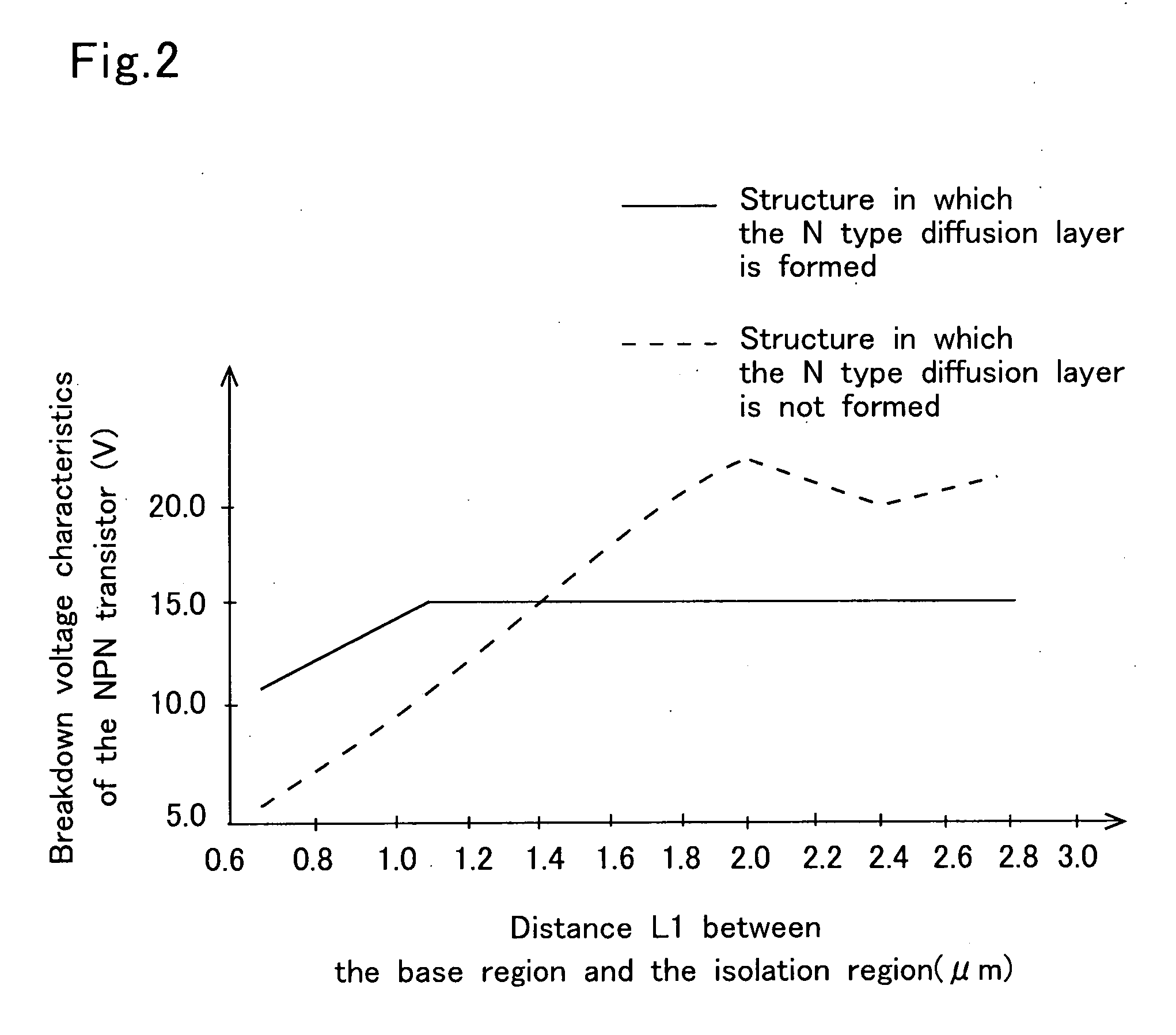

ActiveUS20070145530A1Improve breakdown voltageImproved breakdown voltage characteristicsTransistorSemiconductor/solid-state device manufacturingDevice materialSemiconductor

In a semiconductor device of the present invention, an epitaxial layer is formed on a P type single crystal silicon substrate. Isolation regions are formed in the epitaxial layer, and are divided into a plurality of element formation regions. An NPN transistor is formed in one of the element formation regions. An N type diffusion layer is formed between a P type isolation region and a P type diffusion layer which is used as a base region of the NPN transistor. This structure makes the base region and the isolation region tend not to be short-circuited. Hence, the breakdown voltage characteristics of the NPN transistor can be improved.

Owner:SEMICON COMPONENTS IND LLC

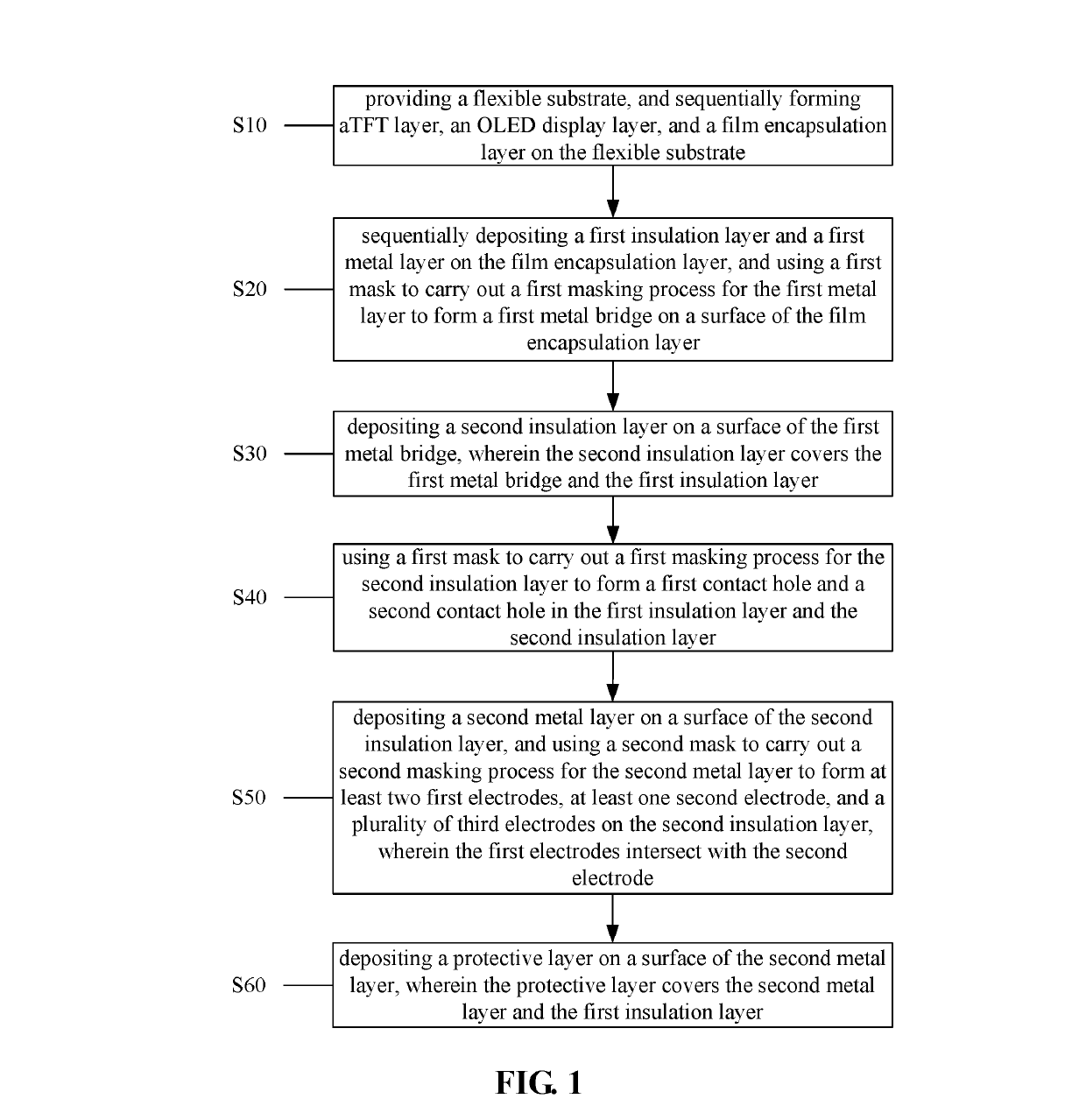

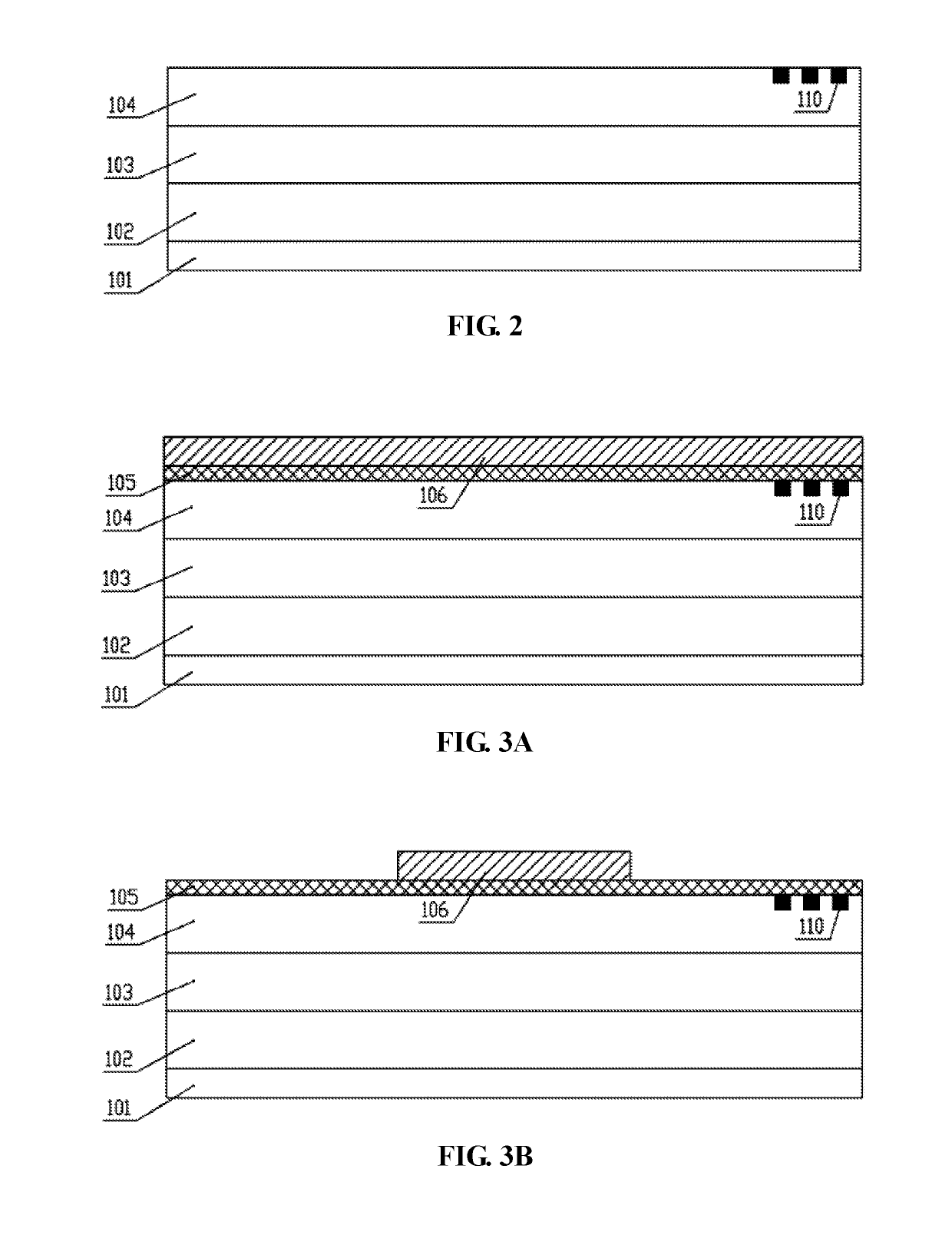

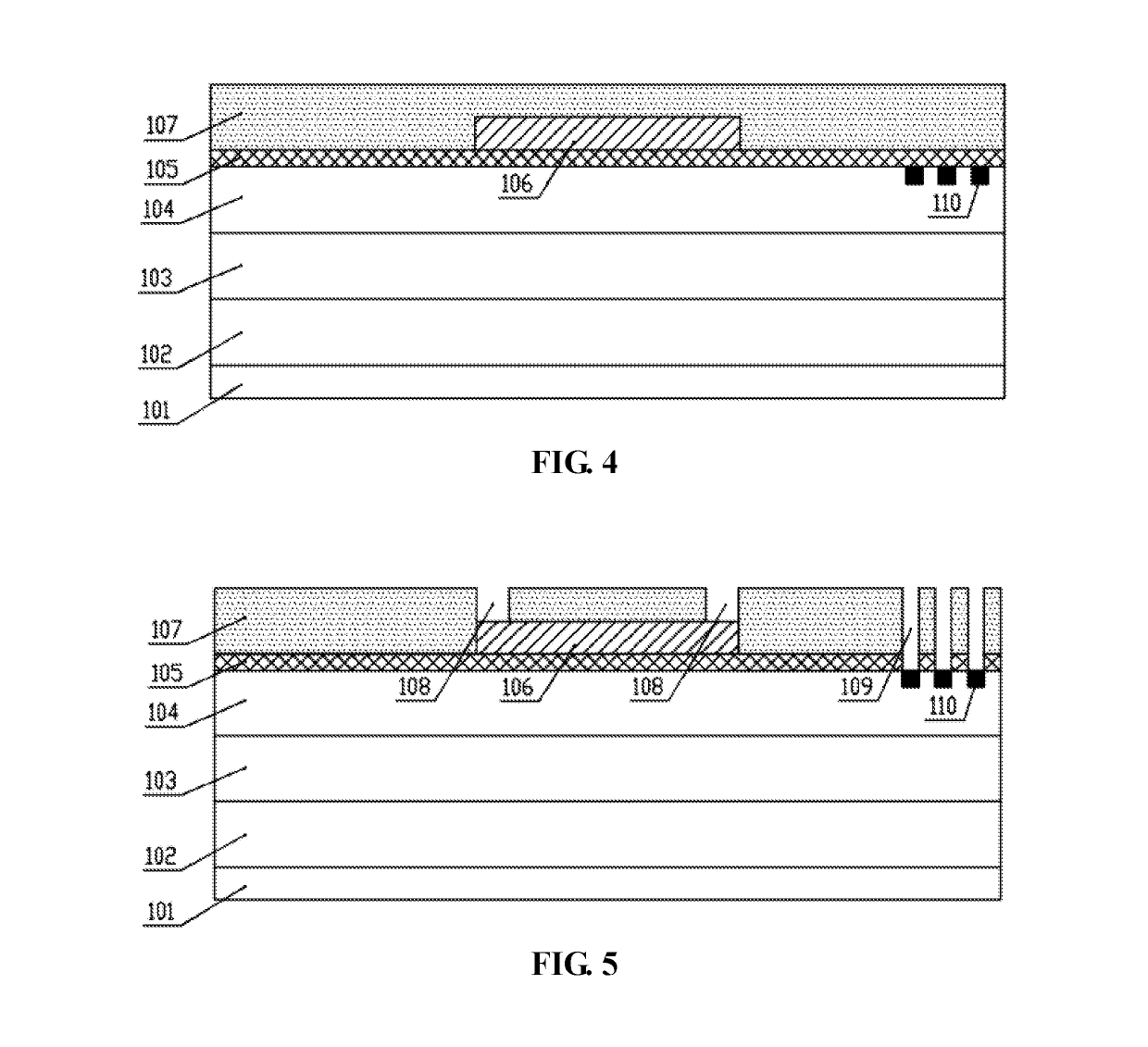

Method for manufacturing flexible touch control display screen

ActiveUS20190165327A1Reduce the number of masksSimple manufacturing processSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerTransmittance

The present disclosure provides a method for manufacturing a flexible touch control display screen. A TFT layer, an OLED display layer, and a film encapsulation layer are sequentially formed on the substrate. A first insulation layer, a first metal bridge, a second insulation layer, a second metal layer, and a protective layer are sequentially formed on the film encapsulation layer. By patterning the first photoresist layer with the use of a multi-transmittance mask, a first contact hole and a second contact hole having different depths are formed in the insulation layer.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

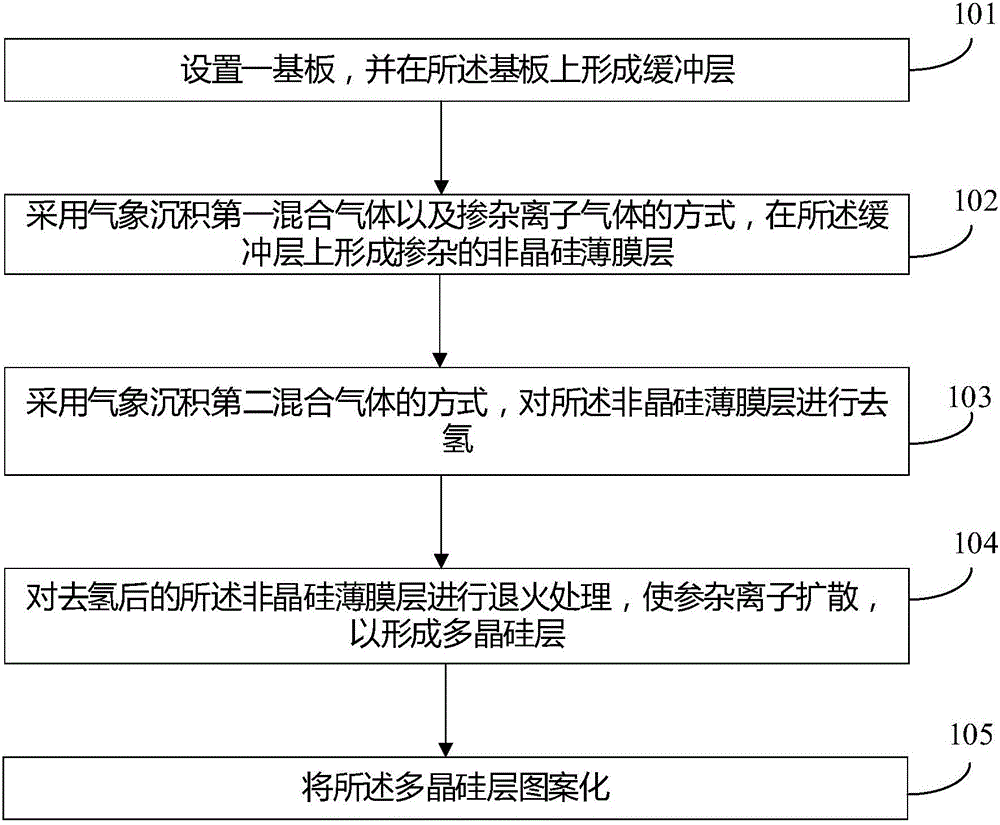

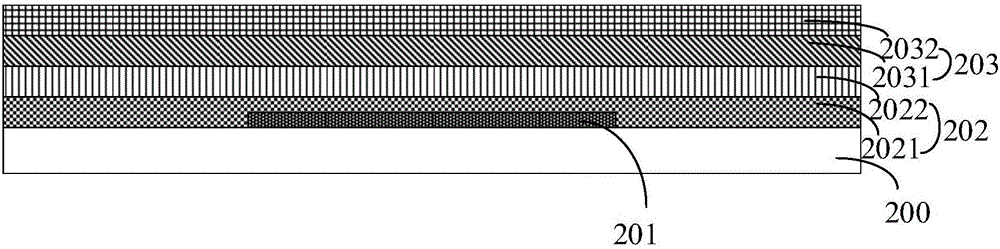

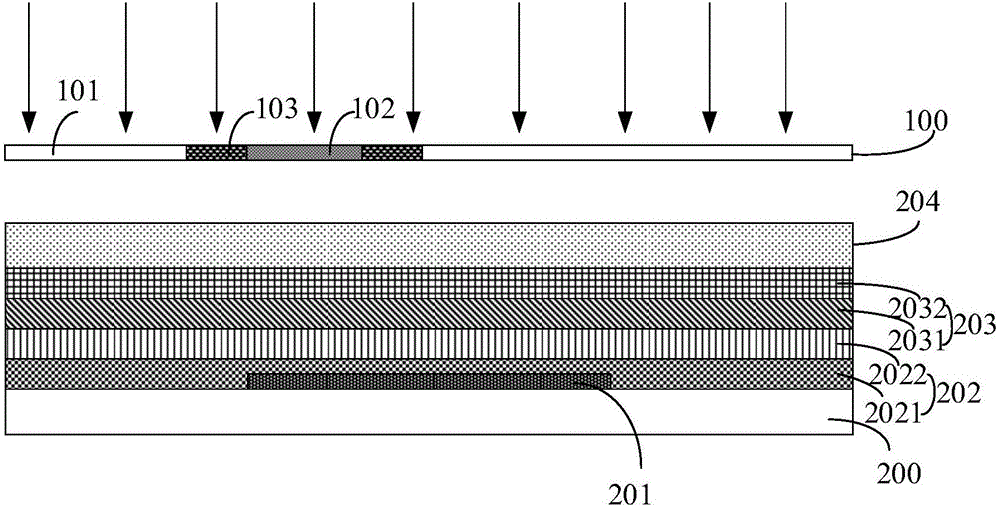

Fabrication method of low temperature poly-silicon array substrate, array substrate and display panel

InactiveCN106328586AImprove electrical performanceSimplify the procedure of introducing gasSolid-state devicesSemiconductor/solid-state device manufacturingHydrogenThin membrane

The invention discloses a fabrication method of a low temperature poly-silicon array substrate, the array substrate and a display panel. The fabrication method comprises the steps of arranging a substrate, and forming a buffer layer on the substrate; forming a doped amorphous silicon film layer on the buffer layer by a mode of vapor deposition of a first mixed gas and a doped ion gas; dehydrogenizing the amorphous silicon film layer by a mode of vapor deposition of a second mixed gas; annealing the dehydrogenized amorphous silicon film layer so that doped ions are diffused to form a poly-silicon layer; and patterning the poly-silicon layer. By the fabrication method, the fabrication process of the low temperature poly-silicon array substrate can be effectively reduced, the investment of fabrication equipment is reduced, and the fabrication cost is further reduced.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

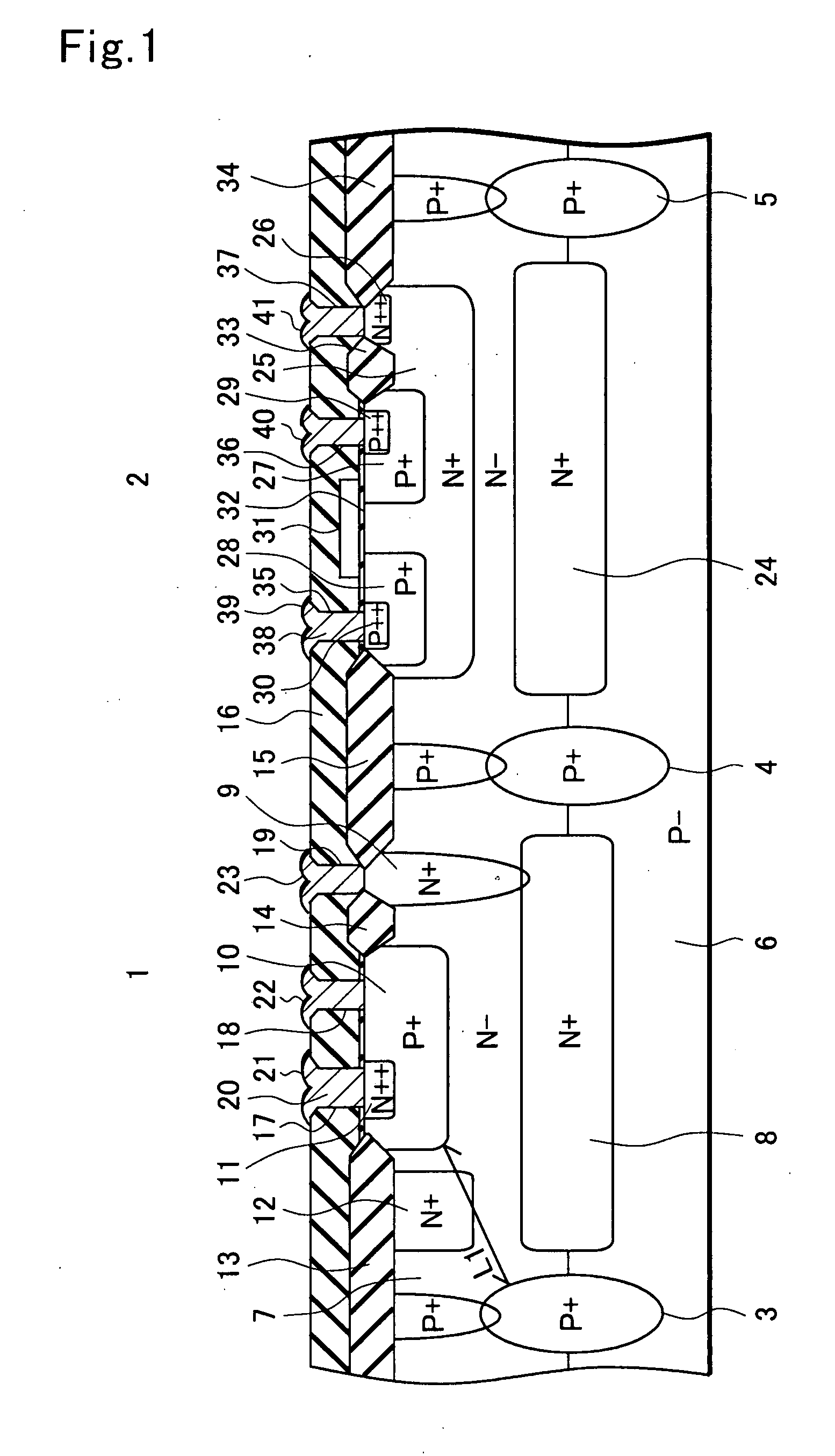

Semiconductor device and manufacturing method of the same

InactiveUS20070145520A1Improved breakdown voltage characteristicsDifficulty occurTransistorSemiconductor/solid-state device manufacturingDevice materialSemiconductor

In a semiconductor device of the present invention, two epitaxial layers are formed on a P type single crystal silicon substrate. One of the epitaxial layers has an impurity concentration higher than that of the other epitaxial layer. The epitaxial layers are divided into a plurality of element formation regions by isolation regions. In one of the element formation regions, an NPN transistor is formed. Moreover, between a P type diffusion layer, which is used as a base region of the NPN transistor, and a P type isolation region, an N type diffusion layer is formed. Use of this structure makes it hard for a short-circuit to occur between the base region and the isolation region. Thus, the breakdown voltage characteristics of the NPN transistor can be improved.

Owner:SEMICON COMPONENTS IND LLC

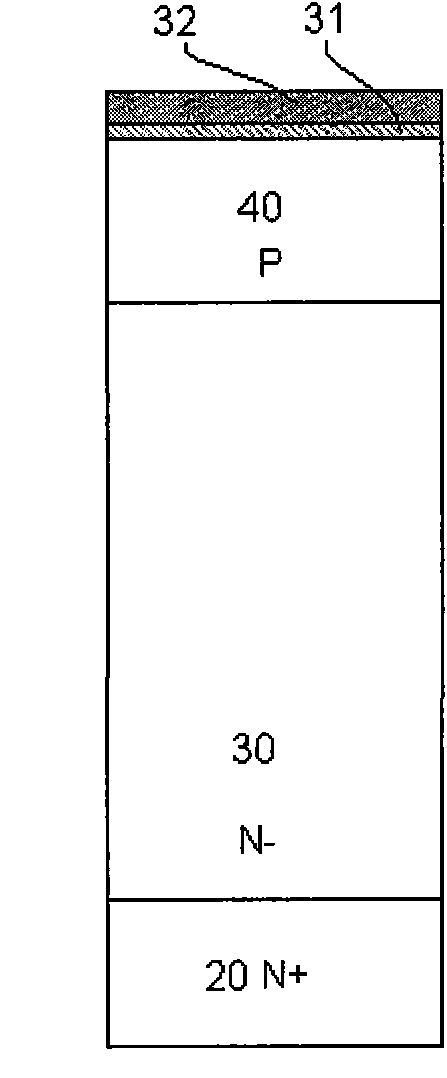

Manufacturing technology of groove MOSFET device with masking films of decreased number

InactiveCN101673685AReduce the number of masksSemiconductor/solid-state device manufacturingTrench mosfetPolycrystalline silicon

The invention relates to a manufacturing technology of a groove MOSFET device with masking films of a decreased number, which is characterized by comprising the following steps: selecting a substratematerial; growing an epitaxial layer on the substrate material; forming a trap area; forming a groove; growing a gate oxide in an oxidizing way; depositing polysilicon, and sculpturing the polysilicon; forming an N+ area. depositing an isolation medium layer; sculpturing a contact hole, and forming a P+ area; depositing a metal layer, and then photoengraving and sculpturing metal, thus the numberof the masking films of the produced groove MOSFET device is decreased to four.

Owner:KEDA SEMICON

Manufacturing method of array substrate of semi-reflection semi-penetration liquid crystal display

ActiveCN1869781ASmall footprintIncrease brightnessSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusCapacitanceLiquid-crystal display

A method for preparing array base plate of semireflection-semitransmission liquid crystal display includes forming transparent conductive layer, the first metal layer, the first protective layer and the second metal layer in sequence on substrate then forming a dielectric layer on substrate; removing off dielectric layer and second metal layer as well as the first protective layer at certain positions to form a channel region above dielectric layer; forming the third metal layer and the second protective layer on base plate; defining three said metal layers and two protective layers as well as transparent layer in following their forming process correspondingly.

Owner:AU OPTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com