Manufacturing technology of groove MOSFET device with masking films of decreased number

A manufacturing process and trench technology, applied in the field of semiconductor device manufacturing, can solve problems such as device defects and achieve the effect of reducing the number of masks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] Embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0039] Refer to the following Figure 1 to Figure 13 A preferred example described further illustrates the trench MOSFET manufacturing method of the present invention, so as to better understand the present invention and its advantages.

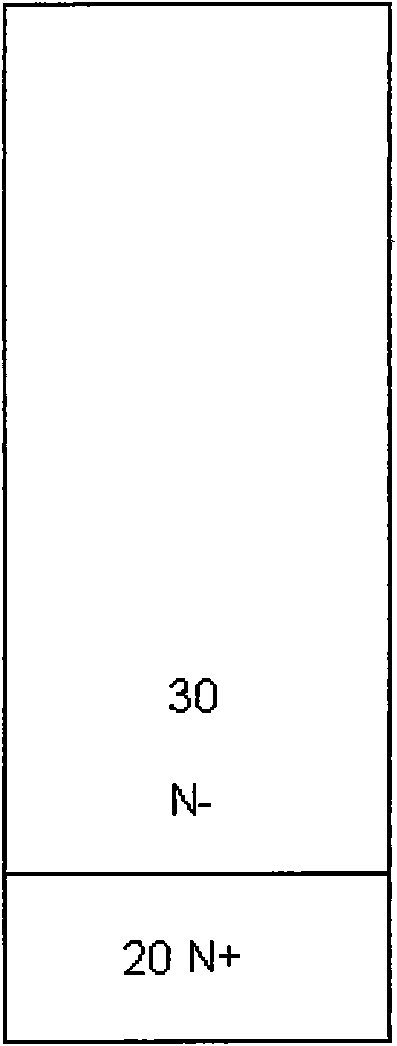

[0040] figure 1 Shown is a schematic of a pristine silicon wafer. exist figure 1 Among them, the original silicon wafer substrate 20 can adopt N+(100) crystal orientation, the resistivity is 0.001~0.002ohm*cm, and the epitaxial layer 30N-silicon polished wafer with resistivity 0.1~10ohm*cm;

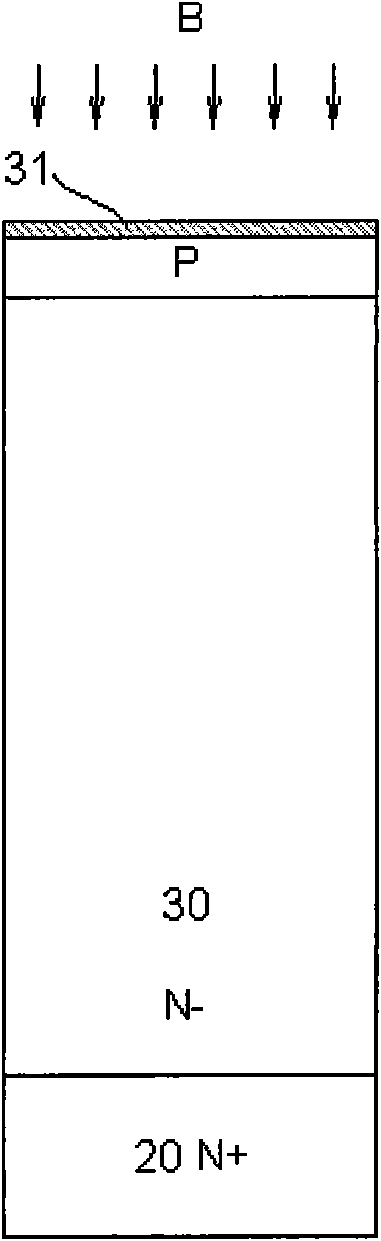

[0041] First, an oxide layer 31 of about 200-800 Å is grown on the silicon material as a pre-implantation oxide layer; then, boron is implanted into the entire silicon wafer. Such as figure 2 shown.

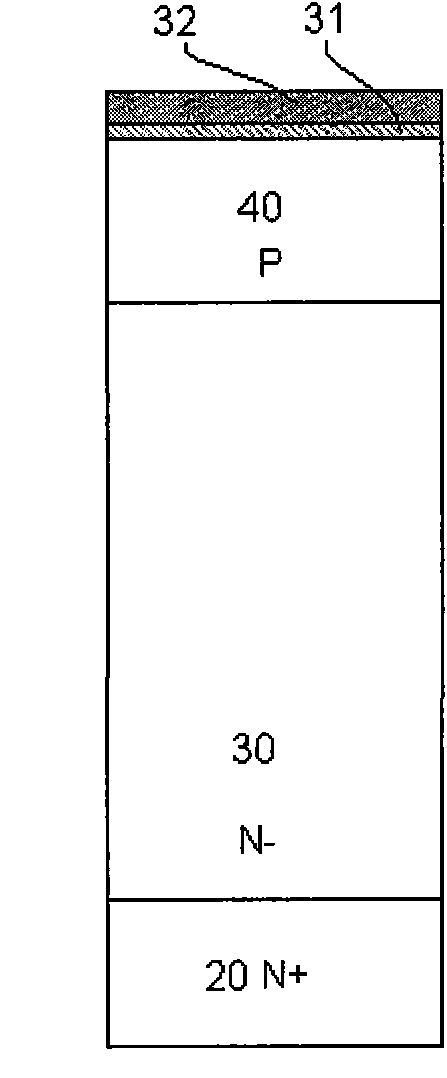

[0042] Then deposit a layer of silicon nitride or oxide layer 32 with a thickness of about 200-5000A, and then advance the ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More