Semiconductor structure and preparation method thereof

A semiconductor and stacked structure technology, applied in semiconductor devices, electrical solid devices, electrical components, etc., can solve the problems of gate layer breakdown, complex etching process of contact holes, high cost, etc., to save costs, reduce etching difficulty, The effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

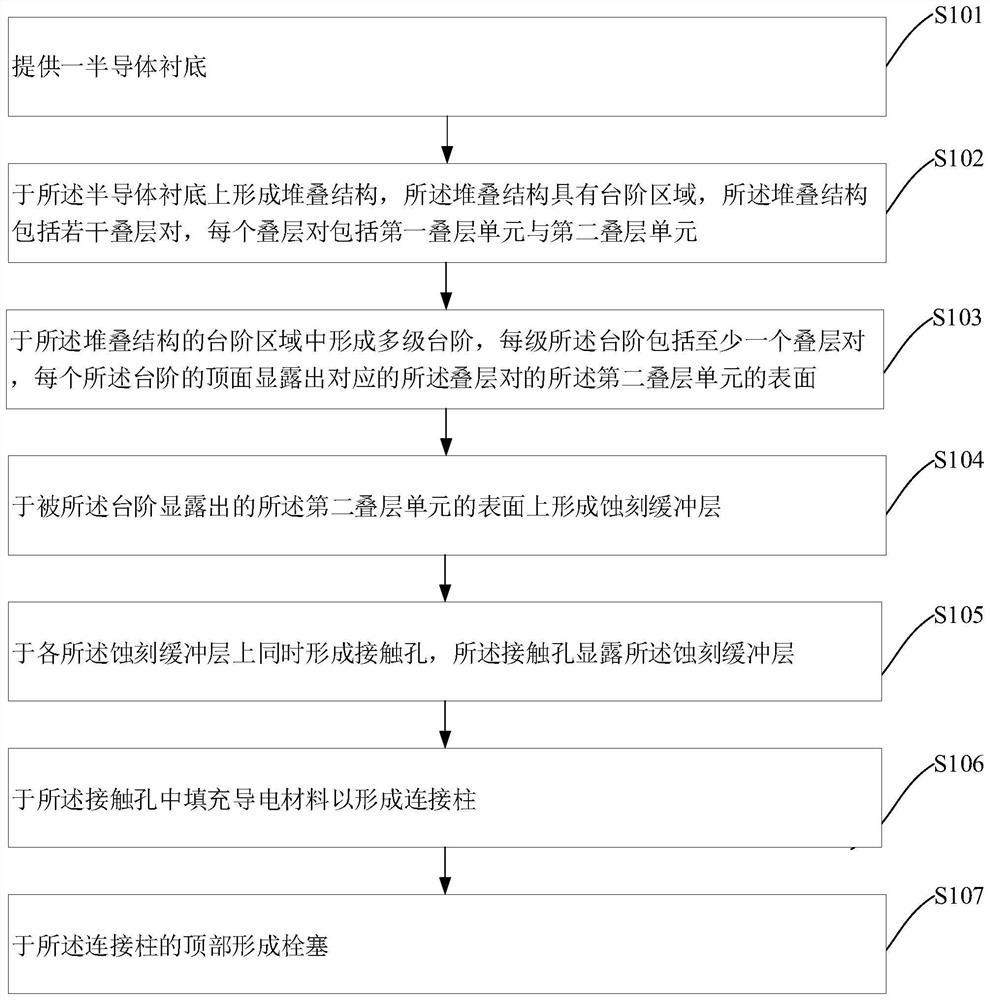

[0112] figure 1 A flow chart of the fabrication of the semiconductor structure of the embodiment of the present invention is shown. see figure 1 , the semiconductor structure method includes:

[0113] Step S101, providing a semiconductor substrate;

[0114] Step S102, forming a stacked structure on the semiconductor substrate, the stacked structure has a stepped region, the stacked structure includes several stacked pairs, each stacked pair includes a first stacked unit and a second stacked unit;

[0115] Step S103, forming multiple steps in the step area of the stacked structure, each level of the steps includes at least one stacked pair, and the top surface of each level of the steps reveals the corresponding first layer of the stacked pair. The surface of the second stack unit;

[0116] Step S104, forming an etching buffer layer on the surface of the second stack unit exposed by the step;

[0117] Step S105, simultaneously forming contact holes on each of the etching...

Embodiment 2

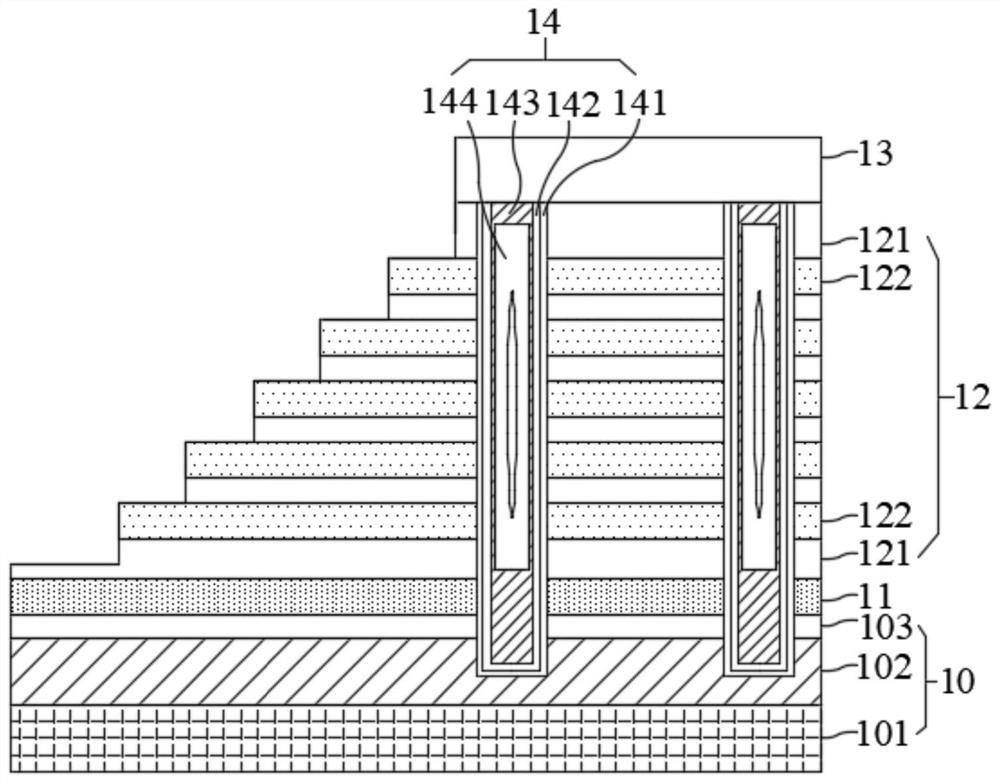

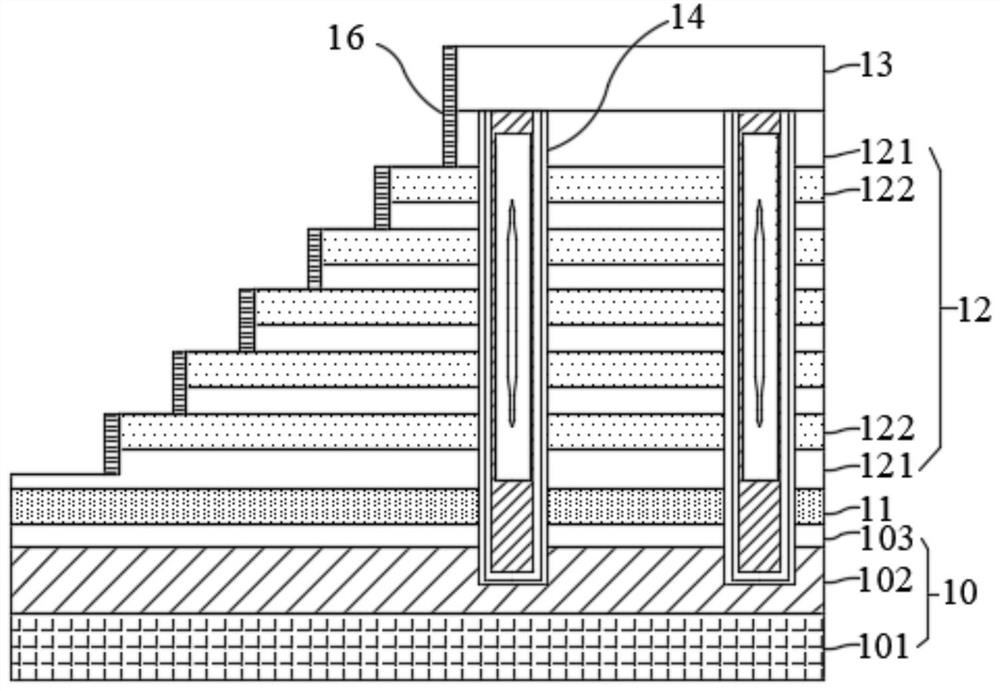

[0152] see Figure 15 , the present invention also provides a semiconductor structure prepared by the preparation method in Embodiment 1, the semiconductor structure at least includes a semiconductor substrate 10, an epitaxial layer 28, a gate stack structure 30, multi-level steps, and an etching buffer layer 18 And some connecting columns 21 ( figure 2 CT in ).

[0153] see Figure 15 , in this embodiment, the semiconductor substrate 10 includes a substrate body 101, and a doped well 102 is formed in the substrate body 101 by a doping process. The substrate body 101 can be selected according to the actual requirements of the device, and the substrate body 101 can include silicon lining, germanium (Ge) substrate, silicon germanium (SiGe) substrate, SOI (Silicon-on-insulator, silicon-on-insulator) substrate or GOI (Germanium-on-Insulator, germanium-on-insulator) substrate, etc., the substrate body 101 can also be a substrate including other element semiconductors or compoun...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More