An accelerator structure and loop unrolling method for binarized neural network

A technology of binary neural and network accelerators, applied in the field of accelerator structure and loop unrolling, which can solve the problems of redundant computing resources and inability to achieve optimal efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention is described in detail below in conjunction with accompanying drawing:

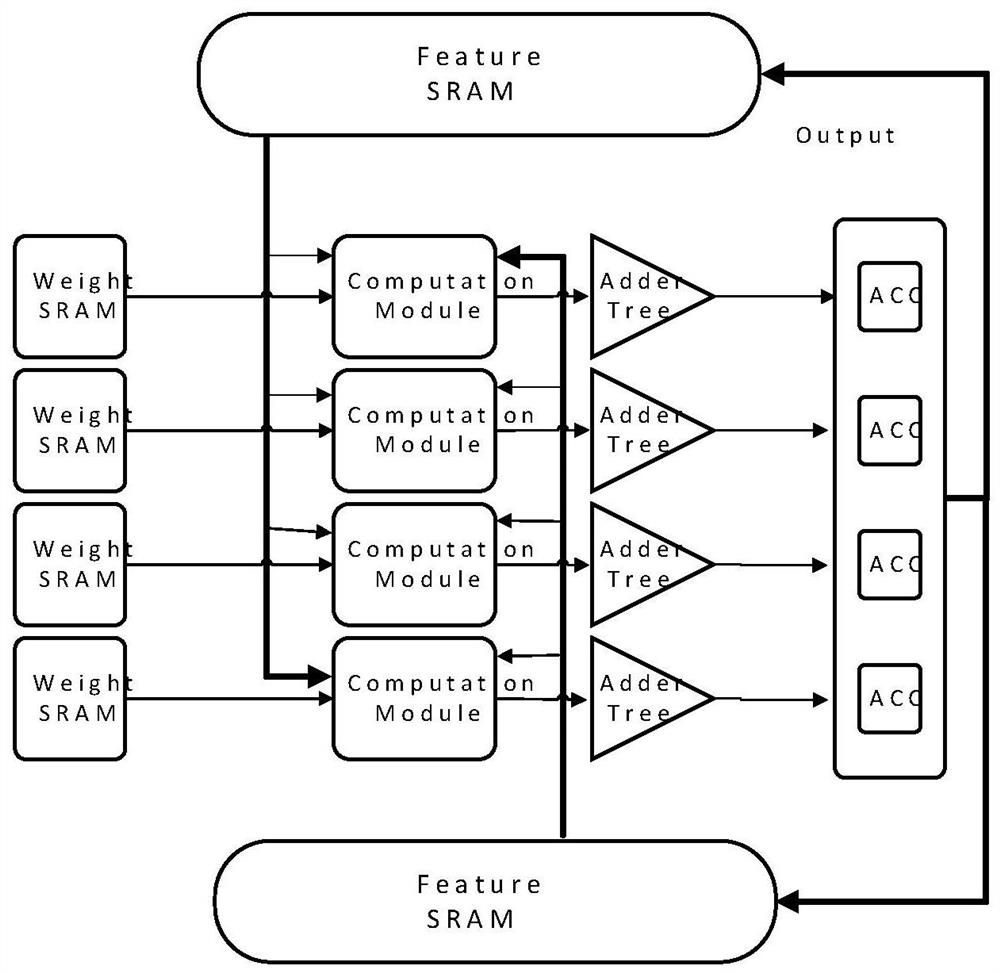

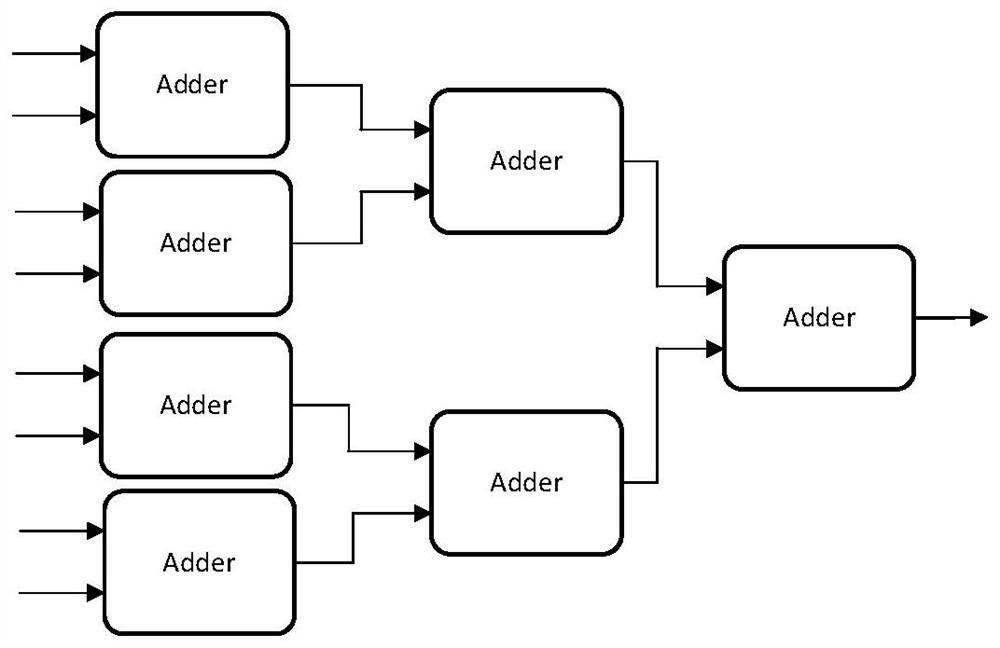

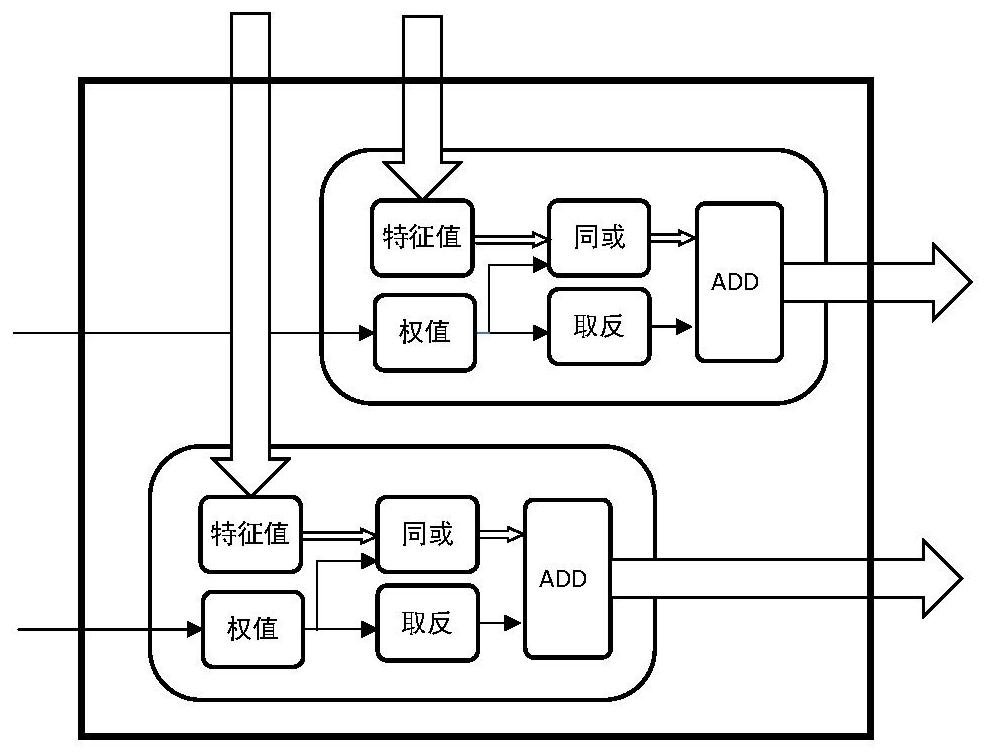

[0029] refer to figure 1 , the binarized neural network hardware accelerator structure of the present invention comprises two eigenvalue SRAMs, the bit width is n*K, K block weight SRAMs, the bit width is K, K special calculation modules, and K addition tree units , K accumulators. The weight SRAM stores the weights arranged according to the rules described later. Two SRAMs with a bit width of eigenvalues of K*n bits store the input eigenvalue and the input eigenvalue respectively. After the calculation of one layer is completed, the output eigenvalue SRAM The stored data becomes the input feature value of the next layer. The two input signals of each weight calculation module come from the same input feature SRAM and different weight SRAM respectively, and the bit widths are K*n bit and K bit respectively. After the calculation is completed, the calculation results enter ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More