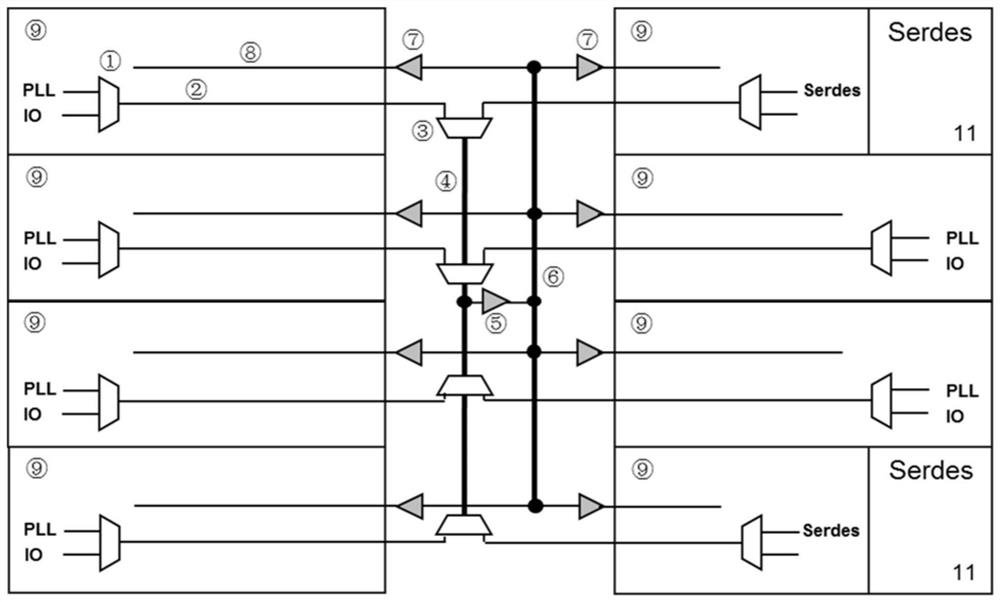

Clock structure of field programmable gate array and adjusting method thereof

A technology of structure adjustment and gate array, applied in the field of FPGA, can solve the problems of inability to achieve performance, unstable clock, and inability of FPGA to reach the clock frequency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In the following description, many technical details are proposed in order to enable readers to better understand the application. However, those skilled in the art can understand that the technical solutions claimed in this application can be realized even without these technical details and various changes and modifications based on the following implementation modes.

[0028] Explanation of some concepts:

[0029] User trigger: refers to the trigger used by the user logic in the FPGA.

[0030] FPGA: Field Programmable Gate Array, Field Programmable Gate Array.

[0031] DFFs: D type flip-flop, D type flip-flop.

[0032] Serdes: Serializer-Deserializer, short for serializer and deserializer.

[0033] The following outlines some innovations in the implementation of the present application:

[0034] Prior to this application, those skilled in the art generally believed that clock skew was harmful, because clock skew would reduce operation efficiency and increase oper...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More