Soi field effect transistor with reduced side leakage and its preparation method

A field-effect transistor and main body technology, which is applied in the direction of transistor, semiconductor/solid-state device manufacturing, circuit, etc., can solve problems such as failure and leakage, and achieve the effect of reducing side leakage, reducing side leakage, and increasing leakage resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

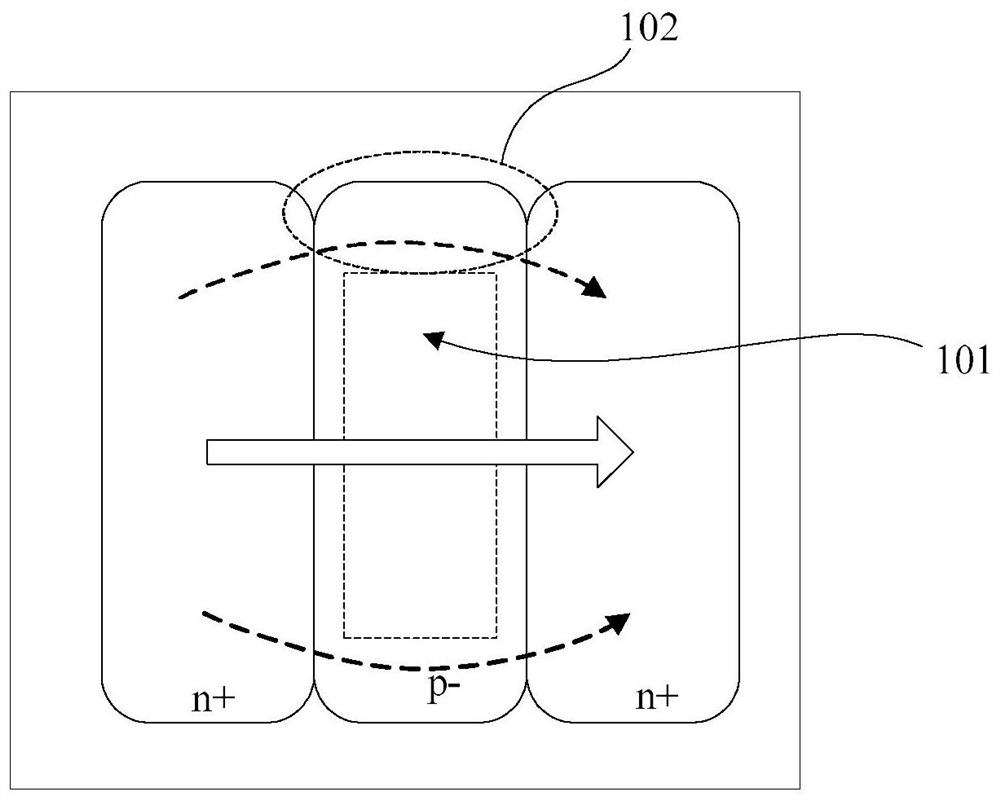

[0060] Such as figure 1 As shown, removing the insulating layer (BOX layer) below the channel of the SOI transistor can effectively prevent the total dose effect. This solution removes the insulating layer below the transistor channel to form a groove 101, which can effectively reduce the total dose effect. However, In the structure, the insulating layer (BOX layer) still has overlapping contact portion 102 with the conductive channel. When the total dose effect occurs, it will cause leakage in the direction of the dashed line.

[0061] Based on the above problems, such as Figure 2 to Figure 28 As shown, the present embodiment provides a method for preparing an SOI field effect transistor with reduced side leakage, and the method for preparing includes the steps of:

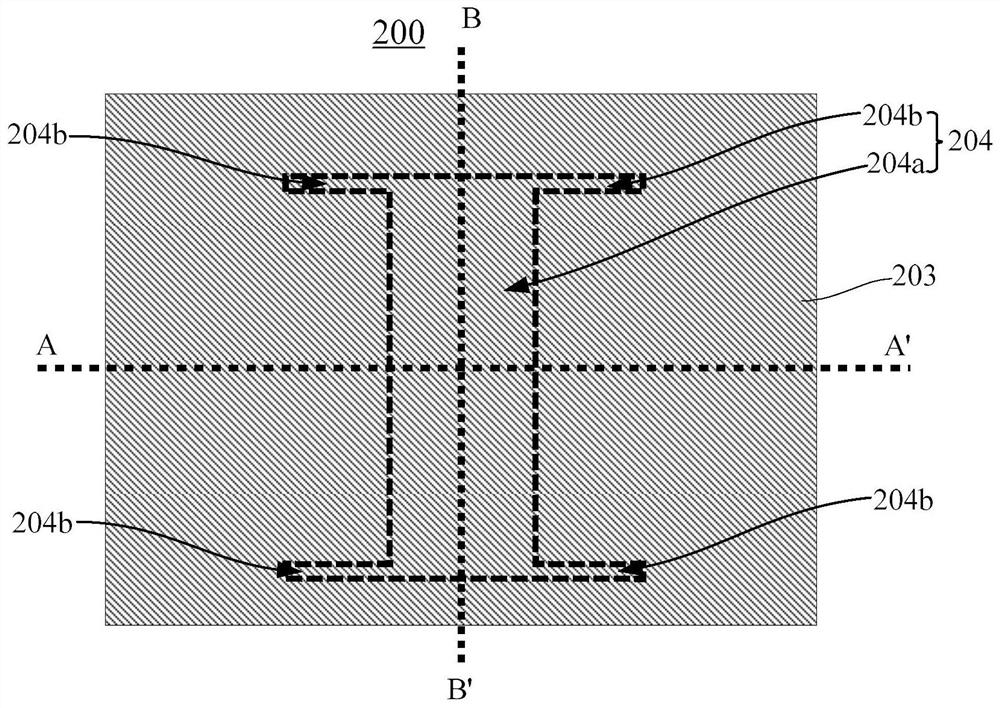

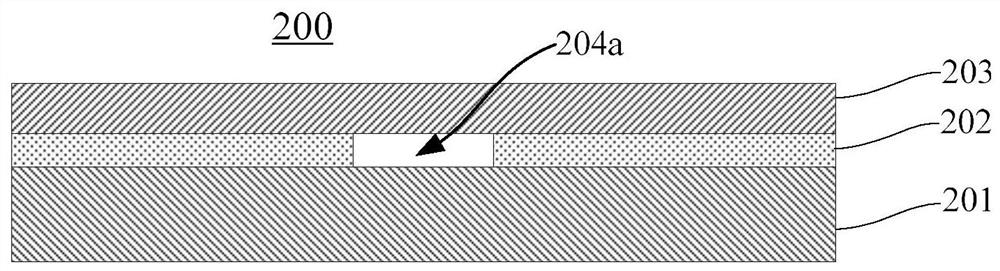

[0062] Such as Figure 2 to Figure 4 As shown, step 1) is first performed to provide a patterned SOI substrate 200, the patterned SOI substrate 200 includes a bottom substrate 201, an insulating layer 202 and...

Embodiment 2

[0088] This embodiment provides an SOI field effect transistor with reduced side leakage. The SOI field effect transistor with reduced side leakage can be prepared by the preparation method of the first embodiment above, but is not limited to the preparation method of the first embodiment, as long as it can be formed An SOI field effect transistor with reduced side leakage is sufficient. For the beneficial effect achieved by the SOI field effect transistor with reduced side leakage, please refer to Embodiment 1, which will not be repeated below.

[0089] Such as figure 2 , Figure 7 , Figure 25 to Figure 27 As shown, the SOI field effect transistor with reduced side leakage includes:

[0090] A patterned SOI substrate 200, the patterned SOI substrate 200 includes a bottom substrate 201, an insulating layer 202 and a top semiconductor layer 203, the insulating layer 202 below the top semiconductor layer 203 has a groove 204, the The groove 204 includes a main body groove ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More