Multi-node multi-channel high-speed parallel processing method and system

A parallel processing and multi-channel technology, applied in the computer field, can solve problems that affect transmission efficiency and processing progress, data congestion, out-of-sequence, etc., and achieve the effects of maximizing utilization, improving efficiency, and improving processing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

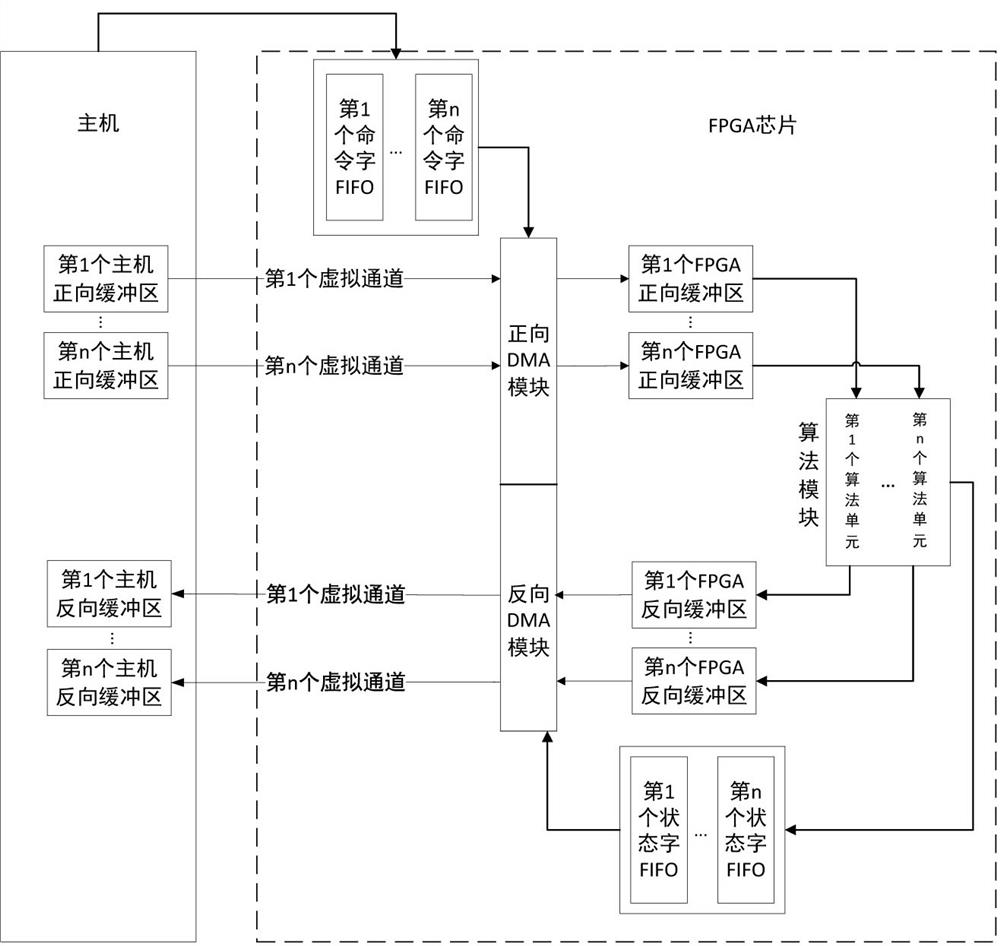

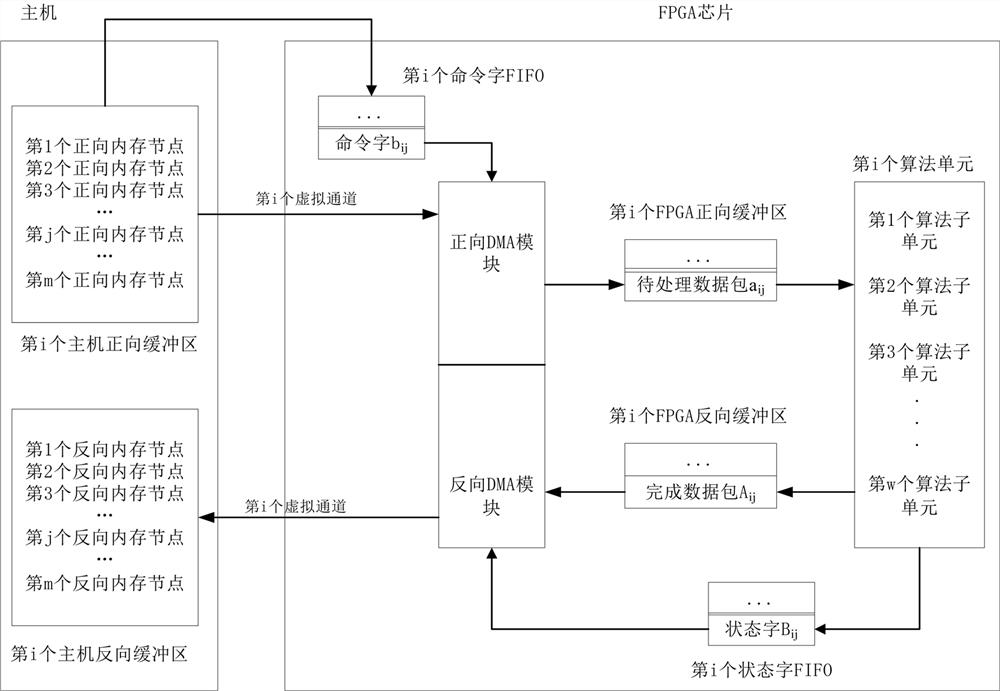

[0026] In order to make the present invention more clear, the technical solutions of the present invention will be further described in detail below through specific embodiments.

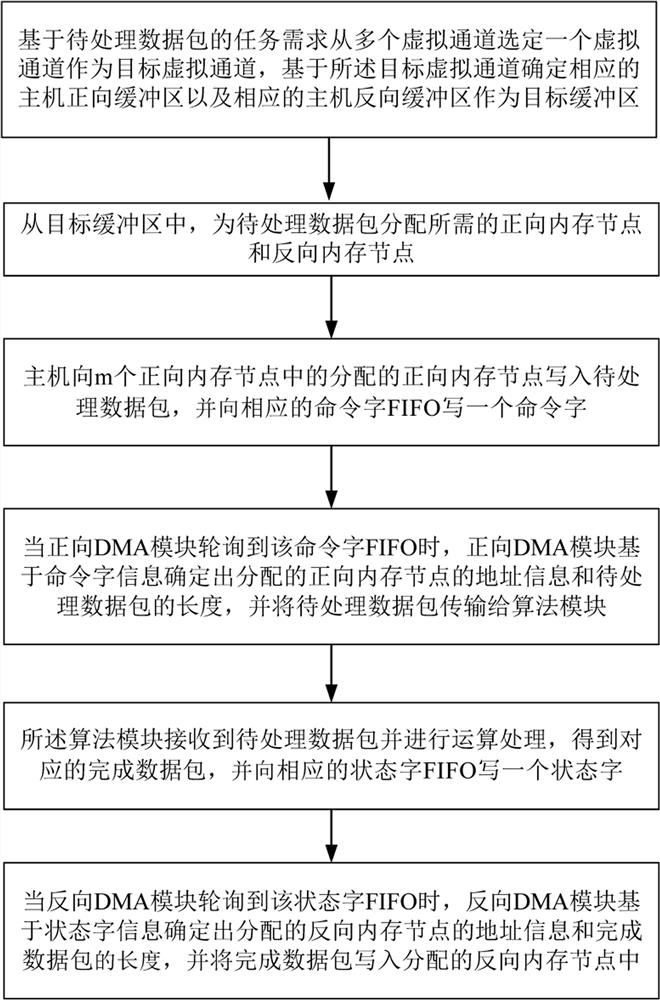

[0027] image 3 A flowchart showing a multi-node multi-channel high-speed parallel processing method of the present invention.

[0028] Such as image 3 As shown, the first aspect of the present invention proposes a kind of multi-node multi-channel high-speed parallel processing method, and described method comprises the following steps:

[0029] Selecting a virtual channel from multiple virtual channels as the target virtual channel based on the task requirements of the data packets to be processed, and determining the corresponding host forward buffer and the corresponding host reverse buffer as the target buffer based on the target virtual channel; Among them, multiple forward memory nodes in the host forward buffer of the same virtual channel are in one-to-one correspondence with multiple reve...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More